**DLPC964** DLPS167 - MARCH 2024

# **DLPC964 Digital Micromirror Device Controller**

#### 1 Features

- Operates the DLP991U DLP® DMD

- Continuous streaming input data over 12 HSS input lanes up to 120Gbps

- Enables high-speed pattern rates up to 12.4kHz binary patterns per second

- 32 lane differential high speed serial interface (HSSI) data bus interface

- Random DMD block addressing and LOAD2

- Compatible with a variety of user-defined FPGAs

- I<sup>2</sup>C interface for control and status queries

## 2 Applications

- Lithography

- Direct imaging

- Flat panel display

- Printed circuit board manufacturing

- Industrial

- 3D printing

- 3D scanners for machine vision

- Quality control

- Displays

- 3D imaging

- Augmented reality and information overlay

### 3 Description

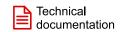

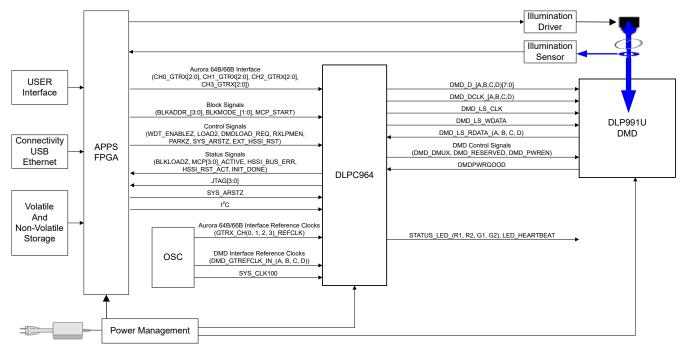

The DLPC964 controller works with the DLP991U digital micromirror device (DMD). The controller provides a high-speed data and control interface for the DMD to enable binary pattern rates up to 12.4kHz. These fast pattern rates set DLP technology apart from other spatial light modulators and offer

a strategic advantage for equipment needing fast, accurate, and programmable light steering capability. The DLPC964 provides the required clocking pulses and timing information to the DMD. The unique capability and value offered by the controller make it well-suited to support a wide variety of direct imaging, industrial, and advanced display applications.

In DLP-based electronics solutions, image data is 100% digital from the DLPC964 input port to the projected image. The image stays in digital form and is never converted into an analog signal. The DLPC964 processes the digital input image and converts the data into a format needed by the DMD for proper display. The DMD then steers the light to the location determined by the pixel data loaded into the DMD.

For complete electrical and mechanical specifications of the DLPC964, see the AMD VirtexTM 7 product specification.

Get started with TI DLP® light-control technology page to learn how to get started with the DLPC964.

The DLP advanced light control resources on ti.com accelerate time to market, which include evaluation modules, optical modules manufacturers, and DLP design network partners.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |  |

|-------------|------------------------|-------------------|--|

| DLPC964     | FCBGA (1158)           | 35.00mm × 35.00mm |  |

For more information, see the Mechanical, Packaging, and Orderable addendum.

\*Each HSSI data bus consists of 8 data pair + 1 clock pair

Simplified Application

# **Table of Contents**

| 1 Features                           | 1  | 7.1 Application Information                          | 50 |

|--------------------------------------|----|------------------------------------------------------|----|

| 2 Applications                       |    | 7.2 Typical Application                              |    |

| 3 Description                        |    | 7.3 Interfacing to DLPC964 Controller High Speed     |    |

| 4 Pin Configuration and Functions    | 3  | Serial (HSS) Aurora 64B/66B Inputs                   | 54 |

| 5 Specifications                     | 12 | 7.4 Power Supply Recommendations                     | 66 |

| 5.1 Absolute Maximum Ratings         | 12 | 7.5 Layout                                           | 68 |

| 5.2 ESD Ratings                      | 12 | 7.6 Layout Example                                   |    |

| 5.3 Recommended Operating Conditions | 12 | 8 Device and Documentation Support                   | 74 |

| 5.4 Thermal Information              | 13 | 8.1 Documentation Support                            | 74 |

| 5.5 Electrical Characteristics       | 13 | 8.2 Receiving Notification of Documentation Updates. | 74 |

| 5.6 Timing Requirements              | 14 | 8.3 Support Resources                                | 74 |

| 6 Detailed Description               | 15 | 8.4 Trademarks                                       | 74 |

| 6.1 Overview                         | 15 | 8.5 Electrostatic Discharge Caution                  | 74 |

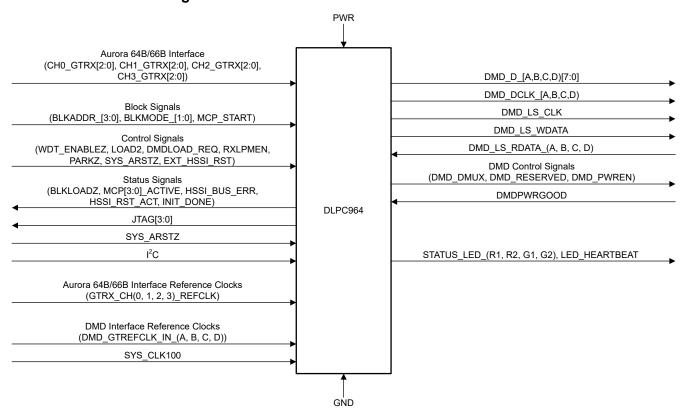

| 6.2 Functional Block Diagram         | 15 | 8.6 Glossary                                         | 74 |

| 6.3 Feature Description              | 15 | 9 Revision History                                   | 74 |

| 6.4 Device Functional Modes          | 23 | 10 Mechanical, Packaging, and Orderable              |    |

| 6.5 Register Map                     | 31 | Information                                          | 75 |

| 7 Application and Implementation     | 50 |                                                      |    |

## 4 Pin Configuration and Functions

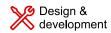

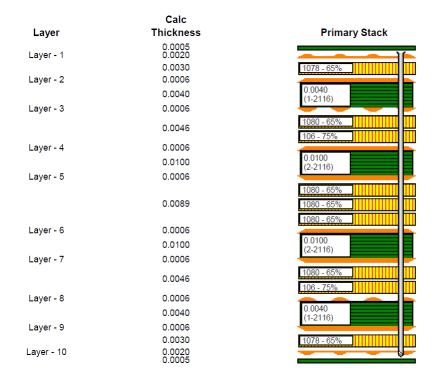

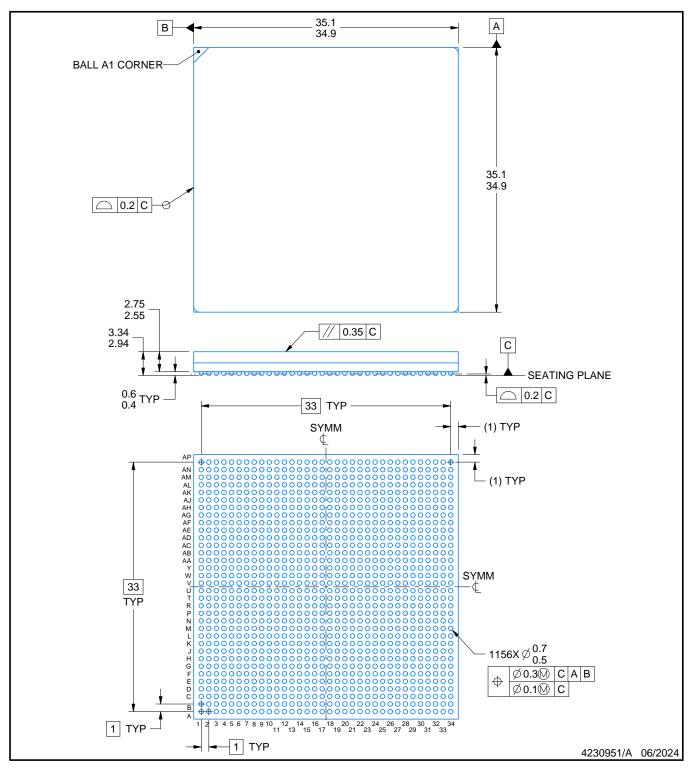

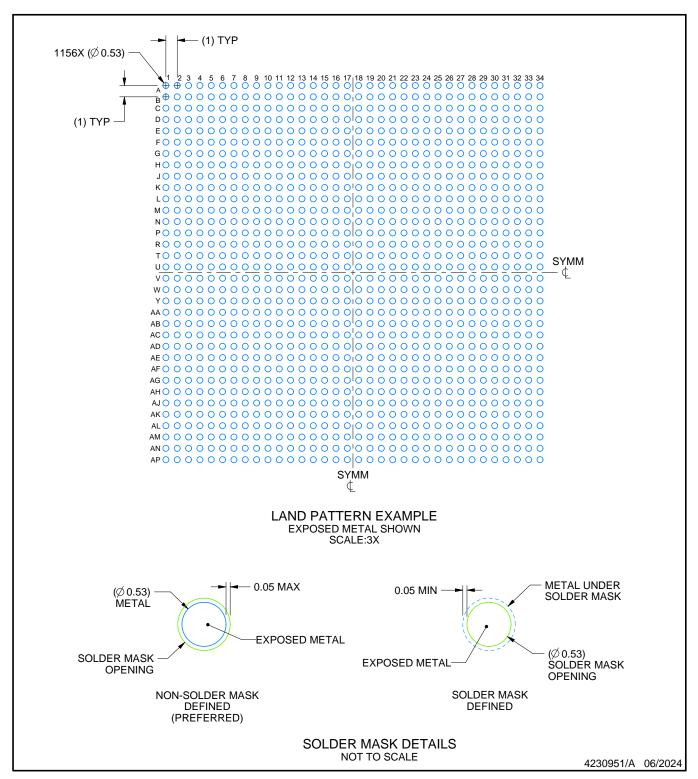

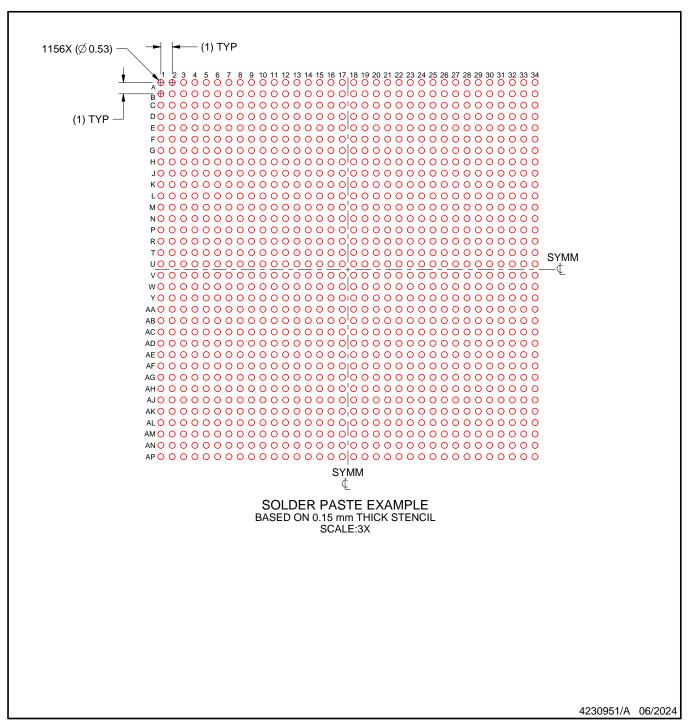

Figure 4-1. ZUM Package, 1158-Pin FCBGA, Bottom View

#### I/O Type Descriptions

| "O Type Beschiptions |                           |  |  |  |  |

|----------------------|---------------------------|--|--|--|--|

| I/O TYPE             | DESCRIPTION               |  |  |  |  |

| PWR                  | Power                     |  |  |  |  |

| GND                  | Ground                    |  |  |  |  |

| LVCMOS18_I           | LVCMOS 1.8V input         |  |  |  |  |

| LVCMOS18_O           | LVCMOS 1.8V output        |  |  |  |  |

| LVCMOS18_B           | LVCMOS 1.8V bidirectional |  |  |  |  |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

I/O Type Descriptions (continued)

| I/O TYPE     | DESCRIPTION                                            |

|--------------|--------------------------------------------------------|

| LVDS_18_NI   | LVDS 1.8V negative input                               |

| LVDS_18_PI   | LVDS 1.8V positive input                               |

| LVDS_18_NO   | LVDS 1.8V negative output                              |

| LVDS_18_PO   | LVDS 1.8V positive output                              |

| LVDCI_18_I   | Low-voltage digitally controlled impedance 1.8V input  |

| LVDCI_18_O   | Low-voltage digitally controlled impedance 1.8V output |

| MGTHRX_18_NI | GTH Receiver Differential 1.8V negative input          |

| MGTHRX_18_PI | GTH Receiver Differential 1.8V positive input          |

| MGTHTX_18_NO | GTH Receiver Differential 1.8V negative output         |

| MGTHTX_18_PO | GTH Receiver Differential 1.8V positive output         |

| MGTREFCLK_NI | GTH Receiver RefClk Differential 1.8V negative input   |

| MGTREFCLK_PI | GTH Receiver RefClk Differential 1.8V positive input   |

| NC           | No connection                                          |

### **Table 4-1. Pin Functions**

|                 |         | 10.010 1 111 111        |                      | ,                     |                                                                                       |

|-----------------|---------|-------------------------|----------------------|-----------------------|---------------------------------------------------------------------------------------|

| NAME            | PIN NO. | I/O TYPE <sup>(1)</sup> | ACTIVE (HI<br>OR LO) | CLOCK SYSTEM          | DESCRIPTION                                                                           |

| SYS ARSTZ       | G25     | LVCMOS18 I              | LO = 0               |                       | DLPC964 Reset                                                                         |

| I2C ADDR SEL[0] | M25     | LVCMOS18 I              | HI = 1               |                       | DLPC964 Slave I <sup>2</sup> C Address Bit 0                                          |

| I2C_ADDR_SEL[1] | D26     | LVCMOS18 I              | HI                   |                       | DLPC964 Slave I <sup>2</sup> C Address Bit 1                                          |

| I2C_SCL         | B23     | LVCMOS18_B              | -                    | _                     | DLPC964 Slave I <sup>2</sup> C Clock. Requires an external 2.2kΩ pullup resistor      |

| I2C_SDA         | B25     | LVCMOS18_B              | _                    | I2C_SCL               | DLPC964 Slave I <sup>2</sup> C Data.<br>Requires an external 2.2kΩ pullup<br>resistor |

| SYS_CLK100_N    | H24     | LVDS_18_NI              | _                    | Reference clock       | 100MHz Differential Reference<br>Clock (N)                                            |

| SYS_CLK100_P    | J24     | LVDS_18_PI              | _                    | Reference clock       | 100MHz Differential Reference<br>Clock (P)                                            |

| CCLK_0          | V25     | LVCMOS18_O              | _                    | Flash interface clock | Connect to Configuration Flash device CLK.                                            |

| FLASH_MISO      | A24     | LVCMOS18_I              | _                    | CCLK_0                | Connect to Configuration Flash MISO.                                                  |

| FLASH_MOSI      | A23     | LVCMOS18_O              | _                    | CCLK_0                | Connect to Configuration Flash device MOSI.                                           |

| FLASH_CSZ       | C24     | LVCMOS18_O              | LO                   | CCLK_0                | Connect to Configuration Flash device CSZ.                                            |

| BLKADDR[0]      | B26     | LVCMOS18_I              | н                    | _                     | Block Address bit 0                                                                   |

| BLKADDR[1]      | A26     | LVCMOS18_I              | н                    | _                     | Block Address bit 1                                                                   |

| BLKADDR[2]      | F24     | LVCMOS18_I              | н                    | _                     | Block Address bit 2                                                                   |

| BLKADDR[3]      | F25     | LVCMOS18_I              | Н                    | _                     | Block Address bit 3                                                                   |

| BLKADDR[4]      | E24     | LVCMOS18_I              | Н                    | _                     | Block Address bit 4                                                                   |

| BLKMODE[0]      | C27     | LVCMOS18_I              | Н                    | _                     | Block Mode bit 0                                                                      |

| BLKMODE[1]      | A25     | LVCMOS18_I              | Н                    | _                     | Block Mode bit 1                                                                      |

| BLKLOADZ        | B27     | LVDCI_18_O              | LO                   | _                     | Connect to Apps FPGA<br>BLKLOADZ.                                                     |

| LOAD2           | D25     | LVCMOS18_I              | н                    | _                     | Enables Load-2 functionality of the DMD. Includes an internal pulldown                |

| WDT_ENABLEZ     | J22     | LVCMOS18_I              | LO                   | -                     | DMD Mirror Clocking Pulse<br>Watchdog Timer Enable. Includes<br>an internal pulldown  |

| MCP_START       | J25     | LVCMOS18_I              | н                    | _                     | Initiates a Mirror Clocking Pulse (MCP)                                               |

| MCP0_ACTIVE     | E27     | LVDCI_18_O              | н                    | _                     | Connect to Apps FPGA MCP_ACTIVE0.                                                     |

| MCP1_ACTIVE     | D27     | LVDCI_18_O              | н                    | _                     | Connect to Apps FPGA MCP_ACTIVE1.                                                     |

| PIN ACTIVE (H)      |      |                         |                      |                   |                                                |  |  |

|---------------------|------|-------------------------|----------------------|-------------------|------------------------------------------------|--|--|

| NAME                | NO.  | I/O TYPE <sup>(1)</sup> | ACTIVE (HI<br>OR LO) | CLOCK SYSTEM      | DESCRIPTION                                    |  |  |

| MCP2_ACTIVE         | E26  | LVDCI_18_O              | н                    | _                 | Connect to Apps FPGA<br>MCP_ACTIVE2.           |  |  |

| MCP3_ACTIVE         | H25  | LVDCI_18_O              | HI                   | _                 | Connect to Apps FPGA MCP ACTIVE3.              |  |  |

| DMDLOAD_REQ         | M22  | LVCMOS18_I              | н                    | _                 | Connect to Apps FPGA                           |  |  |

| DMD_GTREFCLK_IN_A_N | AB30 | LVDS_18_NI              | _                    |                   | DMDLOAD_REQ.  DMD Bus A Reference Clock Input. |  |  |

| DMD_GTREFCLK_IN_A_P | AB29 | LVDS_18_PI              | _                    | - Reference clock | 100Ω internal LVDS termination                 |  |  |

| DMD_GTREFCLK_IN_B_N | AB5  | LVDS_18_NI              | _                    |                   | DMD Bus B Reference Clock Input.               |  |  |

| DMD_GTREFCLK_IN_B_P | AB6  | LVDS_18_PI              | _                    | Reference clock   | 100Ω internal LVDS termination                 |  |  |

| DMD_GTREFCLK_IN_C_N | M30  | LVDS_18_NI              | _                    |                   | DMD Bus C Reference Clock Input.               |  |  |

| DMD_GTREFCLK_IN_C_P | M29  | LVDS_18_PI              | _                    | Reference clock   | 100Ω internal LVDS termination                 |  |  |

| DMD_GTREFCLK_IN_D_N | M5   | LVDS_18_NI              | _                    |                   | DMD Bus D Reference Clock Input.               |  |  |

| DMD_GTREFCLK_IN_D_N | M6   |                         |                      | Reference clock   | 100Ω internal LVDS termination                 |  |  |

|                     | AK34 | LVDS_18_PI              |                      | _                 | Output Rus A Clock to DMD                      |  |  |

| DMD_DCLK_AN         |      | MGTHTX_18_NO            |                      |                   | Output Bus A Clock to DMD                      |  |  |

| DMD_DCLK_AP         | AK33 | MGTHTX_18_PO            | _                    | _                 |                                                |  |  |

| DMD_DCLK_BN         | AJ3  | MGTHTX_18_NO            |                      | _                 | Output Bus B Clock to DMD                      |  |  |

| DMD_DCLK_BP         | AJ4  | MGTHTX_18_PO            | _                    | _                 |                                                |  |  |

| DMD_DCLK_CN         | G32  | MGTHTX_18_NO            | _                    | _                 | Output Bus C Clock to DMD                      |  |  |

| DMD_DCLK_CP         | G31  | MGTHTX_18_PO            | _                    | _                 |                                                |  |  |

| DMD_DCLK_DN         | G3   | MGTHTX_18_NO            | _                    | _                 | Output Bus D Clock to DMD                      |  |  |

| DMD_DCLK_DP         | G4   | MGTHTX_18_PO            | _                    | _                 |                                                |  |  |

| DMD_D_AN[0]         | AP34 | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 0 to DMD                 |  |  |

| DMD_D_AP[0]         | AP33 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        |                                                |  |  |

| DMD_D_AN[1]         | AN32 | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 1 to DMD                 |  |  |

| DMD_D_AP[1]         | AN31 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        | <u> </u>                                       |  |  |

| DMD_D_AN[2]         | AM34 | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 2 to DMD                 |  |  |

| DMD_D_AP[2]         | AM33 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        |                                                |  |  |

| DMD_D_AN[3]         | AJ32 | MGTHTX_18_NO            |                      | DMD_DCLK_A        | Output Bus A Data bit 3 to DMD                 |  |  |

| DMD_D_AP[3]         | AJ31 | MGTHTX_18_PO            |                      | DMD_DCLK_A        | Output Bus A Data bit 3 to Divid               |  |  |

|                     | AH34 |                         |                      |                   | Output Bus A Data hit 4 to DAAD                |  |  |

| DMD_D_AN[4]         |      | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 4 to DMD                 |  |  |

| DMD_D_AP[4]         | AH33 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        |                                                |  |  |

| DMD_D_AN[5]         | AF34 | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 5 to DMD                 |  |  |

| DMD_D_AP[5]         | AF33 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        |                                                |  |  |

| DMD_D_AN[6]         | AD34 | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 6 to DMD                 |  |  |

| DMD_D_AP[6]         | AD33 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        |                                                |  |  |

| DMD_D_AN[7]         | AB34 | MGTHTX_18_NO            | _                    | DMD_DCLK_A        | Output Bus A Data bit 7 to DMD                 |  |  |

| DMD_D_AP[7]         | AB33 | MGTHTX_18_PO            | _                    | DMD_DCLK_A        |                                                |  |  |

| DMD_D_BN[0]         | AB1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 0 to DMD                 |  |  |

| DMD_D_BP[0]         | AB2  | MGTHTX_18_PO            | _                    | DMD_DCLK_B        |                                                |  |  |

| DMD_D_BN[1]         | AD1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 1 to DMD                 |  |  |

| DMD_D_BP[1]         | AD2  | MGTHTX_18_PO            | _                    | DMD_DCLK_B        |                                                |  |  |

| DMD_D_BN[2]         | AF1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 2 to DMD                 |  |  |

| DMD_D_BP[2]         | AF2  | MGTHTX 18 PO            | _                    | DMD_DCLK_B        |                                                |  |  |

| DMD_D_BN[3]         | AH1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 3 to DMD                 |  |  |

| DMD_D_BP[3]         | AH2  |                         |                      |                   | - Cuput Bus B Butta Sit 6 to BINIB             |  |  |

|                     |      | MGTHTX_18_PO            | _                    | DMD_DCLK_B        | Output Puo P Dete hit 4 to DMD                 |  |  |

| DMD_D_BN[4]         | AK1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 4 to DMD                 |  |  |

| DMD_D_BP[4]         | AK2  | MGTHTX_18_PO            | _                    | DMD_DCLK_B        | 0.1.10.05.10.51.51.51                          |  |  |

| DMD_D_BN[5]         | AM1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 5 to DMD                 |  |  |

| DMD_D_BP[5]         | AM2  | MGTHTX_18_PO            | _                    | DMD_DCLK_B        |                                                |  |  |

| DMD_D_BN[6]         | AN3  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 6 to DMD                 |  |  |

| DMD_D_BP[6]         | AN4  | MGTHTX_18_PO            | _                    | DMD_DCLK_B        |                                                |  |  |

| DMD_D_BN[7]         | AP1  | MGTHTX_18_NO            | _                    | DMD_DCLK_B        | Output Bus B Data bit 7 to DMD                 |  |  |

| DMD_D_BP[7]         | AP2  | MGTHTX_18_PO            | _                    | DMD_DCLK_B        |                                                |  |  |

|                   | PIN  |                         | 4-1. Pin Functions (cont |                 |                                                          |

|-------------------|------|-------------------------|--------------------------|-----------------|----------------------------------------------------------|

| NAME              | NO.  | I/O TYPE <sup>(1)</sup> | OR LO)                   | CLOCK SYSTEM    | DESCRIPTION                                              |

| DMD_D_CN[0]       | A32  | MGTHTX_18_NO            | _                        | DMD_DCLK_C      | Output Bus C Data bit 0 to DMD                           |

| DMD_D_CP[0]       | A31  | MGTHTX_18_PO            | _                        | DMD_DCLK_C      |                                                          |

| DMD_D_CN[1]       | B34  | MGTHTX_18_NO            | _                        | DMD_DCLK_C      | Output Bus C Data bit 1 to DMD                           |

| DMD_D_CP[1]       | B33  | MGTHTX_18_PO            | _                        | DMD_DCLK_C      |                                                          |

| DMD_D_CN[2]       | D34  | MGTHTX_18_NO            | _                        | DMD_DCLK_C      | Output Bus C Data bit 2 to DMD                           |

| DMD_D_CP[2]       | D33  | MGTHTX_18_PO            | _                        | DMD_DCLK_C      |                                                          |

| DMD_D_CN[3]       | F34  | MGTHTX_18_NO            | _                        | DMD_DCLK_C      | Output Bus C Data bit 3 to DMD                           |

| DMD D CP[3]       | F33  | MGTHTX_18_PO            | _                        | DMD_DCLK_C      |                                                          |

| DMD D CN[4]       | H34  | MGTHTX_18_NO            | _                        | DMD DCLK C      | Output Bus C Data bit 4 to DMD                           |

| DMD_D_CP[4]       | H33  | MGTHTX 18 PO            | _                        | DMD DCLK C      |                                                          |

| DMD_D_CN[5]       | K34  | MGTHTX_18_NO            | _                        | DMD DCLK C      | Output Bus C Data bit 5 to DMD                           |

| DMD_D_CP[5]       | K33  | MGTHTX_18_PO            | _                        | DMD_DCLK_C      | - Capat Bas o Bata bit o to Bitib                        |

| DMD_D_CN[6]       | M34  |                         |                          | DMD_DCLK_C      | Output Bus C Data bit 6 to DMD                           |

|                   | M33  | MGTHTX_18_NO            |                          | DMD_DCLK_C      | Output Bus C Data bit 0 to Divid                         |

| DMD_D_CP[6]       |      | MGTHTX_18_PO            | _                        |                 | Output Due C Date hit 7 to DMD                           |

| DMD_D_CN[7]       | N32  | MGTHTX_18_NO            |                          | DMD_DCLK_C      | Output Bus C Data bit 7 to DMD                           |

| DMD_D_CP[7]       | N31  | MGTHTX_18_PO            | _                        | DMD_DCLK_C      |                                                          |

| DMD_D_DN[0]       | N3   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 0 to DMD                           |

| DMD_D_DP[0]       | N4   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[1]       | M1   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 1 to DMD                           |

| DMD_D_DP[1]       | M2   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[2]       | K1   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 2 to DMD                           |

| DMD_D_DP[2]       | K2   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[3]       | H1   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 3 to DMD                           |

| DMD_D_DP[3]       | H2   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[4]       | F1   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 4 to DMD                           |

| DMD_D_DP[4]       | F2   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[5]       | D1   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 5 to DMD                           |

| DMD_D_DP[5]       | D2   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[6]       | B1   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 6 to DMD                           |

| DMD_D_DP[6]       | B2   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| DMD_D_DN[7]       | A3   | MGTHTX_18_NO            | _                        | DMD_DCLK_D      | Output Bus D Data bit 7 to DMD                           |

| DMD_D_DP[7]       | A4   | MGTHTX_18_PO            | _                        | DMD_DCLK_D      |                                                          |

| GTRX_CH0_REFCLK_N | R28  | MGTREFCLK_NI            | _                        |                 | Input CH0 Reference Clock. 100Ω                          |

| GTRX_CH0_REFCLK_P | R27  | MGTREFCLK_PI            | _                        | Reference clock | internal LVDS termination                                |

| GTRX_CH1_REFCLK_N | W28  | MGTREFCLK NI            | _                        |                 | Input CH1 Reference Clock. 100Ω                          |

| GTRX_CH1_REFCLK_P | W27  | MGTREFCLK PI            | _                        | Reference clock | internal LVDS termination                                |

| GTRX_CH2_REFCLK_N | R7   | MGTREFCLK_NI            | _                        |                 | Input CH2 Reference Clock. 100Ω                          |

| GTRX CH2 REFCLK P | R8   | MGTREFCLK PI            | _                        | Reference clock | internal LVDS termination                                |

| GTRX CH3 REFCLK N | W7   | MGTREFCLK NI            | _                        |                 | Input CH3 Reference Clock. 100Ω                          |

| GTRX_CH3_REFCLK_P | W8   | MGTREFCLK PI            | _                        | Reference clock | internal LVDS termination                                |

| CH0 GTRX N[0]     | T30  | MGTHRX_18_NI            | _                        |                 | Input Bus CH0 Data bit 0. 100Ω                           |

| CH0_GTRX_N[0]     | T29  |                         | _                        | GTRX_CH0_REFCLK | internal LVDS termination                                |

|                   |      | MGTHRX_18_PI            | _                        |                 | Input Bus CH0 Data bit 1. 100Ω                           |

| CH0_GTRX_N[1]     | R32  | MGTHRX_18_NI            | _                        | GTRX_CH0_REFCLK | internal LVDS termination                                |

| CH0_GTRX_P[1]     | R31  | MGTHRX_18_PI            | _                        |                 |                                                          |

| CH0_GTRX_N[2]     | P30  | MGTHRX_18_NI            | _                        | GTRX_CH0_REFCLK | Input Bus CH0 Data bit 2. 100Ω internal LVDS termination |

| CH0_GTRX_P[2]     | P29  | MGTHRX_18_PI            | _                        |                 |                                                          |

| CH1_GTRX_N[0]     | AA32 | MGTHRX_18_NI            | _                        | GTRX_CH1_REFCLK | Input Bus CH1 Data bit 0. 100Ω internal LVDS termination |

| CH1_GTRX_P[0]     | AA31 | MGTHRX_18_PI            | _                        |                 | Input Bus CH1 Data bit 1. 100Ω internal LVDS termination |

| CH1_GTRX_N[1]     | Y30  | MGTHRX_18_NI            | _                        | GTRX_CH1_REFCLK |                                                          |

| CH1_GTRX_P[1]     | Y29  | MGTHRX_18_PI            | _                        |                 | Internal Ly DO terrification                             |

| CH1_GTRX_N[2]     | V30  | MGTHRX_18_NI            | _                        | GTRX_CH1_REFCLK | Input Bus CH1 Data bit 2. 100Ω                           |

| CH1_GTRX_P[2]     | V29  | MGTHRX_18_PI            | _                        | 5               | internal LVDS termination                                |

| CH2_GTRX_N[0]     | T5   | MGTHRX_18_NI            | _                        | CTDY CU2 DEECLY | Input Bus CH2 Data bit 0. 100Ω                           |

| CH2_GTRX_P[0]     | Т6   | MGTHRX_18_PI            | _                        | GTRX_CH2_REFCLK | internal LVDS termination                                |

|                    | PIN     | 10115 (COII             | inidea)              |                 |                                                                       |

|--------------------|---------|-------------------------|----------------------|-----------------|-----------------------------------------------------------------------|

| NAME               | NO.     | I/O TYPE <sup>(1)</sup> | ACTIVE (HI<br>OR LO) | CLOCK SYSTEM    | DESCRIPTION                                                           |

| CH2_GTRX_N[1]      | R3      | MGTHRX_18_NI            | _                    |                 | Input Bus CH2 Data bit 1. 100Ω                                        |

| CH2_GTRX_P[1]      | R4      | MGTHRX_18_PI            | _                    | GTRX_CH2_REFCLK | internal LVDS termination                                             |

| CH2_GTRX_N[2]      | P5      | MGTHRX 18 NI            | _                    |                 | Input Bus CH2 Data bit 2. 100Ω                                        |

| CH2_GTRX_P[2]      | P6      | MGTHRX_18_PI            | _                    | GTRX_CH2_REFCLK | internal LVDS termination                                             |

| CH3_GTRX_N[0]      | AA3     | MGTHRX_18_NI            | _                    |                 | Input Bus CH3 Data bit 0. 100Ω                                        |

| CH3_GTRX_P[0]      | AA4     | MGTHRX_18_PI            | _                    | GTRX_CH3_REFCLK | internal LVDS termination                                             |

| CH3_GTRX_N[1]      | Y5      | MGTHRX 18 NI            | _                    |                 | Input Bus CH3 Data bit 1. 100Ω                                        |

| CH3_GTRX_P[1]      | Y6      | MGTHRX_18_PI            | _                    | GTRX_CH3_REFCLK | internal LVDS termination                                             |

| CH3_GTRX_N[2]      | V5      | MGTHRX_18_NI            |                      |                 | Input Bus CH3 Data bit 2. 100Ω                                        |

|                    | V6      |                         |                      | GTRX_CH3_REFCLK | internal LVDS termination                                             |

| CH3_GTRX_P[2]      |         | MGTHRX_18_PI            |                      |                 | 0                                                                     |

| HSSI_BUS_ERR       | AJ12    | LVDCI_18_O              | HI                   | _               | Connect to Apps FPGA HSSI_BUS_ERR.                                    |

| HSSI_ERR_LATCH_RST | AN12    | LVDCI_18_O              | LO                   | _               | Connect to Latch Clear on DMD board.                                  |

| EXT_HSSI_RST       | AJ14    | LVCMOS18_I              | н                    | _               | Connect to Apps FPGA EXT_HSSI_RST.                                    |

| HSSI_RST_ACT       | AK12    | LVDCI_18_O              | н                    | _               | Connect to Apps FPGA<br>HSSI_RST_ACT.                                 |

| DMD_LS_CLK_N       | AP11    | LVDS_18_NO              | _                    | _               | Output LS Bus Clock to DMD                                            |

| DMD_LS_CLK_P       | AP12    | LVDS_18_PO              | _                    | _               |                                                                       |

| DMD_LS_WDATA_N     | AP14    | LVDS_18_NO              | _                    | DMD_LS_CLK      | Output WData Bus to DMD                                               |

| DMD_LS_WDATA_P     | AN14    | LVDS_18_PO              | _                    | DMD LS CLK      |                                                                       |

| DMD_LS_RDATA_A     | AM8     | LVCMOS18 I              | _                    | DMD_LS_CLK      | Input Bus RData bit A                                                 |

| DMD_LS_RDATA_B     | AN8     | LVCMOS18 I              | _                    | DMD_LS_CLK      | Input Bus RData bit B                                                 |

| DMD_LS_RDATA_C     | AN9     | LVCMOS18_I              | _                    | DMD_LS_CLK      | Input Bus RData bit C                                                 |

| DMD_LS_RDATA_D     | AP9     | LVCMOS18 I              | _                    | DMD_LS_CLK      | Input Bus RData bit D                                                 |

| DMD_DMUX           | AM12    |                         |                      | DINID_EG_GEIX   | Connect to DMUX_LATCHED on                                            |

| BIND_BINOX         | 7 (11/2 | LVCMOS18_I              | HI                   | _               | DMD board.                                                            |

| IRQZ               | E23     | LVDCI_18_O              | LO                   | _               | Connect to Apps FPGA IRQZ.                                            |

| DMD_RESERVED       | AM13    | LVCMOS18_B              | _                    | _               | Connect to RESERVED pin on DMD.                                       |

| PARKZ              | AK9     | LVCMOS18_I              | LO                   | _               | Immediately parks the DMD when asserted Low                           |

| RXLPMEN            | D24     | LVCMOS18_I              | н                    | _               | Enables Aurora 64B/66B Receiver<br>Low Power Mode                     |

| DMD_PWREN          | AL9     | LVDCI_18_O              | н                    | _               | Connect to DMD Power Enable on DMD board.                             |

| DMDPWRGOOD         | P24     | LVCMOS18_I              | н                    | _               | Connect to DMDPWRGOOD on DMD board.                                   |

| PWRGOOD            | H22     | LVCMOS18_I              | н                    | _               | Connect to Power Good on DLPC964 Controller board.                    |

| LED_PWR            | AL14    | LVDCI_18_O              | н                    | _               | Enable control output for LED Power Supply                            |

| STATUS_LED_R1      | AM10    | LVDCI_18_O              | Н                    | _               | Controller PLL clock circuitry NOT locked Indicator LED output        |

| STATUS_LED_R2      | AK13    | LVDCI_18_O              | н                    | _               | DMD HSSI interface Sync errors detected Indicator LED output          |

| STATUS_LED_G1      | AL10    | LVDCI_18_O              | н                    | _               | Controller PLL clock circuitry locked Indicator LED output            |

| STATUS_LED_G2      | AK8     | LVDCI_18_O              | н                    | _               | No DMD HSSI interface Sync<br>errors detected Indicator LED<br>output |

| LED HEARTBEAT      | AK14    | LVDCI_18_O              | HI                   | _               | Heartbeat Indicator LED output                                        |

| INIT_DONE          | F23     | LVDCI_18_O              | н                    | _               | Connect to Apps FPGA C964_INIT_DONE                                   |

| M0_0               | AA10    | LVCMOS18_I              | _                    | _               | DLPC964 Configuration — connect to 1.8V                               |

| M1_0               | Y10     | LVCMOS18_I              | _                    | _               | DLPC964 Configuration — connect to GND                                |

| M2_0               | W10     | LVCMOS18_I              | _                    | _               | DLPC964 Configuration — connect to GND                                |

|             | PIN  | able 4-1. Pili Fulic    | ACTIVE (HI | ,            |                                                                               |

|-------------|------|-------------------------|------------|--------------|-------------------------------------------------------------------------------|

| NAME        | NO.  | I/O TYPE <sup>(1)</sup> | OR LO)     | CLOCK SYSTEM | DESCRIPTION                                                                   |

| TDO_0       | AA25 | LVCMOS18_O              | _          | _            | JTAG Data out of DLPC964.<br>Connects to JTAG return TDO on<br>JTAG connector |

| TDI_0       | AB25 | LVCMOS18_I              | _          | _            | JTAG Data into DLPC964. Connects to JTAG input TDI on JTAG connector          |

| TMS_0       | W25  | LVCMOS18_I              | _          | _            | JTAG Data. Connects to JTAG<br>TMS on JTAG connector                          |

| TCK_0       | Y25  | LVCMOS18_I              | _          | _            | JTAG Clock. Connects to JTAG TCK on JTAG connector                            |

| INIT_B_0    | T10  | LVCMOS18_O              | _          | _            | DLPC964 Configuration. Pull up to 1.8V with a $4.7K\Omega$ resistor.          |

| CFGBVS_0    | U10  | LVCMOS18_I              | _          | _            | DLPC964 Configuration. Connect to GND.                                        |

| PROGRAM_B_0 | V10  | LVCMOS18_O              | _          | _            | DLPC964 Configuration. Pull up to 1.8V with a $4.7K\Omega$ resistor.          |

| DONE_0      | AB10 | LVCMOS18_O              | н          | _            | DLPC964 Configuration. Pull up to 1.8V with a $330\Omega$ resistor.           |

| K_DATA[0]   | K22  | LVDCI_18_O              | _          | CLK_K        | Bit 64 of user_k_tdata[]                                                      |

| K_DATA[1]   | K23  | LVDCI_18_O              | _          | CLK_K        | Bit 65 of user_k_tdata[]                                                      |

| K_DATA[2]   | M23  | LVDCI_18_O              | _          | CLK_K        | Bit 66 of user_k_tdata[]                                                      |

| K_VALID     | K24  | LVDCI_18_O              | _          | CLK_K        |                                                                               |

| K_DATA[3]   | L23  | LVDCI_18_O              | _          | CLK_K        | Bit 67 of user_k_tdata[]                                                      |

| CLK_K       | L24  | LVDCI_18_I              | _          | _            | K_DATA Clock input (156.25MHz)                                                |

| K_DATA[4]   | L25  | LVDCI_18_O              | _          | CLK_K        | Bit 68 of user_k_tdata[]                                                      |

| FAN_PWM     | N22  | LVDCI_18_O              | _          | _            | To DLPC964 Controller Fan connector                                           |

| TESTMUX0    | AE11 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX1    | AE13 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX2    | AE14 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX3    | AF10 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX4    | AF11 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX5    | AF13 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX6    | AF14 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX7    | AG10 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX8    | AG11 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX9    | AG12 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX10   | AG13 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX11   | AH12 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX12   | AH13 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX13   | AH14 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX14   | AJ9  | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| TESTMUX15   | AJ10 | LVDCI_18_O              | _          | _            | No connect. For access to test point output route to test via.                |

| VN_0        | Y17  | _                       | _          | _            | Connect to GND.                                                               |

| VP_0        | W18  | _                       | _          | _            | Connect to GND.                                                               |

| VREFN_0     | W17  | _                       | _          | _            | Connect to GND.                                                               |

| VREFP_0     | Y18  | _                       | _          | _            | Connect to GND.                                                               |

|           | PIN                                                                                                                                                                                                                                                                                            | VO TVDT(1)              | ACTIVE (HI | 01 001/ 01/07514 | DECORPORTION.    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|------------------|------------------|

| NAME      | NO.                                                                                                                                                                                                                                                                                            | I/O TYPE <sup>(1)</sup> | OR LO)     | CLOCK SYSTEM     | DESCRIPTION      |

| DXN_0     | AA17                                                                                                                                                                                                                                                                                           | _                       | _          | _                | Connect to GND.  |

| DXP_0     | AA18                                                                                                                                                                                                                                                                                           | _                       | _          | _                | Connect to GND.  |

| VCCADC_0  | V18                                                                                                                                                                                                                                                                                            | PWR                     | _          | _                | Connect to 1.8V. |

| VCCBATT_0 | U25                                                                                                                                                                                                                                                                                            | PWR                     | _          | _                | Connect to GND.  |

| vcco      | A12, A22, AC11, AE10, AE20,<br>AF17, AG14, AG24, AH11, AH21,<br>AJ8, AJ18, AK15, AK25, AL12,<br>AL22, AM9, AM19, AN16, AN26,<br>AP13, AP23, B9, B19, C16, C26,<br>D13, D23, E10, E20, F17, G14,<br>G24, H11, H21, J18, K15, K25,<br>L12, L22, M19, N16, P13, P23                               | PWR                     | -          | -                | Power. P1V8      |

| VCCINT    | AA12, AA16, AA22, AA24, AB11,<br>AB15, AB17, AB23, AC10, AC12,<br>AC16, AC18, AC22, AC24, AD11,<br>AD15, AD17, AD23, AD25, R10,<br>R12, R14, R16, R18, R22, R24,<br>T11, T13, T15, T17, T21, T23,<br>T25, U12, U14, U16, U18, U22,<br>U24, V11, V15, V23, W12, W16,<br>W22, W24, Y11, Y15, Y23 | PWR                     | -          | _                | Power. P1V0_CORE |

| VCCAUX    | AA14, AA20, AB13, AB21, AC14,<br>AC20, AD13, AD21, U20, V13,<br>V21, W14, W20, Y13, Y21                                                                                                                                                                                                        | PWR                     | -          | _                | Aux Power. P1V8  |

| VCCBRAM   | AB19, AD19, R20, T19, V19, Y19                                                                                                                                                                                                                                                                 | PWR                     | _          | _                | Power. P1V0_CORE |

| MGTAVCC   | AA29, AC6, AC29, AE6, AE29,<br>AG6, AG29, AJ6, AJ29, AL6,<br>AL29, AN6, AN29, C6, C29, E6,<br>E29, G6, G29, J6, J29, L6, L29,<br>N6, N29, R6, R29                                                                                                                                              | PWR                     | -          | -                | Power. P1V0_MGT  |

| MGTVCCAUX | U6, U29, W6, W29                                                                                                                                                                                                                                                                               | PWR                     | _          | _                | Aux Power. P1V8  |

| MGTAVTT   | AC2, AC33, AD3, AD32, AG2,<br>AG33, AH3, AH32, AL2, AL33,<br>AM3, AM32, C2, C33, D3, D32,<br>G2, G33, H3, H32, L2, L33, M3,<br>M32, R2, R33, T3, T32, W2,<br>W33, Y3, Y32                                                                                                                      | PWR                     | -          | -                | Power. P1V2      |

| GNDADC_0  | V17                                                                                                                                                                                                                                                                                            | GND                     | _          | _                | ADC Ground       |

| Р        | IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1. Pin Functi         | i i                  |              |                                     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|--------------|-------------------------------------|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I/O TYPE <sup>(1)</sup> | ACTIVE (HI<br>OR LO) | CLOCK SYSTEM | DESCRIPTION                         |

| GND      | NO.  A1, A2, A5, A6, A7, A17, A27, A28, A29, A30, A33, A34, A31, AA15, AA19, AA21, AA23, AA26, AA30, AA33, AA34, AB1, AB19, AA21, AA23, AB4, AB7, AB8, AB9, AB12, AB14, AB16, AB18, AB20, AB22, AB24, AB26, AB27, AB28, AB31, AB32, AC1, AC5, AC9, AC13, AC15, AC17, AC19, AC21, AC23, AC25, AC26, AC30, AC34, AD4, AD7, AD8, AD9, AD10, AD12, AD20, AD22, AD24, AD26, AD27, AD28, AD31, AE1, AE2, AE2, AE26, AE30, AE33, AE34, AF3, AF4, AF7, AF8, AF9, AF12, AF22, AF26, AF30, AF31, AF32, AC1, AC5, AC7, AC88, AC99, AC19, AC14, | GND                     |                      |              |                                     |

| RESERVED | R23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                       | _                    | _            | Pull up to 1.8V with 100Ω resistor  |

| RESERVED | R25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                       | _                    | _            | Pull down to GND with 100Ω resistor |

| RESERVED | AE12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                       | _                    | _            | Pull up to 1.8V with 100Ω resistor  |

| RESERVED | AD14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                       | _                    | _            | Pull down to GND with 100Ω resistor |

| RESERVED | G7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                       | _                    | _            | Pull up to 1.2V with 100Ω resistor  |

| RESERVED | G8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         | _                    | _            | Connect to 1.2V                     |

| RESERVED | G27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                       | _                    | _            | Connect to 1.2V                     |

| RESERVED | G28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                       | _                    | _            | Pull up to 1.2V with 100Ω resistor  |

| PIN    |                                                                   | 4-1. PIN FUNCTIONS (CON |        |              |             |

|--------|-------------------------------------------------------------------|-------------------------|--------|--------------|-------------|

| NAME   | NO.                                                               | I/O TYPE <sup>(1)</sup> | OR LO) | CLOCK SYSTEM | DESCRIPTION |

| UNUSED | A8, A9, A10, A11, A13, A14,<br>A15, A16, A18, A19, A20, A21,      |                         |        |              |             |

|        | A23, A24, AC3, AC4, AC7, AC8,                                     |                         |        |              |             |

|        | AC27, AC28, AC31, AC32, AD5,                                      |                         |        |              |             |

|        | AD6, AD16, AD18, AD29, AD30,                                      |                         |        |              |             |

|        | AE3, AE4, AE7, AE8, AE16,                                         |                         |        |              |             |

|        | AE17, AE18, AE19, AE21, AE22,<br>AE23, AE24, AE27, AE28, AE31,    |                         |        |              |             |

|        | AE32, AF5, AF6, AF15, AF16,                                       |                         |        |              |             |

|        | AF18, AF19, AF20, AF21, AF23,                                     |                         |        |              |             |

|        | AF24, AF25, AF29, AF30, AG3,                                      |                         |        |              |             |

|        | AG4, AG15, AG16, AG17, AG18,<br>AG20, AG21, AG22, AG23,           |                         |        |              |             |

|        | AG25, AG31, AG32, AH5, AH6,                                       |                         |        |              |             |

|        | AH10, AH15, AH17, AH18, AH19,                                     |                         |        |              |             |

|        | AH20, AH22, AH23, AH24, AH25,                                     |                         |        |              |             |

|        | AH29, AH30, AJ11, AJ15, AJ16,<br>AJ17, AJ19, AJ20, AJ21, AJ22,    |                         |        |              |             |

|        | AJ24, AJ25, AJ26, AJ27, AK5,                                      |                         |        |              |             |

|        | AK6, AK11, AK16, AK17, AK18,                                      |                         |        |              |             |

|        | AK19, AK21, AK22, AK23, AK24,                                     |                         |        |              |             |

|        | AK26, AK27, AK29, AK30, AL3,                                      |                         |        |              |             |

|        | AL4, AL8, AL11, AL13, AL15,<br>AL16, AL18, AL19, AL20, AL21,      |                         |        |              |             |

|        | AL23, AL24, AL25, AL26, AL31,                                     |                         |        |              |             |

|        | AL32, AM5, AM6, AM11, AM15,                                       |                         |        |              |             |

|        | AM16, AM17, AM18, AM20,                                           |                         |        |              |             |

|        | AM21, AM22, AM23, AM25,<br>AM26, AM27, AM29, AM30,                |                         |        |              |             |

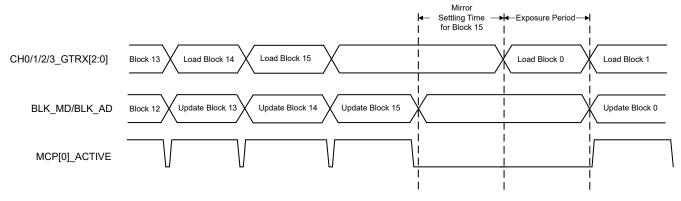

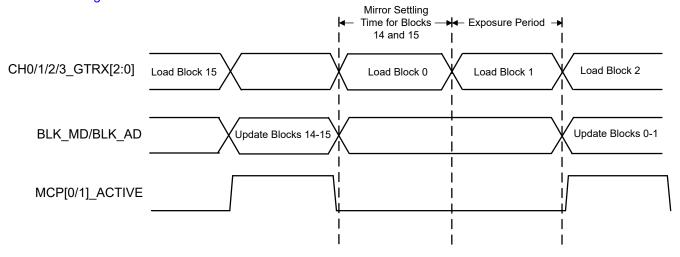

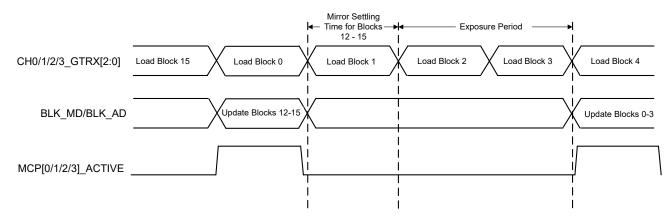

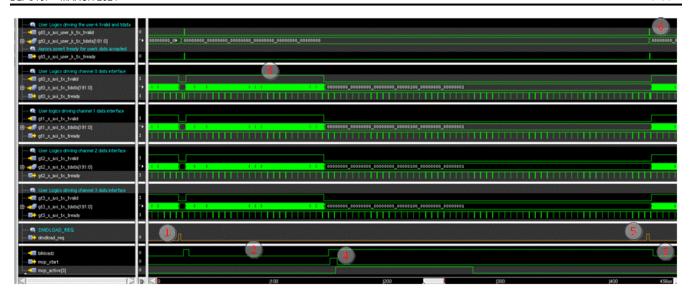

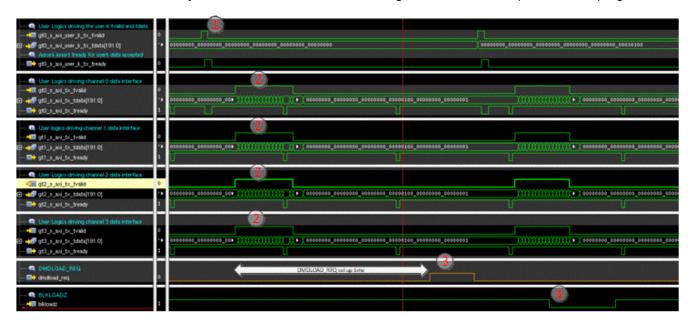

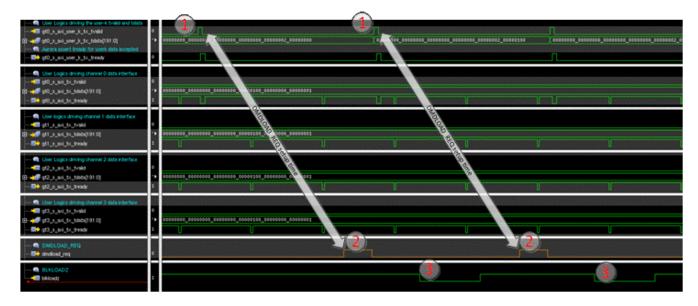

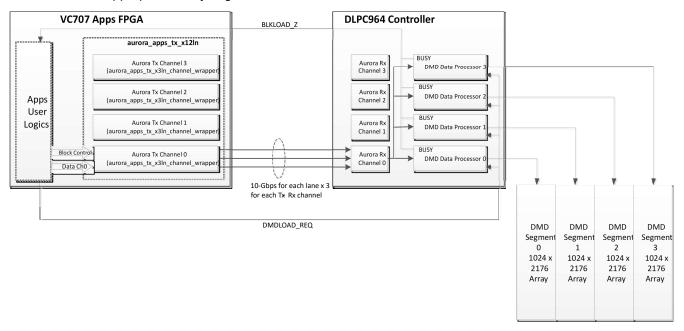

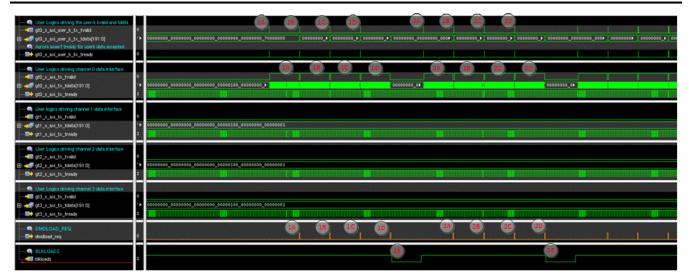

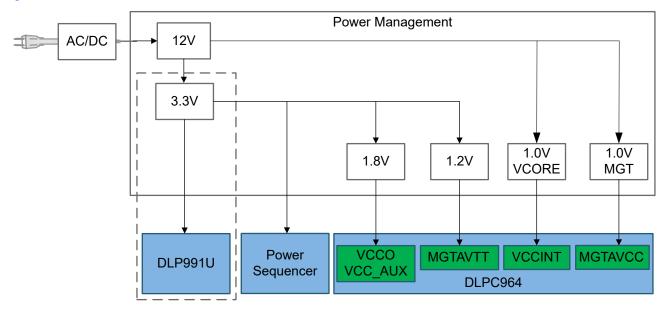

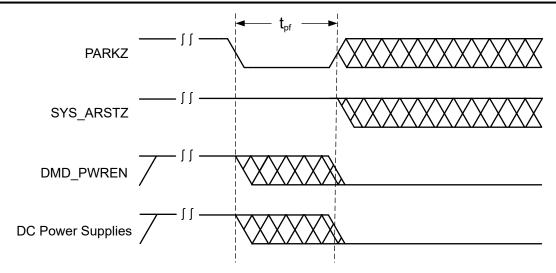

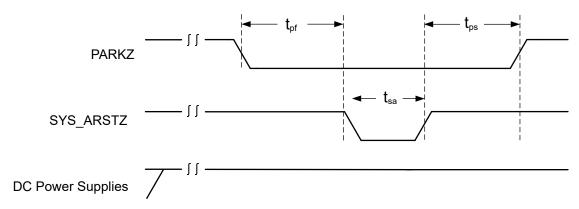

|        | AN13, AN15, AN17, AN18, AN19,                                     |                         |        |              |             |