SBAS326E-JUNE 2004-REVISED JANUARY 2009

# 4-Channel, 12-Bit, 40MSPS Analog-to-Digital Converter with Serial LVDS Interface

### **FEATURES**

www.ti.com

- Maximum Sample Rate: 40MSPS

- 12-Bit Resolution

- No Missing Codes

- Total Power Dissipation: Internal Reference: 584mW External Reference: 518mW

- CMOS Technology

- Simultaneous Sample-and-Hold

- 70.5dBFS SNR at 10MHz IF

- 3.3V Digital/Analog Supply

- Serialized LVDS Outputs

- Integrated Frame and Bit Patterns

- Option to Double LVDS Clock Output Currents

- Four Current Modes for LVDS

- Pin- and Format-Compatible Family

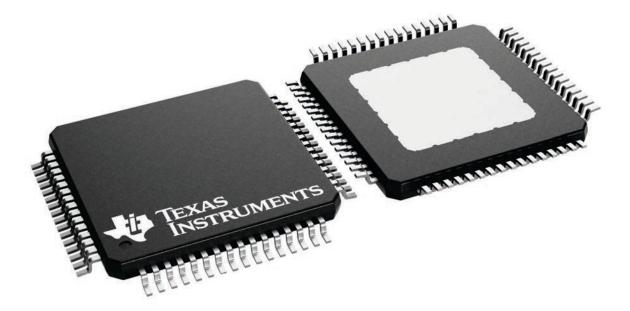

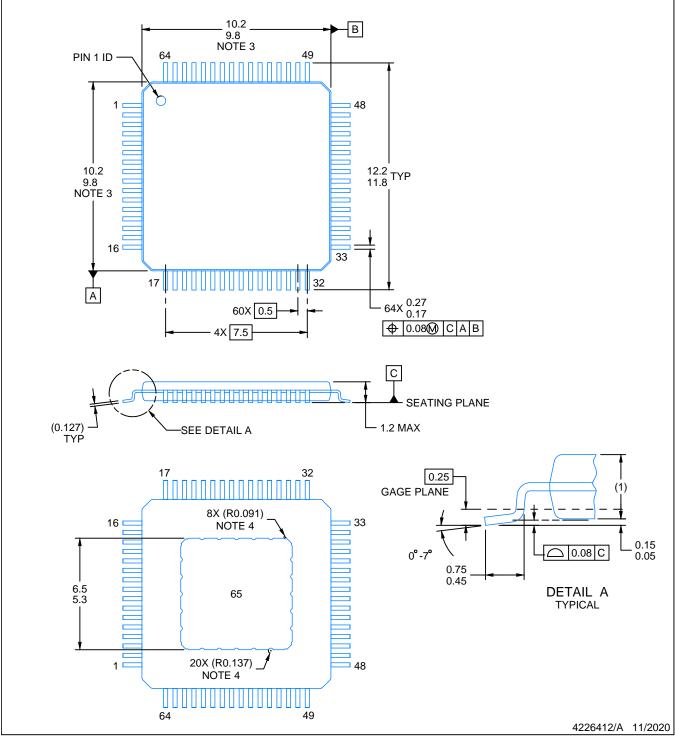

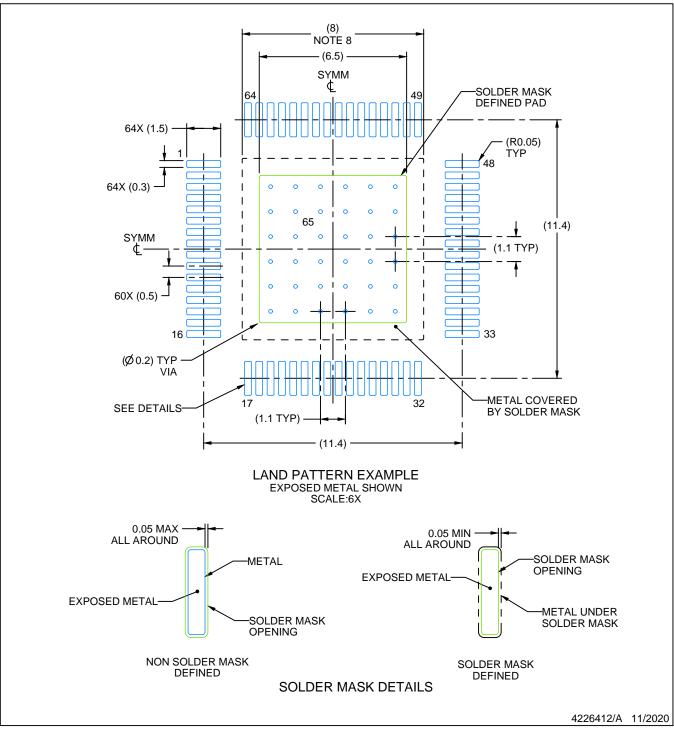

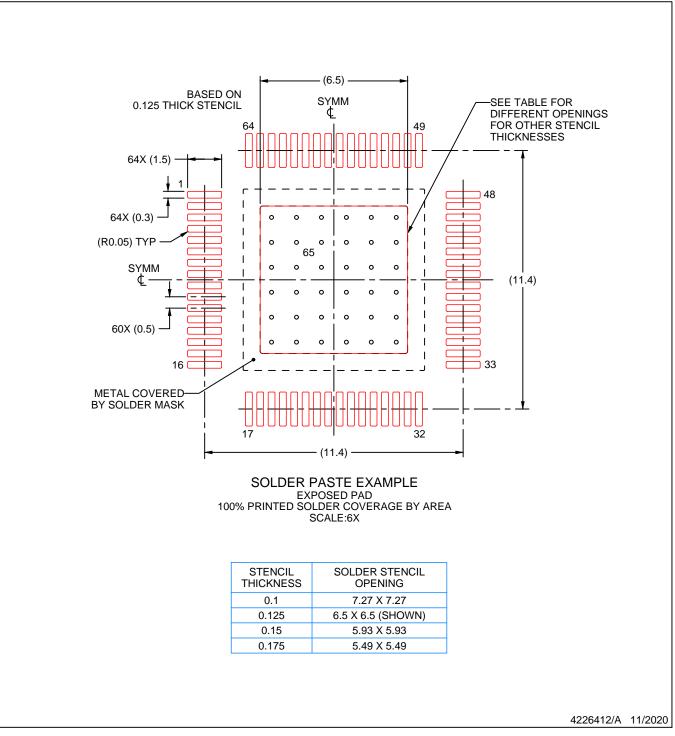

- HTQFP-64 PowerPAD<sup>™</sup> Package

#### **APPLICATIONS**

- Portable Ultrasound Systems

- Tape Drives

- Test Equipment

- Optical Networking

- Communications

### DESCRIPTION

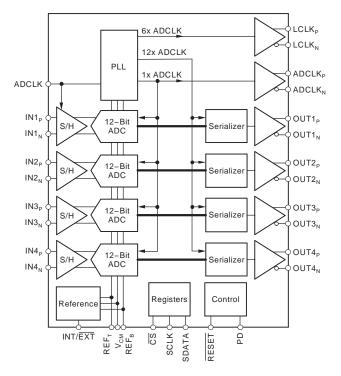

The ADS5240 is a high-performance, 40MSPS, 4-channel analog-to-digital converter (ADC). Internal references are provided, simplifying system design requirements. Low power consumption allows for the highest of system integration densities. Serial LVDS (low-voltage differential signaling) outputs reduce the number of interface lines and package size.

#### **RELATED PRODUCTS**

| RESOLUTION<br>MODEL (BITS) |    | SAMPLE RATE<br>(MSPS) | CHANNELS |

|----------------------------|----|-----------------------|----------|

| ADS5242                    | 12 | 65                    | 4        |

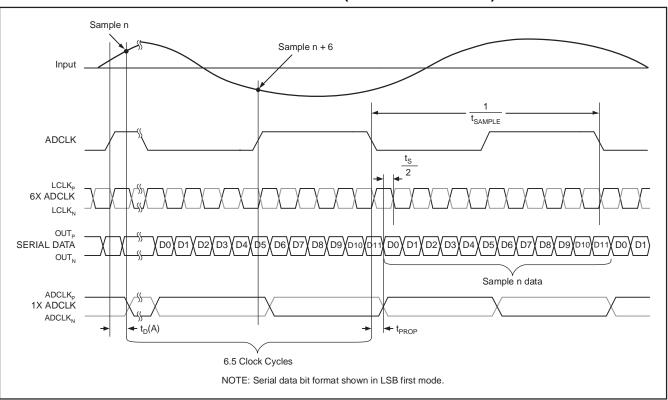

An integrated phase lock loop (PLL) multiplies the incoming ADC sampling clock by a factor of 12. This high-frequency LVDS clock is used in the data serialization and transmission process. The word output of each internal ADC is serialized and transmitted either MSB or LSB first. In addition to the four data outputs, a bit clock and a word clock are also transmitted. The bit clock is at 6x the speed of the sampling clock, whereas the word clock is at the same speed of the sampling clock.

The ADS5240 provides internal references, or can optionally be driven with external references. Best performance can be achieved through the internal reference mode.

The device is available in an HTQFP-64 PowerPAD package and is specified over a -40°C to +85°C operating range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### SBAS326E-JUNE 2004-REVISED JANUARY 2009

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

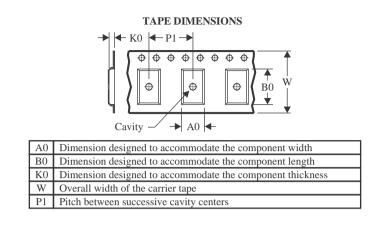

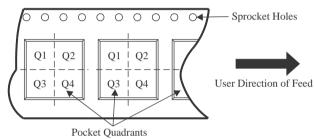

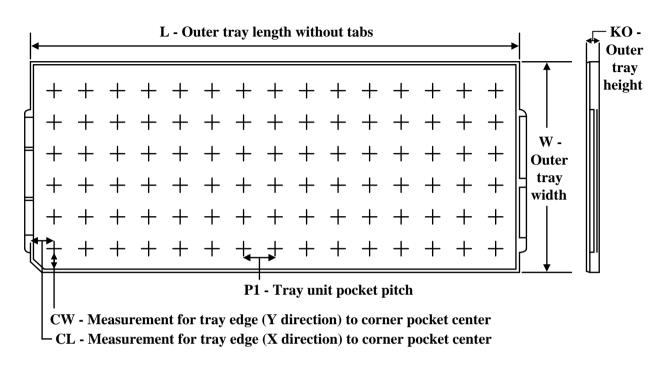

#### **ORDERING INFORMATION**<sup>(1)</sup>

| PRODUCT | PACKAGE-LEAD <sup>(2)</sup> | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|-----------------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| ADS5240 | HTQFP-64                    | PAP                   | –40°C to +85°C                    | ADS5240IPAP        | ADS5240IPAP        | Tray, 160                    |

| AD35240 |                             | FAF                   | -40 C 10 +65 C                    | AD35240IFAF        | ADS5240IPAPT       | Tape and Reel, 1000          |

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Thermal pad size: 5.29mm × 5.29mm (min), 6.50mm × 6.50mm (max).

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Supply Voltage Range, AVDD                           | -0.3V to +3.8V                                     |

|------------------------------------------------------|----------------------------------------------------|

| Supply Voltage Range, LVDD                           | -0.3V to +3.8V                                     |

| Voltage Between AVSS and LVSS                        | -0.3V to +0.3V                                     |

| Voltage Between AVDD and LVDD                        | -0.3V to +0.3V                                     |

| Voltage Applied to External REF Pins                 | -0.3V to +2.4V                                     |

| All LVDS Data and Clock Outputs                      | -0.3V to +2.4V                                     |

| Analog Input Pins <sup>(2)</sup>                     | -0.3V to min. [3.3V, (AVDD + 0.3V)]                |

| Digital Input Pins, Set 1 (pins 54, 61-63)           | -0.3V to min. [3.9V, (AVDD + 0.3V)] <sup>(3)</sup> |

| Digital Input Pins, Set 2 (pins 12, 37)              | -0.3V to min. [3.9V, (LVDD + 0.3V)] <sup>(3)</sup> |

| Operating Free-Air Temperature Range, T <sub>A</sub> | –40°C to +85°C                                     |

| Lead Temperature, 1.6mm (1/16" from case for 10s)    | +260°C                                             |

| Junction Temperature                                 | +105°C                                             |

| Storage Temperature Range                            | –65°C to +150°C                                    |

|                                                      |                                                    |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

(2) The dc voltage applied on the input pins should not go below –0.3V. Also, the dc voltage should be limited to the lower of either 3.3V or (AVDD + 0.3V). If the input can go higher than +3.3V, then a resistor greater than or equal to 25Ω should be added in series with each of the input pins. Also, the duty cycle of the overshoot beyond +3.3V should be limited. The overshoot duty cycle can be defined either as a percentage of the time of overshoot over a clock period, or over the entire device lifetime. For a peak voltage between +3.3V and +3.5V, a duty cycle up to 10% is acceptable. For a peak voltage between +3.5V and +3.7V, the overshoot duty cycle should not exceed 1%. Any overshoot beyond +3.7V should be restricted to less than 0.1% duty cycle, and never exceed +3.9V.

(3) It is recommended to use a series resistor of  $1k\Omega$  or greater if the digital input pins are tied to AVDD or LVDD.

#### **RECOMMENDED OPERATING CONDITIONS**

|                                                                       |       | ADS5240            |       |       |

|-----------------------------------------------------------------------|-------|--------------------|-------|-------|

|                                                                       | MIN   | TYP                | MAX   | UNITS |

| SUPPLIES AND REFERENCES                                               |       |                    |       |       |

| Analog Supply Voltage, AVDD                                           | 3.0   | 3.3                | 3.6   | V     |

| Output Driver Supply Voltage, LVDD                                    | 3.0   | 3.3                | 3.6   | V     |

| REF <sub>T</sub> — External Reference Mode                            | 1.825 | 1.95               | 2.0   | V     |

| REF <sub>B</sub> — External Reference Mode                            | 0.9   | 0.95               | 1.075 | V     |

| REFCM = $(REF_T + REF_B)/2 - External Reference Mode(1)$              |       | $V_{CM} \pm 50 mV$ |       | V     |

| Reference = $(REF_T - REF_B)$ – External Reference Mode               | 0.75  | 1.0                | 1.1   | V     |

| Analog Input Common-Mode Range <sup>(1)</sup>                         |       | $V_{CM} \pm 50 mV$ |       | V     |

| CLOCK INPUT AND OUTPUTS                                               |       |                    |       |       |

| ADCLK Input Sample Rate (low-voltage TTL)                             | 20    |                    | 40    | MSPS  |

| ADCLK Duty Cycle                                                      | 45    | 50                 | 55    | %     |

| Low-Level Voltage Clock Input                                         |       |                    | 0.6   | V     |

| High-Level Voltage Clock Input                                        | 2.2   |                    |       | V     |

| ADCLK <sub>P</sub> and ADCLK <sub>N</sub> Outputs (LVDS)              | 20    |                    | 40    | MHz   |

| LCLK <sub>P</sub> and LCLK <sub>N</sub> Outputs (LVDS) <sup>(2)</sup> | 120   |                    | 240   | MHz   |

| Operating Free-Air Temperature, T <sub>A</sub>                        | -40   |                    | +85   | °C    |

| Thermal Characteristics:                                              |       |                    |       |       |

| $\theta_{JA}$                                                         |       | 20.4               |       | °C/W  |

| θJC                                                                   |       | 14.5               |       | °C/W  |

(1) These voltages need to be set to 1.45V  $\pm$  50mV if they are derived independent of V\_CM. (2) 6  $\times$  ADCLK.

SBAS326E-JUNE 2004-REVISED JANUARY 2009

### **ELECTRICAL CHARACTERISTICS**

$T_{MIN} = -40^{\circ}$ C and  $T_{MAX} = +85^{\circ}$ C. Typical values are at  $T_A = +25^{\circ}$ C, clock frequency = maximum specified, 50% clock duty cycle, AVDD = 3.3V, LVDD = 3.3V, transformer coupled inputs, -1dBFS,  $I_{SET} = 56.2$ k $\Omega$ , internal voltage reference, and LVDS buffer current at 3.5mA per channel, unless otherwise noted. All values are applicable after the device has been reset.

|                   |                                                 |                         | ADS5240 |                        |       |        |

|-------------------|-------------------------------------------------|-------------------------|---------|------------------------|-------|--------|

|                   | PARAMETER                                       | TEST CONDITIONS         | MIN     | ТҮР                    | MAX   | UNITS  |

| DC ACC            | URACY                                           |                         |         |                        |       |        |

|                   | No Missing Codes                                |                         |         | Tested                 |       |        |

| DNL               | Differential Nonlinearity                       | f <sub>IN</sub> = 5MHz  | -0.9    | ±0.4                   | +0.9  | LSB    |

| INL               | Integral Nonlinearity                           | f <sub>IN</sub> = 5MHz  | -2.0    | ±0.75                  | +2.0  | LSB    |

|                   | Offset Error <sup>(1)</sup>                     |                         | -0.75   | ±0.2                   | +0.75 | %FS    |

|                   | Offset Temperature Coefficient                  |                         |         | 14                     |       | ppm/°C |

|                   | Fixed Attenuation in Channel <sup>(2)</sup>     |                         |         | 1.5                    |       | %FS    |

|                   | Fixed Attenuation Matching Across Channels      |                         |         | 0.01                   | 0.2   | dB     |

|                   | Gain Error/Reference Error <sup>(3)</sup>       | $VREF_T - VREF_B$       | -5      | ±1.0                   | +5    | %FS    |

|                   | Gain Error Temperature Coefficient              |                         |         | ±20                    |       | ppm/°C |

| POWER             | REQUIREMENTS <sup>(4)</sup>                     |                         |         |                        |       |        |

| Internal I        | Reference                                       |                         |         |                        |       |        |

|                   | Power Dissipation                               | Analog Only (AVDD)      |         | 452                    | 495   | mW     |

|                   |                                                 | Output Driver (LVDD)    |         | 132                    | 155   | mW     |

|                   | Total Power Dissipation                         |                         |         | 584                    | 650   | mW     |

| External          | Reference                                       |                         |         |                        |       |        |

|                   | Power Dissipation                               | Analog Only (AVDD)      |         | 386                    |       | mW     |

|                   |                                                 | Output Driver (LVDD)    |         | 132                    |       | mW     |

|                   | Total Power Dissipation                         |                         |         | 518                    |       | mW     |

| Total Po          | wer-Down                                        | Clock Running           |         | 95                     |       | mW     |

| REFERE            | NCE VOLTAGES                                    |                         |         |                        |       |        |

| $VREF_T$          | Reference Top (internal)                        |                         | 1.9     | 1.95                   | 2.0   | V      |

| $VREF_B$          | Reference Bottom (internal)                     |                         | 0.9     | 0.95                   | 1.0   | V      |

| V <sub>CM</sub>   | Common-Mode Voltage                             |                         | 1.4     | 1.45                   | 1.5   | V      |

|                   | V <sub>CM</sub> Output Current <sup>(5)</sup>   | ±50mV Change in Voltage |         | ±2.0                   |       | mA     |

| $VREF_T$          | Reference Top (external)                        |                         | 1.825   | 1.95                   | 2.0   | V      |

| VREF <sub>B</sub> | Reference Bottom (external)                     |                         | 0.9     | 0.95                   | 1.075 | V      |

|                   | External Reference Common-Mode                  |                         |         | V <sub>CM</sub> ± 50mV |       | V      |

|                   | External Reference Input Current <sup>(6)</sup> |                         |         | 0.5                    |       | mA     |

(1) Offset error is the deviation of the average code with a -1dBFS coherent sinusoid input from mid-code (2048).

(2) Fixed attenuation in the channel arises due to a fixed attenuation in the sample-and-hold amplifier. When the differential voltage at the analog input pins are changed from -V<sub>REF</sub> to +V<sub>REF</sub>, the swing of the output code is expected to deviate from the full-scale code (4096LSB) by the extent of this fixed attenuation. NOTE: V<sub>REF</sub> is defined as (VREF<sub>T</sub> - VREF<sub>B</sub>).

(3) The reference voltages are trimmed at production so that (VREF<sub>T</sub> - VREF<sub>B</sub>) is within ± 25mV of the ideal value of 1V. This specification does not include fixed attenuation.

(4) Supply current can be calculated from dividing the power dissipation by the supply voltage of 3.3V.

(5)  $V_{CM}$  provides the common-mode current for the inputs of all four channels when the inputs are ac-coupled. The  $V_{CM}$  output current specified is the additional drive of the  $V_{CM}$  buffer if loaded externally.

(6) Average current drawn from the reference pins in the external reference mode.

**ELECTRICAL CHARACTERISTICS (continued)**

$T_{MIN} = -40^{\circ}$ C and  $T_{MAX} = +85^{\circ}$ C. Typical values are at  $T_A = +25^{\circ}$ C, clock frequency = maximum specified, 50% clock duty cycle, AVDD = 3.3V, LVDD = 3.3V, transformer coupled inputs, -1dBFS,  $I_{SET} = 56.2$ k $\Omega$ , internal voltage reference, and LVDS buffer current at 3.5mA per channel, unless otherwise noted. All values are applicable after the device has been reset.

|                                               |                                   |        | ADS5240                |                    |                 |

|-----------------------------------------------|-----------------------------------|--------|------------------------|--------------------|-----------------|

| PARAMETER                                     | TEST CONDITIONS                   | MIN    | TYP                    | MAX                | UNITS           |

| ANALOG INPUT                                  |                                   |        |                        |                    |                 |

| Differential Input Capacitance                |                                   |        | 4.0                    |                    | pF              |

| Analog Input Common-Mode Range                |                                   |        | $V_{CM} \pm 50$        |                    | mV              |

| Differential Input Voltage Range              | Internal Reference                |        | 2.03                   |                    | V <sub>PP</sub> |

|                                               | External Reference                | 2.03 > | (VREF <sub>T</sub> – V | REF <sub>B</sub> ) | V <sub>PP</sub> |

| Voltage Overhead Recovery Time <sup>(7)</sup> |                                   |        | 3.0                    |                    | CLK Cycles      |

| Input Bandwidth                               | –3dBFS, 25Ω Series<br>Resistances |        | 300                    |                    | MHz             |

| DIGITAL DATA INPUTS                           |                                   |        |                        |                    |                 |

| V <sub>IH</sub> High-Level Input Voltage      |                                   | 2.2    |                        |                    | V               |

| VIL Low-Level Input Voltage                   |                                   |        |                        | 0.6                | V               |

| C <sub>IN</sub> Input Capacitance             |                                   |        | 3.0                    |                    | pF              |

| DIGITAL DATA OUTPUTS                          |                                   |        |                        |                    |                 |

| Data Format                                   |                                   | Stra   | ight Offset B          | inary              |                 |

| Data Bit Rate                                 |                                   | 240    |                        | 480                | Mbps            |

| SERIAL INTERFACE                              |                                   |        |                        |                    |                 |

| SCLK Serial Clock Input Frequency             |                                   |        |                        | 20                 | MHz             |

(7) A differential ON/OFF pulse is applied to the ADC input. The differential amplitude of the pulse in its ON (high) state is twice the full-scale range of the ADC, while the differential amplitude of the pulse in its OFF (low) state is zero. The overload recovery time of the ADC is measured as the time required by the ADC output code to settle within 1% of full-scale, as measured from its mid-code value when the pulse is switched from ON (high) to OFF (low).

#### **REFERENCE SELECTION**

| MODE                                                                      | INT/EXT | DESCRIPTION                                                                                                                                                                                    |

|---------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Reference; FSR = $2.03V_{PP}$                                    | 1       | Default with internal pull-up.                                                                                                                                                                 |

| External Reference; FSR = 2.03 × (VREF <sub>T</sub> – VREF <sub>B</sub> ) | 0       | Internal reference is powered down. The common-mode voltage of the external reference should be within 50mV of V <sub>CM</sub> . V <sub>CM</sub> is derived from the internal bandgap voltage. |

SBAS326E-JUNE 2004-REVISED JANUARY 2009

#### www.ti.com

#### **AC CHARACTERISTICS**

$T_{MIN} = -40^{\circ}$ C and  $T_{MAX} = +85^{\circ}$ C. Typical values are at  $T_A = +25^{\circ}$ C, clock frequency = maximum specified, 50% clock duty cycle, AVDD = 3.3V, LVDD = 3.3V, -1dBFS, I<sub>SET</sub> = 56.2k $\Omega$ , internal voltage reference, and LVDS buffer current at 3.5mA per channel, unless otherwise noted.

| PARAMETER                                     | CONDITIONS                                                                                                | MIN | MIN TYP |  | UNITS |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|---------|--|-------|

| DYNAMIC CHARACTERISTICS                       |                                                                                                           |     |         |  |       |

|                                               | f <sub>IN</sub> = 1MHz                                                                                    |     | 87      |  | dBc   |

| SFDR Spurious-Free Dynamic Rang               | e f <sub>IN</sub> = 5MHz                                                                                  | 78  | 85      |  | dBc   |

|                                               | f <sub>IN</sub> = 10MHz                                                                                   |     | 85      |  | dBc   |

|                                               | f <sub>IN</sub> = 1MHz                                                                                    |     | 95      |  | dBc   |

| HD <sub>2</sub> 2nd-Order Harmonic Distortio  | f <sub>IN</sub> = 5MHz                                                                                    | 85  | 95      |  | dBc   |

|                                               | f <sub>IN</sub> = 10MHz                                                                                   |     | 90      |  | dBc   |

|                                               | f <sub>IN</sub> = 1MHz                                                                                    |     | 87      |  | dBc   |

| HD <sub>3</sub> 3rd-Order Harmonic Distortior | f <sub>IN</sub> = 5MHz                                                                                    | 78  | 85      |  | dBc   |

|                                               | f <sub>IN</sub> = 10MHz                                                                                   |     | 85      |  | dBc   |

|                                               | f <sub>IN</sub> = 1MHz                                                                                    |     | 70.5    |  | dBFS  |

| SNR Signal-to-Noise Ratio                     | f <sub>IN</sub> = 5MHz                                                                                    | 68  | 70.5    |  | dBFS  |

|                                               | f <sub>IN</sub> = 10MHz                                                                                   |     | 70      |  | dBFS  |

|                                               | f <sub>IN</sub> = 1MHz                                                                                    |     | 70      |  | dBFS  |

| SINAD Signal-to-Noise and Distortion          | f <sub>IN</sub> = 5MHz                                                                                    | 67  | 70      |  | dBFS  |

|                                               | f <sub>IN</sub> = 10MHz                                                                                   |     | 69.5    |  | dBFS  |

| ENOB Effective Number of Bits                 | f <sub>IN</sub> = 5MHz                                                                                    |     | 11.3    |  | Bits  |

| Crosstalk                                     | 5MHz Full-Scale Signal Applied to 3 Channels;<br>Measurement Taken on the Channel with No Input<br>Signal |     | -90     |  | dBc   |

| IMD3 Two-Tone, Third-Order                    | f <sub>1</sub> = 9.5MHz at −7dBFS                                                                         |     | 00      |  | dBc   |

| Intermodulation Distortion                    | $f_2 = 10.2MHz$ at $-7dBFS$                                                                               |     | -88     |  |       |

LVDS DIGITAL DATA AND CLOCK OUTPUTS

Test conditions at  $I_0 = 3.5$ mA,  $R_{LOAD} = 100\Omega$ , and  $C_{LOAD} = 6$ pF.  $I_0$  refers to the current setting for the LVDS buffer.  $R_{LOAD}$  is the differential load resistance between the LVDS pair.  $C_{LOAD}$  is the effective single-ended load capacitance between each of the LVDS pins and ground.  $C_{LOAD}$  includes the receiver input parasitics as well as the routing parasitics. Measurements are done with a transmission line of 100 $\Omega$  characteristic impedance between the device and the load. All LVDS specifications are characterized, but not tested at production. LCLKOUT refers to (LCLK<sub>P</sub> – LCLK<sub>N</sub>); ADCLKOUT refers to (ADCLK<sub>P</sub> – ADCLK<sub>N</sub>); DATA OUT refers to (OUT<sub>P</sub> – OUT<sub>N</sub>); and ADCLK refers to the input sampling clock.

| PARAMETER                                                          | CONDITIONS                                                       | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------------------------|------------------------------------------------------------------|-------|------|-------|-------|

| DC SPECIFICATIONS <sup>(1)</sup>                                   |                                                                  |       |      |       |       |

| $V_{OH}$ Output Voltage High, OUT <sub>P</sub> or OUT <sub>N</sub> | $R_{LOAD} = 100\Omega \pm 1\%$ ; See LVDS Timing Diagram, Page 8 | 1265  | 1365 | 1465  | mV    |

| $V_{OL}$ Output Voltage Low, $OUT_P$ or $OUT_N$                    | $R_{LOAD} = 100\Omega \pm 1\%$                                   | 940   | 1040 | 1140  | mV    |

| V <sub>OD</sub>   Output Differential Voltage                      | $R_{LOAD} = 100\Omega \pm 1\%$                                   | 275   | 325  | 375   | mV    |

| V <sub>OS</sub> Output Offset Voltage <sup>(2)</sup>               | $R_{LOAD} = 100\Omega \pm 1\%$ ; See LVDS Timing Diagram, Page 8 | 1.1   | 1.2  | 1.3   | V     |

| R <sub>O</sub> Output Impedance, Differential                      | Normal Operation                                                 |       | 13   |       | kΩ    |

| Ro Output Impedance, Differential                                  | Power-Down                                                       |       | 20   |       | kΩ    |

| C <sub>O</sub> Output Capacitance <sup>(3)</sup>                   |                                                                  |       | 4    |       | pF    |

| $ \Delta V_{OD} $ Change in $ V_{OD} $ Between 0 and 1             | $R_{LOAD} = 100\Omega \pm 1\%$                                   |       |      | 10    | mV    |

| $\Delta V_{OS}$ Change Between 0 and 1                             | $R_{LOAD} = 100\Omega \pm 1\%$                                   |       |      | 25    | mV    |

| ISOUT Output Short-Circuit Current                                 | Drivers Shorted to Ground                                        |       |      | 40    | mA    |

| ISOUT <sub>NP</sub> Output Current                                 | Drivers Shorted Together                                         |       |      | 12    | mA    |

| DRIVER AC SPECIFICATIONS                                           |                                                                  |       |      |       |       |

| ADCLKOUT Clock Duty Cycle <sup>(4)</sup>                           |                                                                  | 45    | 50   | 55    | %     |

| LCLKOUT Duty Cycle <sup>(4)</sup>                                  |                                                                  | 44    | 50   | 56    | %     |

| Data Setup Time <sup>(5)(6)</sup>                                  |                                                                  | 0.7   |      |       | ns    |

| Data Hold Time <sup>(6)(7)</sup>                                   |                                                                  | 0.61  |      |       | ns    |

| LVDS Outputs Rise/Fall Time <sup>(8)</sup>                         | I <sub>O</sub> = 2.5mA                                           |       | 400  |       | ps    |

|                                                                    | I <sub>O</sub> = 3.5mA                                           | 180   | 300  | 500   | ps    |

|                                                                    | I <sub>O</sub> = 4.5mA                                           |       | 230  |       | ps    |

|                                                                    | I <sub>O</sub> = 6.0mA                                           |       | 180  |       | ps    |

| LCLKOUT Rising Edge to ADCLKOUT Rising Edge <sup>(9)</sup>         |                                                                  | 0.74  | 1.04 | 1.34  | ns    |

| ADCLKOUT Rising Edge to LCLKOUT Falling Edge <sup>(9)</sup>        |                                                                  | 0.74  | 1.04 | 1.34  | ns    |

| ADCLKOUT Rising Edge to DATA OUT Transition <sup>(9)</sup>         |                                                                  | -0.35 | 0    | +0.35 | ns    |

(1) The dc specifications refer to the condition where the LVDS outputs are not switching, but are permanently at a valid logic level 0 or 1.

(2)  $V_{OS}$  refers to the common-mode of OUT<sub>P</sub> and OUT<sub>N</sub>.

(3) Output capacitance inside the device, from either  $OUT_P$  or  $OUT_N$  to ground.

(4) Measured between zero crossings.

(5) DATA OUT ( $OUT_P - OUT_N$ ) crossing zero to LCLKOUT (LCLK<sub>P</sub> - LCLK<sub>N</sub>) crossing zero.

(6) Data setup and hold time accounts for data-dependent skews, channel-to-channel mismatches, as well as effects of clock jitter within the device.

(7) LCLKOUT crossing zero to DATA OUT crossing zero.

(8) Measured from -100mV to +100mV on the differential output for rise time, and +100mV to -100mV for fall time.

(9) Measured between zero crossings.

#### SWITCHING CHARACTERISTICS

$T_{MIN} = -40^{\circ}C$  and  $T_{MAX} = +85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , clock frequency = maximum specified, 50% clock duty cycle, AVDD = 3.3V, LVDD = 3.3V, -1dBFS,  $I_{SET} = 56.2k\Omega$ , internal voltage reference, and LVDS buffer current at 3.5mA per channel, unless otherwise noted.

|                           | PARAMETER                        | CONDITIONS | MIN | TYP | MAX | UNITS  |

|---------------------------|----------------------------------|------------|-----|-----|-----|--------|

| SWITCHING SP              | ECIFICATIONS                     |            |     |     |     |        |

|                           | t <sub>SAMPLE</sub>              |            | 25  |     | 50  | ns     |

| t <sub>D</sub> (A)        | Aperture Delay <sup>(1)</sup>    |            | 2   | 4   | 6.5 | ns     |

|                           | Aperture Jitter (uncertainty)    |            |     | 1   |     | ps     |

| t <sub>D</sub> (pipeline) | Latency                          |            |     | 6.5 |     | Cycles |

| t <sub>PROP</sub>         | Propagation Delay <sup>(2)</sup> |            | 3   | 4.8 | 6.5 | ns     |

(1) Rising edge of ADCLK to actual instant when data is sampled within the ADC.

(2) Falling edge of ADCLK to zero-crossing of rising edge of ADCLKOUT.

# ADS5240

### TEXAS INSTRUMENTS

www.ti.com

SBAS326E-JUNE 2004-REVISED JANUARY 2009

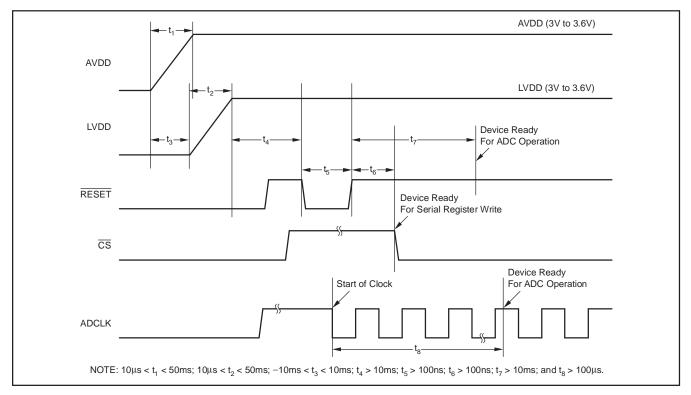

#### **RECOMMENDED POWER-UP SEQUENCING AND RESET TIMING**

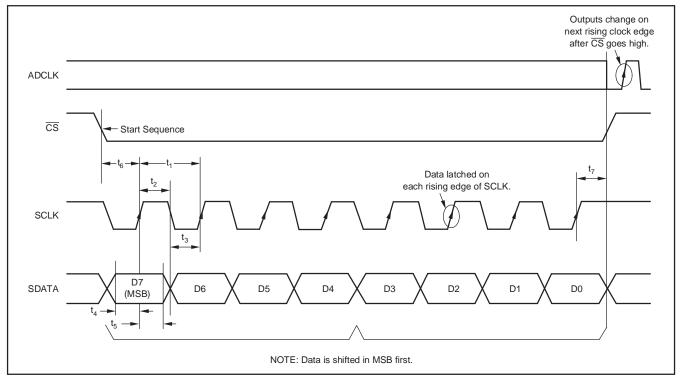

### LVDS TIMING DIAGRAM (PER ADC CHANNEL)

### LVDS TIMING DIAGRAM (PER ADC CHANNEL) (continued)

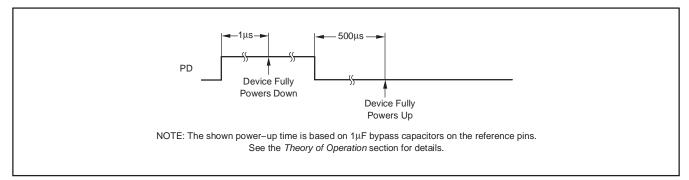

#### **POWER-DOWN TIMING**

#### SERIAL INTERFACE TIMING

| PARAMETER      | DESCRIPTION             | MIN | ТҮР | MAX | UNIT |

|----------------|-------------------------|-----|-----|-----|------|

| t <sub>1</sub> | Serial CLK Period       | 50  |     |     | ns   |

| t <sub>2</sub> | Serial CLK High Time    | 20  |     |     | ns   |

| t <sub>3</sub> | Serial CLK Low Time     | 20  |     |     | ns   |

| t <sub>4</sub> | Minimum Data Setup Time | 5   |     |     | ns   |

| t <sub>5</sub> | Minimum Data Hold Time  | 5   |     |     | ns   |

| t <sub>6</sub> | CS Fall to SCLK Rise    | 8   |     |     | ns   |

| t <sub>7</sub> | SCLK Rise to CS Rise    | 8   |     |     | ns   |

|    |     |      |    |    | S  | ERIAL |    | RFACE REGISTERS                             |                                                    |

|----|-----|------|----|----|----|-------|----|---------------------------------------------|----------------------------------------------------|

|    | ADD | RESS |    |    | DA | TA    |    | DESCRIPTION                                 | REMARKS                                            |

| D7 | D6  | D5   | D4 | D3 | D2 | D1    | D0 |                                             |                                                    |

| 0  | 0   | 0    | 0  |    |    |       |    | LVDS BUFFERS (Register 0)                   | All Data Outputs                                   |

|    |     |      |    | 0  | 0  |       |    | Normal ADC Output                           | (default after reset)                              |

|    |     |      |    | 0  | 1  |       |    | Deskew Pattern                              |                                                    |

|    |     |      |    | 1  | 0  |       |    | Sync Pattern                                | Patterns Get Reversed in MSB<br>First Mode of LVDS |

|    |     |      |    | 1  | 1  |       |    | Custom Pattern                              |                                                    |

|    |     |      |    |    |    | 0     | 0  | Output Current in LVDS = 3.5mA              | (default after reset)                              |

|    |     |      |    |    |    | 0     | 1  | Output Current in LVDS = 2.5mA              |                                                    |

|    |     |      |    |    |    | 1     | 0  | Output Current in LVDS = 4.5mA              |                                                    |

|    |     |      |    |    |    | 1     | 1  | Output Current in LVDS = 6.0mA              |                                                    |

| 0  | 0   | 0    | 1  |    |    |       |    | CLOCK CURRENT (Register 1)                  |                                                    |

|    |     |      |    | 0  | Х  | Х     | 0  | Default LVDS Clock Output Current           | I <sub>OUT</sub> = 3.5mA (default)                 |

|    |     |      |    | 0  | х  | Х     | 1  | 2x LVDS Clock Output Current <sup>(1)</sup> | I <sub>OUT</sub> = 7.0mA                           |

|    |     |      |    |    |    |       |    | LSB/MSB MODE (Register 1)                   |                                                    |

|    |     |      |    | 0  | 0  | Х     | х  | LSB First Mode                              | (default after reset)                              |

|    |     |      |    | 0  | 1  | Х     | х  | MSB First Mode                              |                                                    |

| 0  | 0   | 1    | 0  |    |    |       |    | POWER-DOWN ADC CHANNELS<br>(Register 2)     |                                                    |

|    |     |      |    | 0  | 1  | 0     | х  | D2: Power-Down for Channel 2                | Logic 1 = Channel Powered                          |

|    |     |      |    | 0  | Х  | 0     | 1  | D0: Power-Down for Channel 1                | Down                                               |

| 0  | 0   | 1    | 1  |    |    |       |    | POWER-DOWN ADC CHANNELS<br>(Register 3)     |                                                    |

|    |     |      |    | 1  | 0  | Х     | 0  | D3: Power-Down for Channel 4                | Logic 1 = Channel Powered                          |

|    |     |      |    | х  | 0  | 1     | 0  | D1: Power-Down for Channel 3                | Down                                               |

|    |     |      |    |    |    |       |    | CUSTOM PATTERN (Registers 4-6)              |                                                    |

|    |     |      |    | D3 | D2 | D1    | D0 | Bits for Custom Pattern                     | See Test Patterns                                  |

| 0  | 1   | 0    | 0  | Х  | Х  | Х     | Х  |                                             |                                                    |

|    | 1   |      |    | 1  |    |       | 1  |                                             |                                                    |

(1) (1) Output current drive for the two clock LVDS buffers (LCLK<sub>P</sub> and LCLK<sub>N</sub> and ADCLK<sub>P</sub> and ADCLK<sub>N</sub>) is double the output current setting programmed in register 0. The current drive of the data buffers remains the same as the setting in register 0.

Х

Х

### **TEST PATTERNS**

1

1

0

1

1 0

0

0

| Serial Output <sup>(1)</sup>  | LSB   |       |       |       |       |       |       |       |       |       |       | MSB   |

|-------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ADC Output <sup>(2)</sup>     | D0    | D1    | D2    | D3    | D4    | D5    | D6    | D7    | D8    | D9    | D10   | D11   |

| Deskew Pattern                | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     |

| Sync Pattern                  | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     |

| Custom Pattern <sup>(3)</sup> | D0(4) | D1(4) | D2(4) | D3(4) | D0(5) | D1(5) | D2(5) | D3(5) | D0(6) | D1(6) | D2(6) | D3(6) |

(1) The serial output stream comes out LSB first by default.

Х

Х

Х

Х

Х

Х

D11...D0 represent the 12 output bits from the ADC.

(2) (3) D0(4) represents the content of bit D0 of register 4, D3(6) represents the content of bit D3 of register 6, etc.

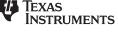

### PIN CONFIGURATION

#### SBAS326E-JUNE 2004-REVISED JANUARY 2009

www.ti.com

#### **PIN DESCRIPTIONS**

| NAME               | PIN #                              | I/O | DESCRIPTION                                                                                        |

|--------------------|------------------------------------|-----|----------------------------------------------------------------------------------------------------|

| ADCLK              | 56                                 | Ι   | Data Converter Clock Input                                                                         |

| ADCLK <sub>N</sub> | 34                                 | 0   | Negative LVDS ADC Clock Output                                                                     |

| ADCLK <sub>P</sub> | 33                                 | 0   | Positive LVDS ADC Clock Output                                                                     |

| AVDD               | 1, 5, 10, 39, 44, 48, 55, 60       | I   | Analog Power Supply                                                                                |

| AVSS               | 4, 6, 9, 40, 43, 45, 49, 57-59, 64 | I   | Analog Ground                                                                                      |

| CS                 | 61                                 | I   | Chip-Select; 0 = Select, 1 = No Select                                                             |

| IN1 <sub>N</sub>   | 3                                  | I   | Channel 1 Differential Analog Input Low                                                            |

| IN1 <sub>P</sub>   | 2                                  | I   | Channel 1 Differential Analog Input High                                                           |

| IN2 <sub>N</sub>   | 8                                  | I   | Channel 2 Differential Analog Input Low                                                            |

| IN2 <sub>P</sub>   | 7                                  | Т   | Channel 2 Differential Analog Input High                                                           |

| IN3 <sub>N</sub>   | 42                                 | I.  | Channel 3 Differential Analog Input Low                                                            |

| IN3 <sub>P</sub>   | 41                                 | Т   | Channel 3 Differential Analog Input High                                                           |

| IN4 <sub>N</sub>   | 47                                 | I.  | Channel 4 Differential Analog Input Low                                                            |

| IN4 <sub>P</sub>   | 46                                 | Т   | Channel 4 Differential Analog Input High                                                           |

| INT/EXT            | 54                                 | Т   | Internal/External Reference Select; 0 = External, 1 = Internal. Weak pull-up to supply.            |

| I <sub>SET</sub>   | 50                                 | I/O | Bias Current Setting Resistor of 56.2k $\Omega$ to Ground                                          |

| LCLK <sub>N</sub>  | 16                                 | 0   | Negative LVDS Clock                                                                                |

| LCLK <sub>P</sub>  | 15                                 | 0   | Positive LVDS Clock                                                                                |

| LVDD               | 21, 27                             | Т   | LVDS Power Supply                                                                                  |

| LVSS               | 11, 13, 14, 22, 28, 35, 36, 38     | I   | LVDS Ground                                                                                        |

| NC                 | 17, 18, 31, 32                     | —   | No Connection                                                                                      |

| OUT1 <sub>N</sub>  | 20                                 | 0   | Channel 1 Negative LVDS Data Output                                                                |

| OUT1 <sub>P</sub>  | 19                                 | 0   | Channel 1 Positive LVDS Data Output                                                                |

| OUT2 <sub>N</sub>  | 24                                 | 0   | Channel 2 Negative LVDS Data Output                                                                |

| OUT2 <sub>P</sub>  | 23                                 | 0   | Channel 2 Positive LVDS Data Output                                                                |

| OUT3 <sub>N</sub>  | 26                                 | 0   | Channel 3 Negative LVDS Data Output                                                                |

| OUT3 <sub>P</sub>  | 25                                 | 0   | Channel 3 Positive LVDS Data Output                                                                |

| OUT4 <sub>N</sub>  | 30                                 | 0   | Channel 4 Negative LVDS Data Output                                                                |

| OUT4 <sub>P</sub>  | 29                                 | 0   | Channel 4 Positive LVDS Data Output                                                                |

| PD                 | 12                                 | I   | Power-Down; 0 = Normal, 1 = Power-Down. Weak pull-down to ground.                                  |

| REFB               | 52                                 | I/O | Reference Bottom Voltage (2 $\Omega$ resistor in series with a capacitor $\ge 0.1\mu F$ to ground) |

| $REF_{T}$          | 53                                 | I/O | Reference Top Voltage (2 $\Omega$ resistor in series with a capacitor $\ge 0.1\mu F$ to ground)    |

| RESET              | 37                                 | Т   | Reset to Default; 0 = Reset, 1 = Normal. Weak pull-down to ground.                                 |

| SCLK               | 63                                 | I   | Serial Data Clock                                                                                  |

| SDATA              | 62                                 | I   | Serial Data Input                                                                                  |

| V <sub>CM</sub>    | 51                                 | 0   | Common-Mode Output Voltage                                                                         |

### DEFINITION OF SPECIFICATIONS

#### Analog Bandwidth

The analog input frequency at which the spectral power of the fundamental frequency (as determined by FFT analysis) is reduced by 3dB.

#### **Aperture Delay**

The delay in time between the rising edge of the input sampling clock and the actual time at which the sampling occurs.

#### **Aperture Uncertainty (Jitter)**

The sample-to-sample variation in aperture delay.

#### Clock Duty Cycle

Pulse width high is the minimum amount of time that the ADCLK pulse should be left in logic '1' state to achieve rated performance. Pulse width low is the minimum time that the ADCLK pulse should be left in a low state (logic '0'). At a given clock rate, these specifications define an acceptable clock duty cycle.

#### **Differential Nonlinearity (DNL)**

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation of any single LSB transition at the digital output from an ideal 1 LSB step at the analog input. If a device claims to have no missing codes, it means that all possible codes (for a 12-bit converter, 4096 codes) are present over the full operating range.

#### Effective Number of Bits (ENOB)

The ENOB is a measure of converter performance as compared to the theoretical limit based on quantization noise.

$\mathsf{ENOB} = \frac{\mathsf{SINAD} - 1.76}{6.02}$

#### Integral Nonlinearity (INL)

INL is the deviation of the transfer function from a reference line measured in fractions of 1 LSB using a *best straight line* or *best fit* determined by a least square curve fit. INL is independent from effects of offset, gain or quantization errors.

#### **Maximum Conversion Rate**

The encode rate at which parametric testing is performed. This is the maximum sampling rate where certified operation is given.

#### Minimum Conversion Rate

This is the minimum sampling rate where the ADC still works.

SBAS326E-JUNE 2004-REVISED JANUARY 2009

#### Signal-to-Noise and Distortion (SINAD)

SINAD is the ratio of the power of the fundamental  $(P_S)$  to the power of all the other spectral components including noise  $(P_N)$  and distortion  $(P_D)$ , but not including dc.

$$SINAD = 10Log_{10} \frac{P_{S}}{P_{N} + P_{D}}$$

SINAD is either given in units of dBc (dB to carrier) when the absolute power of the fundamental is used as the reference, or dBFS (dB to full-scale) when the power of the fundamental is extrapolated to the full-scale range of the converter.

#### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the power of the fundamental ( $P_S$ ) to the noise floor power ( $P_N$ ), excluding the power at dc and the first eight harmonics.

$$SNR = 10Log_{10} \frac{P_s}{P_N}$$

SNR is either given in units of dBc (dB to carrier) when the absolute power of the fundamental is used as the reference, or dBFS (dB to full-scale) when the power of the fundamental is extrapolated to the full-scale range of the converter.

#### **Spurious-Free Dynamic Range**

The ratio of the power of the fundamental to the highest other spectral component (either spur or harmonic). SFDR is typically given in units of dBc (dB to carrier).

# Two-Tone, Third-Order Intermodulation Distortion

Two-tone IMD3 is the ratio of power of the fundamental (at frequencies  $f_1$  and  $f_2$ ) to the power of the worst spectral component of third-order intermodulation distortion at either frequency  $2f_1 - f_2$  or  $2f_2 - f_1$ . IMD3 is either given in units of dBc (dB to carrier) when the absolute power of the fundamental is used as the reference, or dBFS (dB to full-scale) when the power of the fundamental is extrapolated to the full-scale range of the converter.

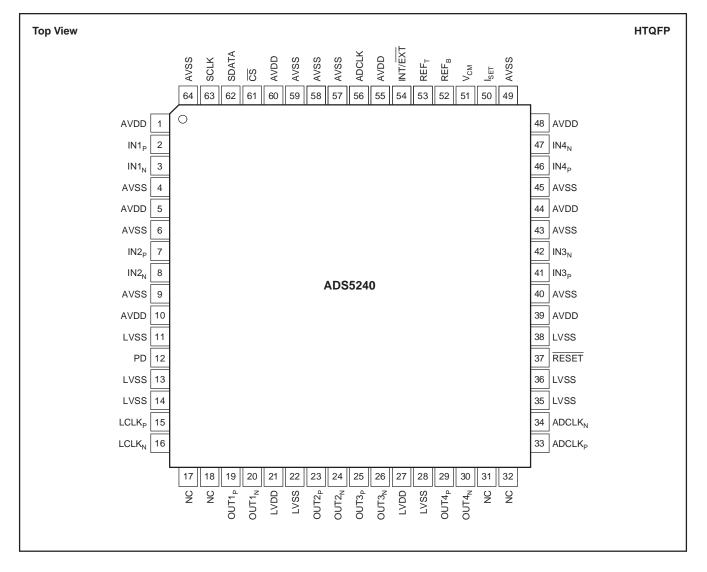

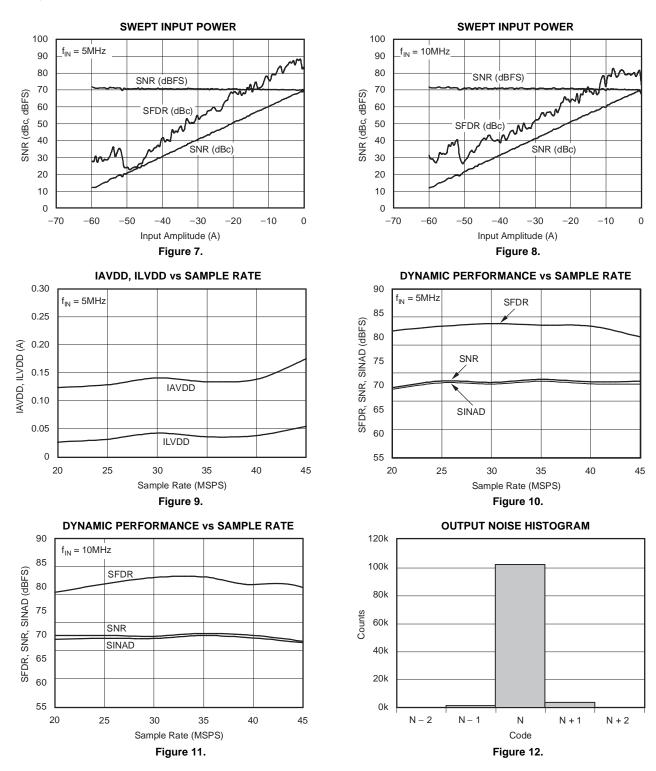

#### **TYPICAL CHARACTERISTICS**

$T_{MIN} = -40^{\circ}C$  and  $T_{MAX} = +85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , clock frequency = maximum specified, 50% clock duty cycle, AVDD = 3.3V, LVDD = 3.3V, -1dBFS,  $I_{SET} = 56.2k\Omega$ , internal voltage reference, and LVDS buffer current at 3.5mA per channel, unless otherwise noted.

#### SBAS326E-JUNE 2004-REVISED JANUARY 2009

### **TYPICAL CHARACTERISTICS (continued)**

$T_{MIN} = -40^{\circ}C$  and  $T_{MAX} = +85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , clock frequency = maximum specified, 50% clock duty cycle, AVDD = 3.3V, LVDD = 3.3V, -1dBFS,  $I_{SET} = 56.2k\Omega$ , internal voltage reference, and LVDS buffer current at 3.5mA per channel, unless otherwise noted.

### THEORY OF OPERATION

#### OVERVIEW

The ADS5240 is a 4-channel, high-speed, CMOS ADC. lt consists of а high-performance sample-and-hold circuit at the input, followed by a 12-bit ADC. The 12 bits given out by each channel are serialized and sent out on a single pair of pins in LVDS format. All four channels of the ADS5240 operate from a single clock referred to as ADCLK. The sampling clocks for each of the four channels are generated from the input clock using a carefully matched clock buffer tree. The 12x clock required for the serializer is generated internally from ADCLK using a phase lock loop (PLL). A 6x and a 1x clock are also output in LVDS format along with the data to enable easy data capture. The ADS5240 operates from internally generated reference voltages that are trimmed to ensure matching across multiple devices on a board. This feature eliminates the need for external routing of reference lines and also improves matching of the gain across devices. The nominal values of  $REF_T$  and  $REF_B$  are 1.95V and 0.95V, respectively. These values imply that a differential input of -1V corresponds to the zero code of the ADC, and a differential input of +1V corresponds to the full-scale code (4095 LSB).  $V_{CM}$  (common-mode voltage of  $REF_T$  and  $REF_B$ ) is also made available externally through a pin, and is nominally 1.45V.

The ADC employs a pipelined converter architecture consisting of a combination of multi-bit and single-bit internal stages. Each stage feeds its data into the digital error correction logic, ensuring excellent differential linearity and no missing codes at the 12-bit level. The pipeline architecture results in a data latency of 6.5 clock cycles.

The output of the ADC goes to a serializer that operates from a 12x clock generated by the PLL. The 12 data bits from each channel are serialized and sent LSB first. In addition to serializing the data, the serializer also generates a 1x clock and a 6x clock. These clocks are generated in the same way the serialized data is generated, so these clocks maintain perfect synchronization with the data. The data and clock outputs of the serializer are buffered externally using LVDS buffers. Using LVDS buffers to transmit data externally has multiple advantages, such as a reduced number of output pins (saving routing space on the board), reduced power consumption, and reduced effects of digital noise coupling to the analog circuit inside the ADS5240.

The ADS5240 operates from two sets of supplies and grounds. The analog supply/ground set is denoted as AVDD/AVSS, while the digital set is denoted by LVDD/LVSS.

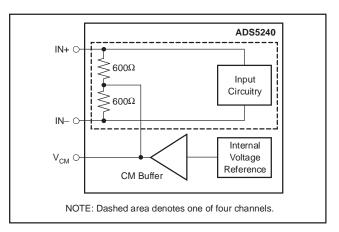

#### **DRIVING THE ANALOG INPUTS**

The analog input biasing is shown in Figure 13. The inputs are biased internally using two  $600\Omega$  resistors to enable ac-coupling. A resistor greater than  $20\Omega$  is recommended in series with each input pin.

A 4pF sampling capacitor is used to sample the inputs. The choice of the external ac-coupling capacitor is dictated by the attenuation at the lowest desired input frequency of operation. The attenuation resulting from using a 10nF ac-coupling capacitor is 0.04%.

Figure 13. Analog Input Bias Circuitry

If the input is dc-coupled, then the output common-mode voltage of the circuit driving the ADS5240 should match the  $V_{CM}$  (which is provided as an output pin) to within ±50mV. It is recommended that the output common-mode of the driving circuit be derived from  $V_{CM}$  provided by the device.

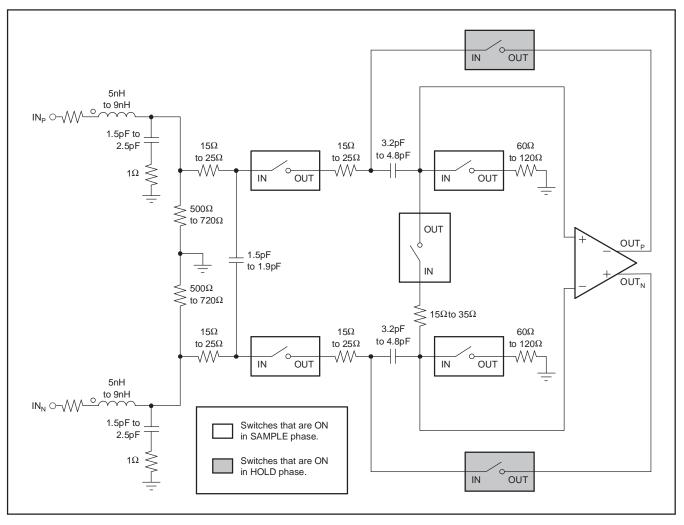

Figure 14 shows a detailed RLC model of the sample-and-hold circuit. The circuit operates in two phases. In the sample phase, the input is sampled on two capacitors that are nominally 4pF. The sampling circuit consists of a low-pass RC filter at the input to filter out noise components that might be differentially coupled on the input pins. The next phase is the hold phase wherein the voltage sampled on the capacitors is transferred (using the amplifier) to a subsequent pipeline ADC stage.

#### INPUT OVER-VOLTAGE RECOVERY

The differential full-scale range supported by the ADS5240 is nominally 2.03V. The ADS5240 is specially designed to handle an over-voltage condition where the differential peak-to-peak voltage can exceed up to twice the ADC full-scale range. If the input common-mode is not considerably off from  $V_{CM}$  during overload (less than 300mV around the nominal value of 1.45V), recovery from an

over-voltage pulse input of twice the amplitude of a full-scale pulse is expected to be within three clock cycles when the input switches from overload to zero signal. All of the amplifiers in the SHA and ADC are specially designed for excellent recovery from an overload signal.

In most applications, the ADC inputs are driven with differential sinusoidal inputs. While the pulse-type signal remains at peak overload conditions throughout its HIGH state, the sinusoid signal only attains peak overload intermittently, at its minima and maxima. This condition is much less severe for the ADC input and the recovery of the ADC output (to 1% of full-scale around the expected code). This typically happens within the second clock when the input is driven with a sinusoid of amplitude equal to twice that of the ADC differential full-scale range.

#### SBAS326E-JUNE 2004-REVISED JANUARY 2009

#### **REFERENCE CIRCUIT DESIGN**

The digital beam-forming algorithm relies heavily on gain matching across all receiver channels. A typical system would have about 24 quad ADCs on the board. In such a case, it is critical to ensure that the gain is matched, essentially requiring the reference voltages seen by all the ADCs to be the same. Matching references within the four channels of a chip is done by using a single internal reference voltage buffer. Trimming the reference voltages on each chip during production ensures the reference voltages are well matched across different chips.

All bias currents required for the internal operation of the device are set using an external resistor to ground at pin  $I_{SET}$ . Using a 56.2k $\Omega$  resistor on  $I_{SET}$  generates an internal reference current of 20µA. This current is mirrored internally to generate the bias current for the internal blocks. Using a larger external resistor at  $I_{SET}$  reduces the reference bias current and thereby scales down the device operating power. However, it is recommended that the external resistor be within 10% of the specified value of 56.2k $\Omega$  so that the internal bias margins for the various blocks are proper.

Buffering the internal bandgap voltage also generates a voltage called  $V_{CM}$ , which is set to the midlevel of REF<sub>T</sub> and REF<sub>B</sub>, and is accessible on a pin. It is meant as a reference voltage to derive the input common-mode in case the input is directly coupled. It can also be used to derive the reference common-mode voltage in the external reference mode.

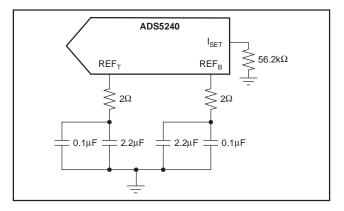

When using the internal reference mode, a  $2\Omega$  resistor should be added between the reference pins (REF<sub>T</sub> and REF<sub>B</sub>) and the decoupling capacitor, as shown in Figure 15. If the device is used in the external reference mode, this  $2\Omega$  resistor is not required.

Figure 15. Internal Reference Mode

The device also supports the use of external reference voltages. This mode involves forcing  $REF_T$

and REF<sub>B</sub> externally. In this mode, the internal reference buffer is tri-stated. Since the switching current for the four ADCs come from the externally forced references, it is possible for the performance to be slightly less than when the internal references are used. It should be noted that in this mode, V<sub>CM</sub> and I<sub>SET</sub> continue to be generated from the internal bandgap voltage, as in the internal reference mode. It is therefore important to ensure that the common-mode voltage of the externally forced reference voltages matches to within 50mV of  $V_{CM}$ . The state of the reference voltages during various combinations of PD and INT/EXT is shown in Table 1.

Table 1. State of Reference Voltages for Various

Combinations of PD and INT/EXT

| PD              | 0         | 0     | 1                        | 1                        |

|-----------------|-----------|-------|--------------------------|--------------------------|

| INT/EXT         | 0         | 1     | 0                        | 1                        |

| REFT            | Tri-State | 1.95V | Tri-State                | Tri-State                |

| REFB            | Tri-State | 0.95V | Tri-State                | Tri-State                |

| V <sub>CM</sub> | 1.45V     | 1.45V | Tri-State <sup>(1)</sup> | Tri-State <sup>(1)</sup> |

(1) Weak pull-down (approximately  $5k\Omega$ ) to ground.

#### CLOCKING

The four channels on the chip operate from a single ADCLK input. To ensure that the aperture delay and itter are same for all the channels, a clock tree network is used to generate individual sampling clocks to each channel. The clock paths for all the channels are matched from the source point all the way to the sample-and-hold amplifier. This ensures that the performance and timing for all the channels are identical. The use of the clock tree for matching introduces an aperture delay, which is defined as the delay between the rising edge of ADCLK and the actual instant of sampling. The aperture delays for all the channels are matched to the best possible extent. However, a mismatch of  $\pm 20$  ps ( $\pm 3\sigma$ ) could exist between the aperture instants of the four ADCs within the same chip. However, the aperture delays of ADCs across two different chips can be several Another hundred picoseconds apart. critical specification is the aperture jitter that is defined as the uncertainty of the sampling instant. The gates in the clock path are designed to provide an rms litter of approximately 1ps.

Ideally, the input ADCLK should have a 50% duty cycle. However, while routing ADCLK to different components onboard, the duty cycle of the ADCLK reaching the ADS5240 could deviate from 50%. A smaller (or larger) duty cycle reduces the time available for sample or hold phases of each circuit, and is therefore not optimal. For this reason, the internal PLL is used to generate an internal clock that has 50% duty cycle. The input sampling instant,

however, is determined by the rising edge of the external clock and is not affected by jitter in the PLL. In addition to generating a 50% duty cycle clock for the ADC, the PLL also generates a 12x clock that is used by the serializer to convert the parallel data from the ADC to a serial stream of bits.

The use of the PLL automatically dictates the minimum sample rate to be about 20MSPS. The PLL also requires the input clock to be free-running. If the input clock is momentarily stopped (for a duration of less than 300ns) then the PLL would require approximately  $10\mu$ s to lock back to the input clock frequency.

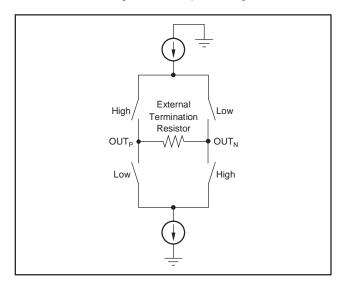

#### LVDS BUFFERS

The LVDS buffer has two current sources, as shown in Figure 16.  $OUT_P$  and  $OUT_N$  are loaded externally by a resistive load that is ideally about  $100\Omega$ . Depending on whether the data is 0 or 1, the currents are directed in one direction or the other through the resistor. The LVDS buffer has four current settings. The default current setting is 3.5mA, and provides a differential drop of about  $\pm 350 \text{mV}$  across the  $100\Omega$  resistor.

The single-ended output impedance of the LVDS drivers is very high because they are current-source driven. If there are excessive reflections from the receiver, it might be necessary to place a  $100\Omega$  termination resistor across the outputs of the LVDS drivers to minimize the effect of reflections. In such a situation, the output current of the LVDS drivers can be increased to regain the output swing.

#### Figure 16. LVDS Buffer

The LVDS buffer receives data from a serializer that takes the output data from each channel and serializes it into a single data stream. For a clock frequency of 65MHz, the data rate output of the

serializer is 780Mbps. The data comes out LSB first, with a register programmability that allows it to revert to MSB first. The serializer also transmits a 1x clock and a 6x clock. The 6x clock (denoted as  $LCLK_P/LCLK_N$ ) is meant to synchronize the capture of the LVDS data.

Deskew mode can be enabled as well, using a register setting. This mode gives out a data stream of alternate 0s and 1s and can be used determine the relative delay between the 6x clock and the output data for optimum capture. A 1x clock is also generated by the serializer and transmitted through the LVDS buffer. The 1x clock (referred to as ADCLK<sub>P</sub>/ADCLK<sub>N</sub>) is used to determine the start of the 12-bit data frame. Sync mode (enabled through a register setting) gives out a data of six 0s followed by six 1s. Using this mode, the 1x clock can be used to determine the start of the data frame. In addition to the deskew mode pattern and the sync mode pattern, a custom pattern can be defined by the user and output from the LVDS buffer. The LVDS buffers are tri-stated in the power-down mode. The LVDS outputs are weakly forced to 1.2V through  $10k\Omega$  resistors (from each output pin to 1.2V).

### NOISE COUPLING ISSUES

High-speed mixed signals are sensitive to various types of noise coupling. One of the main sources of noise is the switching noise from the serializer and the output buffers. Maximum care is taken to isolate these noise sources from the sensitive analog blocks. As a starting point, the analog and digital domains of the chip are clearly demarcated. AVDD and AVSS are used to denote the supplies for the analog sections, while LVDD and LVSS are used to denote the digital supplies. Care is taken to ensure that there is minimal interaction between the supply sets within the device. The extent of noise coupled and transmitted from the digital to the analog sections depends on the following:

- 1. The effective inductances of each of the supply/ground sets.

- 2. The isolation between the digital and analog supply/ground sets.

Smaller effective inductance of the supply/ground pins leads to better suppression of the noise. For this reason, multiple pins are used to drive each supply/ground. It is also critical to ensure that the impedances of the supply and ground lines on board are kept to the minimum possible values. Use of ground planes in the board as well as large decoupling capacitors between the supply and ground lines are necessary to get the best possible SNR from the device.

Copyright © 2004–2009, Texas Instruments Incorporated

It is recommended that the isolation be maintained on board by using separate supplies to drive AVDD and LVDD, as well as separate ground planes for AVSS and LVSS.

The use of LVDS buffers reduces the injected noise considerably, compared to CMOS buffers. The current in the LVDS buffer is independent of the direction of switching. Also, the low output swing as well as the differential nature of the LVDS buffer results in low-noise coupling.

#### **POWER-DOWN MODE**

The ADS5240 has a power-down pin, referred to as PD. Pulling PD high causes the device to enter the power-down mode. In this mode, the reference and clock circuitry, as well as all the channels, are powered down. Device power consumption drops to less than 100mW in this mode. In power-down mode, the internal buffers driving  $REF_{T}$  and  $REF_{B}$  are tri-stated and their outputs are forced to a voltage roughly equal to half of the voltage on AVDD. Speed of recovery from power-down mode depends on the value of the external capacitance on the  $REF_T$  and REF<sub>B</sub> pins. For capacitances on REF<sub>T</sub> and REF<sub>B</sub> less than  $1\mu$ F, the reference voltages settle to within 1% of their steady-state values in less than 500µs. Individual channels can also be selectively powered down by programming registers.

The ADS5240 also has an internal circuit that monitors the state of stopped clocks. If ADCLK is stopped for longer than 300ns (or if it runs at a speed less than 3MHz), this monitoring circuit generates a logic signal that puts the device in a partial power-down state. As a result, the power consumption of the device is reduced when ADCLK is stopped. The recovery from such a partial power-down takes approximately 100µs; this is described in Table 2.

#### RESET

After the supplies have stabilized, it is necessary to give the device an active RESET pulse. This results in all internal registers resetting to their default value of 0 (inactive). Without a reset, it is possible that some registers may be in their non-default state on power-up. This may cause the device to malfunction. When a reset is active, the device outputs '0' code on all channels. However, the LVDS output clocks are unaffected by reset.

#### LAYOUT OF PCB WITH PowerPAD THERMALLY-ENHANCED PACKAGES

The ADS5240 is housed in a 64-lead PowerPAD thermally-enhanced package. To make optimum use of the thermal efficiencies designed into the PowerPAD package, the printed circuit board (PCB) must be designed with this technology in mind. Please refer to SLMA004 PowerPAD brief PowerPAD Made Easy (refer to our web site at www.ti.com), which addresses the specific considerations required when integrating a PowerPAD package into a PCB design. For more detailed information, including thermal modeling and repair procedures, please see brief SLMA002, PowerPAD technical the Thermally-Enhanced Package (www.ti.com).

Interfacing High-Speed LVDS Outputs (SBOA104), an application report discussing the design of a simple deserializer that can deserialize LVDS outputs up to 840Mbps, can also be found on the TI web site (www.ti.com).

#### CONNECTING HIGH-SPEED, MULTI-CHANNEL ADCs TO XILINX FPGAs

A separate application note (XAPP774) describing how to connect TI's high-speed, multi-channel ADCs with serial LVDS outputs to Xilinx FPGAs can be downloaded directly from the Xilinx web site (http://www.xilinx.com).

| Table 2. Time Constraints Associated with Device Recovery from | rom Power-Down and Clock Stoppage |

|----------------------------------------------------------------|-----------------------------------|

|----------------------------------------------------------------|-----------------------------------|

| DESCRIPTION                                             | ТҮР   | REMARKS                                                                   |

|---------------------------------------------------------|-------|---------------------------------------------------------------------------|

| Recovery from power-down mode ( $PD = 1$ to $PD = 0$ ). | 500µs | Capacitors on $\text{REF}_T$ and $\text{REF}_B$ less than $1\mu\text{F}.$ |

| Recovery from momentary clock stoppage ( < 300ns).      | 10µs  |                                                                           |

| Recovery from extended clock stoppage ( > 300ns).       | 100µs |                                                                           |

SBAS326E-JUNE 2004-REVISED JANUARY 2009

www.ti.com

### **Revision History**

| Cł | hanges from Revision D (September 2005) to Revision E                                                                                         | Page |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Updated Absolute Maximum Ratings table: added entries for Digital Input Pins, Set 1 and Set 2 and added footnote                              | 3 2  |

| Cł | hanges from Revision C (December 2004) to Revision D                                                                                          | Page |

| •  | Changed component image to have TI logo                                                                                                       | 1    |

| •  | Changed fourth bullet in Features section.                                                                                                    |      |

| •  | Changed 12th bullet of Features section.                                                                                                      |      |

| •  | Added fifth bullet to Applications section.                                                                                                   |      |

| •  | Changed front page figure.                                                                                                                    |      |

| •  | Changed first footnote of Ordering Information table.                                                                                         |      |

| •  | Changed Absolute Maximum Ratings table and footnotes.                                                                                         |      |

| •  | Changed Recommended Operating Conditions table and footnotes.                                                                                 |      |

| •  | Changed Electrical Characteristics table, conditions, and footnotes.                                                                          |      |

| •  | Changed Reference Selection table; moved from page 3.                                                                                         |      |

| •  | Changed AC Characteristics conditions.                                                                                                        |      |

| •  | Changed ENOB, Crosstalk, and IMD rows of AC Characteristics table.                                                                            | 6    |

| •  | Changed LVDS table.                                                                                                                           | 7    |

| •  | Changed Switching Characteristics table.                                                                                                      | 7    |

| •  | Changed LVDS timing diagram.                                                                                                                  |      |

| •  | Changed Reset timing diagram.                                                                                                                 | 8    |

| •  | Changed Power-Down timing diagram.                                                                                                            | 9    |

| •  | Deleted Serial Interface table.                                                                                                               | 9    |

| •  | Changed LVDS timing diagram.                                                                                                                  | 9    |

| •  | Changed Serial Interface timing diagram and table.                                                                                            | 9    |

| •  | Changed Serial Interface Registers table.                                                                                                     | 10   |

| •  | Changed Test Patterns table.                                                                                                                  | 10   |

| •  | Changed Aperture Delay, Clock Duty Cycle, ENOB, SINAD, SNR, SFDR, and IMD3 sections of <i>Definitions of Specifications</i> section.          | 13   |

| •  | Deleted Nyquist Sampling, Offset Error, Propagation Delay, Temperature Drift, and THD sections of <i>Definition of Specification</i> section. | 13   |

| •  | Changed Figure 1.                                                                                                                             | 14   |

| •  | Changed Figure 2.                                                                                                                             | 14   |

| •  | Changed Figure 3.                                                                                                                             | 14   |

| •  | Changed Figure 4.                                                                                                                             | 14   |

| •  | Changed Figure 9.                                                                                                                             | 15   |

| •  | Deleted Figure 12 (Power Dissipation vs Temperature).                                                                                         | 15   |

| •  | Changed 2V to 1.95V, 1V to 0.95V, and 1.5V to 1.45V in first paragraph of Overview section in Theory of operation.                            | 16   |

| •  | Changed first paragraph of Driving the Analog Inputs section in Theory of Operation.                                                          | 16   |

| •  | Added second paragraph of Driving the Analog Inputs section in Theory of Operation.                                                           | 16   |

| •  | Changed Figure 14.                                                                                                                            | 16   |

| •  | Deleted second and fourth paragraphs of Driving the Analog Inputs section in Theory of Operation.                                             | 16   |

| •  | Deleted Figure 15 (Input Circuitry) of Driving the Analog Inputs section in Theory of Operation.                                              |      |

| •  | Added fourth paragraph of Driving the Analog Inputs section in Theory of Operation.                                                           | 17   |

| •  | Changed Input Over-Voltage Recovery section in Theory of Operation.                                                                           | 17   |

| •  | Added Figure 15 (Overall Structure of the Sample-and-Hold Circuit).                                                                           | 17   |

| •  | Changed second sentence of first paragraph of Reference Circuit Design in Theory of Operation.                                                | 18   |

| •  | Changed third paragraph of Reference Circuit Design in Theory of Operation                                                                    | 18   |

## ADS5240

### TEXAS INSTRUMENTS

SBAS326E-JUNE 2004-REVISED JANUARY 2009

#### www.ti.com

| • | Changed fourth paragraph of Reference Circuit Design in Theory of Operation.                                                                               | 18 |