LMX8410L

SNAS730A - MARCH 2018-REVISED NOVEMBER 2018

# LMX8410L High-Performance Mixer With Integrated Synthesizer

#### **Features**

- Wideband RF Input: 4 to 10 GHz

- Large IF Bandwidth: DC to 1350 MHz

- Input IP3: 28 dBm at 5-GHz RF Input

- Noise Figure: 15 dB at 5-GHz RF Input

- High Voltage Conversion Gain: 11 dB at 5-GHz **RF** Input

- Integrated Wideband RF Input Balun

- Automatic Offline DC Offset Correction to ±2 mV

- Programmable IMRR Calibration

- SYNC Feature for Multiple Devices

- High-Performance Integrated LO Synthesizer: 56.5-dBc DSB Integrated Noise at 5-GHz carrier

- External LO mode: Integrated LO Synthesizer can be Bypassed; Support External LO Injection

- Integrated Low-Noise LDOs

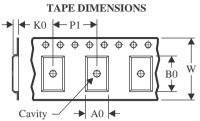

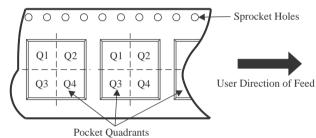

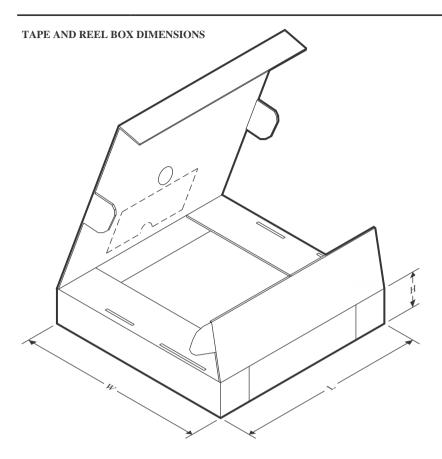

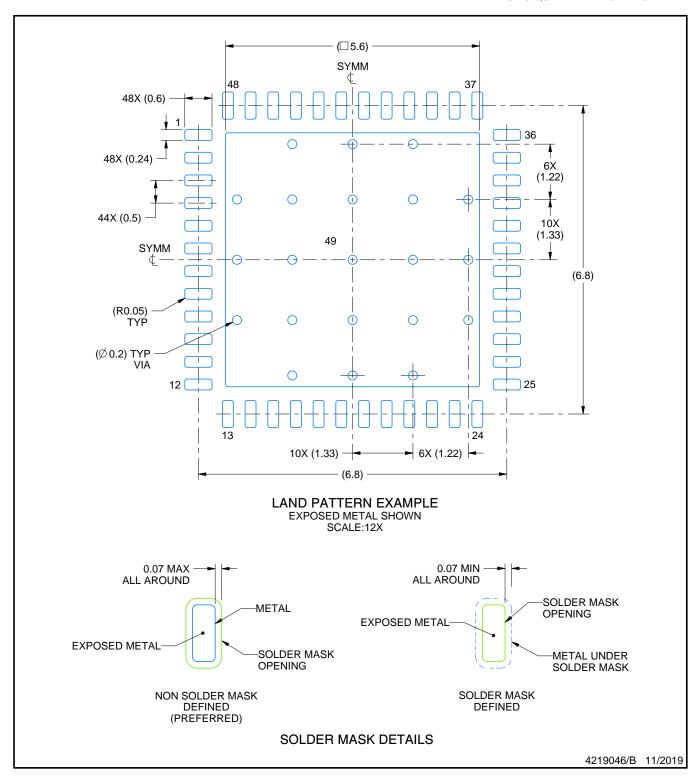

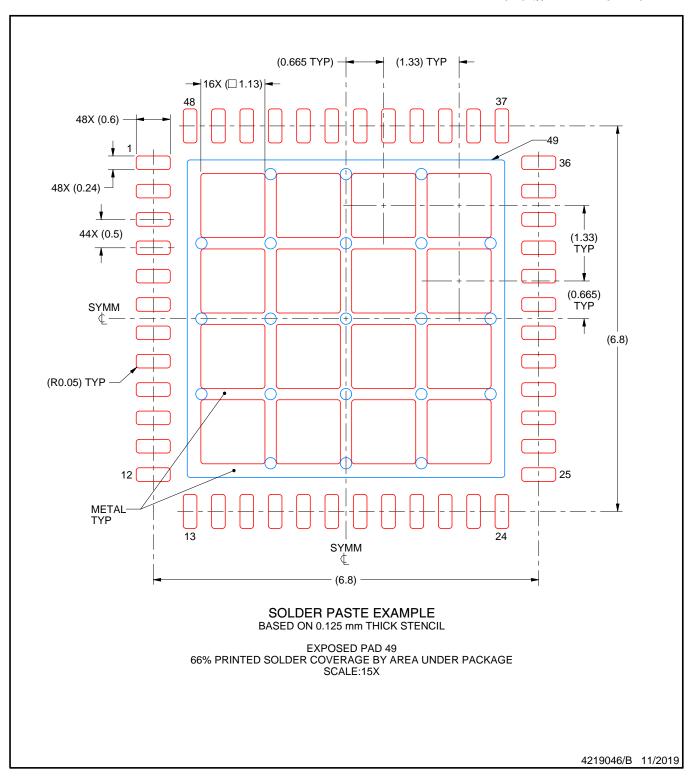

- 7-mm × 7-mm 48-pin QFN Package

# **Applications**

- Test and Measurement Equipment

- Wireless Infrastructure

- Phased Array Radar

- Microwave Backhaul

- Satellite Communications

- Software-Defined Radio

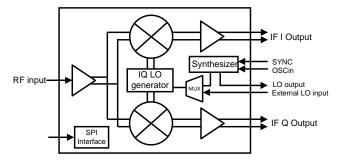

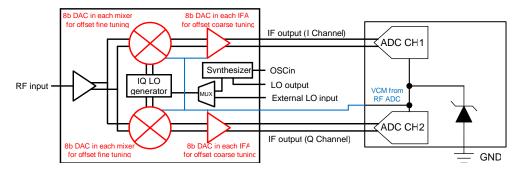

# 3 Description

The LMX8410L is a high-performance wideband (RF frequency input from 4 to 10 GHz) I/Q demodulator with an integrated LO and IF amplifier. With IIP3 of 28 dBm and NF of 15 dB (both at 5GHz), it provides excellent dynamic range for high performance applications. The device offers large complex bandwidth of 2.7 GHz for high data-rate applications.

The LMX8410L offers an automatic DC offset correction algorithm that reduces the offset to less than ±2 mV. Fine control of gain and phase of I and Q channels is enabled using SPI interface to achieve high image rejection.

The LMX8410L has a high level of integration providing high performance while saving board space and complexity. It integrates a wideband RF input balun, eliminating the need for external baluns, It integrates a high-performance PLL and VCO, eliminating the need for external LO and LO driver. The device also integrates an IF amplifier and several low noise LDOs, further simplifying the board.

LMX8410L integrates a very low-noise synthesizer, with a PLL FOM of -236 dBc/Hz, providing up to 56.5-dBc DSB integrated noise at GHz carrier. The LO allows for phase synchronization across multiple devices. The highperformance synthesizer output can be brought out to drive another stage or a data converter. The integrated LO can be bypassed for applications that share a common external LO.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| LMX8410L    | VQFN (48) | 7.00 mm × 7.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

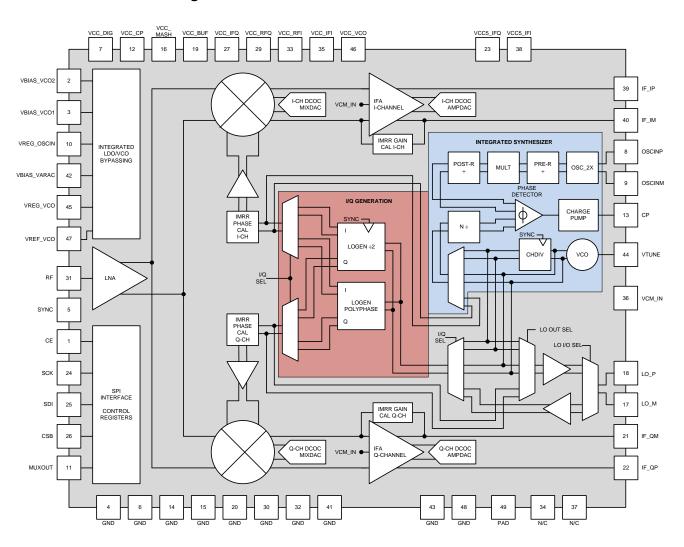

#### Simplified Block Diagram

# **Table of Contents**

| 1 | Features 1                           | 7.5 Programming                                         |

|---|--------------------------------------|---------------------------------------------------------|

| 2 | Applications 1                       | 7.6 Register Map30                                      |

| 3 | Description 1                        | 8 Application and Implementation 53                     |

| 4 | Revision History2                    | 8.1 Application Information 53                          |

| 5 | Pin Configuration and Functions 3    | 8.2 Typical Application53                               |

| 6 | Specifications6                      | 9 Power Supply Recommendations 56                       |

| • | 6.1 Absolute Maximum Ratings         | 10 Layout 56                                            |

|   | 6.2 ESD Ratings                      | 10.1 Layout Guidelines 56                               |

|   | 6.3 Recommended Operating Conditions | 10.2 Layout Examples 57                                 |

|   | 6.4 Thermal Information              | 11 Device and Documentation Support 61                  |

|   | 6.5 Electrical Characteristics       | 11.1 Documentation Support61                            |

|   | 6.6 Timing Requirements              | 11.2 Receiving Notification of Documentation Updates 61 |

|   | 6.7 Typical Characteristics          | 11.3 Community Resources61                              |

| 7 | Detailed Description 22              | 11.4 Trademarks 61                                      |

|   | 7.1 Overview                         | 11.5 Electrostatic Discharge Caution61                  |

|   | 7.2 Functional Block Diagram         | 11.6 Glossary61                                         |

|   | 7.3 Feature Description              | 12 Mechanical, Packaging, and Orderable                 |

|   | 7.4 Device Functional Modes28        | Information 61                                          |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Original (March 2018) to Revision A                                                                                       | Page |

|----|---------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | First release of production-data data sheet                                                                                           | 1    |

| •  | Changed many numbers in electrical specifications table.                                                                              | 6    |

| •  | Added typical performance characteristics section.                                                                                    | 14   |

| •  | Changed and added significant details in detailed descriptions sections. Added sections, changed several portions of the register map | 22   |

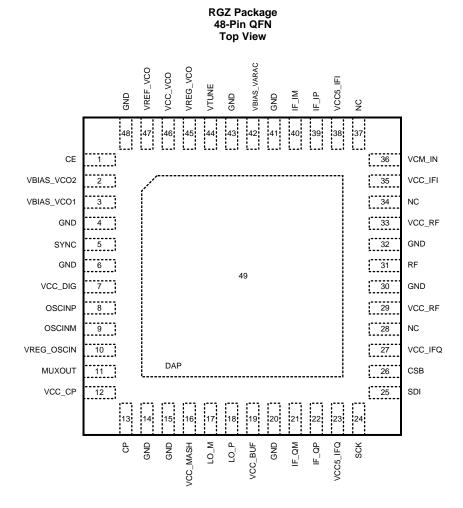

# 5 Pin Configuration and Functions

#### **Pin Functions**

|      | PIN        | 1/0    | DESCRIPTION                                                                                                                                                                                            |  |  |

|------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | NAME NAME  |        | DESCRIPTION                                                                                                                                                                                            |  |  |

| 1    | CE         | Input  | Chip Enable input. Active HIGH powers on the device. 1.8V to 3.3V logic.                                                                                                                               |  |  |

| 2    | VBIAS_VCO2 | Bypass | O bias. Requires connecting 10-µF capacitor to VCO ground. Place close to pin. If using ernal LO, this pin should either be floated or configured the same way as internal LO mode.                    |  |  |

| 3    | VBIAS_VCO1 | Bypass | D bias. Requires connecting 10-μF capacitor to VCO ground. Place close to pin. If using rnal LO, this pin should either be floated or configured the same way as internal LO mode.                     |  |  |

| 4    | GND        | Ground | O ground. VBIAS pin capacitors must bypass to this point.                                                                                                                                              |  |  |

| 5    | SYNC       | Input  | gger pin for synchronizing multiple devices. If using external LO, tie this pin to GND.                                                                                                                |  |  |

| 6    | GND        | Ground | Digital ground. VCC_DIG bypass capacitors must bypass to this point.                                                                                                                                   |  |  |

| 7    | VCC_DIG    | Supply | Digital supply. TI recommends connecting 0.1-µF capacitor to digital ground.                                                                                                                           |  |  |

| 8    | OSCINP     | Input  | Reference input clock (+). High input impedance. Requires connecting series capacitor (0.1 µF recommended). If using external LO, tie this pin to GND.                                                 |  |  |

| 9    | OSCINM     | Input  | Reference input clock (–). High input impedance. Requires connecting series capacitor (0.1 µF recommended). If using external LO, tie this pin to GND.                                                 |  |  |

| 10   | VREG_OSCIN | Bypass | Internal LDO output. Requires connecting 1-µF capacitor to digital ground. Place close to pin. If using external LO, this pin should either be floated or configured the same way as internal LO mode. |  |  |

# Pin Functions (continued)

|      | PIN         |              |                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NAME        | I/O          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |  |

| 11   | MUXOUT      | Output       | Readback or lock detect output. Pin mode configured by internal register settings.                                                                                                                                                                                                                                                                                                    |  |

| 12   | VCC_CP      | Supply       | Charge pump supply. TI recommends connecting 0.1 µF and 100 pF to charge pump ground. Place close to pin. This pin must be connected to VCC, even if using external LO.                                                                                                                                                                                                               |  |

| 13   | СР          | Output       | Charge pump output. TI recommends connecting C1 of loop filter close to pin. If using external LO, this pin should either be floated or configured the same way as internal LO mode.                                                                                                                                                                                                  |  |

| 14   | GND         | Ground       | Charge pump ground. VCC_CP bypass capacitors must bypass to this point.                                                                                                                                                                                                                                                                                                               |  |

| 15   | GND         | Ground       | MASH engine ground. VCC_MASH bypass capacitors must bypass to this point.                                                                                                                                                                                                                                                                                                             |  |

| 16   | VCC_MASH    | Supply       | MASH engine supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to MASH engine ground. Place close to pin. This pin must be connected to VCC, even if using external LO.                                                                                                                                                                                                          |  |

| 17   | LO_M        | Input/Output | Internal LO differential output (–) or external LO differential input (–). In differential output mode, requires connecting $50-\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin. In differential input mode, remove the pull up resistors or inductors. The input should be capacitively coupled with internal biasing. See <i>LO Interface</i> for more information. |  |

| 18   | LO_P        | Input/Output | Internal LO differential output (+) or external LO differential input (+). In differential output mode, requires connecting $50-\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin. In differential input mode, remove the pull up resistors or inductors. The input should be capacitively coupled with internal biasing. See LO Interface for more information.        |  |

| 19   | VCC_BUF     | Supply       | LO buffer supply. TI recommends connecting 0.1 µF and 100 pF to VCO ground. This pin must be connected to VCC, even if using external LO.                                                                                                                                                                                                                                             |  |

| 20   | GND         | Ground       | IF amplifier Q-channel ground. Q-channel VCC5 bypass capacitors must bypass to this point.                                                                                                                                                                                                                                                                                            |  |

| 21   | IF_QM       | Output       | IF amplifier Q-channel differential output (–). TI recommends connecting series $50-\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                    |  |

| 22   | IF_QP       | Output       | IF amplifier Q-channel differential output (+). TI recommends connecting series $50-\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                    |  |

| 23   | VCC5_IFQ    | Supply       | IF amplifier Q-channel 5-V supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to IF amplifier Q-channel ground. Place close to pin.                                                                                                                                                                                                                                              |  |

| 24   | SCK         | Input        | SPI clock signal. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                                                                                                                                                                                                                    |  |

| 25   | SDI         | Input        | SPI data signal. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                                                                                                                                                                                                                     |  |

| 26   | CSB         | Input        | SPI chip select signal. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                                                                                                                                                                                                              |  |

| 27   | VCC_IFQ     | Supply       | IF mixer Q-channel supply. TI recommends connecting 0.1 μF and 100 pF to digital ground.                                                                                                                                                                                                                                                                                              |  |

| 28   | NC          | N/A          | No connect. Pin is not internally connected and may be floated or shorted to other nodes.                                                                                                                                                                                                                                                                                             |  |

| 29   | VCC_RFQ     | Supply       | RF Q-channel supply. TI recommends connecting 0.1 µF and 100 pF to digital ground.                                                                                                                                                                                                                                                                                                    |  |

| 32   | GND         | Ground       | RF input path ground.                                                                                                                                                                                                                                                                                                                                                                 |  |

| 31   | RF          | Input        | RF input. Single-ended. Must be AC coupled.                                                                                                                                                                                                                                                                                                                                           |  |

| 32   | GND         | Ground       | RF input path ground.                                                                                                                                                                                                                                                                                                                                                                 |  |

| 33   | VCC_RFI     | Supply       | RF I-channel supply. TI recommends connecting 0.1 µF and 100 pF to digital ground.                                                                                                                                                                                                                                                                                                    |  |

| 34   | GND         | Ground       | Should be connected IF ground.                                                                                                                                                                                                                                                                                                                                                        |  |

| 35   | VCC_IFI     | Supply       | IF mixer I-channel supply. TI recommends connecting 0.1 μF and 100 pF to digital ground.                                                                                                                                                                                                                                                                                              |  |

| 36   | VCM_IN      | Input        | Common-mode voltage input. When the VCM_CONFIG register is set to external (0xF), the voltage on this pin sets the common-mode voltage of the IF amplifiers.                                                                                                                                                                                                                          |  |

| 37   | NC          | Ground       | Connect this pin to IF ground.                                                                                                                                                                                                                                                                                                                                                        |  |

| 38   | VCC5_IFI    | Supply       | IF amplifier I-channel 5-V supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to IF amplifier I-channel ground. Place close to pin.                                                                                                                                                                                                                                              |  |

| 39   | IF_IP       | Output       | IF amplifier I-channel differential output (+). TI recommends connecting series 50- $\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                   |  |

| 40   | IF_IM       | Output       | IF amplifier I-channel differential output (–). TI recommends connecting series 50- $\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                   |  |

| 41   | GND         | Ground       | IF amplifier I-channel ground. I-channel VCC5 bypass capacitors should bypass to this point.                                                                                                                                                                                                                                                                                          |  |

| 42   | VBIAS_VARAC | Bypass       | VCO varactor bias. Requires connecting $10\mu F$ capacitor to VCO ground. If using external LO, this pin should either be floated or configured the same way as internal LO mode.                                                                                                                                                                                                     |  |

| 43   | GND         | Ground       | VCO ground. Varactor bias bypass capacitor should bypass to this point.                                                                                                                                                                                                                                                                                                               |  |

Submit Documentation Feedback

# Pin Functions (continued)

|      | PIN      | I/O    | DESCRIPTION                                                                                                                                                                       |  |  |

|------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | NAME     | 1/0    | DESCRIPTION                                                                                                                                                                       |  |  |

| 44   | VTUNE    | Input  | VCO tuning voltage input. If using internal LO, connect the output of the loop filter to this point. If using external LO, tie this pin to GND.                                   |  |  |

| 45   | VREG_VCO | Bypass | VCO LDO output node. Requires connecting 10-µF capacitor to VCO ground. Place close to pin. This capacitor must be present even if used in external LO mode.                      |  |  |

| 46   | VCC_VCO  | Supply | VCO supply. TI recommends connecting 0.1-µF and 100-pF capacitors to VCO ground. This pin must be connected to VCC, even if using external LO.                                    |  |  |

| 47   | VREF_VCO | Bypass | VCO LDO reference node. Requires connecting 1-µF capacitor to VCO ground. If using external LO, this pin should either be floated or configured the same way as internal LO mode. |  |  |

| 48   | GND      | Ground | VCO ground. VCO LDO, LDO reference, and supply bypass capacitors must bypass to this point.                                                                                       |  |  |

| 49   | PAD      | Ground | Die attach pad. Internally connected to ground. TI recommends shorting ground pins to this pad on the same plane, if possible.                                                    |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                  | MIN  | MAX | UNIT |

|------------------|----------------------------------|------|-----|------|

| $V_{CC}$         | Power supply voltage, 3.3-V rail | -0.3 | 3.6 | V    |

| V <sub>CC5</sub> | Power supply voltage, 5-V rail   | -0.3 | 5.3 | V    |

| $P_D$            | Power dissipation                |      | 5   | W    |

| TJ               | Junction temperature             | -40  | 150 | °C   |

| T <sub>stg</sub> | Storage temperature              | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Rating* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Condition*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

| V                  | ANS                     | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins             | 2500  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins | 500   | V    |

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                 | MIN  | NOM | MAX  | UNIT |

|----------------|---------------------------------|------|-----|------|------|

| $V_{CC}$       | Power supply voltage, 3.3V rail | 3.15 | 3.3 | 3.45 | V    |

| $V_{CC5}$      | Power supply voltage, 5V rail   | 4.75 | 5   | 5.25 | V    |

| T <sub>A</sub> | Ambient temperature             | -40  | 25  | 85   | °C   |

| $T_{J}$        | Junction temperature            |      |     | 125  | °C   |

# 6.4 Thermal Information

|                      |                                                                                                                                                                                                                                                  | LMX8410L   |      |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|

|                      | R <sub>0JC(top)</sub> Junction-to-case (top) thermal resistance  R <sub>0JB</sub> Junction-to-board thermal resistance  P <sub>JT</sub> Junction-to-top characterization parameter  P <sub>JB</sub> Junction-to-board characterization parameter | RGZ (VQFN) | UNIT |

|                      |                                                                                                                                                                                                                                                  | 48 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance                                                                                                                                                                                                           | 21.9       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                                                                                                                                                                                                        | 9.4        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                                                                                                                                                                                                             | 5.6        | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter                                                                                                                                                                                                       | 0.1        | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter                                                                                                                                                                                                     | 5.6        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance                                                                                                                                                                                                     | 0.4        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report

<sup>(2)</sup> Thermal model based on JEDEC standard coupon, 50.8 mm × 50.8 mm × 1.6 mm, six-layer Cu, 0.5 oz top layer, 2 oz else. 6 × 6 thermal vias in DAP, 0.2 mm diameter.

# 6.5 Electrical Characteristics

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

|                  | PARAMETER                                            | TEST CONDITIONS | MIN  | TYP  | MAX   | UNIT |

|------------------|------------------------------------------------------|-----------------|------|------|-------|------|

| POWER SU         | PPLY                                                 |                 |      |      |       |      |

| V <sub>CC</sub>  | Power supply voltage, 3.3-V rail                     |                 | 3.15 | 3.3  | 3.45  | V    |

|                  | D                                                    | Internal LO     |      | 650  |       |      |

| I <sub>CC</sub>  | Power supply current, 3.3-V rail                     | External LO     |      | 330  |       | mA   |

| V <sub>CC5</sub> | Power supply voltage, 5-V rail                       |                 | 4.75 | 5    | 5.25  | V    |

| I <sub>CC5</sub> | Power supply current both channels I and Q, 5-V rail |                 |      | 130  |       | mA   |

| FREQUENC         | Y RANGES                                             |                 | 11   |      | •     |      |

| F <sub>RF</sub>  | RF port frequency range                              |                 | 4000 |      | 10000 | MHz  |

| F <sub>LO</sub>  | LO port frequency range                              |                 | 4000 |      | 10000 | MHz  |

| F <sub>IF</sub>  | IF port frequency range (3dB bandwidth)              |                 | DC   |      | 1350  | MHz  |

| DYNAMIC P        | ERFORMANCE                                           |                 | - 1  |      | (I)   |      |

|                  |                                                      | RF = 4 GHz      |      | 15   |       |      |

|                  |                                                      | RF = 5 GHz      |      | 15   |       |      |

|                  |                                                      | RF = 6 GHz      |      | 16   |       |      |

| NF               | Noise figure                                         | RF = 7 GHz      |      | 17   |       | dB   |

|                  |                                                      | RF = 8 GHz      |      | 18   |       |      |

|                  |                                                      | RF = 9 GHz      |      | 19   |       |      |

|                  |                                                      | RF = 10 GHz     |      | 19   |       |      |

|                  |                                                      | RF = 4 GHz      |      | 11   |       |      |

|                  |                                                      | RF = 5 GHz      |      | 11   |       |      |

|                  |                                                      | RF = 6 GHz      |      | 10.5 |       |      |

| G                | Voltage gain <sup>(1)</sup>                          | RF = 7 GHz      |      | 9.5  |       | dB   |

|                  |                                                      | RF = 8 GHz      |      | 9    |       |      |

|                  |                                                      | RF = 9 GHz      |      | 8    |       |      |

|                  |                                                      | RF = 10 GHz     |      | 7    |       | ı    |

|                  |                                                      | RF = 4 GHz      |      | 28   |       |      |

|                  |                                                      | RF = 5 GHz      |      | 28   |       |      |

|                  |                                                      | RF = 6 GHz      |      | 26.5 |       |      |

| IIP3             | Input intercept point, 3rd order <sup>(2)</sup>      | RF = 7 GHz      |      | 27   |       | dBm  |

|                  |                                                      | RF = 8 GHz      |      | 26.5 |       |      |

|                  |                                                      | RF = 9 GHz      |      | 27   |       |      |

|                  |                                                      | RF = 10 GHz     |      | 27   |       |      |

| IIP2             |                                                      | RF = 4 GHz      |      | 48   |       |      |

|                  |                                                      | RF = 5 GHz      |      | 48   |       |      |

|                  |                                                      | RF = 6 GHz      |      | 46   |       |      |

|                  | Input intercept point, 2nd order (uncalibrated)      | RF = 7 GHz      |      | 44   |       | dBn  |

|                  | (uncambrateu)                                        | RF = 8 GHz      |      | 45   |       |      |

|                  |                                                      | RF = 9 GHz      |      | 44   |       |      |

|                  |                                                      | RF = 10 GHz     |      | 42   |       |      |

<sup>(1)</sup> For measurements that require RF input, RF input power is -10dBm unless otherwise specified.

<sup>(2)</sup> For two-tone measurements, tone separation is 17MHz.

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

|                      | PARAMETER                            | TEST CONDITIONS | MIN TYF | MAX MAX | UNIT |

|----------------------|--------------------------------------|-----------------|---------|---------|------|

|                      |                                      | RF = 4 GHz      | -58     | 3       |      |

|                      |                                      | RF = 5 GHz      | -58     | 3       |      |

| SP <sub>2x2</sub>    |                                      | RF = 6 GHz      | -58     | 3       |      |

|                      | 2x2 spur [RF input power at -10 dBm] | RF = 7 GHz      | -54     | ļ       | dBc  |

|                      |                                      | RF = 8 GHz      | -52     | 2       |      |

|                      |                                      | RF = 9 GHz      | -50     | )       |      |

|                      |                                      | RF = 10 GHz     | -48     | 3       |      |

|                      |                                      | RF = 4 GHz      | -75     | 5       |      |

|                      |                                      | RF = 5 GHz      | -75     | 5       |      |

|                      |                                      | RF = 6 GHz      | -75     | 5       |      |

| SP <sub>3x3</sub>    | 3x3 spur [RF input power at -10 dBm] | RF = 7 GHz      | -75     | 5       | dBc  |

|                      |                                      | RF = 8 GHz      | -75     | 5       |      |

|                      |                                      | RF = 9 GHz      | -75     | 5       |      |

|                      |                                      | RF = 10 GHz     | -75     | 5       |      |

|                      |                                      | RF = 4 GHz      | 12      | 2       |      |

|                      |                                      | RF = 5 GHz      | 12      | 2       |      |

|                      | Output 1-dB compression point        | RF = 6 GHz      | 12      | 2       |      |

| ) <sub>P1dB</sub>    |                                      | RF = 7 GHz      | 12      | 2       | dBm  |

|                      |                                      | RF = 8 GHz      | 12      | 2       |      |

|                      |                                      | RF = 9 GHz      | 12      | 2       |      |

|                      |                                      | RF = 10 GHz     | 12      | 2       |      |

|                      |                                      | RF = 4 GHz      | 43      | 3       |      |

|                      |                                      | RF = 5 GHz      | 43      | 3       |      |

|                      |                                      | RF = 6 GHz      | 44      | 1       |      |

| RR                   | Image rejection ratio [calibrated]   | RF = 7 GHz      | 44      | ļ       | dB   |

|                      |                                      | RF = 8 GHz      | 43      | 3       |      |

|                      |                                      | RF = 9 GHz      | 42      | 2       |      |

|                      |                                      | RF = 10 GHz     | 36      | 3       |      |

|                      |                                      | RF = 4 GHz      | 40      | )       |      |

|                      |                                      | RF = 5 GHz      | 40      | )       |      |

|                      |                                      | RF = 6 GHz      | 40      | )       |      |

| SO <sub>RFxIF</sub>  | RF to IF isolation                   | RF = 7 GHz      | 40      | )       | dB   |

|                      |                                      | RF = 8 GHz      | 40      | )       |      |

|                      |                                      | RF = 9 GHz      | 40      | )       |      |

|                      |                                      | RF = 10 GHz     | 40      | )       |      |

|                      |                                      | LO = 4 GHz      | -35     | 5       |      |

|                      |                                      | LO = 5 GHz      | -35     | 5       |      |

|                      |                                      | LO = 6 GHz      | -35     | 5       |      |

| EAK <sub>RFxIF</sub> | LO to IF leakage                     | LO = 7 GHz      | -35     |         | dBm  |

| 200                  |                                      | LO = 8 GHz      | -35     |         |      |

|                      |                                      | LO = 9 GHz      | -35     |         |      |

|                      |                                      | LO = 10 GHz     | -35     |         |      |

Product Folder Links: LMX8410L

Submit Documentation Feedback

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

|                       | PARAMETER                                           | TEST CONDITIONS                                                 | MIN TYP | MAX  | UNIT    |  |  |  |

|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------|---------|------|---------|--|--|--|

|                       |                                                     | LO = 4 GHz                                                      | -60     |      |         |  |  |  |

|                       |                                                     | LO = 5 GHz                                                      | -60     |      |         |  |  |  |

|                       |                                                     | LO = 6 GHz                                                      | -52     |      |         |  |  |  |

| LEAK <sub>LOxRF</sub> | LO to RF leakage (internal Lo mode)                 | LO = 7 GHz                                                      | -50     |      | dBm     |  |  |  |

|                       |                                                     | LO = 8 GHz                                                      | -50     |      |         |  |  |  |

|                       |                                                     | LO = 9 GHz                                                      | -45     |      |         |  |  |  |

|                       |                                                     | LO = 10 GHz                                                     | -40     | -40  |         |  |  |  |

| PERFORMANO            | E TUNING                                            |                                                                 |         |      |         |  |  |  |

| G <sub>IQ_CAL</sub>   | I/Q gain calibration range                          | IMRR_GCAL register full range                                   | ±0.5    |      | dB      |  |  |  |

| G <sub>IQ_STEP</sub>  | I/Q gain calibration step size                      |                                                                 | 0.05    |      | dB      |  |  |  |

| PH <sub>IQ_CAL</sub>  | I/Q phase calibration range                         | IMRR_PCAL register full range                                   | ±20     |      | Deg     |  |  |  |

| PH <sub>IQ_STEP</sub> | I/Q phase calibration step size                     | Step size can be made reduced to 0.25 deg in fine accuracy mode | 0.45    |      | Deg     |  |  |  |

| V <sub>DCOC</sub>     | calibrated differential DC offset                   |                                                                 | +/- 2   |      | mV      |  |  |  |

| PORTS                 |                                                     |                                                                 |         |      |         |  |  |  |

|                       |                                                     | RF = 4 GHz                                                      | 8       |      | dB      |  |  |  |

|                       |                                                     | RF = 5 GHz                                                      | 19      |      | dB      |  |  |  |

|                       |                                                     | RF = 6 GHz                                                      | 21      |      | dB      |  |  |  |

| S11 <sub>RF</sub>     | RF return loss                                      | RF = 7 GHz                                                      | 16      |      | dB      |  |  |  |

|                       |                                                     | RF = 8 GHz                                                      | 10      |      | dB      |  |  |  |

|                       |                                                     | RF = 9 GHz                                                      | 9       |      | dB      |  |  |  |

|                       |                                                     | RF = 10 GHz                                                     | 9       |      | dB      |  |  |  |

|                       |                                                     | RF = 4 GHz                                                      | 15      |      | dB      |  |  |  |

|                       |                                                     | RF = 5 GHz                                                      | 15      |      | dB      |  |  |  |

|                       |                                                     | RF = 6 GHz                                                      | 20      |      | dB      |  |  |  |

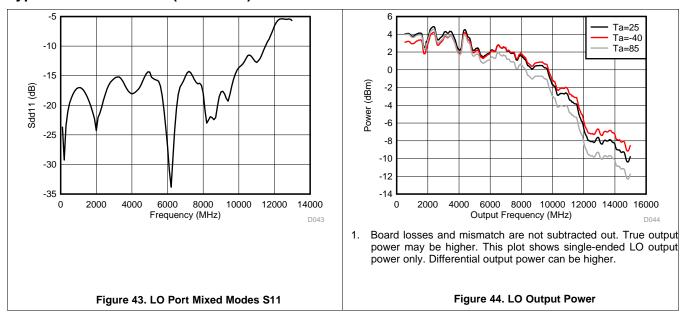

| S11 <sub>LO</sub>     | LO return loss (differential measurement)           | RF = 7 GHz                                                      | 17      |      | dB      |  |  |  |

|                       | measurement)                                        | RF = 8 GHz                                                      | 18      |      | dB      |  |  |  |

|                       |                                                     | RF = 9 GHz                                                      | 17      |      | dB      |  |  |  |

|                       |                                                     | RF = 10 GHz                                                     | 12      |      | dB      |  |  |  |

| P <sub>LO_IN</sub>    | External LO input power                             | 8 GHz RF <sub>IN</sub>                                          | 6       |      | dBm     |  |  |  |

|                       | First and I O putting a group (3)                   | <7 GHz RFout                                                    | 2       |      | dBm     |  |  |  |

| P <sub>LO_OUT</sub>   | External LO output power <sup>(3)</sup>             | <10 GHz RFout                                                   | -1      |      | dBm     |  |  |  |

| V <sub>IF_RANGE</sub> | IF output voltage swing (differential)              |                                                                 | 2       |      | VPP     |  |  |  |

| V <sub>CM</sub>       | IF common mode voltage, internal or external source |                                                                 | 1.2 1.7 | 2    | V       |  |  |  |

| Pin <sub>RF</sub>     | RF input power                                      |                                                                 |         | 5    | dBm     |  |  |  |

| LO SYNTHESIZ          | ZER INPUT SIGNAL PATH                               |                                                                 |         |      |         |  |  |  |

| F <sub>OSCIN</sub>    | Reference oscillator port frequency                 | OSC_2X = 0                                                      | 5       | 1400 | MHz     |  |  |  |

| OSCIN                 | range                                               | OSC_2X = 1                                                      | 5       | 200  | IVII IZ |  |  |  |

| V <sub>OSCIN</sub>    | Reference input voltage                             | AC-coupled required <sup>(4)</sup>                              | 0.2     | 2    | Vpp     |  |  |  |

| F                     | Multiplier frequency (when multiplier               | Input range                                                     | 30      | 70   | MHz     |  |  |  |

| F <sub>MULT</sub>     | enabled)                                            | Output range                                                    | 180     | 250  | IVI□Z   |  |  |  |

<sup>3)</sup> Output power, spurs, and harmonics can vary based on board layout and components.

<sup>(4)</sup> For lower VCO frequencies, the N divider minimum value can limit the phase detector frequency.

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

|                                               | PARAMETER                                                   | TEST CONDITIONS                                  | MIN   | TYP  | MAX | UNIT   |  |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|-------|------|-----|--------|--|--|--|--|--|--|

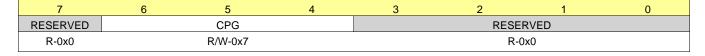

| LO SYNTHESIZER PHASE DETECTOR AND CHARGE PUMP |                                                             |                                                  |       |      |     |        |  |  |  |  |  |  |

|                                               |                                                             | Integer Mode (FRAC_ORDER = 0)                    | 0.125 |      | 400 |        |  |  |  |  |  |  |

| $F_{PD}$                                      | Phase detector frequency                                    | Fractional Mode (FRAC_ORDER = 1,2,3)             | 5     |      | 300 | MHz    |  |  |  |  |  |  |

|                                               |                                                             | Fractional Mode (FRAC_ORDER = 4)                 | 5     | 240  |     |        |  |  |  |  |  |  |

|                                               | Charge pump leakage current                                 | CPG = 0                                          |       | 15   |     | nA     |  |  |  |  |  |  |

|                                               |                                                             | CPG = 4                                          |       | 3    |     |        |  |  |  |  |  |  |

|                                               |                                                             | CPG = 1                                          |       | 6    |     |        |  |  |  |  |  |  |

| ICPOUT                                        | Effective charge pump current (sum of up and down currents) | CPG = 5                                          |       | 9    |     | mA     |  |  |  |  |  |  |

|                                               | up and down currents)                                       | CPG = 3                                          | 12    |      |     |        |  |  |  |  |  |  |

|                                               |                                                             | CPG = 7                                          |       | 15   |     |        |  |  |  |  |  |  |

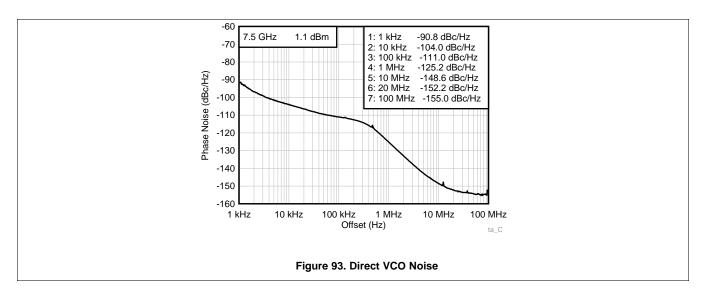

| PN <sub>1/F</sub>                             | Normalized PLL flicker noise                                | F <sub>PD</sub> = 100 MHz, F <sub>VCO</sub> = 12 |       | -129 |     | dBc/Hz |  |  |  |  |  |  |

| PN <sub>FLAT</sub>                            | Normalized PLL thermal noise floor                          | GHz <sup>(5)</sup>                               |       | -236 |     | dBc/Hz |  |  |  |  |  |  |

<sup>(5)</sup> The PLL noise contribution is measured using a clean reference and a wide loop bandwidth and is composed into flicker and flat components. PLL<sub>FLAT</sub> = PLL<sub>FOM</sub> + 20log(F<sub>VCO</sub> / F<sub>PD</sub>) + 10log(F<sub>PD</sub> / 1Hz). PLL<sub>FLICKER</sub> (offset) = PLL<sub>FLICKER</sub> NORM + 20log(F<sub>VCO</sub> / 1GHz) - 10log(offset frequency / 10kHz). Once these two components are found, the total PLL noise can be calculated as PLL<sub>NOISE</sub> = 10log(10<sup>PLLFLAT</sup> / 10 + 10<sup>PLLFLICKER</sup> / 10).

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER      |                                                                                                 | TEST CONDITIONS              | MIN TYP MAX | UNIT   |

|----------------|-------------------------------------------------------------------------------------------------|------------------------------|-------------|--------|

| LO SYNTHESIZE  | R VCO                                                                                           |                              |             |        |

|                |                                                                                                 | 8 GHz VCO, 10 kHz offset     | -80         |        |

|                |                                                                                                 | 8 GHz VCO, 100 kHz offset    | -107        |        |

|                |                                                                                                 | 8 GHz VCO, 1 MHz offset      | <b>–128</b> |        |

|                |                                                                                                 | 8 GHz VCO, 10 MHz offset     | -148        |        |

|                |                                                                                                 | 8 GHz VCO, 90 MHz offset     | <b>–157</b> |        |

|                |                                                                                                 | 9.2 GHz VCO, 10 kHz offset   | <b>–79</b>  |        |

|                |                                                                                                 | 9.2 GHz VCO, 100 kHz offset  | -105        |        |

|                |                                                                                                 | 9.2 GHz VCO, 1 MHz offset    | -127        |        |

|                |                                                                                                 | 9.2 GHz VCO, 10 MHz offset   | -147        | 1      |

|                |                                                                                                 | 9.2 GHz VCO, 90 MHz offset   | <b>–157</b> | 1      |

|                |                                                                                                 | 10.3 GHz VCO, 10 kHz offset  | <b>–77</b>  | 1      |

|                |                                                                                                 | 10.3 GHz VCO, 100 kHz offset | -104        | Ī      |

|                |                                                                                                 | 10.3 GHz VCO, 1 MHz offset   | -126        | Ī      |

|                |                                                                                                 | 10.3 GHz VCO, 10 MHz offset  | -147        | Ī      |

|                |                                                                                                 | 10.3 GHz VCO, 90 MHz offset  | -157        |        |

|                |                                                                                                 | 11.3 GHz VCO, 10 kHz offset  | <b>–76</b>  |        |

|                |                                                                                                 | 11.3 GHz VCO, 100 kHz offset | -103        |        |

| PNvco          | Open loop VCO phase noise                                                                       | 11.3 GHz VCO, 1 MHz offset   | -125        | dBc/Hz |

|                |                                                                                                 | 11.3 GHz VCO, 10 MHz offset  | -145        |        |

|                |                                                                                                 | 11.3 GHz VCO, 90 MHz offset  | -158        |        |

|                |                                                                                                 | 12.5 GHz VCO, 10 kHz offset  | <b>–74</b>  |        |

|                |                                                                                                 | 12.5 GHz VCO, 100 kHz offset | -100        |        |

|                |                                                                                                 | 12.5 GHz VCO, 1 MHz offset   | -123        |        |

|                |                                                                                                 | 12.5 GHz VCO, 10 MHz offset  | -144        |        |

|                |                                                                                                 | 12.5 GHz VCO, 90 MHz offset  | <b>–157</b> |        |

|                |                                                                                                 | 13.3 GHz VCO, 10 kHz offset  | <b>-73</b>  |        |

|                |                                                                                                 | 13.3 GHz VCO, 100 kHz offset | -100        |        |

|                |                                                                                                 | 13.3 GHz VCO, 1 MHz offset   | -122        |        |

|                |                                                                                                 | 13.3 GHz VCO, 10 MHz offset  | -143        |        |

|                |                                                                                                 | 13.3 GHz VCO, 90 MHz offset  | <b>–155</b> |        |

|                |                                                                                                 | 14.5 GHz VCO, 10 kHz offset  | -73         | 1      |

|                |                                                                                                 | 14.5 GHz VCO, 100 kHz offset | -99         | 1      |

|                |                                                                                                 | 14.5 GHz VCO, 1 MHz offset   | -121        | 1      |

|                |                                                                                                 | 14.5 GHz VCO, 10 MHz offset  | -143        | 1      |

|                |                                                                                                 | 14.5 GHz VCO, 90 MHz offset  | -152        | †      |

|                | VCO calibration speed, switch across                                                            | No assist                    | 50          |        |

| $t_{VCO\_CAL}$ | the entire frequency band, F <sub>OSC</sub> = 200 MHz, F <sub>PD</sub> = 100 MHz <sup>(6)</sup> | Close frequency              | 20          | μs     |

Submit Documentation Feedback

<sup>(6)</sup> See Application and Implementation for more details on the different VCO calibration modes.

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

|                  | PARAMETER                                                 | TEST CONDITIONS                | MIN           | TYP | MAX  | UNIT  |  |

|------------------|-----------------------------------------------------------|--------------------------------|---------------|-----|------|-------|--|

|                  |                                                           | 8 GHz                          |               | 89  |      |       |  |

|                  |                                                           | 9.2 GHz                        |               | 93  |      |       |  |

|                  |                                                           | 10.3 GHz                       |               | 110 |      | •     |  |

| K <sub>VCO</sub> | VCO gain                                                  | 11.3 GHz                       |               | 124 |      | MHz/V |  |

|                  |                                                           | 12.5 GHz                       |               | 189 |      |       |  |

|                  |                                                           | 13.3 GHz                       |               | 182 |      |       |  |

|                  |                                                           | 14.5 GHz                       |               | 205 |      |       |  |

| ΔT <sub>CL</sub> | Allowable temperature drift when VCO is not re-calibrated |                                |               | 125 |      | °C    |  |

| H2               | VCO second harmonic                                       | FVCO = 8 GHz, divider disabled |               | -30 |      | dBc   |  |

| H3               | VCO third harmonic                                        | FVCO = 8 GHz, divider disabled | -40           |     |      | abc   |  |

| SYNC PIN AND     | PHASE ALIGNMENT                                           |                                |               |     |      |       |  |

| Г                | Maximum usable OSCIN frequency                            | Category 3 (int LO mode)       | 0             |     | 100  |       |  |

| Foscin_sync      | with SYNC pin                                             | Category 1 or 2                | 0             |     | 1400 | MHz   |  |

| DIGITAL INTER    | FACE (SCK, SDI, CSB, MUXOUT, SYNC,                        | CE)                            |               |     |      |       |  |

| V <sub>IH</sub>  | High level input voltage                                  |                                | 1.4           |     | VCC  | V     |  |

| V <sub>IL</sub>  | Low level input voltage                                   |                                | 0             |     | 0.4  | V     |  |

| I <sub>IH</sub>  | High level input current                                  |                                | -50           |     | 50   | μΑ    |  |

| I <sub>IL</sub>  | Low level input current                                   |                                | -50           |     | 50   | μA    |  |

| V <sub>OH</sub>  | High level output voltage                                 | I <sub>L</sub> = -5 mA         | VCC -<br>0.55 |     |      | V     |  |

| V <sub>OL</sub>  | High level output current                                 | I <sub>L</sub> = 5 mA          |               |     | 0.55 | V     |  |

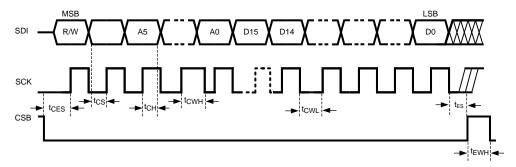

## 6.6 Timing Requirements

|                        |                                                  | MIN | NOM MAX | UNIT |

|------------------------|--------------------------------------------------|-----|---------|------|

| SYNC                   |                                                  |     |         |      |

| t <sub>SETUP</sub>     | Setup time for pin relative to OSCIN rising edge | 2.5 |         | ns   |

| t <sub>HOLD</sub>      | Hold time for pin relative to OSCIN rising edge  | 2   |         | ns   |

| DIGITAL W              | RITE INTERFACE <sup>(1)</sup>                    |     |         |      |

| F <sub>SPI_WRITE</sub> | SPI write speed                                  |     | 50      | MHz  |

| t <sub>ES</sub>        | Clock to enable low time                         | 5   |         | ns   |

| t <sub>CS</sub>        | Data to clock setup time                         | 2   |         | ns   |

| t <sub>CH</sub>        | Data to clock hold time                          | 2   |         | ns   |

| t <sub>CWH</sub>       | Clock pulse width high                           | 5   |         | ns   |

| t <sub>CWL</sub>       | Clock pulse width low                            | 10  |         | ns   |

| t <sub>CES</sub>       | Enable to clock setup time                       | 10  |         | ns   |

| t <sub>EWH</sub>       | Enable pulse width high                          | 10  |         | ns   |

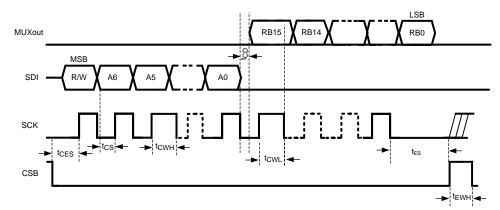

| DIGITAL R              | EADBACK INTERFACE <sup>(2)</sup>                 |     |         |      |

| F <sub>SPI_READ</sub>  | SPI readback speed                               |     | 50      | MHz  |

| t <sub>ES</sub>        | Clock to enable low time                         | 10  |         | ns   |

| t <sub>CS</sub>        | Clock to data wait time                          |     | 10      | ns   |

| t <sub>CWH</sub>       | Clock pulse width high                           | 10  |         | ns   |

| t <sub>CWL</sub>       | Clock pulse width low                            | 10  |         | ns   |

| t <sub>CES</sub>       | Enable to clock setup time                       | 10  |         | ns   |

<sup>(1)</sup> See Figure 1

Submit Documentation Feedback

<sup>(2)</sup> See Figure 2

# **Timing Requirements (continued)**

|                  |                         | MIN | NOM | MAX | UNIT | l |

|------------------|-------------------------|-----|-----|-----|------|---|

| t <sub>EWH</sub> | Enable pulse width high | 10  |     |     | ns   | Ì |

Figure 1. Serial Data Input Timing Diagram

There are several other considerations for writing on the SPI:

- The R/W bit must be set to 0.

- The signal on the SDI pin is clocked into a shift register on each rising edge of the SCK pin.

- The CSB must be held low for data to be clocked. Device ignores clock pulses if CSB is held high.

- The CSB transition from high to low must occur when SCK is low.

- When SCK and SDI lines are shared between devices, TI recommends holding the CSB line high on any devices besides the intended programming target.

Figure 2. Serial Data Readback Timing Diagram

There are several other considerations for SPI readback:

The R/W bit must be set to 1.

- The MUXOUT pin is always for the address portion of the transaction.

- The address on the SDI pin is clocked into a shift register on each rising edge of the SCK pin.

- The data portion of the transaction on the SDI line is always ignored.

- The data on the MUXOUT pin should be considered valid on each rising edge of the SCK pin, provided all timing requirements are met.

- All CSB considerations for SPI writing also apply to SPI readback.

# TEXAS INSTRUMENTS

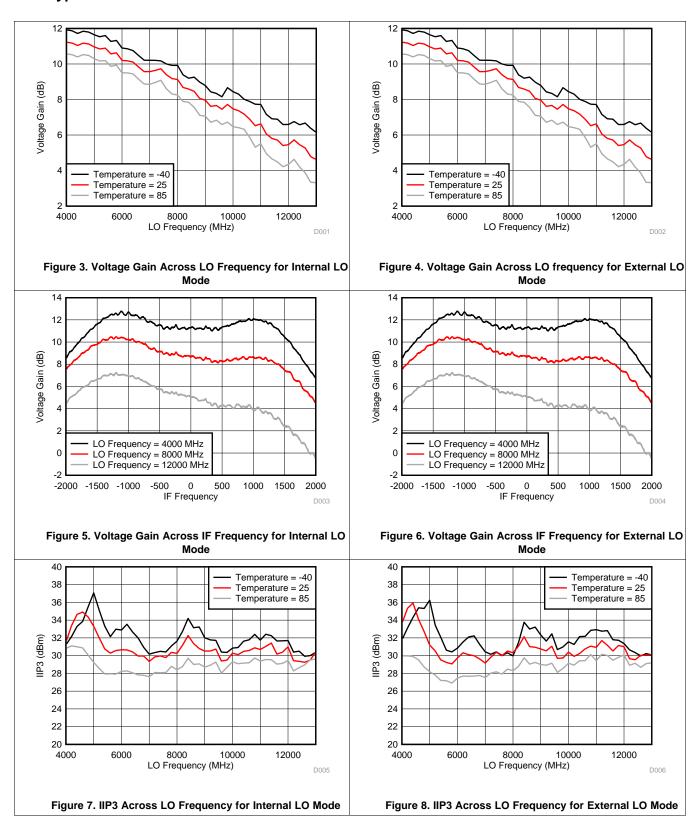

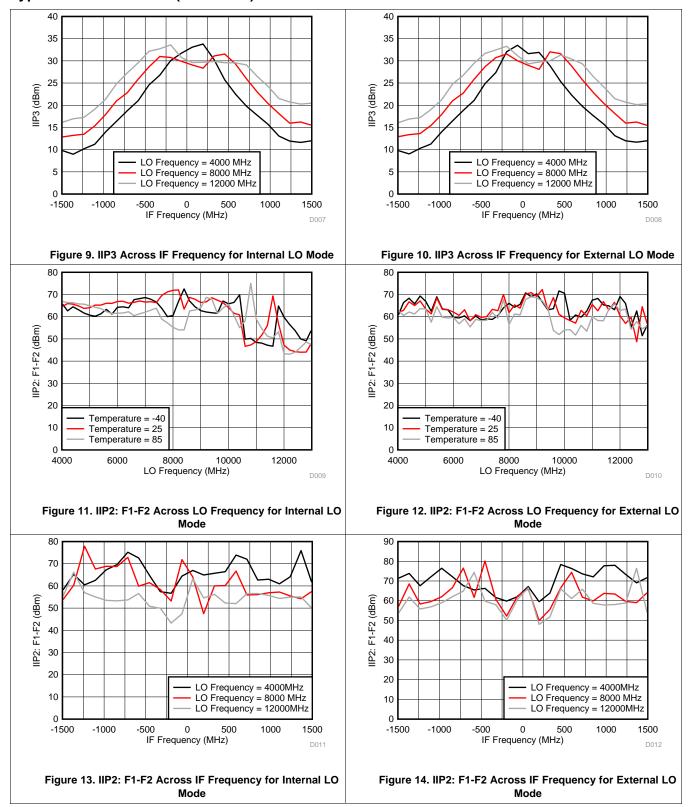

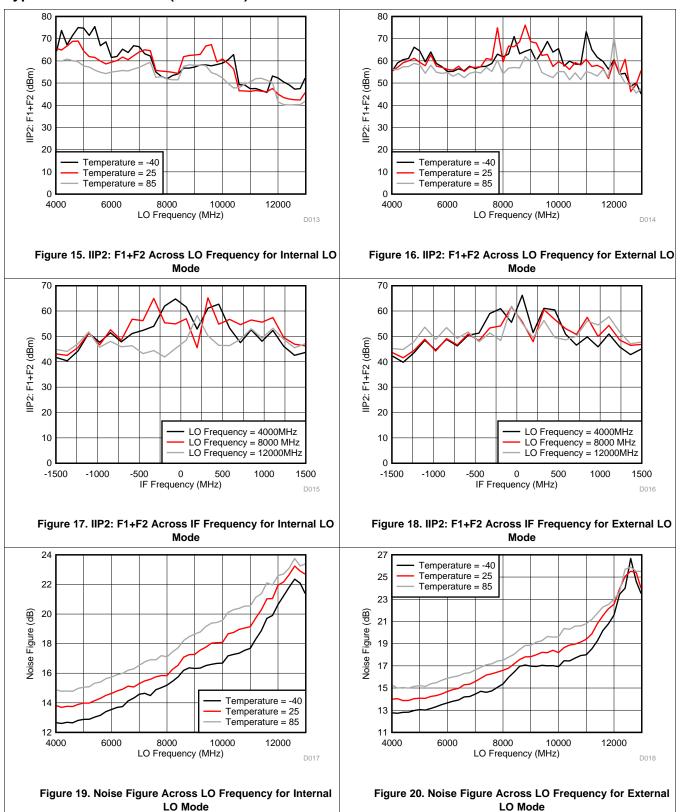

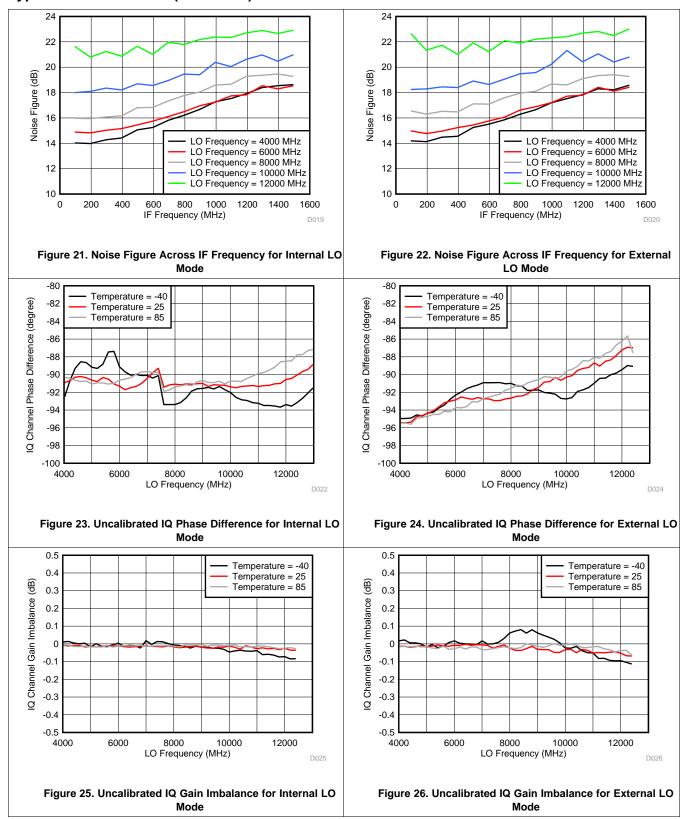

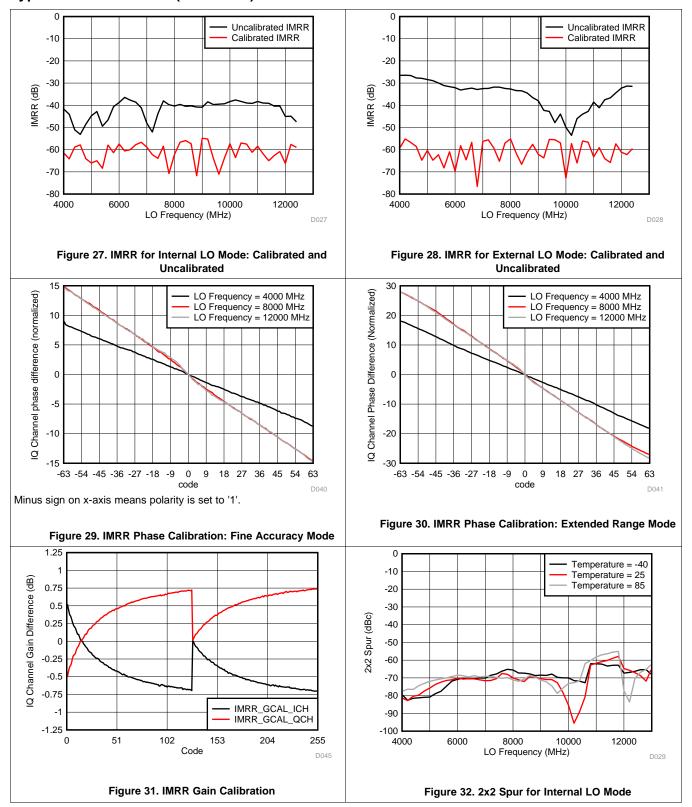

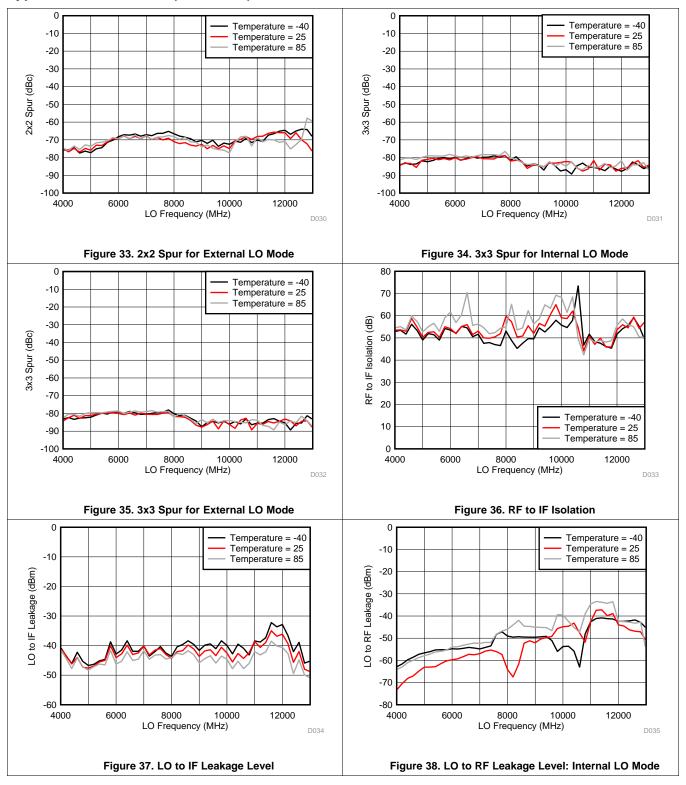

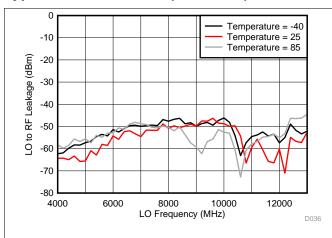

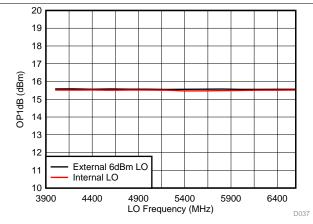

# 6.7 Typical Characteristics

Submit Documentation Feedback

# **Typical Characteristics (continued)**

Product Folder Links: LMX8410L

Submit Documentation Feedback

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Submit Documentation Feedback

# **Typical Characteristics (continued)**

Submit Documentation Feedback

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Submit Documentation Feedback

# **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

The LO frequency is capped at 6600MHz because IP1dB exceeds +10dBm when LO frequency goes beyond 6600MHz; The device can be damaged when input power is more than +10dBm.

Figure 39. LO to RF Leakage Level: External LO Mode

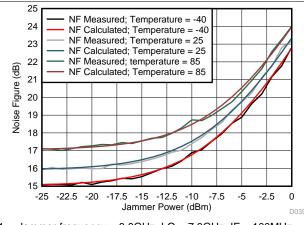

- 1. Jammer frequency = 8.8GHz, LO = 7.8GHz, IF = 100MHz.

- Internal LO phase noise values used for calculation at -40, 25, and 85 degrees C are -155, -154.5 and -154 dBc/Hz, separately.

Figure 41. Noise Figure with Jammer

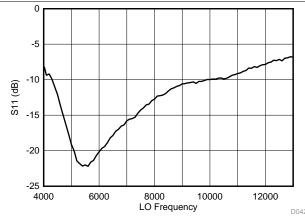

Figure 42. RF Port S11

Submit Documentation Feedback

# **Typical Characteristics (continued)**

Measurements are done at 25 degree C unless temperature is specified in the plots.

For measurements across LO frequency, IF = 65MHz, and LO injection type is high side injection. For measurements across IF frequency, high side injection is applied

For all measurements that require RF input, RF input power = -10 dBm unless otherwise specified.

For two-tone measurements, the separation between two tones is 17MHz.

For all measurements, internal 1.7V VCM is applied.

For all external LO mode measurements, LO power = +6 dBm.

IF baluns used for measurements are: ADT2-18+ from Mini-Circuits™.

LO balun used for measurements is: BIB-100G from PPM-Test™.

RF combiner used for measurements of IP2, IP3 and NF with jammer is: 4426-2 from Narda-MITEQ™.

All path losses are calibrated out.

# 7 Detailed Description

#### 7.1 Overview

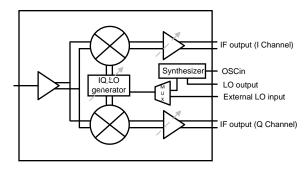

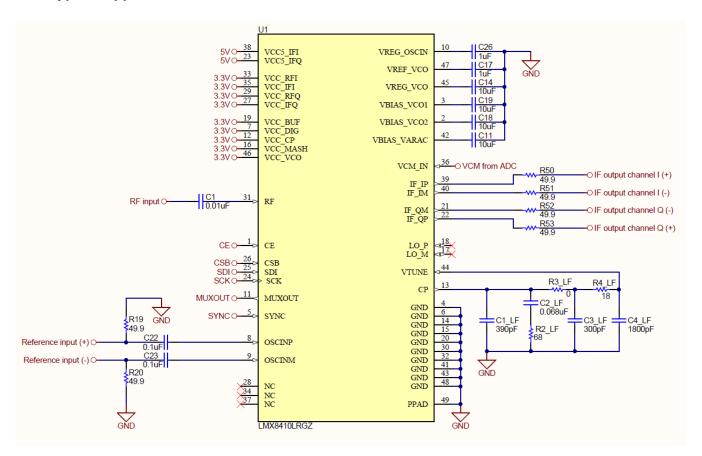

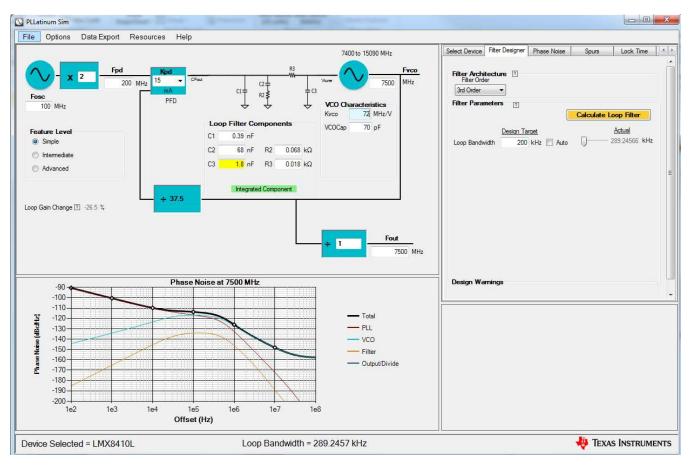

The LMX8410L is a high-performance I/Q demodulator with an RF input range of 4 to 10 GHz and an IF output range of DC to 1350 MHz. This device integrates many components to allow high system performance as well as simplified design. There is an integrated synthesizer that generates wide-band frequencies at very low phase noise, with signal carefully conditioned for driving the mixer LO port. The RF input is single ended, enabled by an integrated wide-band RF balun at the front end. The two mixers on each I/Q channel are highly linear with optimized filtering and interfacing with components on each port. The IF amplifier is a high gain and high linearity component, saving users from matching discrete amplifiers and being restricted by common mode voltages typically encountered when interfacing mixers and ADC's. In addition to high linearity and low noise performance, the LMX8410L comes equipped with many features to further optimize certain parameters. The automatic DC offset calibration is run by an internal automatic algorithm which will sense and tune the DC offset between the N and P sides of the differential signal of each IF amplifier, thus ensuring optimal performance when directly DC coupled to the ADC. The I/Q calibration knob allows tuning blocks within the mixer and IF amplifier to balance both the gain and the phase of the I/Q output signals, thus giving the user capability to adjust and achieve high image rejection. The internal synthesizer also has a feature of synchronization, which allows multiple LMX8410L designed in parallel to have synchronized LO signal phase.

# 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Device Configurations and Feature Description

### 7.3.1.1 RF, LO and IF Interfaces

#### 7.3.1.1.1 RF Interface

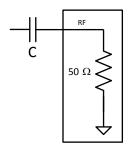

LMX8410 RF input stage provides a wideband input matching in complete RF frequency range. The RF interface requires an external DC block capacitor.

Figure 45. RF Interface

#### 7.3.1.1.2 LO Interface

LO interface for LMX8410 serves dual functionality:

- 1. Drive the VCO or channel divider output to pin LO M and LO P.

- 2. Inject external LO signal in external LO mode where on-chip synthesizer needs to be bypassed.

#### 7.3.1.1.2.1 LO Interface as Output Port

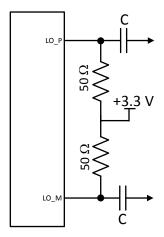

When LO interface operates as output port, it drives either VCO or Channel Divider output to the port. The device provides open collector output. Therefore, a pair of off-chip load resistors or inductors are needed in order to have LO output power.

Figure 46. LO Port Operating In Output Mode Requires Load Resistors Or Inductors

#### 7.3.1.1.2.2 LO Interface as Input Port

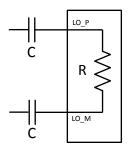

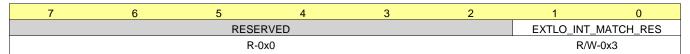

When LO interface operates as input port, the pull-up resistors or inductors must be removed. Device pins must be AC coupled with DC block. LO pins offer wideband differential 100 Ohm termination to enable port matching. The value of termination can be set to 100Ohm, 200Ohm or high impedance through register EXTLO\_INT\_MATCH\_RES (R123<1:0>). It is recommended to keep the termination setting to 100 ohm during external LO injection and to high impedance mode while LO is brought out from the device.

## **Feature Description (continued)**

Figure 47. LO Port Operating In Input Mode

#### 7.3.1.1.3 Baseband Interface

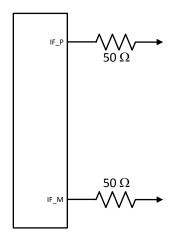

LMX8410 has a low impedance output driver capable of driving the resistive as well as capacitive loads. Therefore, a pair of 50 ohm off-chip resistors can be placed in both IF\_P and IF\_M paths to provide 1000hm differential matching if IF port matching is required.

Figure 48. IF Interface Requires External Resistors for 1000hm Differential Matching

# 7.3.1.2 Device Configurations Overview

Follow below steps to configure the device successfully.

#### 7.3.1.2.1 Initialize the Device

After the device is powered on, follow below setups in sequence.

- 1. Set R127 = 0x0003

- 2. Set R6 = 0x0100

- 3. Set R127 = 0x0000

- 4. Load device configuration bits.

#### 7.3.1.2.2 Configure LO Modes

Refer to *Table 5* to set up correct LO modes. After LO mode is configured, In case of internal LO mode, lock the integrated synthesizer and jump to *Perform DCOC (DC Offset Correction)*. In case of external LO mode, go to *Set Up External LO Clock*.

## Feature Description (continued)

#### 7.3.1.2.3 Set Up External LO Clock

Follow below steps to set up external LO clock:

- 1. Set external LO divider. Refer to State Machine Clock

- 2. Provide external LO signal on the pin.

- 3. Enable the divider by setting EXTLO\_CLK\_DIV\_EN (R81<7:6>) to 3. This step should be done only after valid external LO signal is driven on the pin.

- 4. Select SM clock source towards external LO driven SM clock by setting SM\_CLK\_SEL (R81<0>) = 1.

- 5. Wait for 100 usec before performing DCOC.

#### 7.3.1.2.4 Perform DCOC (DC Offset Correction)

Perform DCOC for both I and Q channels. Refer to DCOC (DC Offset Correction) for detailed instructions.

#### 7.3.1.2.5 Turn Off SM Clock

Turn off SM clock after DCOC to remove coupling spurs from clock signals.

- 1. In internal LO mode, set SM\_CLK\_EN (R2<10>) to 0.

- 2. In external LO mode, set EXTLO\_CLK\_DIV\_EN (R81<7:6>) to 0.

#### 7.3.1.2.6 Perform IMRR (Image Rejection Ratio) Calibration

Refer to Image Rejection Calibration for detailed instructions.

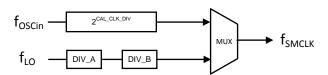

#### 7.3.1.3 State Machine Clock

The State machine clock can be derived, through a MUX, from division of OSCin frequency in internal LO mode or from division of external LO frequency in external LO mode. The upper bound for State machine clock is 200MHz while lower bound is 1MHz/10MHZ in internal/external LO modes. In external LO mode, two sets of dividers need to be programmed to set the right SM clock frequency. DIV\_A is an 8-state divider which drives DIV\_B. Input frequency to DIV\_B must be kept less than 1.4GHz. Recommended SM\_CLK frequency is 100MHz.

Figure 49. Block Diagram of SM Clock

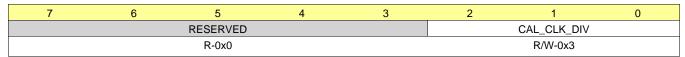

#### 7.3.1.3.1 Set Divider Values For Internal LO Mode

The value of divider in internal LO mode is 2<sup>\(\)</sup>(value of CAL\_CLK\_DIV).

# **Feature Description (continued)**

#### 7.3.1.3.2 Set Divider Values For External LO Mode

The divider for external LO mode is EXTLO\_DIV (R82<5:0>), where R82<5:3> sets DIV\_A and R82<2:0> sets DIV\_B. The value of DIV\_A should be set according to **Table 1**. The value of DIV\_B is 2^(value of R82<2:0>).

Table 1. DIV\_A Encoding

| EXTLO_DIV (R82<5:3>) | Division Value |

|----------------------|----------------|

| 000                  | /1             |

| 001                  | /2             |

| 010                  | /16            |

| 011                  | /4             |

| 100                  | /16            |

| 101                  | /16            |

| 110                  | /16            |

| 111                  | /8             |

# 7.3.1.4 DCOC (DC Offset Correction)

The DC offset of IF output can be automatically corrected by checking EN\_DCOC\_ICH\_LUT and EN\_DCOC\_QCH\_LUT

Figure 50. DC Offset Correction Diagram

#### 7.3.1.4.1 RF Input Power Restriction During DCOC

For best accuracy, power at the RF input of the LMX8410 should be kept below -50dBm during DCOC calibration. Additional isolation (~15dB) can be obtained by turning of LNA PD and LNA BIAS OFF.

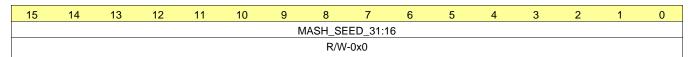

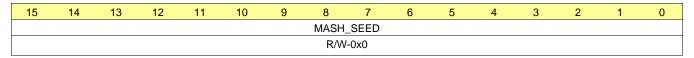

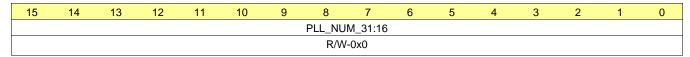

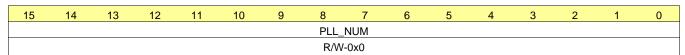

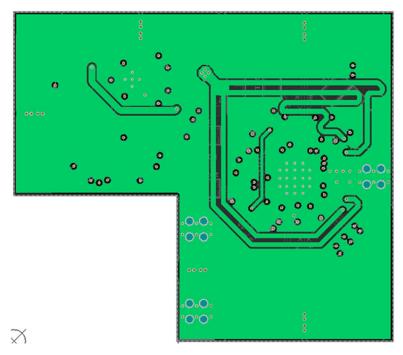

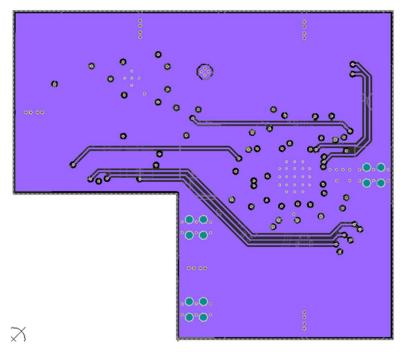

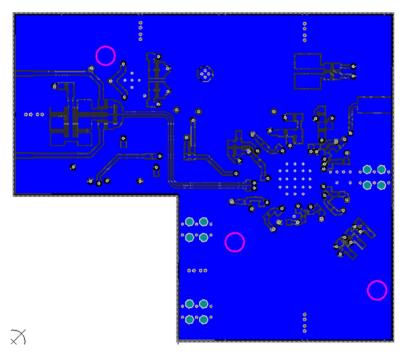

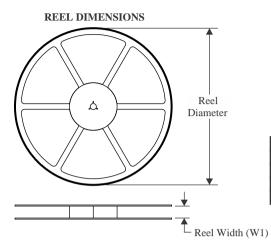

#### 7.3.1.4.2 Set Up DCOC Clock Divider