# TPS7H60x5-SP and TPS7H60x5-SEP Radiation-Hardness-Assured Half Bridge GaN FET Gate Drivers

### 1 Features

- · Radiation Performance:

- Radiation-hardness-assurance (RHA) up to total ionizing dose (TID) of 100krad(Si)

- Single-event transient (SET), single-event burnout (SEB), and single-event gate rupture (SEGR) immune to

- linear energy transfer (LET) = 75MeV-cm<sup>2</sup>/mg

- Single-event transient (SET) and single-event functional interrupt (SEFI) characterized up to LET = 75MeV-cm<sup>2</sup>/mg

- 1.3A peak source, 2.5A peak sink current

- · Two operational modes:

- Single PWM input with adjustable dead time

- Two independent inputs

- Selectable input interlock protection in independent input mode

- Split outputs for adjustable turn-on and turn-off times

- 30ns typical propagation delay in independent input mode

- 5.5ns typical delay matching

- Plastic packages outgas tested per ASTM E595

- Available in military temperature range (–55°C to 125°C)

## 2 Applications

- · Space satellite power supplies

- Motor drives

- · Reaction wheels

- · Communications payload

- Optical imaging payload

- · Satellite electrical power system

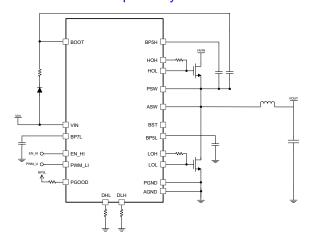

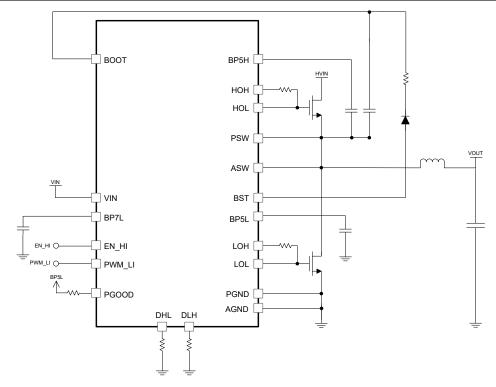

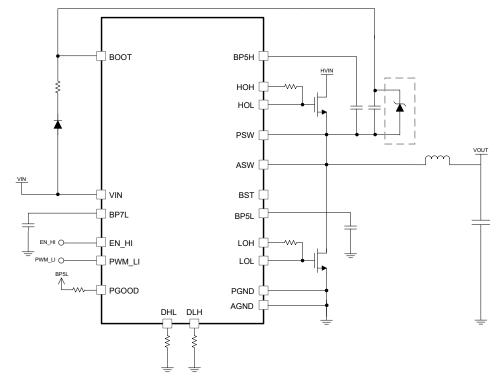

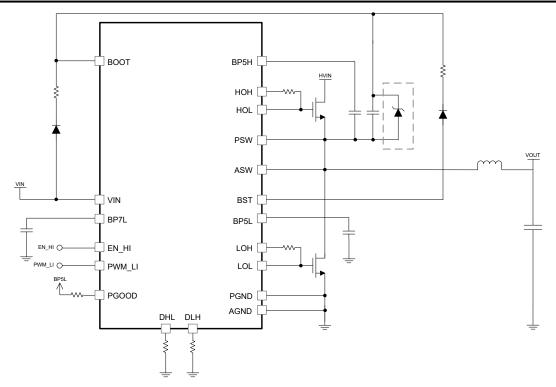

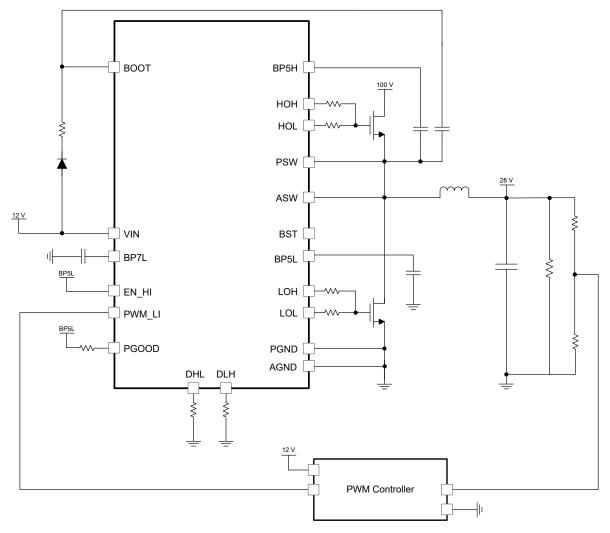

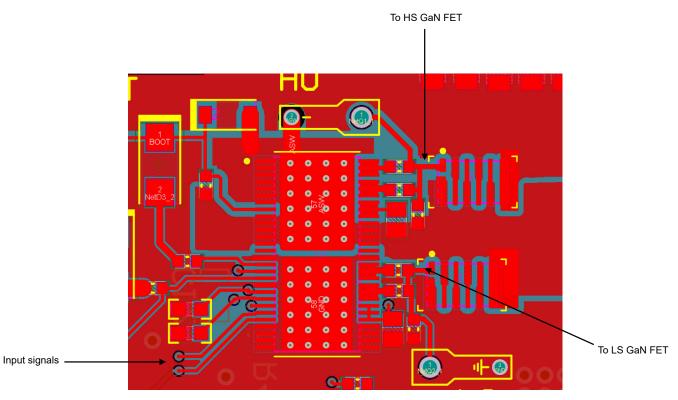

Simplified Application Diagram

## 3 Description

The TPS7H60x5 series of radiation-hardness-assured (RHA) gallium nitride (GaN) field effect transistor (FET) gate drivers is designed for high frequency, high efficiency, and high current applications. The series consists of the TPS7H6005 (200V rating), TPS7H6015 (60V rating), and the TPS7H6025 (22V rating). Each of these devices has a 56-pin HTSSOP plastic package, and availability in both the QMLP and Space Enhanced Plastic (SEP) grades. The drivers feature adjustable dead time capability, small 30ns propagation delay and 5.5ns high-side and low-side matching. These parts also include internal high-side and low-side LDOs which ensure a drive voltage of 5V regardless of supply voltage. The TPS7H60x5 drivers all have split-gate outputs, providing flexibility to adjust the turn-on and turn-off strength of the outputs independently.

The TPS7H60x5 drivers feature two control input modes: independent input mode (IIM) and PWM mode. In IIM each of the outputs is controlled by a dedicated input. In PWM mode, two complementary outputs signals are generated from a single input and the user can adjust the dead time for each edge.

The gate drivers also offer user configurable input interlock in independent input mode as anti-shoot through protection. Input interlock disallows turn-on of both outputs when both inputs are on simultaneously. The user has the option to enable or disable this protection in independent input mode, which allows the driver to be used in a number of different converter configurations. The drivers can also be utilized for both half-bridge and dual-low side converter applications.

#### **Device Information**

| PART NUMBER <sup>(1)</sup>     | GRADE    | BODY SIZE(2)                     |

|--------------------------------|----------|----------------------------------|

| 5962R2220104PYE <sup>(4)</sup> | QMLP-RHA |                                  |

| TPS7H6005MDCATSEP              | SEP      |                                  |

| 5962R2220105PYE <sup>(4)</sup> | QMLP-RHA | 56-pin plastic<br>6.1mm × 14.0mm |

| TPS7H6015MDCATSEP(5)           | SEP      | Mass = 119mg <sup>(3)</sup>      |

| 5962R2220106PYE <sup>(4)</sup> | QMLP-RHA |                                  |

| TPS7H6025MDCATSEP(5)           | SEP      |                                  |

- (1) For additional information view the *Device Options* table.

- (2) The body size (length × width) is a nominal value and does not include pins.

- (3) Mass is a nominal value.

- (4) Product preview.

- (5) Advance information.

# **Table of Contents**

| 1 Features1                           | 8.3 Feature Description23                              |

|---------------------------------------|--------------------------------------------------------|

| 2 Applications1                       | 8.4 Device Functional Modes31                          |

| 3 Description1                        | 9 Application and Implementation32                     |

| 4 Device Comparison Table3            | 9.1 Application Information32                          |

| 5 Device Options Table4               | 9.2 Typical Application33                              |

| 6 Pin Configuration and Functions5    | 9.3 Power Supply Recommendations37                     |

| 7 Specifications8                     | 9.4 Layout38                                           |

| 7.1 Absolute Maximum Ratings8         | 10 Device and Documentation Support40                  |

| 7.2 ESD Ratings8                      | 10.1 Documentation Support40                           |

| 7.3 Recommended Operating Conditions9 | 10.2 Receiving Notification of Documentation Updates40 |

| 7.4 Thermal Information9              | 10.3 Support Resources40                               |

| 7.5 Electrical Characteristics10      | 10.4 Trademarks40                                      |

| 7.6 Switching Characteristics12       | 10.5 Electrostatic Discharge Caution40                 |

| 7.7 Quality Conformance Inspection13  | 10.6 Glossary40                                        |

| 7.8 Typical Characteristics14         | 11 Revision History40                                  |

| 8 Detailed Description22              | 12 Mechanical, Packaging, and Orderable                |

| 8.1 Overview22                        | Information4                                           |

| 8.2 Functional Block Diagram22        |                                                        |

|                                       |                                                        |

# **4 Device Comparison Table**

| DEVICE                       | ABSOLUTE MAXIMUM VOLTAGE(1) | RECOMMENDED OPERATING VOLTAGE <sup>(1)</sup> |

|------------------------------|-----------------------------|----------------------------------------------|

| TPS7H6005 <sup>(2)</sup>     | 200V                        | 150V                                         |

| TPS7H6015 <sup>(2) (3)</sup> | 60V                         | 45V                                          |

| TPS7H6025 <sup>(2) (3)</sup> | 22V                         | 14V                                          |

- (1) This represents the "SW to GND" voltage rating of the devices as shown in the Specifications section.

- (2) Product preview (QMLP).

- (3) Advance information (SÉP).

# **5 Device Options Table**

| GENERIC PART<br>NUMBER | RADIATION RATING(1)                                                            | GRADE <sup>(2)</sup>   | PACKAGE      | ORDERABLE PART<br>NUMBER         |

|------------------------|--------------------------------------------------------------------------------|------------------------|--------------|----------------------------------|

| TPS7H6005-SP           | TID up to 100krad(Si) RLAT and DSEE free up to LET = 75MeV-cm <sup>2</sup> /mg | QMLP-RHA               |              | 5962R2220104PYE <sup>(3)</sup>   |

| TPS7H6005-SEP          | TID up to 50krad(Si) RLAT and DSEE free up to LET = 43MeV-cm <sup>2</sup> /mg  | Space Enhanced Plastic |              | TPS7H6005MDCATSEP                |

| TPS7H6015-SP           | TID up to 100krad(Si) RLAT and DSEE free up to LET = 75MeV-cm²/mg              | QMLP-RHA               | 56-pin TSSOP | 5962R2220105PYE <sup>(3)</sup>   |

| TPS7H6015-SEP          | TID up to 50krad(Si) RLAT and DSEE free up to LET = 43MeV-cm²/mg               | Space Enhanced Plastic | DCA          | TPS7H6015MDCATSEP <sup>(4)</sup> |

| TPS7H6025-SP           | TID up to 100krad(Si) RLAT and DSEE free up to LET = 75MeV-cm <sup>2</sup> /mg | QMLP-RHA               |              | 5962R2220106PYE <sup>(3)</sup>   |

| TPS7H6025-SEP          | TID up to 50krad(Si) RLAT and DSEE free up to LET = 43MeV-cm²/mg               | Space Enhanced Plastic |              | TPS7H6025MDCATSEP <sup>(4)</sup> |

<sup>(1)</sup> TID is total ionizing dose and DSEE is destructive single event effects. Additional information is available in the associated TID and SEE radiation reports for the device.

<sup>(2)</sup> For additional information about part grade, view SLYB235.

<sup>(3)</sup> Product preview.

<sup>(4)</sup> Advance information.

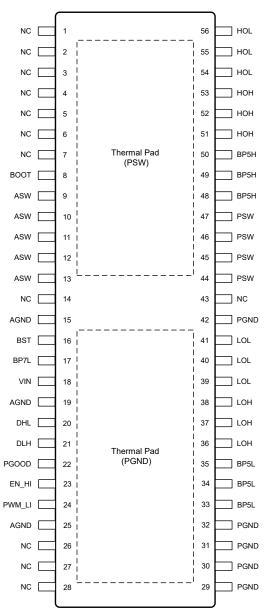

# **6 Pin Configuration and Functions**

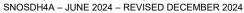

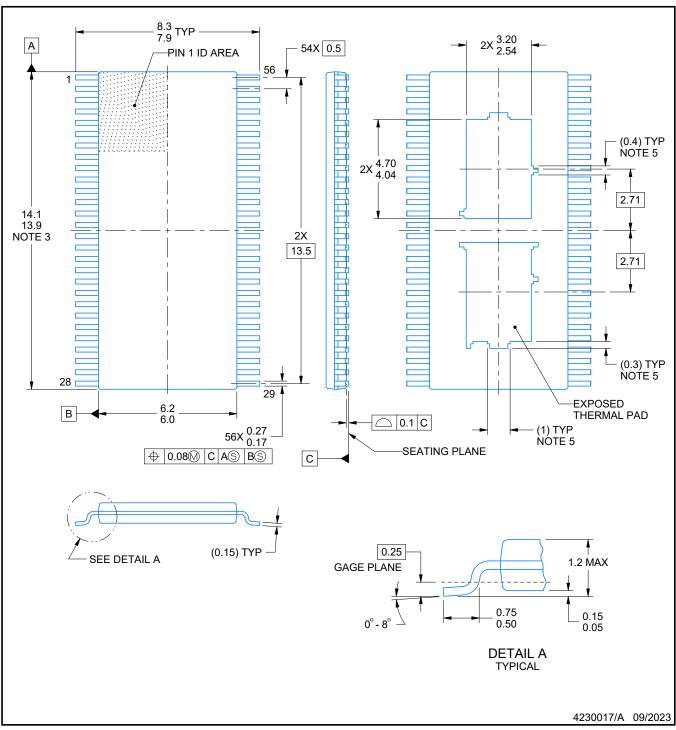

Figure 6-1. DCA Package 56-Pin TSSOP (Top View)

Table 6-1. Pin Functions

|        | PIN              | <b>UO</b> (1) | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

|--------|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | BER NAME  BOOT I | DESCRIPTION   |                                                                                                                                                                                                                                                                                                                      |

| 8      | воот             | I             | Input voltage supply of the high-side linear regulator. The external bootstrap capacitor is placed between BOOT and ASW. The cathode of the external bootstrap diode is connected to this pin. A Zener diode clamp may be needed between BOOT and ASW in order to not exceed the absolute maximum electrical rating. |

| 9–13   | ASW              | _             | High-side driver signal return. ASW(9) is internally connected to PSW and the high-side thermal pad. Connect ASW(10-13) to ASW externally.                                                                                                                                                                           |

## Table 6-1. Pin Functions (continued)

| PIN        |        | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER     | NAME   |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 16         | BST    | 0                  | For bootstrap charging that utilizes the internal bootstrap switch, this pin serves as the bootstrap diode anode connection point. The external high-side bootstrap capacitor can be charged through this pin using the input voltage applied to VIN, internal bootstrap switch, and external bootstrap diode(s).                                                                                                                            |  |  |

| 17         | BP7L   | 0                  | Low-side 7V linear regulator output. A minimum of 1µF capacitance is required from BP7L to AGND.                                                                                                                                                                                                                                                                                                                                             |  |  |

| 18         | VIN    | 1                  | Gate driver input voltage supply. Input voltage range is from 10V to 14V. This pin serves as the input to the low-side linear regulators and the internal bootstrap switch. For bootstrap charging directly from the input voltage, VIN also serves as the bootstrap diode anode connection point.                                                                                                                                           |  |  |

| 15, 19, 25 | AGND   | _                  | Low-side driver signal return. AGND(15) and AGND(19) are internally connected to PGND and the low-side thermal pad. Connect AGND(25) to AGND externally.                                                                                                                                                                                                                                                                                     |  |  |

| 20         | DHL    | ı                  | High-side to low-side dead time set. In PWM mode, a resistor from DHL to AGND sets the dead time between the high-side turn-off and low-side turn-on. In independent input mode (IIM), DHL is used to configure the input interlock protection of the driver. DHL is connected to BP5L in IIM with interlock enabled. A resistor valued between $100k\Omega$ and $220k\Omega$ is connected from DHL to AGND for IIM with interlock disabled. |  |  |

| 21         | DLH    | ı                  | Low-side to high-side dead time set. In PWM mode, a resistor from DLH to AGND sets the dead time between the low-side turn-off and high-side turn-on. In independent input mode (IIM), DLH is used to configure the input interlock protection of the driver. A resistor valued between $100k\Omega$ and $220k\Omega$ is connected from DLH to AGND for IIM with interlock enabled. DLH is connected to BP5L in IIM with interlock disabled. |  |  |

| 22         | PGOOD  | 0                  | Power good pin. Asserts low when any of the low-side internal linear regulators or VIN goes into undervoltage lockout. Requires a $10k\Omega$ pull-up resistor to BP5L.                                                                                                                                                                                                                                                                      |  |  |

| 23         | EN_HI  | I                  | Enable input or high-side driver control input. In PWM mode this is used as an enable pin. In independent input mode (IIM) this serves as the control input for the high-side driver.                                                                                                                                                                                                                                                        |  |  |

| 24         | PWM_LI | I                  | PWM input or low-side driver control input. In PWM mode this is used as the PWM input to the gate driver. In independent input mode (IIM) this serves as the control input for the low-side driver.                                                                                                                                                                                                                                          |  |  |

| 29–32, 42  | PGND   | _                  | Low-side power ground. Connect to the source of the low-side GaN FET. Internally connected to AGND and low-side thermal pad. Connect to AGND at printed circuit board level.                                                                                                                                                                                                                                                                 |  |  |

| 33–35      | BP5L   | 0                  | Low-side 5V linear regulator output. A minimum of 1µF capacitance is required from BP5L to PGND.                                                                                                                                                                                                                                                                                                                                             |  |  |

| 36–38      | LOH    | 0                  | Low-side driver source current ouput. Connect to the gate of low-side GaN FET with short, low inductance path. A resistor between LOH and the gate of the GaN FET can be used to adjust the turn-on speed.                                                                                                                                                                                                                                   |  |  |

| 39–41      | LOL    | 0                  | Low-side driver sink current output. Connect to the gate of the low-side GaN FET with short, low inductance path. A resistor between LOL and the gate of the GaN FET can be used to adjust the turn-off speed.                                                                                                                                                                                                                               |  |  |

| 44–47      | PSW    | _                  | Switch node connection. Connect to the source of the high-side GaN FET. Internally connected to ASW and high-side thermal pad. Connect to ASW at printed circuit board level.                                                                                                                                                                                                                                                                |  |  |

| 48–50      | BP5H   | 0                  | High-side 5V linear regulator output. A minimum of 1µF capacitance is required from BP5H to PSW.                                                                                                                                                                                                                                                                                                                                             |  |  |

| 51–53      | НОН    | 0                  | High-side driver source current output. Connect to the gate of the high-side GaN FET with short, low inductance path. A resistor between HOH and the gate of the GaN FET can be used to adjust the turn-on speed.                                                                                                                                                                                                                            |  |  |

| 54–56      | HOL    | 0                  | High-side driver sink current output. Connect to the gate of the high-side GaN FET with short, low inductance path. A resistor between HOL and the gate of the GaN FET can be used to adjust the turn-off speed.                                                                                                                                                                                                                             |  |  |

## **Table 6-1. Pin Functions (continued)**

|                        | PIN      | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER                 | NAME     | 1/0                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1–7, 14, 26–<br>28, 43 | NC       | _                  | No connect. These pins are not connected internally. Pins 1-7 and 26-28 can be left unconnected or connected to the respective reference voltage (ASW or AGND) in order to avoid floating metal and prevent charge buildup. For pins 14 and 43, these are recommended to be left unconnected in order to meet the requirements of IEC-60664 for creepage and clearance. Ultimately, the connections of pins 14 and 43 are left to the discretion of the user based on the specific creepage and clearance guidelines that are selected for the design. |

| _                      | PSW PAD  | _                  | High-side thermal pad. Internally connected to ASW(9) and PSW. Should be connected to ASW pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| _                      | PGND PAD | _                  | Low-side thermal pad. Internally connected to AGND(15), AGND(19) and PGND. Should be connected to AGND pins.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

(1) I = Input, O = Output, I/O = Input or Output, — = Other

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating temperature (unless otherwise noted)(1)

|                                                   | MIN                   | MAX                     | UNIT |

|---------------------------------------------------|-----------------------|-------------------------|------|

| VIN to AGND                                       | -0.3                  | 16                      | V    |

| BP7L to AGND                                      | -0.3                  | 8                       | V    |

| BP5L to AGND                                      | -0.3                  | 7                       | V    |

| BP5H to SW                                        | -0.3                  | 7                       | V    |

| BOOT to SW                                        | -0.3                  | V <sub>SW</sub> + 16    | V    |

| EN_HI                                             | -0.3                  | 16                      | V    |

| PWM_LI                                            | -0.3                  | 16                      | V    |

| DHL, DLH                                          | -0.3                  | V <sub>BP5L</sub> + 0.3 | V    |

| LOH, LOL                                          | -0.3                  | V <sub>BP5L</sub> + 0.3 | V    |

| HOH, HOL                                          | V <sub>SW</sub> – 0.3 | V <sub>BP5H</sub> + 0.3 | V    |

| PGOOD                                             | -0.3                  | V <sub>BP5L</sub> + 0.3 | V    |

| SW to AGND (TPS7H6005)                            | -10                   | 200                     | V    |

| SW to AGND (TPS7H6015)                            | -10                   | 60                      | V    |

| SW to AGND (TPS7H6025)                            | -10                   | 22                      | V    |

| BOOT to AGND (TPS7H6005)                          | 0                     | 216                     | V    |

| BOOT to AGND (TPS7H6015)                          | 0                     | 76                      | V    |

| BOOT to AGND (TPS7H6025)                          | 0                     | 38                      | V    |

| BST to AGND                                       | -0.3                  | 16                      | V    |

| BST current (3µs transient pulse, non-repetitive) |                       | 4                       | Α    |

| Junction temperature, T <sub>J</sub>              | -55                   | 150                     | °C   |

| Storage temperature, T <sub>stg</sub>             | -65                   | 150                     | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |                         |                                                                                 | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

|                                | MIN                 | NOM MAX              | UNIT |

|--------------------------------|---------------------|----------------------|------|

| VIN to AGND                    | 10                  | 14                   | V    |

| EN_HI                          | 0                   | 14                   | V    |

| PWM_LI                         | 0                   | 14                   | V    |

| BOOT to SW                     | V <sub>SW</sub> + 8 | V <sub>SW</sub> + 14 | V    |

| SW (TPS7H6005)                 | -10                 | 150                  | V    |

| SW (TPS7H6015)                 | -10                 | 45                   | V    |

| SW (TPS7H6025)                 | -10                 | 14                   | V    |

| SW slew rate                   |                     | 100                  | V/ns |

| VIN slew rate                  |                     | 0.03                 | V/µs |

| PWM_LI, EN_HI slew rate        | 2                   |                      | V/µs |

| Operating junction temperature | <b>–</b> 55         | 125                  | °C   |

## 7.4 Thermal Information

|                       |                                                                                                                               | TPS7H60x5 |      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------|------|

|                       | Junction-to-case (top) thermal resistance  Junction-to-case (bottom) thermal resistance  Junction-to-board thermal resistance | HTSSOP    | UNIT |

|                       |                                                                                                                               | 56 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance                                                                                        | 21.4      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                                                                                     | 9.2       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                                                                                  | 0.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                                                                                          | 5.4       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter                                                                                    | 0.3       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter                                                                                  | 5.3       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

Specifications are over ambient temperature operating range  $T_A = -55^{\circ}C$  to 125°C, VIN = 10V to 14V,  $V_{BP5L} = V_{BP5H} = 5V$ , and no load on LOH, LOL, HOH, and HOL (unless otherwise noted).

|                           | PARAMETER                                  | TEST CONDI                                       | TIONS                       | SUBGROUP <sup>(1)</sup> | MIN  | TYP  | MAX   | UNIT |

|---------------------------|--------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------|------|------|-------|------|

| SUPPLY C                  | CURRENTS                                   |                                                  |                             |                         |      |      |       |      |

| l                         | Low-side quiescent current                 | VIN = 12V, BOOT = 10V                            | MODE = PWM,<br>EN = 0V      | 1, 2, 3                 |      | 5    | 6.8   | mA   |

| I <sub>QLS</sub>          | Low-side quiescent current                 | VIN = 12V, BOOT = 10V                            | MODE = IIM, LI<br>= HI = 0V | 1, 2, 3                 |      | 5    | 8     | mA   |

| l                         | High-side guiescent current                | VIN = 12V, BOOT = 10V                            | MODE = PWM,<br>EN = 0V      | 1, 2, 3                 |      | 4    | 6.3   | mA   |

| I <sub>QHS</sub>          | High-side quiescent current                | M                                                | MODE = IIM, LI<br>= HI = 0V | 1, 2, 3                 |      | 4    | 6.3   | IIIA |

| QBG                       | BOOT to AGND quiescent current (TPS7H6005) | SW = 100V, BOOT = 110V                           | ,                           |                         |      | 20   |       | μΑ   |

| $I_{QBG}$                 | BOOT to AGND quiescent current (TPS7H6015) | SW = 28V, BOOT = 38V                             |                             |                         |      | 15   |       | μΑ   |

| $I_{QBG}$                 | BOOT to AGND quiescent current (TPS7H6025) | SW = 12V, BOOT = 22V                             |                             |                         |      | 10   |       | μΑ   |

| I <sub>OP_BG</sub>        | BOOT to AGND operating current (TPS7H6005) | SW = 100V, BOOT = 110V                           | ,                           |                         |      | 20   |       | μΑ   |

| I <sub>OP_BG</sub>        | BOOT to AGND operating current (TPS7H6015) | SW = 28V, BOOT = 38V                             |                             |                         |      | 15   |       | μA   |

| I <sub>OP_BG</sub>        | BOOT to AGND operating current (TPS7H6025) | SW = 12V, BOOT = 22V                             |                             |                         |      | 10   |       | μΑ   |

|                           |                                            |                                                  | f = 500kHz                  | 1, 2, 3                 |      | 6    | 9     |      |

|                           |                                            | MODE = PWM, no load                              | f = 1MHz                    | 1, 2, 3                 |      | 8    | 11    |      |

|                           |                                            | for LOL and LOH                                  | f = 2MHz                    | 1, 2, 3                 |      | 12   | 16    |      |

| OP_LS                     | l: d                                       |                                                  | f = 5MHz                    | 1, 2, 3                 |      | 20   | 30    | mA   |

|                           | Low-side operating current                 | MODE = IIM, no load for LOL and LOH              | f = 500kHz                  | 1, 2, 3                 |      | 6    | 9     |      |

|                           |                                            |                                                  | f = 1MHz                    | 1, 2, 3                 |      | 8    | 12    |      |

|                           |                                            |                                                  | f = 2MHz                    | 1, 2, 3                 |      | 11   | 17    |      |

|                           |                                            |                                                  | f = 5MHz                    | 1, 2, 3                 |      | 20   | 30    |      |

|                           |                                            | MODE = PWM, no load for HOL and HOH              | f = 500kHz                  | 1, 2, 3                 |      | 5    | 6.5   |      |

|                           |                                            |                                                  | f = 1MHz                    | 1, 2, 3                 |      | 5.3  | 8     |      |

|                           |                                            |                                                  | f = 2MHz                    | 1, 2, 3                 |      | 7    | 10.5  |      |

|                           |                                            |                                                  | f = 5MHz                    | 1, 2, 3                 |      | 13   | 19    |      |

| I <sub>OP_HS</sub>        | High-side operating current                |                                                  | f = 500kHz                  | 1, 2, 3                 |      | 4.5  | 6.5   | mA   |

|                           |                                            | MODE = IIM, no load for                          | f = 1MHz                    | 1, 2, 3                 |      | 5.3  | 8     |      |

|                           |                                            | HOL and HOH                                      | f = 2MHz                    | 1, 2, 3                 |      | 7    | 10.5  |      |

|                           |                                            |                                                  | f = 5MHz                    | 1, 2, 3                 |      | 11.7 | 15    |      |

| LOW-SIDE                  | E TO HIGH-SIDE CAPACITANCE                 | 1                                                | 1                           | 1                       |      | ,    |       |      |

|                           | Low-side to high-side capacitance          | Low-side pins shorted toge pins shorted together | ether and high-side         |                         |      | 6    |       | pF   |

| GATE DRI                  | IVER                                       |                                                  |                             |                         |      |      |       |      |

| V <sub>OL</sub>           | Low-level output voltage                   | I <sub>OL</sub> = 100mA                          |                             | 1, 2, 3                 |      | 0.07 | 0.15  | V    |

| BP5x –<br>V <sub>OH</sub> | High-level output voltage                  | I <sub>OH</sub> = 100mA                          |                             | 1, 2, 3                 |      | 0.13 | 0.3   | V    |

| I <sub>OH</sub>           | Peak source current                        | HOH, LOH = 0V, BP5x = 5                          | V                           | 1, 2, 3                 | 0.7  | 1.3  | 2.3   | Α    |

| I <sub>OL</sub>           | Peak sink current                          | HOL, LOL = 5V, BP5x = 5V                         | /                           | 1, 2, 3                 | 1.6  | 2.5  | 4.6   | Α    |

|                           | L REGULATORS                               | 1                                                |                             |                         |      | ,    |       |      |

| V <sub>BP5L</sub>         | Low-side 5V regulator output voltage       | C <sub>BP5L</sub> = 1µF                          |                             | 1, 2, 3                 | 4.75 | 5.0  | 5.175 | V    |

|                           | Required BP5L output capacitor (2)         | -                                                |                             | 1, 2, 3                 | 1    |      |       | μF   |

| V <sub>BP5H</sub>         | High-side 5V regulator output voltage      | C <sub>BP5H</sub> = 1μF                          |                             | 1, 2, 3                 | 4.75 | 5.0  | 5.175 |      |

| 51 011                    | Required BP5H output capacitor (2)         | 5.011                                            |                             | . ,                     | 1    | -    | -     | μF   |

## 7.5 Electrical Characteristics (continued)

Specifications are over ambient temperature operating range  $T_A = -55^{\circ}C$  to 125°C, VIN = 10V to 14V,  $V_{BP5L} = V_{BP5H} = 5V$ , and no load on LOH, LOL, HOH, and HOL (unless otherwise noted).

|                     | PARAMETER                                   | TEST CONDIT                                                      | TIONS        | SUBGROUP <sup>(1)</sup> | MIN  | TYP  | MAX   | UNIT |

|---------------------|---------------------------------------------|------------------------------------------------------------------|--------------|-------------------------|------|------|-------|------|

| V <sub>BP7L</sub>   | 7V regulator output voltage                 |                                                                  |              | 1, 2, 3                 | 6.65 | 7    | 7.35  | V    |

|                     | Required BP7L output capacitor (2)          |                                                                  |              |                         | 1    |      |       | μF   |

| UNDERVO             | OLTAGE PROTECTION                           |                                                                  |              |                         |      |      | ·     |      |

| BP5H <sub>R</sub>   | BP5H UVLO rising threshold                  | C <sub>BP5H</sub> = 1µF                                          |              | 1, 2, 3                 | 4.0  | 4.25 | 4.5   | V    |

| BP5H <sub>F</sub>   | BP5H UVLO falling threshold                 | C <sub>BP5H</sub> = 1µF                                          |              | 1, 2, 3                 | 3.8  | 4.05 | 4.3   | V    |

| BP5H <sub>H</sub>   | BP5H UVLO hysteresis                        | C <sub>BP5H</sub> = 1µF                                          |              |                         |      | 0.2  |       | V    |

| BP5L <sub>R</sub>   | BP5L UVLO rising threshold                  | C <sub>BP5L</sub> = 1µF                                          |              | 1, 2, 3                 | 4.0  | 4.25 | 4.5   | V    |

| BP5L <sub>F</sub>   | BP5L UVLO falling threshold                 | C <sub>BP5L</sub> = 1µF                                          |              | 1, 2, 3                 | 3.8  | 4.05 | 4.3   | V    |

| BP5L <sub>H</sub>   | BP5L UVLO hysteresis                        | C <sub>BP5L</sub> = 1µF                                          |              |                         |      | 0.2  |       | V    |

| BP7L <sub>R</sub>   | BP7L UVLO rising threshold                  | C <sub>BP7L</sub> = 1μF                                          |              | 1, 2, 3                 | 6.2  | 6.5  | 6.8   | V    |

| BP7L <sub>F</sub>   | BP7L UVLO falling threshold                 | C <sub>BP7L</sub> = 1μF                                          |              | 1, 2, 3                 | 5.9  | 6.2  | 6.5   | V    |

| BP7L <sub>H</sub>   | BP7L UVLO hysteresis                        | C <sub>BP7L</sub> = 1µF                                          |              |                         |      | 0.3  |       | V    |

| VIN <sub>R</sub>    | VIN UVLO rising threshold                   |                                                                  |              | 1, 2, 3                 | 8.0  | 8.6  | 9.0   | V    |

| VIN <sub>F</sub>    | VIN UVLO falling threshold                  |                                                                  |              | 1, 2, 3                 | 7.5  | 8.1  | 8.5   | V    |

| VIN <sub>H</sub>    | VIN UVLO hysteresis                         |                                                                  |              |                         |      | 0.5  |       | V    |

| BOOTR               | BOOT UVLO rising threshold                  |                                                                  |              | 1, 2, 3                 | 6.6  | 7.1  | 7.4   | V    |

| BOOT <sub>F</sub>   | BOOT UVLO falling threshold                 |                                                                  |              | 1, 2, 3                 | 6.2  | 6.65 | 7     | V    |

| BOOT <sub>H</sub>   | BOOT UVLO hysteresis                        |                                                                  |              |                         |      | 0.45 |       | V    |

| INPUT PI            | NS                                          |                                                                  |              |                         |      |      |       |      |

| V <sub>IR</sub>     | Input rising edge threshold                 |                                                                  |              | 1, 2, 3                 | 1.80 |      | 2.65  | V    |

| V <sub>IF</sub>     | Input falling edge threshold                |                                                                  |              | 1, 2, 3                 | 1.15 |      | 1.85  | V    |

| V <sub>IHYS</sub>   | Input hysteresis                            |                                                                  |              |                         |      | 0.8  |       | V    |

| R <sub>PD</sub>     | Input pull-down resistance                  | V = 2.15V applied at input (EN_HI or PWM_LI)                     |              | 1, 2, 3                 | 100  |      | 400   | kΩ   |

| PROGRA              | MMBLE DEAD TIME                             |                                                                  |              |                         |      |      | '     |      |

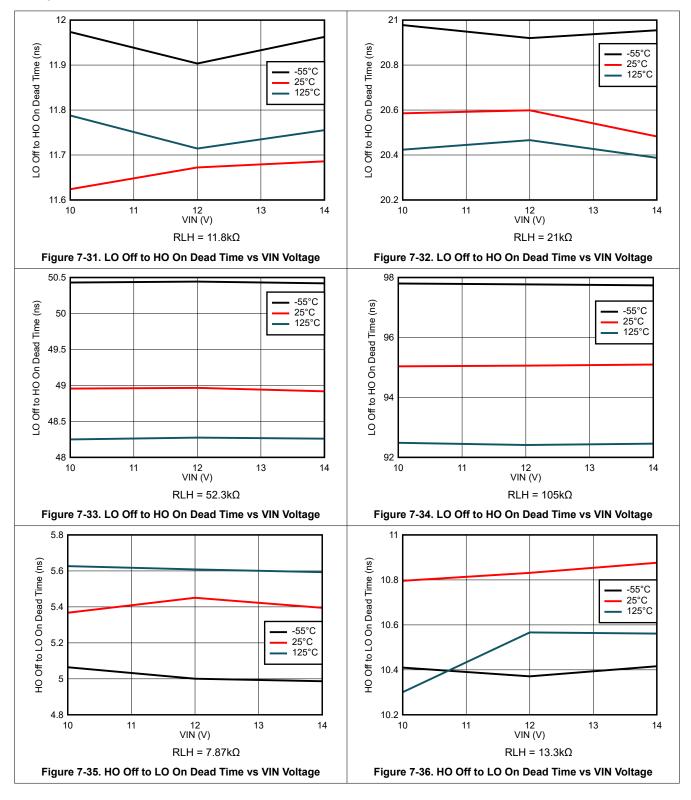

| T <sub>DLH</sub>    | LO off to HO on dead time                   | MODE = PWM, LO falling<br>to HO rising (90% to<br>10%), f ≤ 2MHz | RLH = 3.32kΩ | 9, 10 , 11              | 0    | 4.5  | 10    | ns   |

|                     |                                             |                                                                  | RLH = 11.8kΩ | 9, 10 , 11              | 8    | 12   | 15.5  |      |

|                     |                                             |                                                                  | RLH = 21kΩ   | 9, 10 , 11              | 15.5 | 21   | 24    |      |

|                     |                                             |                                                                  | RLH = 52.3kΩ | 9, 10 , 11              | 36   | 50   | 59    |      |

|                     |                                             |                                                                  | RLH = 105kΩ  | 9, 10 , 11              | 74   | 97   | 113.5 |      |

|                     |                                             |                                                                  | RHL = 7.87kΩ | 9, 10 , 11              | 0    | 5    | 10    |      |

|                     | HO off to LO on dead time                   | MODE = PWM, HO falling<br>to LO rising (90% to 10%),<br>f≤2MHz   | RHL = 13.3kΩ | 9, 10 , 11              | 6    | 10.5 | 15    | ns   |

| T <sub>DHL</sub>    |                                             |                                                                  | RHL = 23.7kΩ | 9, 10 , 11              | 16   | 21   | 24.5  |      |

|                     |                                             |                                                                  | RHL = 57.6kΩ | 9, 10 , 11              | 44   | 53   | 61    |      |

|                     |                                             |                                                                  | RHL = 113kΩ  | 9, 10 , 11              | 81   | 105  | 125   |      |

| воотѕт              | RAP DIODE SWITCH                            |                                                                  | 1            |                         |      |      |       |      |

| R <sub>BST SW</sub> | Bootstrap diode switch resistance           | I <sub>BST_SW</sub> = 100mA                                      |              | 1, 2, 3                 |      | 0.43 |       | Ω    |

|                     | Bootstrap diode switch parallel resistance  | I <sub>BST_RP</sub> = 1mA                                        |              | 1, 2, 3                 | 0.8  | 1    | 1.2   | kΩ   |

| POWER 0             | GOOD                                        | •                                                                |              |                         |      |      | I     |      |

|                     | Logic-low output                            | I <sub>FLT</sub> = 1mA                                           |              | 1, 2, 3                 |      |      | 0.4   | V    |

|                     | PGOOD internal resistance                   | BP5L = 5V, BP7L = 7V, VIN                                        | N = 12V      | 1, 2, 3                 | 0.7  | 1    | 1.9   | ΜΩ   |

|                     | Minimum BP5L voltage for valid PGOOD output |                                                                  |              | 1, 2, 3                 |      | 2    | 2.85  | V    |

|                     |                                             |                                                                  |              |                         |      |      |       |      |

<sup>(1)</sup> Subgroups are applicable for QML parts. For subgroup definitions, see Quality Conformance Inspection.

<sup>(2)</sup> Specified by design; not tested in production.

## 7.6 Switching Characteristics

Specifications are over ambient temperature operating range  $T_A = -55$ °C to 125°C, VIN = 10V to 14V,  $V_{BP5L} = V_{BP5H} = 5V$ , and no load on LOH, LOL, HOH, and HOL (unless otherwise noted).

| PARAMETER               |                                                               | TEST CONDITIONS                |                                              | SUBGR<br>OUP <sup>(1)</sup> | MIN | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------------|--------------------------------|----------------------------------------------|-----------------------------|-----|-----|-----|------|

| •                       | LO turnoff propagation delay                                  | MODE = PWM                     | PWM rising to LOL falling                    | 9, 10, 11                   |     | 30  | 48  | no   |

| t <sub>LPHL</sub>       | LO turnon propagation delay                                   | MODE = IIM                     | LI falling to LOL falling                    | 9, 10, 11                   |     | 27  | 38  | ns   |

| t <sub>LPLH</sub>       | LO turnon propagation delay                                   | MODE = IIM                     | LI rising to LOH rising                      | 9, 10, 11                   |     | 24  | 38  | ns   |

| t <sub>HPHL</sub>       | HO turnoff propagation delay                                  | MODE = PWM                     | PWM falling to HOL falling                   | 9, 10, 11                   |     | 35  | 50  | ns   |

|                         |                                                               | MODE = IIM                     | HI falling to HOL falling                    | 9, 10, 11                   |     | 30  | 40  |      |

| t <sub>HPLH</sub>       | HO turnon propagation delay                                   | MODE = IIM                     | HI rising to<br>HOH rising                   | 9, 10, 11                   |     | 26  | 40  | ns   |

| t <sub>MON</sub>        | Delay matching LO on and HO off <sup>(3)</sup>                | MODE = IIM                     |                                              | 9, 10, 11                   |     | 5.5 | 12  | ns   |

| t <sub>MOFF</sub>       | Delay matching LO off and HO on <sup>(3)</sup>                | MODE = IIM                     | 9, 10, 11                                    |                             | 1.5 | 4   | ns  |      |

| t <sub>HRC</sub>        | HO rise time                                                  |                                | 10% to 90%                                   | 9, 10, 11                   |     | 3.5 | 7.5 | ns   |

| t <sub>LRC</sub>        | LO rise time                                                  | $C_1 = 1000 pF$                | 10% to 90%                                   | 9, 10, 11                   |     | 3   | 7.5 |      |

| t <sub>HFC</sub>        | HO fall time                                                  | - C <sub>L</sub> = 1000pr      | 90% to 10%                                   | 9, 10, 11                   |     | 4   | 5.5 |      |

| t <sub>LFC</sub>        | LO fall time                                                  |                                | 90% to 10%                                   | 9, 10, 11                   |     | 3   | 5.5 |      |

| t <sub>PW_IIM</sub>     | Minimum input pulse width (turnon)                            | MODE = IIM                     |                                              | 9, 10, 11                   |     | 5   | 8   | ns   |

| t <sub>PW_IIM_OFF</sub> | Minimum input pulse width (turn-off)                          | MODE = IIM 9                   |                                              | 9, 10, 11                   |     | 8   | 12  | ns   |

|                         | Minimum required input pulse width for targeted dead time (2) | MODE = PWM, DT reduction ≤ 2ns | RLH = $11.9k\Omega$ ,<br>RHL = $13.3k\Omega$ |                             |     | 22  |     | no   |

| t <sub>PW_PWM</sub>     |                                                               | MODE = PWM, DT reduction ≤ 3ns | RLH = 21 kΩ,<br>RHL = 23.7kΩ                 |                             |     | 30  |     | ns   |

<sup>(1)</sup> Subgroups are applicable for QML parts. For subgroup definitions, see the Quality Conformance Inspection table.

<sup>(2)</sup> Specified by design; not tested in production.

<sup>(3)</sup> Specification limits for this parameter are represented as an absolute value.

# 7.7 Quality Conformance Inspection

MIL-STD-883, Method 5005 - Group A

| SUBGROUP | DESCRIPTION         | TEMP (°C)   |  |

|----------|---------------------|-------------|--|

| 1        | Static tests at     | 25          |  |

| 2        | Static tests at     | 125         |  |

| 3        | Static tests at     | <b>-</b> 55 |  |

| 4        | Dynamic tests at    | 25          |  |

| 5        | Dynamic tests at    | 125         |  |

| 6        | Dynamic tests at    | <b>-</b> 55 |  |

| 7        | Functional tests at | 25          |  |

| 8A       | Functional tests at | 125         |  |

| 8B       | Functional tests at | <b>–</b> 55 |  |

| 9        | Switching tests at  | 25          |  |

| 10       | Switching tests at  | 125         |  |

| 11       | Switching tests at  | -55         |  |

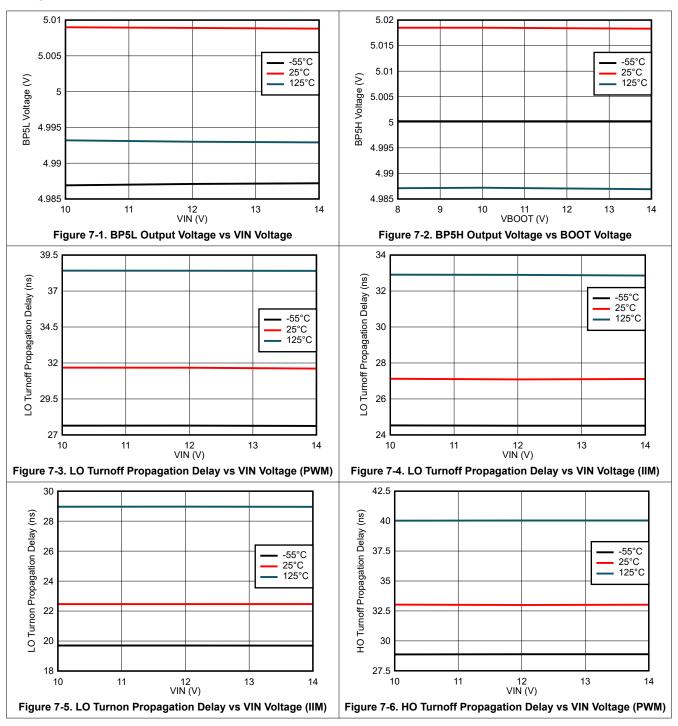

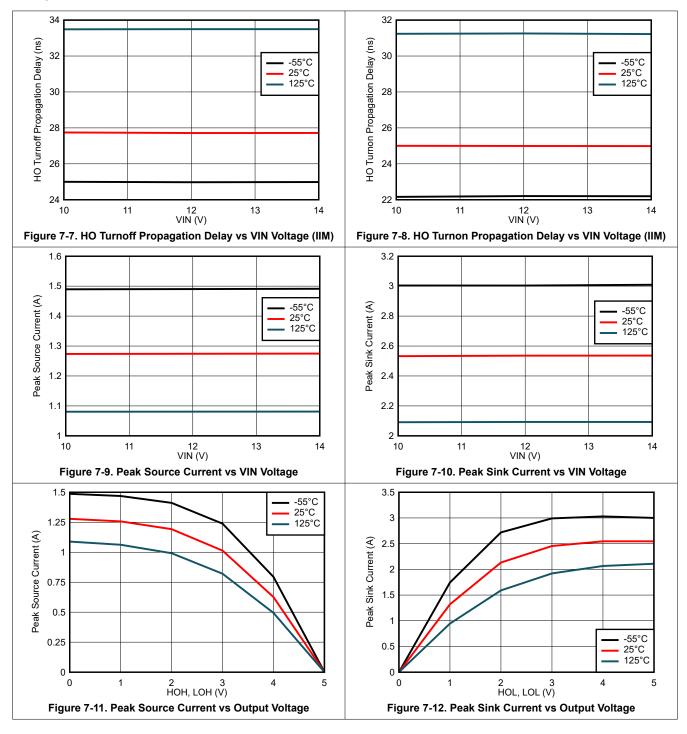

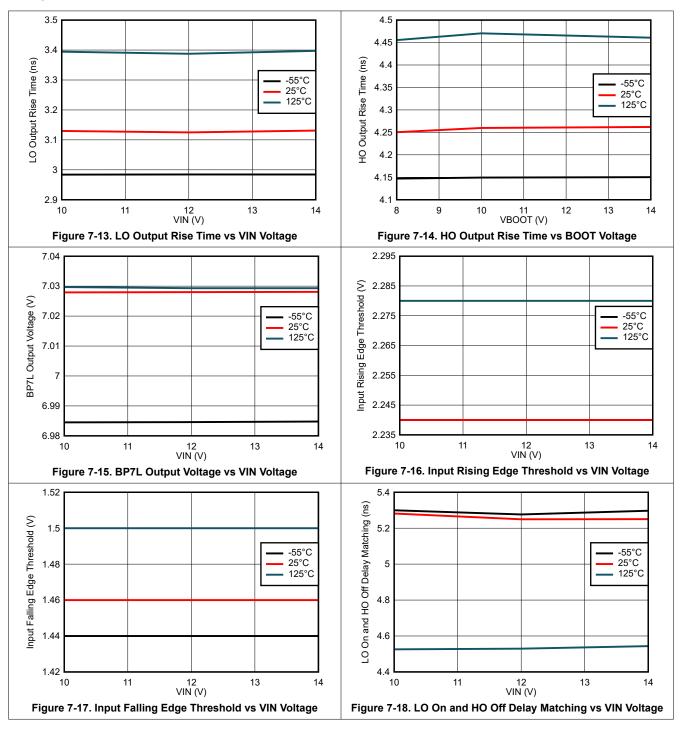

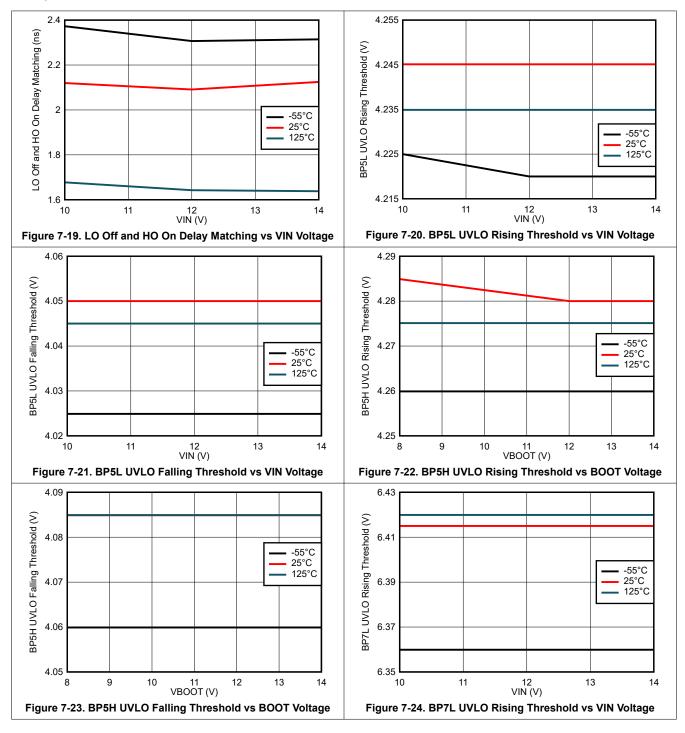

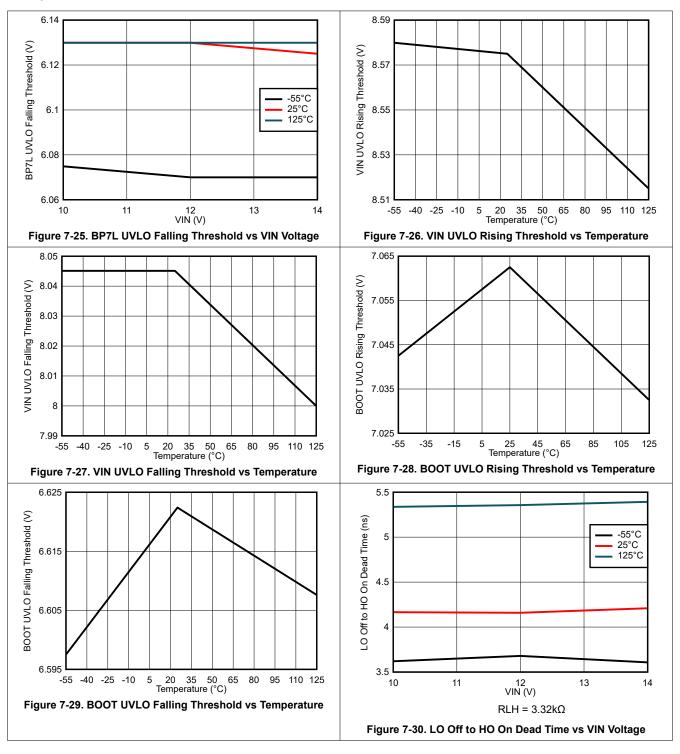

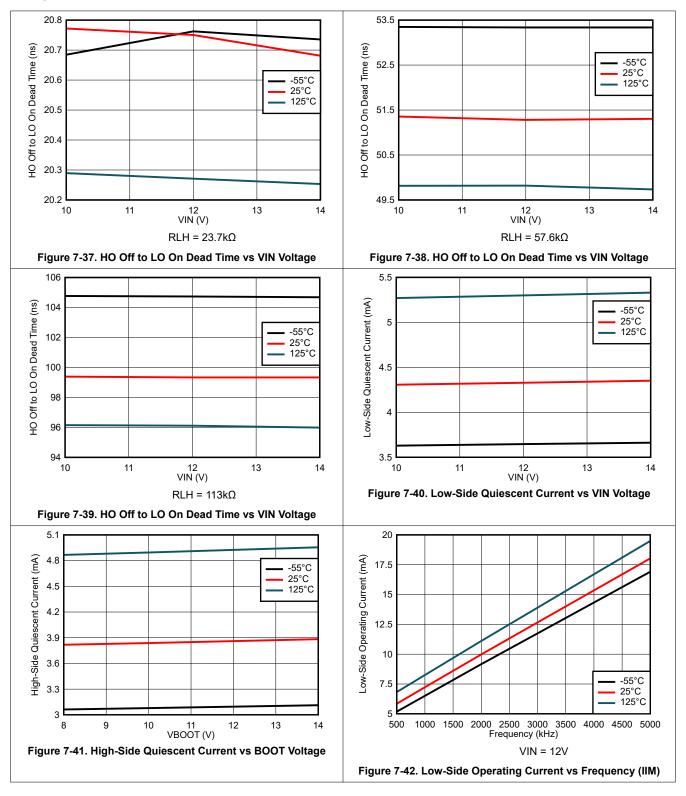

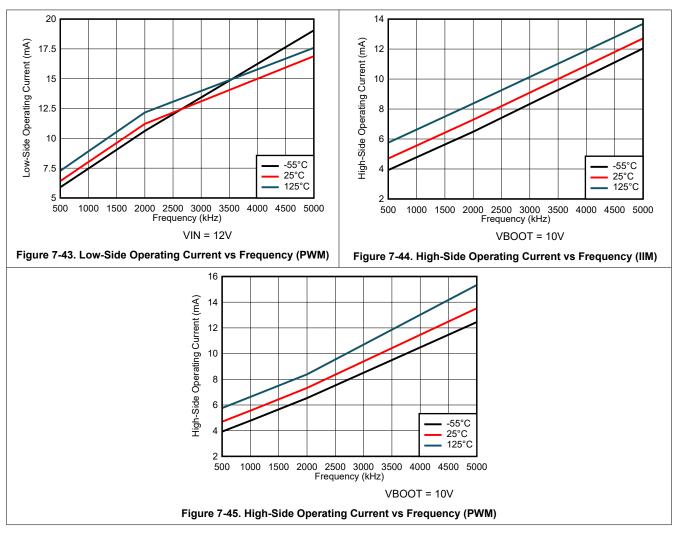

## 7.8 Typical Characteristics

# 8 Detailed Description

### 8.1 Overview

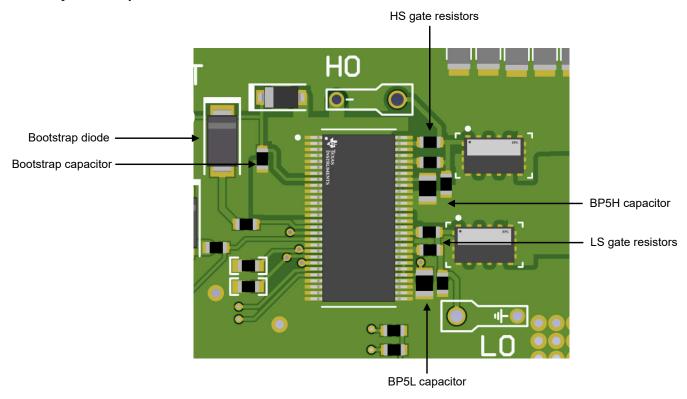

The TPS7H60x5 series of radiation-hardness-assured (RHA) half-bridge gate drivers are intended for use with enhancement mode GaN FETs. The series consists of the TPS7H6005 (200V driver), TPS7H6015 (60V driver), and the TPS7H6025 (22V driver). Each driver in the series has a 56-pin HTSSOP package and is available in both QMLP and SEP device grades. The drivers can be utilized in high frequency, high efficiency GaN based power converter designs. Each driver is designed to have a propagation delay of 30ns (typical) as well as 5.5ns (typical) high-side to low-side delay matching.

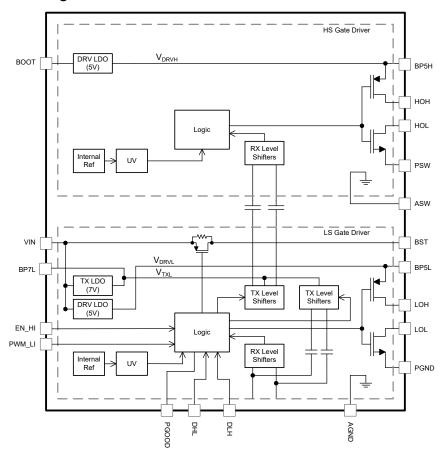

The drivers contain high-side and low-side internal linear regulators. These ensure that the gate voltages are maintained at 5V in order to prevent any damage of the GaN devices that are being driven. Split outputs on the high-side and low-side drivers provide the user the flexibility to independently adjust the turn-on and turn-off times of the GaN FETs. An external bootstrap diode is required for the gate drivers and as such, the user has the ability to optimize the diode based on the application. The drivers contain an internal switch in series with the bootstrap diode that can be used to prevent overcharging of the bootstrap capacitor and decreases reverse recovery losses in the diode.

The gate drivers have two modes of operation: PWM mode and independent input mode (IIM). The dual mode operation allows for each gate driver to be used with a wide number of PWM controllers to enable both synchronous rectifier control and GaN FET compatibility. The user also has the option to enable input interlock protection in IIM, allowing for anti-shoot through protection in synchronous buck and half-bridge topologies. This protection can also be disabled in IIM if desired, which allows the drivers to be utilized in two-switch forward converters and dual single ended applications.

## 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Input Voltage

During steady state operation, the input voltage of the TPS7H60x5 must be between 10V and 14V. This voltage serves as the input to the two low-side linear regulators, BP5L and BP7L. The external high-side bootstrap capacitor is also charged from VIN (see *Bootstrap Charging*). For best performance, add a bypass capacitor from VIN to AGND. Place this bypass capacitor as close to the gate driver as possible. This bypass capacitor is typically at least ten times greater than the value selected for the bootstrap capacitor.

## 8.3.2 Linear Regulator Operation

The TPS7H60x5 contains three internal linear regulators: BP5L, BP7L, and BP5H. BP5L and BP7L are included on the low side of the driver. These linear regulators provide 5V and 7V, respectively, as the nominal output voltages. BP5L is used to power the low-side logic circuitry as well as the low-side gate drive voltage. The BP5L regulator has an accuracy of 5V +3.5%/-5% to provide the proper voltage for driving GaN FETs. A minimum capacitor of  $1\mu$ F is required from the BP5L pin to PGND. BP7L powers the low-side transmitters within the driver. A minimum capacitor of  $1\mu$ F is also required from the BP7L pin to AGND.

On the high side, the voltage on BOOT serves as the input to the high side linear regulator BP5H. Similar to BP5L on the low-side, this regulator is used to power the high-side logic circuitry while providing the 5V  $\pm 3.5\%$ -5% high-side gate voltage to the external FET. A minimum capacitor of 1µF is required from BP5H to PSW. The recommendation for all internal linear regulators is that these not be externally loaded other than where indicated within this document.

## 8.3.3 Bootstrap Operation

To generate the power for the high-side gate driver circuitry when used in a half-bridge configuration, the gate driver requires the use of a bootstrap circuit. The selection of the TPS7H60x5 bootstrap components is critical for proper gate driver operation. There are also various methods for bootstrap capacitor charging that can be utilized for this device.

#### 8.3.3.1 Bootstrap Charging

The TPS7H60x5 provides the user several options for charging the bootstrap capacitor. The flexibility is to allow for operation with a wide range of PWM controllers, and also to allow the user to select an option with trade-offs that are most desirable for the specific application. In both instances, a bootstrap resistor is recommended to limit the bootstrap current during initial startup. The bootstrap resistor and capacitor need to be chosen such that sufficient time is allowed for the re-charge of the capacitor for the specific application.

The first option is to allow for charging of the bootstrap capacitor through the internal bootstrap switch of the driver. This switch is internally connected between VIN and BST pins and the bootstrap diode is connected externally between BST (anode) and BOOT (cathode). The bootstrap switch is only on when the low side driver output is on. By disallowing bootstrap charging during the converter dead times, the maximum voltage across the bootstrap capacitor can be reduced. The internal bootstrap switch has a parallel resistance of  $1k\Omega$  that allows for slow charging the bootstrap capacitor at start-up before low-side FET turn-on.

Figure 8-1. Internal Switch Bootstrap Charging Configuration

Another option is to charge the bootstrap capacitor directly from VIN. This is a more conventional method used with half-bridge drivers. This option can be considered in a number of use cases, but is particularly helpful in instances where the low-side FET turn-on is not immediate. This is the case when using the TPS7H60x5 with one of the three controllers in the TPS7H500x-SP family that have integrated synchronous rectification outputs. The synchronous rectification outputs are disabled during soft-start, and as such, when implementing a synchronous buck topology the bootstrap capacitor cannot be charged through the internal bootstrap switch of the driver. The bootstrap switch does have the parallel resistor for slow-charging, but sequencing and/or startup requirements for the converter can potientially dictate that the charging need to occur more rapidly. When using the direct VIN charging, the options for preventing overcharging of the bootstrap capacitor are to add a resistor in series with the bootstrap capacitor, to add a Zener diode in parallel with the bootstrap capacitor, or a combination of both. A consideration that must be made if using the Zener diode is that has an associated leakage current during normal operation, which contributes to the overall converter losses.

Figure 8-2. Direct VIN Bootstrap Charging Configuration

Lastly, a dual-charging option can be considered, which is a combination of the bootstrap switch and direct VIN charging methods. This method offers the benefit of circumventing any potential bootstrap charging issues during startup due to the low-side FET not turning on, while also taking advantage of the reduction of bootstrap voltage during normal operation offered by the internal switch. The series resistor used with the bootstrap diode in the direct VIN charging path must be higher than the resistance of the internal bootstrap switch to make sure that the charging is via the bootstrap switch during normal operation. This higher resistor value also effectively reduces the Zener current during normal operation. The trade-off for this configuration is the additional part count.

Figure 8-3. Dual Bootstrap Charging Configuration

#### 8.3.3.2 Bootstrap Capacitor

The external bootstrap capacitor that is required for the driver is connected between BOOT and ASW. The bootstrap capacitor voltage serves as the input to the high-side linear regulator BP5H that provides the gate drive voltage for the high-side GaN FET. A general guideline for bootstrap capacitor selection is that its value should be at least 10× greater than the gate capacitance of the high-side GaN FET that is being driven:

$$C_{BOOT} \ge 10 \times C_{g} \tag{1}$$

where:

• C<sub>q</sub> is the gate capacitance for the high-side GaN FET

A more detailed calculation of the minimum bootstrap capacitance needed can be found using Equation 2:

$$C_{\text{BOOT}} \ge \frac{Q_{\text{total}}}{\Delta V_{\text{BOOT}}}$$

(2)

$$Q_{\text{total}} = Q_{\text{g}} + I_{\text{QBG}} \times \frac{D_{\text{MAX}}}{f_{\text{SW}}} + \frac{I_{\text{QHS}}}{f_{\text{SW}}}$$

(3)

where:

- Q<sub>a</sub> is the total gate charge for the high-side GaN FET

- I<sub>OBG</sub> is the BOOT to AGND quiescent current

- D<sub>MAX</sub> is the maximum duty cycle

- I<sub>OHS</sub> is the high-side quiescent current

- f<sub>SW</sub> is the switching frequency

and  $\Delta V_{BOOT}$  is the maximum allowable drop on BOOT for proper operation:

$$\Delta V_{BOOT} = VIN - (n \times V_F) - V_{BOOT\_UVLO}$$

(4)

where:

#### www.ti.com

- · VIN is the gate driver input voltage

- n is the number of external bootstrap diodes placed in series

- V<sub>F</sub> is the forward voltage drop of the bootstrap diode

- V<sub>BOOT UVLO</sub> is the falling undervoltage lockout threshold of BOOT (6.65V typical)

Using a sufficiently sized capacitor, low frequency motor driver applications can be supported using the TPS7H60x5 devices. Selection of a bootstrap capacitor with low ESR and ESL is recommended. The voltage rating of the bootstrap capacitor should have sufficient margin above the maximum expected bootstrap voltage.

#### 8.3.3.3 Bootstrap Diode

Regardless of the method of charging the bootstrap capacitor, the TPS7H60x5 requires an external bootstrap diode rated to withstand the input voltage that is applied to the converter power stage in the half-bridge configuration. Care must be taken when selecting the external bootstrap diode. The bootstrap diode needs to be capable of handling peak transient currents that occur during the startup period. Fast recovery diodes should be used in the bootstrap circuit. The user needs to examine the I-V characteristics of the selected diode to verify that the forward voltage under the intended operating conditions does not become too large to trigger the undervoltage lockout of the BP5H regulator. Overall, the user needs to meet the conditions of Equation 5:

$$VIN - (n \times V_F) \ge V_{BOOT\ UVLO} \tag{5}$$

#### where:

- VIN is the gate driver input voltage

- n is the number of external bootstrap diodes placed in series

- V<sub>F</sub> is the forward voltage drop of the bootstrap diode

- V<sub>BOOT UVLO</sub> is the falling undervoltage lockout threshold of BOOT (6.65V typical)

#### 8.3.3.4 Bootstrap Resistor

The bootstrap resistor is used to (1) limit the peak current during gate driver startup and (2) control the slew rate (dv/dt) at BOOT. The peak current through the bootstrap diode, and through the BST switch if utilized, can become excessively high during the initial charging period. Furthermore, excessive slew rates at BOOT can cause a slight overshoot of the BP5H voltage during startup. To mitigate these issues a bootstrap resistor of at least  $2\Omega$  is recommended.

While the bootstrap resistor does alleviate peak current and slew rate issues, this resistor in conjunction with the bootstrap capacitor introduces a time constant  $\tau$ :

$$\tau = \frac{R_{\text{BOOT}} \times C_{\text{BOOT}}}{D} \tag{6}$$

#### where:

- R<sub>BOOT</sub> is the value of the bootstrap resistor in ohms

- C<sub>BOOT</sub> is the value of bootstrap capacitor in Farads

- D is the duty cycle of the switching converter

The time required to charge and refresh the charge of the bootstrap capacitor needs to be checked against the time constant. Lastly, the resistor can experience high power dissipation during the initial charging period. Select a resistor that can handle the energy during this charging period:

$$E = \frac{1}{2} \times C_{BOOT} \times V_{BOOT}^2 \tag{7}$$

#### where:

- C<sub>BOOT</sub> is the value of bootstrap capacitor in Farads

- V<sub>BOOT</sub> is the final voltage of the bootstrap capacitor

SNOSDH4A - JUNE 2024 - REVISED DECEMBER 2024

### 8.3.4 High-Side Driver Startup

For proper startup up of the high side, the BOOT to SW voltage must be greater than the BOOT UVLO rising threshold value of 6.4V (typical). In half-bridge converter configurations that have a pre-bias voltage present at the output, the bootstrap capacitor may not be able to adequately charge from VIN until the output voltage is sufficiently discharged. This same behavior can be seen during a brownout of VIN in which the input voltage temporarily decreases below the VIN UVLO falling threshold. Upon recovery, the low-side driver will attempt to begin normal operation, but the turn-on of the high-side driver will be delayed due to the output voltage that is present on the converter. This is a problem that is inherent in half-bridge gate drivers. Discharge circuits at the converter output can help alleviate the problem by forcing the output to a low voltage, only after which gate drive startup is attempted.

## 8.3.5 Inputs and Outputs

The input pins of the TPS7H60x5 are PWM\_LI and EN\_HI. Each of these pins has an internal pull-down resistance of approximately  $200k\Omega$  (typical). The functions of these pins vary depending on the selected mode of operation of the gate driver as described in *Device Functional Modes*. In PWM mode, PWM\_LI serves as the input pin for the single PWM control signal into the driver and EN\_HI is an enable pin for the driver. In independent input mode, PWM\_LI serves as the low-side input and EN\_HI serves as the high-side input. The inputs are capable of withstanding voltages up to 14V, which allows them to be directly connected to the outputs of an analog PWM controller with a power supply voltage less than or equal to 14V. If operating in independent input mode and either of the two input channels PWM\_LI or EN\_HI is not used, it is recommended to connect the input to AGND. Given that the inputs are edge-triggered, it is recommended to use input signals with slew rates faster than  $2V/\mu s$  for expected operation.

The TPS7H60x5 contains split outputs on both the high-side and low-side. The high-side consists of outputs HOH and HOL, which are the source and sink outputs, respectively. Likewise, the low-side has source output LOH and sink output LOL. These split outputs offer the flexibility to adjust the turn-on and turn-off speed independently by placing additional impedance to either the turn-on or turn-off path of the GaN device that is being driven. These outputs are capable of sourcing 1.3A and sinking 2.5A, typical.

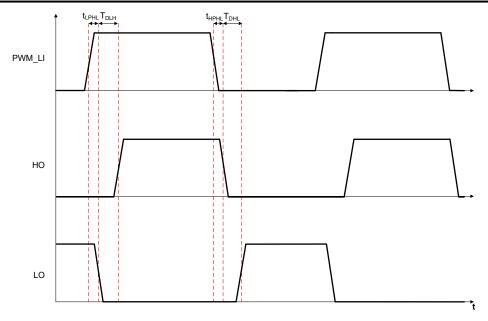

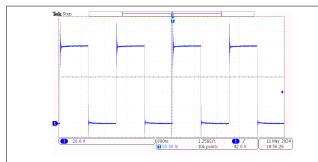

#### 8.3.6 Dead Time

When operating in PWM mode, resistors to AGND are required on both DLH and DHL to program the dead time. The DHL resistor sets the dead time between high-side output (HO) turn-off to low-side (LO) output turn-on. Likewise, the resistor on DLH sets the dead-time between low-side (LO) turn-off to high-side (HO) turn-on. The resistor can be used to set the dead time from a minimum value of roughly 5ns up to 100ns. The resistor must be populated on both pins to operate the device in this mode.

Figure 8-4. Timing Waveforms in PWM Mode Showing Dead Time

The resistors required to program for a desired dead times are calculated from

$$RHL = 1.077 \times T_{DHL} + 1.812 \tag{8}$$

where:

- T<sub>DHL</sub> is the desired "HO off to LO on" dead time in ns

- RHL is in kΩ

$$RLH = 1.064 \times T_{DLH} - 0.630 \tag{9}$$

where:

- T<sub>DLH</sub> is the desired "LO off to HO on" dead time in ns

- RLH is in kΩ

Carefully select dead time to prevent cross-conduction between the high-side and low-side switches, while also minimizing losses during this period. The resistors selected for RHL and RLH are recommended to have a tolerance of 1% or better.

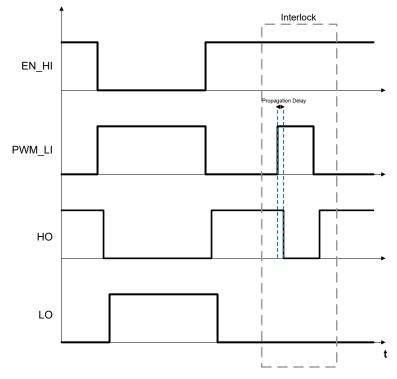

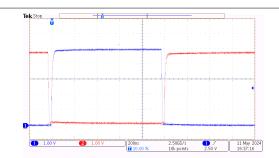

#### 8.3.7 Input Interlock Protection

The TPS7H60x5 can be configured to have input interlock protection in independent input mode (IIM). To activate the input interlock protection in IIM, DHL must be connected to 5V while DLH has a resistor (valued between  $100k\Omega$  and  $220k\Omega$ ) connected between the pin and AGND. This protection is intended to improve the robustness and reliability of the power stage with which the driver is being used by preventing shoot-through of the GaN FETs in a half-bridge configuration. In any instance when the protection is enabled and both inputs are logic high, the internal logic turns both of the outputs off. Both outputs remain off until one of the inputs goes low, in which case the outputs follow the input logic. There is no fixed time deglitching for this feature in order to not impact the propagation delay and dead time of the driver. Small filters at the inputs of the driver can be utilized to improve robustness in noise prone applications.

Figure 8-5. Input Interlock Protection in Independent Input Mode

#### 8.3.8 Undervoltage Lockout and Power Good (PGOOD)

The TPS7H60x5 has undervoltage lockout (UVLO) on BP5L, BP7L, BP5H, BOOT, and VIN. When the output voltage on any of the low-side linear regulators or VIN falls below the UVLO threshold (4.05V for the BP5L linear regulator, 6.2V for the BP7L linear regulator, and 8.1V for VIN), the PWM inputs are ignored to prevent the GaN FETs from partial turn-on. In this scenario, the UVLO actively pulls LO and HO low. When the low-side regulators and VIN are each above the respective UVLO threshold but one of the high-side UVLOs is triggered (4.05V for BP5H and/or 6.65V for BOOT), then only HO is pulled low.

The gate driver also has a power good (PGOOD) pin, which indicates when any of the low-side linear regulators have entered undervoltage lockout. The pin enters the logic-high state when all low-side regulators and VIN each have surpassed the respective rising UVLO threshold. The pin goes, or remains, logic-low if any one of these linear regulators or VIN falls below the corresponding falling UVLO threshold. The PGOOD pin has an internal pull-down resistance of  $1M\Omega$  when the pin is in the logic-high state. A pull-up of  $10k\Omega$  connected from PGOOD to BP5L is recommended.

#### 8.3.9 Negative SW Voltage Transients

Though enhancement mode GaN FETs do not contain a body diode like silicon FETs, the devices are capable of reverse conduction due to the symmetrical device structure. During the reverse conduction periods, the source-drain voltage of the GaN FET is typically higher than what is encountered with a traditional silicon FET, largely depending on the type of GaN device that is being used. As such, the switch node pins of the driver (ASW and PSW, collectively referred to as SW) have a negative voltage present. This negative transient can lead to an excessive bootstrap voltage, since BOOT is always referenced to SW. Furthermore, the printed circuit board layout and device parasitic inductances can further intensify the negative voltage transients. Operating at a bootstrap voltage above the absolute maximum of 16V can be detrimental to the gate driver, so care must be taken to make sure that the maximum BOOT to SW voltage differential is not exceeded. Generally, BOOT follows SW instantaneously so that the BOOT to SW voltage does not overshoot significantly. However, an external Zener diode can be used between BOOT and SW to clamp the bootstrap voltage to acceptable values during operation.

#### 8.3.10 Level Shifter

The TX and RX level shifters interface between the inputs on the low-side to the high-side driver stage which is referenced to the high voltage switch node (ASW). The level shifters allow control of the HO output. The level shifters in both the high-side and low-side signal paths are identical and provide excellent delay matching (5.5ns typical).

#### 8.4 Device Functional Modes

The mode of operation for the TPS7H60x5 is determined by the state of the DHL and DLH pins. The configuration of these pins should not be changed during device operation. There are two different operational modes: PWM and independent input mode. In PWM mode, the EN\_HI pin is used to enable the device and a single PWM input signal is required on PWM\_LI and the TPS7H6005 generates the complementary output signals on LO and HO. Since the primary application of this mode is a synchronous buck converter, HO will generate the main output and LO will generate the synchronous rectification output. Resistors are connected from DHL to AGND and DLH to AGND in order to program the dead time between the high-side and low-side outputs. For acceptable resistor values (TBD) to use in PWM mode, refer to *Dead Time* section.

In independent input mode (IIM), separate PWM input signals are required on PWM\_LI and EN\_HI. The corresponding outputs of the TPS7H60x5 are driven directly from these inputs. In IIM with interlock disabled, DLH is tied to BP5L and DHL has a resistor connected to AGND. For operation in IIM with interlock enabled, connect a resistor between DLH and AGND while connecting DHL to BP5L. For both operating mode options in IIM, resistors used must be valued between  $100k\Omega$  and  $220k\Omega$ .

Table 8-1 shows the configuration for each operating mode. Note that these are the only valid operating modes for the driver, and the connections for DLH and DHL must adhere to one of these configurations for proper operation.

Table 8-1. TPS7H60x5 Operating Mode Selection

| Operating Mode                                    | DLH                                                | DHL                                                |  |  |

|---------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--|--|

| PWM                                               | Resistor to AGND                                   | Resistor to AGND                                   |  |  |

| Independent input mode - input interlock disabled | BP5L                                               | Resistor to AGND (100k $\Omega$ to 220k $\Omega$ ) |  |  |

| Independent input mode - input interlock enabled  | Resistor to AGND (100k $\Omega$ to 220k $\Omega$ ) | BP5L                                               |  |  |

Table 8-2 shows the truth table for each functional mode of the TPS7H60x5.

Table 8-2. TPS7H60x5 Truth Table

| Inputs |        | PWM Mode |    | IIM - Interlock Disabled |    | IIM - Interlock Enabled |    |

|--------|--------|----------|----|--------------------------|----|-------------------------|----|

| EN_HI  | PWM_LI | НО       | LO | НО                       | LO | НО                      | LO |

| 0      | 0      | 0        | 0  | 0                        | 0  | 0                       | 0  |

| 0      | 1      | 0        | 0  | 0                        | 1  | 0                       | 1  |

| 1      | 0      | 0        | 1  | 1                        | 0  | 1                       | 0  |

| 1      | 1      | 1        | 0  | 1                        | 1  | 0                       | 0  |

SNOSDH4A - JUNE 2024 - REVISED DECEMBER 2024