Sample &

Buy

## DAC7551-Q1

SLAS767B-JUNE 2011-REVISED MARCH 2015

# DAC7551-Q1 12-Bit, Ultra-Low Glitch, Voltage Output **Digital-to-Analog Converter**

#### Features 1

- Qualified for Automotive Applications

- Relative Accuracy (INL): ±0.35 LSB

- Ultra-Low Glitch Energy: 0.1 nV-s

- Low-Power Operation: 100 µA at 2.7 V

- Power-On Reset-to-Zero Scale

- Power Supply: 2.7- to 5.5-V Single Supply

- Power-Down: 0.05 µA at 2.7 V

- 12-Bit Linearity and Monotonicity

- Rail-to-Rail Voltage Output

- Settling Time: 5 µs (Max)

- SPI-Compatible Serial Interface With Schmitt-Trigger Input: Up to 50 MHz

- **Daisy-Chain Capability**

- Asynchronous Hardware Clear-to-Zero Scale

- Specified Temperature Range: -40°C to +105°C

- Small, 2-mm × 3-mm, 12-Lead USON Package

- Z-Suffix Offers Improved Delamination

#### 2 Applications

- Portable, Battery-Powered Instruments

- **Digital Gain and Offset Adjustment**

- Programmable Voltage and Current Sources

- **Programmable Attenuators**

- Industrial Process Control

- **ADAS Radar Applications**

- **Collision Warning**

- Blind-Spot Detection

## 3 Description

The DAC7551-Q1 device is a single-channel, voltageoutput digital-to-analog converter (DAC) with exceptional linearity and monotonicity, and a proprietary architecture that minimizes glitch energy. The low-power DAC7551-Q1 device operates from a single 2.7- to 5.5-V supply. The DAC7551-Q1 output amplifiers can drive a 2-kΩ, 200-pF load rail-to-rail with 5-µs settling time. The output range is set using an external voltage reference.

The 3-wire serial interface operates at clock rates up to 50 MHz and is compatible with SPI™, QSPI™, microwire, and DSP interface standards. The device incorporates a power-on-reset (POR) circuit to ensure that the DAC output powers up to 0 V and remains at that voltage until a valid write cycle to the device occurs. The device contains a power-down feature that reduces the current consumption of the device to under 2 µA.

Small size and low-power operation make the DAC7551-Q1 device ideally suited for batteryapplications. operated, portable The power consumption is typically 0.5 mW at 5 V, 0.23 mW at 3 V, and reduces to 1 µW in power-down mode.

The DAC7551-Q1 device is available in a 12-pin USON package and is specified over -40°C to +105°C. The Z-suffix offers reduced delamination compared to standard device.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DAC7551-Q1  | USON (12) | 2.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

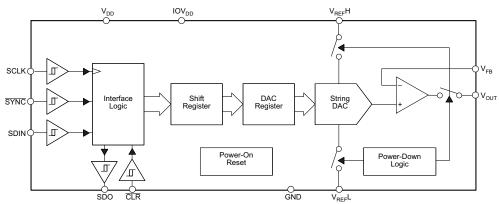

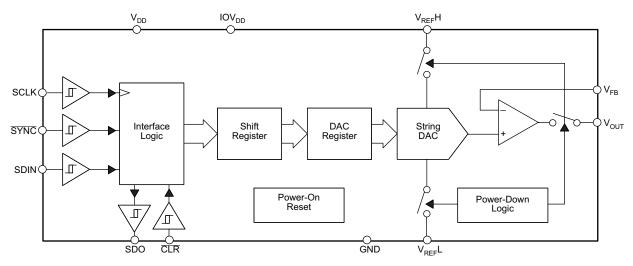

### **Functional Block Diagram**

Features ..... 1

Applications ..... 1

Description ..... 1

Recommended Operating Conditions ...... 4

Thermal Information ...... 4

7.1

Overview

11

7.2

Functional Block Diagram

11

1

2

3

4

5 6

7

2

6.1

6.2

6.3

6.4

## Table of Contents

|    | 7.3  | Feature Description               | 11 |

|----|------|-----------------------------------|----|

|    | 7.4  | Device Functional Modes           | 13 |

|    | 7.5  | Programming                       | 14 |

| 8  | Арр  | lication and Implementation       | 15 |

|    | 8.1  | Application Information           | 15 |

|    | 8.2  | Typical Application               | 16 |

| 9  | Pow  | er Supply Recommendations         | 17 |

| 10 | Lay  | out                               | 18 |

|    | 10.1 | Layout Guidelines                 | 18 |

|    | 10.2 | Layout Example                    | 18 |

| 11 | Dev  | ice and Documentation Support     | 19 |

|    | 11.1 | Documentation Support             | 19 |

|    | 11.2 | Trademarks                        | 19 |

|    | 11.3 | Electrostatic Discharge Caution   | 19 |

|    | 11.4 | Glossary                          | 19 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           | 19 |

|    |      |                                   |    |

Copyright © 2011–2015, Texas Instruments Incorporated

4 Revision History

|    | hanges from Revision A (February 2015) to Revision B Pa                                            | age |  |  |  |

|----|----------------------------------------------------------------------------------------------------|-----|--|--|--|

| •  | Added ADAS radar, collision warning, and blind-spot detection to Applications list                 | 1   |  |  |  |

| •  | Changed the thermal information values for the DRN (USON) package in the Thermal Information table |     |  |  |  |

|    |                                                                                                    |     |  |  |  |

| CI | hanges from Original (June 2011) to Revision A Pa                                                  | age |  |  |  |

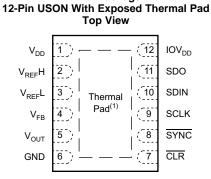

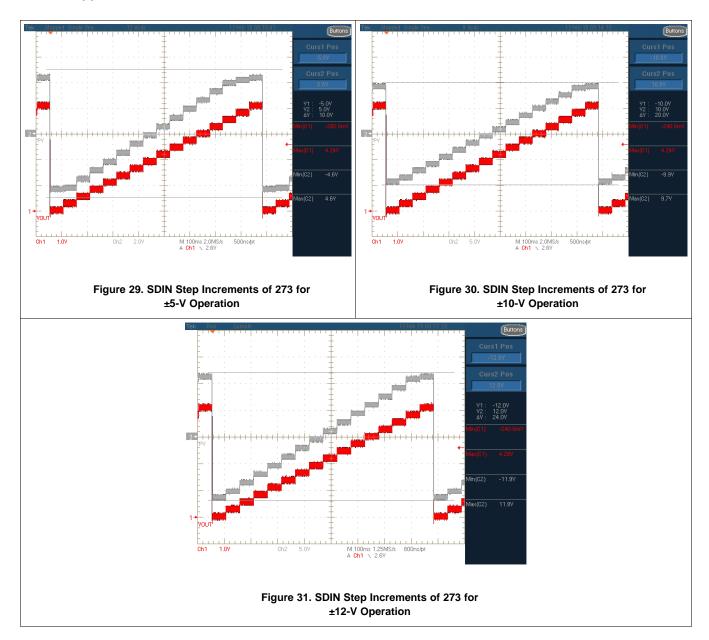

## 5 Pin Configuration and Functions

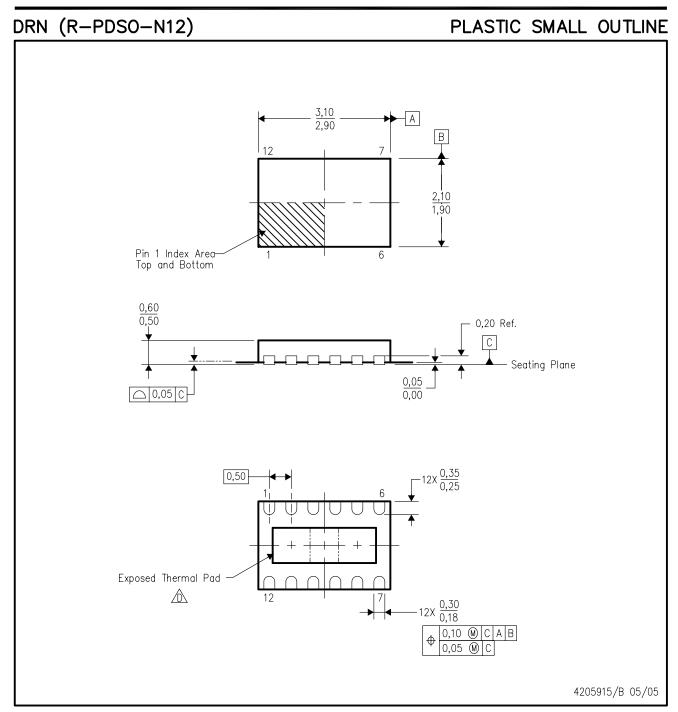

**DRN Package**

(1) The thermal pad should be connected to GND.

#### **Pin Functions**

| PIN |                    | I/O | DESCRIPTION                                                                                                                                                |  |  |

|-----|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME               | 1/0 | DESCRIPTION                                                                                                                                                |  |  |

| 1   | V <sub>DD</sub>    | I   | Analog voltage supply input                                                                                                                                |  |  |

| 2   | V <sub>REF</sub> H | Ι   | Positive reference voltage input                                                                                                                           |  |  |

| 3   | V <sub>REF</sub> L | Ι   | legative reference voltage input                                                                                                                           |  |  |

| 4   | V <sub>FB</sub>    | I   | AC amplifier sense input.                                                                                                                                  |  |  |

| 5   | V <sub>OUT</sub>   | 0   | Analog output voltage from DAC                                                                                                                             |  |  |

| 6   | GND                | _   | Ground.                                                                                                                                                    |  |  |

| 7   | CLR                | I   | Asynchronous input to clear the DAC registers. When the $\overline{\text{CLR}}$ pin is low, the DAC register is set to 000h and the output voltage to 0 V. |  |  |

| 8   | SYNC               | I   | Frame synchronization input. The falling edge of the SYNC pulse indicates the start of a serial data frame shifted out to the DAC7551-Q1 device.           |  |  |

| 9   | SCLK               | I   | Serial clock input                                                                                                                                         |  |  |

| 10  | SDIN               | I   | Serial data input                                                                                                                                          |  |  |

| 11  | SDO                | 0   | Serial data output                                                                                                                                         |  |  |

| 12  | IOV <sub>DD</sub>  | I   | I/O voltage supply input                                                                                                                                   |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted).<sup>(1)</sup>

|                                            | MIN                 | MAX                                   | UNIT |

|--------------------------------------------|---------------------|---------------------------------------|------|

| V <sub>DD</sub> , IOV <sub>DD</sub> to GND | -0.3                | 6                                     | V    |

| Digital input voltage to GND               | -0.3                | V <sub>DD</sub> + 0.3                 | V    |

| V <sub>OUT</sub> to GND                    | -0.3                | V <sub>DD</sub> + 0.3                 | V    |

| Operating temperature range                | -40                 | 105                                   | °C   |

| Junction temperature, T <sub>J</sub> max   |                     | 150                                   | °C   |

| Power dissipation (DRN)                    | (T <sub>J</sub> max | – Τ <sub>Α</sub> ) / R <sub>θJA</sub> |      |

| Storage temperature, T <sub>stg</sub>      | -65                 | 150                                   | °C   |

(1) Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

STRUMENTS

XAS

## 6.2 ESD Ratings

|                    |                         |                                                         |                               | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                               | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            | All pins                      | ±500  | V    |

| (ESD)              |                         |                                                         | Corner pins (1, 6, 7, and 12) | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|    |                                |                    | MIN  | NOM | MAX      | UNIT |

|----|--------------------------------|--------------------|------|-----|----------|------|

|    |                                | V <sub>DD</sub>    | 2.7  |     | 5.5      |      |

| VI |                                | V <sub>REF</sub> H | 0.25 |     | $V_{DD}$ |      |

|    |                                | V <sub>REF</sub> L | 0    | GND | $V_{DD}$ |      |

|    |                                | V <sub>FB</sub>    | 0    |     | $V_{DD}$ |      |

|    | Input voltage                  | IOV <sub>DD</sub>  | 1.8  |     | $V_{DD}$ | V    |

|    |                                | CLR                | 0    |     | $IOV_DD$ |      |

|    |                                | SYNC               | 0    |     | $IOV_DD$ |      |

|    |                                | SCLK               | 0    |     | $IOV_DD$ |      |

|    |                                | SDIN               | 0    |     | $IOV_DD$ |      |

| V  |                                | SDO                | 0    |     | $IOV_DD$ | V    |

| Vo | Output voltage                 | V <sub>OUT</sub>   | 0    |     | $V_{DD}$ | v    |

| TJ | Operating junction temperature |                    |      |     | 150      | °C   |

#### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | DRN (USON)<br>12 PINS | UNIT |

|-----------------------|----------------------------------------------|-----------------------|------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 49.8                  |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 45.8                  |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 18.2                  | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.8                   | C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 18.3                  |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.9                   |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

all specifications at –40°C to +105°C,  $V_{DD}$  = 2.7 to 5.5 V,  $V_{REF}H = V_{DD}$ ,  $V_{REF}L = GND$ ,  $R_L = 2 k\Omega$  to GND, and  $C_L = 200 \text{ pF}$  to GND (unless otherwise noted).

| PARAMETER                         | TEST CONDITIONS                   | MIN | TYP   | MAX   | UNIT             |

|-----------------------------------|-----------------------------------|-----|-------|-------|------------------|

| STATIC PERFORMANCE <sup>(1)</sup> |                                   |     |       |       |                  |

| Resolution                        |                                   | 12  |       |       | Bits             |

| Relative accuracy                 |                                   |     | ±0.35 | ±1    | LSB              |

| Differential nonlinearity         | Specified monotonic by design     |     | ±0.08 | ±0.5  | LSB              |

| Offset error                      |                                   |     |       | ±12   | mV               |

| Zero-scale error                  | All zeroes loaded to DAC register |     |       | ±12   | mV               |

| Gain error                        |                                   |     |       | ±0.15 | %FSR             |

| Full-scale error                  |                                   |     |       | ±0.5  | %FSR             |

| Zero-scale error drift            |                                   |     | 7     |       | µV/°C            |

| Gain temperature coefficient      |                                   |     | 3     |       | ppm of<br>FSR/°C |

(1) Linearity tested using a reduced code range of 30 to 4065; output unloaded.

#### **Electrical Characteristics (continued)**

all specifications at -40°C to +105°C,  $V_{DD}$  = 2.7 to 5.5 V,  $V_{REF}H = V_{DD}$ ,  $V_{REF}L$  = GND,  $R_L$  = 2 k $\Omega$  to GND, and  $C_L$  = 200 pF to GND (unless otherwise noted).

|                   | PARAME                            | TER                                     | TEST CONDITIONS                                                                          | MIN                       | TYP  | MAX                      | UNIT   |  |

|-------------------|-----------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|---------------------------|------|--------------------------|--------|--|

| SRR               | Power-supply rejecti              | ion ratio                               | $V_{DD} = 5 V$                                                                           |                           | 0.75 |                          | mV/V   |  |

| OUTPU             | T CHARACTERISTIC                  | S <sup>(2)</sup>                        |                                                                                          |                           |      |                          |        |  |

|                   | Output voltage range              | e                                       |                                                                                          | 2 ×<br>V <sub>REF</sub> L |      | $V_{REF}H$               | V      |  |

|                   | Output voltage settli             | ng time                                 | $R_L = 2 \text{ k}\Omega, 0 \text{ pF} < C_L < 200 \text{ pF}$                           |                           |      | 5                        | μs     |  |

|                   | Slew rate                         |                                         |                                                                                          |                           | 1.8  |                          | V/µs   |  |

|                   | Capacitive load stab              |                                         | R <sub>L</sub> = ∞                                                                       |                           | 470  |                          | ъĘ     |  |

|                   | Capacitive load stab              | anty                                    | $R_L = 2 k\Omega$                                                                        |                           | 1000 |                          | pF     |  |

|                   | Digital-to-analog glite           | ch impulse                              | 1 LSB change around major carry                                                          |                           | 0.1  |                          | nV-s   |  |

|                   | Digital feedthrough               |                                         |                                                                                          |                           | 0.1  |                          | nV-s   |  |

|                   | Output noise density              | /                                       | 10kHz offset frequency                                                                   |                           | 120  |                          | nV/√Hz |  |

| THD               | Total harmonic disto              | ortion                                  | $f_{OUT}$ = 1 kHz, $f_{S}$ = 1 MSPS, BW = 20 kHz                                         |                           | -85  |                          | dB     |  |

|                   | DC output impedance               | ce                                      |                                                                                          |                           | 1    |                          | Ω      |  |

|                   | Short circuit current             |                                         | $V_{DD} = 5 V$                                                                           |                           | 50   |                          | mA     |  |

|                   | Short-circuit current             |                                         | $V_{DD} = 3 V$                                                                           |                           | 20   |                          | ша     |  |

|                   | Power-up time                     |                                         | Coming out of power-down mode, $V_{DD} = 5 V$                                            |                           | 15   |                          |        |  |

|                   |                                   |                                         | Coming out of power-down mode, $V_{DD} = 3 V$                                            |                           | 15   |                          | μs     |  |

| REFER             | ENCE INPUT                        |                                         |                                                                                          |                           |      |                          |        |  |

|                   | V <sub>REF</sub> H input range    |                                         |                                                                                          | 0                         |      | V <sub>DD</sub>          | V      |  |

|                   | V <sub>REF</sub> L input range    |                                         | $V_{REF}L < V_{REF}H$                                                                    | 0                         | GND  | V <sub>DD</sub>          | V      |  |

|                   | Reference input imp               | edance                                  |                                                                                          |                           | 100  |                          | kΩ     |  |

|                   |                                   |                                         | $V_{REF} = V_{DD} = 5 V$                                                                 |                           | 50   | 100                      |        |  |

|                   | Reference current                 |                                         | $V_{REF} = V_{DD} = 3 V$                                                                 |                           | 30   | 60                       | μA     |  |

| LOGIC             | INPUTS <sup>(2)</sup>             |                                         |                                                                                          |                           |      |                          |        |  |

|                   | Input current                     |                                         |                                                                                          |                           |      | ±1                       | μA     |  |

| V <sub>IN_L</sub> | Input low voltage                 |                                         | $IOV_{DD} \ge 2.7 V$                                                                     |                           |      | 0.3<br>IOV <sub>DD</sub> | V      |  |

| V <sub>IN_H</sub> | Input high voltage                |                                         | $IOV_{DD} \ge 2.7 V$                                                                     | 0.7<br>IOV <sub>DD</sub>  |      |                          | V      |  |

|                   | Pin capacitance                   |                                         |                                                                                          |                           |      | 3                        | pF     |  |

| POWER             | REQUIREMENTS                      |                                         |                                                                                          | 1                         |      |                          |        |  |

| V <sub>DD</sub>   | Supply voltage                    |                                         |                                                                                          | 2.7                       |      | 5.5                      | V      |  |

| IOV <sub>DD</sub> | I/O supply voltage <sup>(3)</sup> |                                         |                                                                                          | 1.8                       |      | $V_{DD}$                 | V      |  |

|                   |                                   | Normal operation                        | $V_{\text{DD}}$ = 3.6 to 5.5 V, $V_{\text{IH}}$ = IOV_{\text{DD}}, $V_{\text{IL}}$ = GND |                           | 150  | 200                      |        |  |

| I <sub>DD</sub>   | Supply current <sup>(4)</sup>     | (DAC active and excluding load current) | $V_{\text{DD}}$ = 2.7 to 3.6 V, $V_{\text{IH}}$ = IOV_{\text{DD}}, $V_{\text{IL}}$ = GND |                           | 100  | 150                      | μA     |  |

| 50                | cappi) canon                      | All power down modes                    | $V_{\text{DD}}$ = 3.6 to 5.5 V, $V_{\text{IH}}$ = IOV_{\text{DD}}, $V_{\text{IL}}$ = GND |                           | 0.2  | 2                        | μA     |  |

|                   |                                   | All power-down modes                    | $V_{\text{DD}}$ = 2.7 to 3.6 V, $V_{\text{IH}}$ = IOV_{\text{DD}}, $V_{\text{IL}}$ = GND |                           | 0.05 | 2                        | μΑ     |  |

| POWER             | EFFICIENCY                        |                                         |                                                                                          |                           |      |                          |        |  |

|                   | I <sub>OUT</sub> /I <sub>DD</sub> |                                         | $I_{LOAD} = 2 \text{ mA}, V_{DD} = 5 \text{ V}$                                          |                           | 93%  |                          |        |  |

| TEMPE             | RATURE RANGE                      |                                         |                                                                                          |                           |      |                          |        |  |

|                   | Specified performan               | се                                      |                                                                                          | -40                       |      | 105                      | °C     |  |

Specified by design and characterization; not production tested. For 1.8 V < IOV<sub>DD</sub> < 2.7 V, TI recommends that  $V_{IH} \ge 0.8$  IOV<sub>DD</sub>, and (2)  $V_{IL} \le 0.2 \text{ IOV}_{DD}$ . IOV<sub>DD</sub> operates down to 1.8 V with slightly degraded timing, as long as  $V_{IH} \ge 0.8 \text{ IOV}_{DD}$  and  $V_{IL} \le 0.2 \text{ IOV}_{DD}$ .

(3)

(4)  $I_{DD}$  tested with digital input code = 0032.

#### DAC7551-Q1

SLAS767B-JUNE 2011-REVISED MARCH 2015

www.ti.com

STRUMENTS

XAS

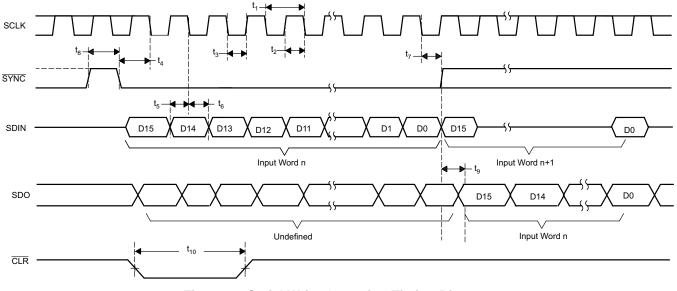

## 6.6 Timing Requirements<sup>(1)</sup>

All specifications at -40°C to +105°C,  $V_{DD}$  = 2.7 to 5.5 V, and  $R_L$  = 2 k $\Omega$  to GND (unless otherwise noted). See Figure 1.

|                                   |                                                               |                                                                      | MIN      | MAX                                   | UNIT |  |

|-----------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|----------|---------------------------------------|------|--|

| t <sub>1</sub> <sup>(2)</sup>     |                                                               | $V_{DD}$ = 2.7 V to 3.6 V                                            | 20       |                                       | 20   |  |

| ι <sub>1</sub> ,,                 | SCLK cycle time                                               | $V_{DD}$ = 3.6 V to 5.5 V                                            | 20       |                                       | ns   |  |

|                                   |                                                               | V <sub>DD</sub> = 2.7 V to 3.6 V                                     | 6.5      |                                       |      |  |

| t <sub>2</sub>                    | SCLK HIGH time                                                | $V_{DD}$ = 3.6 V to 5.5 V                                            | 6.5      |                                       | ns   |  |

|                                   |                                                               | V <sub>DD</sub> = 2.7 V to 3.6 V                                     | 6.5      |                                       |      |  |

| t <sub>3</sub>                    | SCLK LOW time                                                 | $V_{DD}$ = 3.6 V to 5.5 V                                            | 6.5      |                                       | ns   |  |

| t <sub>4</sub> SYNC fa            | <u>EV/NC</u> folling added to CCLL/ folling added active time | $V_{DD}$ = 2.7 V to 3.6 V                                            | 4        |                                       | 20   |  |

|                                   | SYNC falling edge to SCLK falling edge setup time             | $V_{DD}$ = 3.6 V to 5.5 V                                            | 4        |                                       | ns   |  |

|                                   | Data actua tima                                               | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$                           | 3        |                                       | 20   |  |

| t <sub>5</sub>                    | Data setup time                                               | $V_{DD}$ = 3.6 V to 5.5 V                                            | 3        |                                       | ns   |  |

|                                   | Data hald time                                                | $V_{DD}$ = 2.7 V to 3.6 V                                            | 3        |                                       | 20   |  |

| t <sub>6</sub>                    | Data hold time                                                | $V_{DD}$ = 3.6 V to 5.5 V                                            | 3        |                                       | ns   |  |

|                                   | COLIX falling adapts CVAIC rising adapt                       | V <sub>DD</sub> = 2.7 V to 3.6 V                                     | 0        | t <sub>1</sub> – 10 ns <sup>(3)</sup> |      |  |

| t <sub>7</sub>                    | SCLK falling edge to SYNC rising edge                         | $V_{DD}$ = 3.6 V to 5.5 V                                            | 0        | t <sub>1</sub> – 10 ns <sup>(3)</sup> | ns   |  |

|                                   | Minimum SYNC HIGH time                                        | $V_{DD}$ = 2.7 V to 3.6 V                                            | 20       |                                       | 20   |  |

| t <sub>8</sub>                    | Minimum Stric High line                                       | $V_{DD}$ = 3.6 V to 5.5 V                                            | 20       |                                       | ns   |  |

|                                   | SCLK folling adap to SDO volid                                | $V_{DD}$ = 2.7 V to 3.6 V                                            | 10       |                                       | 20   |  |

| lg                                |                                                               | $V_{DD}$ = 3.6 V to 5.5 V                                            | 10       |                                       | ns   |  |

|                                   |                                                               | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$                           | 10       |                                       | 20   |  |

| <b>1</b> 0                        | CLR puise width low                                           | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$                           | 10       |                                       | ns   |  |

| t <sub>9</sub><br>t <sub>10</sub> | SCLK falling edge to SDO valid                                | V <sub>DD</sub> = 3.6 V to 5.5 V<br>V <sub>DD</sub> = 2.7 V to 3.6 V | 10<br>10 |                                       |      |  |

All input signals are specified with  $t_R = t_F = 1$  ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ ) / 2. (1)

(2) (3) Maximum SCLK frequency is 50 MHz at  $V_{DD}$  = 2.7 to 5.5 V.

SCLK falling edge to  $\overline{SYNC}$  rising edge time shold not exceed (t<sub>1</sub> - 10 ns) to latch the correct data.

DAC7551-Q1

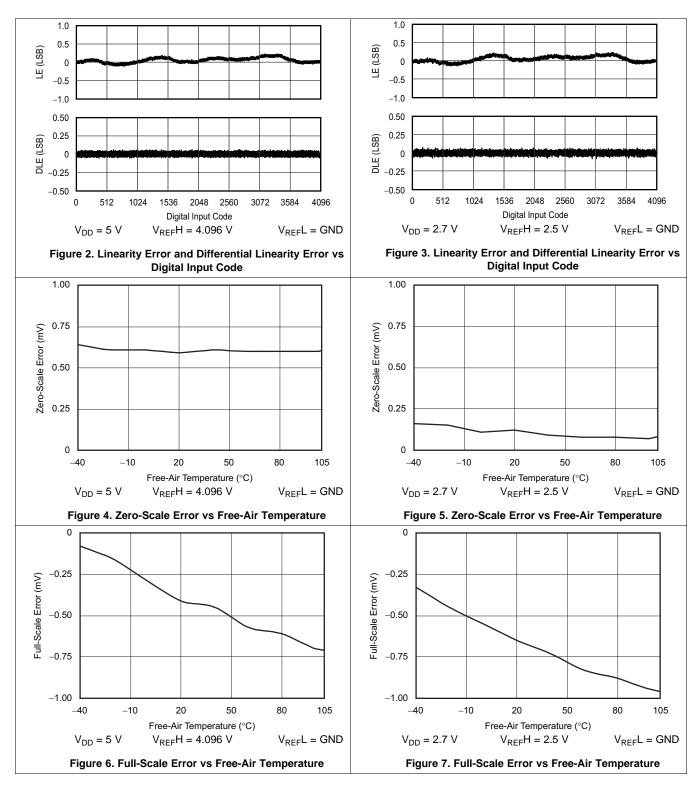

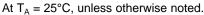

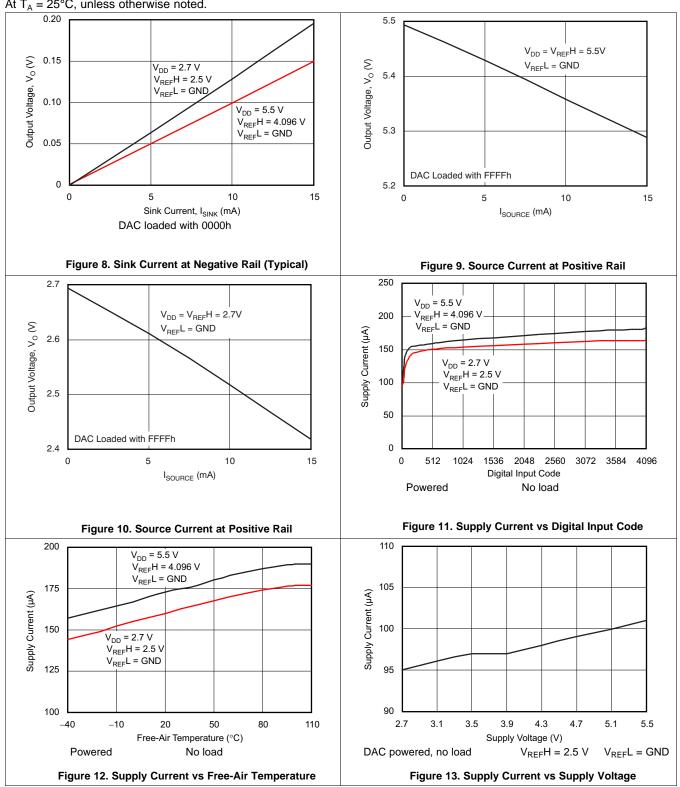

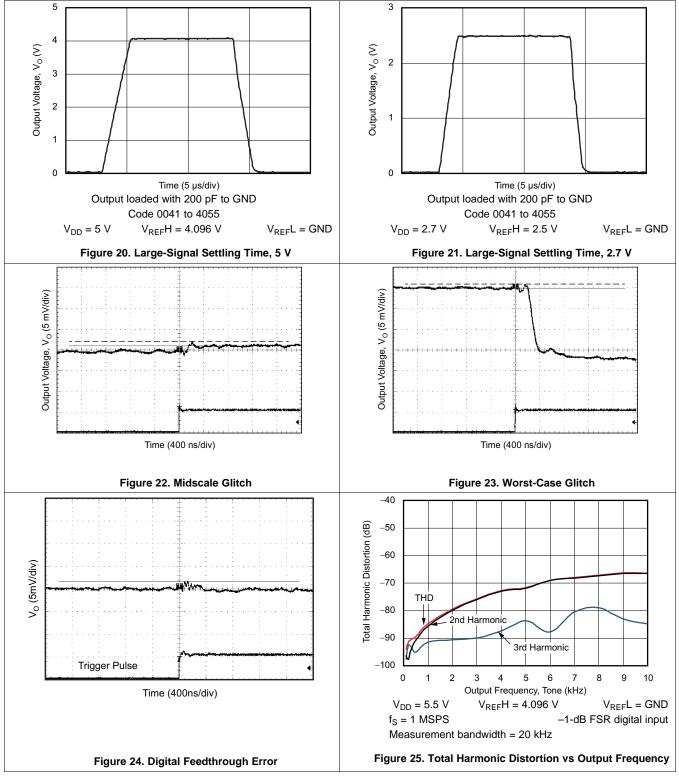

## 6.7 Typical Characteristics

At  $T_A = 25^{\circ}$ C, unless otherwise noted.

## Typical Characteristics (continued)

### **Typical Characteristics (continued)**

### **Typical Characteristics (continued)**

At  $T_A = 25^{\circ}C$ , unless otherwise noted.

### 7 Detailed Description

### 7.1 Overview

The DAC7551-Q1 device is a 12-bit resistor-string digital-to-analog converter (DAC). Unbuffered external reference inputs allow for a positive voltage reference as low as 0.25 V and as high as  $V_{DD}$ . An amplifier-feedback input is available for better DC accuracy at the load point. The device is controlled over a 16-bit word three-wire serial peripheral interface (SPI) up to 50 MHz with an option to daisy-chain multiple devices. An asynchronous clear function along with power-down features allows for software controlled resets and low-power consumption. A separate logic-supply input means the device can be used with different logic families across a wide range of supply voltages.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Digital-to-Analog Converter

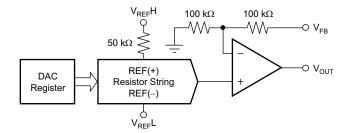

The architecture of the DAC7551-Q1 device consists of a string DAC followed by an output buffer amplifier. Figure 26 shows a generalized block diagram of the DAC architecture.

Figure 26. Typical DAC Architecture

The input coding to the DAC7551-Q1 device is unsigned binary, which gives the ideal output voltage as show in Equation 1.

$V_{OUT} = 2 \times V_{REF}L + (V_{REF}H - V_{REF}L) \times D / 4096$

where

• D is the decimal equivalent of the binary code that is loaded to the DAC register, which ranges from 0 to 4095.

(1)

12

#### Feature Description (continued)

#### 7.3.2 Resistor String

Figure 27 shows the resistor string section. This section is simply a string of resistors, each of value R. The digital code loaded to the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier. The voltage is tapped off by closing one of the switches connecting the string to the amplifier. The output of the DAC is specified monotonic because it is a string of resistors.

$V_{REF}H \rightarrow V_{REF}L$  R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R

Figure 27. Typical Resistor String

#### 7.3.3 Output Buffer Amplifiers

The output buffer amplifier is capable of generating rail-to-rail voltages on the output, providing an output range of 0 V to  $V_{DD}$ . The amplifier is capable of driving a load of 2 k $\Omega$  in parallel with up to 1000 pF to ground. Figure 8, Figure 9, and Figure 10 show the sink and source capabilities of the output amplifier. The slew rate is 1.8 V/µs with a half-scale settling time of 3 µs with the output unloaded.

### 7.3.3.1 DAC External Reference Input

The DAC7551-Q1 device contains  $V_{REF}H$  and  $V_{REF}L$  reference inputs which are unbuffered. The  $V_{REF}H$  reference voltage can be as low as 0.25 V, and as high as  $V_{DD}$  because there is no restriction of headroom and footroom from any reference amplifier.

Using a buffered reference in the external circuit is recommended (for example, the REF3140 device). The input impedance is typically 100 k $\Omega$ .

#### **Feature Description (continued)**

#### 7.3.3.2 Amplifier Sense Input

The DAC7551-Q1 device contains an amplifier-feedback input pin,  $V_{FB}$ . For voltage output operation,  $V_{FB}$  must be externally connected to  $V_{OUT}$ . For better DC accuracy, this connection should be made at load points. The  $V_{FB}$ pin is also useful for a variety of applications, including digitally-controlled current sources. The feedback input pin is internally connected to the DAC amplifier negative input terminal through a 100-k $\Omega$  resistor. The amplifier negative input terminal internally connects to ground through another 100-k $\Omega$  resistor (see Figure 26). These connections form a gain-of-two, noninverting, amplifier configuration. Overall gain remains 1 because the resistor string has a divide-by-two configuration. The resistance seen at the  $V_{FB}$  pin is approximately 200 k $\Omega$  to ground.

#### 7.3.3.3 Power-On Reset

On power up, all registers are cleared and the DAC channel is updated with zero-scale voltage. The DAC output remains in this state until valid data are written. This setup is particularly useful in applications where knowing the state of the DAC output while the device is powering up is important. To not turn on ESD protection devices,  $V_{DD}$  and  $IOV_{DD}$  should be applied before any other pin (such as  $V_{REF}H$ ) is brought high. The power-up sequence of  $V_{DD}$  and  $IOV_{DD}$  is irrelevant. Therefore,  $IOV_{DD}$  can be brought up before  $V_{DD}$ , or the other way around.

#### 7.3.3.4 Power Down

The DAC7551-Q1 device has a flexible power-down capability. During a power-down condition, the user has flexibility to select the output impedance of the DAC. During power-down operation, the DAC can have either  $1k\Omega$ ,  $100k\Omega$ , or Hi-Z output impedance to ground.

#### 7.3.3.5 Asynchronous Clear

The DAC7551-Q1 output is asynchronously set to zero-scale voltage immediately after the CLR pin is brought low. The CLR signal resets all internal registers and therefore functions similar to the power-on reset. The DAC7551-Q1 device updates at the first rising edge of the SYNC signal that occurs after the CLR pin is brought back to high.

#### 7.3.3.6 IOVDD and Level Shifters

The DAC7551-Q1 device can be used with different logic families that require a wide range of supply voltages. To enable this useful feature, the  $IOV_{DD}$  pin must be connected to the logic supply voltage of the system. All DAC7551-Q1 digital input and output pins are equipped with level-shifter circuits. Level shifters at the input pins ensure that external logic-high voltages are translated to the internal logic-high voltage, with no additional power dissipation. Similarly, the level shifter for the SDO pin translates the internal logic-high voltage ( $V_{DD}$ ) to the external logic-high level ( $IOV_{DD}$ ). For single-supply operation, the  $IOV_{DD}$  pin can be tied to the  $V_{DD}$  pin.

#### 7.3.4 Integral and Differential Linearity

The DAC7551-Q1 device uses precision thin-film resistors providing exceptional linearity and monotonicity. Integral linearity error is typically within  $\pm 0.35$  LSBs, and differential linearity error is typically within  $\pm 0.08$  LSBs.

#### 7.3.5 Glitch Energy

The DAC7551-Q1 device uses a proprietary architecture that minimizes glitch energy. The code-to-code glitches are so low that they are usually buried within the wide-band noise and cannot be easily detected. The DAC7551-Q1 glitch is typically well under 0.1 nV-s. Such low glitch energy provides more than a ten-time improvement over industry alternatives.

### 7.4 Device Functional Modes

The DAC7551-Q1 device uses four modes of operation. These modes are accessed by setting bit PD0 (DB13) and PD1 (DB14) in the control register. Table 1 shows how to control the operating mode with data bits PD0 (DB13) and PD1 (DB14). The DAC7551-Q1 device treats the power-down condition as data; all the operation modes are still valid for power down. Broadcasting a power-down condition to all the DAC7551-Q1 devices in a system is possible. Powering down a channel and updating data on other channels is also possible. Furthermore, writing to the DAC register or buffer of the DAC channel that is powered down is also possible. When the DAC is the powered on, the DAC contains this new value.

Copyright © 2011–2015, Texas Instruments Incorporated

#### **Device Functional Modes (continued)**

When both the PD0 and PD1 bits are set to 0, the device works normally with the typical consumption of 100  $\mu$ A at 2.7 V. For the three power-down modes, the supply current falls to 0.05  $\mu$ A at 2.7 V. As listed in Table 1, three different power-down options are available. The VOUT pin can be connected internally to GND through a 1-k $\Omega$  resistor or a 100-k $\Omega$  resistor or can be open circuited (High-Z). In other words, DB14 and DB13 = 11 represent a power-down condition with High-Z output impedance for a selected channel. DB14 and DB13 = 01 and 10 represent a power-down condition with a 1-k $\Omega$  and 100-k $\Omega$  output impedance respectively.

### 7.5 Programming

#### 7.5.1 Serial Interface

The DAC7551-Q1 device is controlled over a versatile 3-wire serial interface, which operates at clock rates up to 50 MHz and is compatible with SPI, QSPI, Microwire, and DSP interface standards.

|      | CON  | TROL          |               | DATA BITS |                 |

|------|------|---------------|---------------|-----------|-----------------|

| DB15 | DB14 | DB13<br>(PD1) | DB12<br>(PD0) | DB11–DB0  | FUNCTION        |

| Х    | Х    | 0             | 0             | data      | Normal mode     |

| Х    | Х    | 0             | 1             | Х         | Powerdown 1kΩ   |

| Х    | Х    | 1             | 0             | Х         | Powerdown 100kΩ |

| Х    | Х    | 1             | 1             | Х         | Powerdown Hi-Z  |

#### Table 1. Serial Interface Programming

#### 7.5.1.1 16-Bit Word and Input Shift Register

The input shift register is 16 bits wide. DAC data are loaded into the device as a 16-bit word under the control of a serial clock input, SCLK, as shown in Figure 1. The 16-bit word, listed in Table 1, consists of four control bits followed by 12 bits of DAC data. The data format is straight binary with all 0s corresponding to 0-V output and all 1s corresponding to full-scale output ( $V_{REF} - 1$  LSB). Data are loaded MSB first (bit 15) where the first two bits (DB15 and DB14) are *don't care* bits. Bit 13 and bit 12 (DB13 and DB12) determine either normal mode operation or power-down mode (see Table 1).

The SYNC input is a level-triggered input that acts as a frame synchronization signal and chip enable. Data can only be transferred into the device while the SYNC pin is low. To begin the serial data transfer, the SYNC pin should be taken low, observing the minimum SYNC-to-SCLK falling edge setup time, t<sub>4</sub>. After the SYNC pin goes low, serial data is shifted into the device input shift register on the falling edges of SCLK for 16 clock pulses.

The SPI is enabled after the SYNC pin becomes low and the data are continuously shifted into the shift register at each falling edge of the SCLK input. When the SYNC pin is brought high, the last 16 bits stored in the shift register are latched into the DAC register, and the DAC updates.

#### 7.5.1.2 Daisy-Chain Operation

Daisy-chain operation is used for updating serially-connected devices on the rising edge of the SYNC in.

As long as the SYNC pin is high, the SDO pin is in a high-impedance state. When the SYNC pin is brought low the output of the internal shift register is tied to the SDO pin. As long as the SYNC pin is low, the SDO pin duplicates the SDIN signal with a 16-cycle delay. To support multiple devices in a daisy chain, the SCLK and SYNC signals are shared across all devices, and the SDO pin of one DAC7551-Q1 device should be tied to the SDIN pin of the next DAC7551-Q1 device. For *n* devices in such a daisy chain, 16*n* SCLK cycles are required to shift the entire input data stream. After 16*n* SCLK falling edges are received, following a falling SYNC signal, the data stream becomes complete and the SYNC pin can be brought high to update *n* devices simultaneously. SDO operation is specified at a maximum SCLK speed of 10 MHz.

In daisy-chain mode, the use of a weak pulldown resistor on the SDO output pin, which provides the SDIN data for the next device in the chain, is recommended. For standalone operation, the maximum clock speed is 50 MHz. For daisy-chain operation, the maximum clock speed is 10 MHz.

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

#### 8.1.1 Waveform Generation

As a result of the exceptional linearity and low glitch of the DAC7551-Q1 device, the device is well-suited for waveform generation (from DC to 10kHz). The DAC7551-Q1 large-signal settling time is 5 µs, supporting an update rate of 200 kSPS. However, the update rates can exceed 1 MSPS if the waveform to be generated consists of small voltage steps between consecutive DAC updates. To obtain a high dynamic range, the REF3140 device (4.096 V) or the REF02 device (5 V) is recommended for reference-voltage generation.

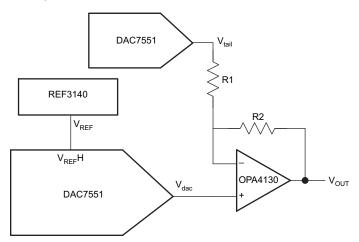

#### 8.1.2 Generating ±5-V, ±10-V, and ±12-V Outputs For Precision Industrial Control

Industrial control applications can require multiple feedback loops consisting of sensors, analog-to-digital converters (ADCs), microcontrollers (MCUs), DACs, and actuators. Loop accuracy and loop speed are the two important parameters of such control loops.

#### 8.1.2.1 Loop Accuracy

DAC offset, gain, and the integral linearity errors are not factors in determining the accuracy of the loop. As long as a voltage exists in the transfer curve of a monotonic DAC, the loop can find this voltage and settle to it. On the other hand, DAC resolution and differential linearity do determine the loop accuracy, because each DAC step determines the minimum incremental change the loop can generate. A DNL error less than -1 LSB (non-monotonicity) can create loop instability. A DNL error greater than 1 LSB implies unnecessarily large voltage steps and missed voltage targets. With high DNL errors, the loop loses stability, resolution, and accuracy. Offering 12-bit ensured monotonicity and ±0.08-LSB typical DNL error, the DAC755x devices are great choices for precision control loops.

#### 8.1.2.2 Loop Speed

Many factors determine the control-loop speed, such as ADC conversion time, MCU speed, and DAC settling time. Typically, the ADC conversion time, and the MCU computation time are the two major factors that dominate the time constant of the loop. DAC settling time is rarely a dominant factor because ADC conversion times usually exceed DAC conversion times. DAC offset, gain, and linearity errors can slow the loop down only during the startup. When the loop reaches the steady-state operation, these errors do not affect loop speed any further. Depending on the ringing characteristics of the loop-transfer function, DAC glitches can also slow the loop down. With a 1-MSPS (small-signal) maximum data-update rate, the DAC7551-Q1 device can support high-speed control loops. Ultralow glitch energy of the DAC7551-Q1 device significantly improves loop stability and loop settling time.

### 8.2 Typical Application

#### 8.2.1 Generating Industrial Voltage Ranges

For control-loop applications, DAC gain and offset errors are not important parameters. This consideration could be exploited to lower trim and calibration costs in a high-voltage control-circuit design. Using a quad operational amplifier (OPA4130), and a voltage reference (REF3140), the DAC7551-Q1 can generate the wide voltage swings required by the control loop.

### 8.2.1.1 Design Requirements

For ±5-V operation:

R1 = 10 kΩ R2 = 15 kΩ V<sub>tail</sub> = 3.33 V V<sub>REF</sub> = 4.096 V For ±10-V operation: R1 = 10 kΩ R2 = 39 kΩ V<sub>tail</sub> = 2.56 V V<sub>REF</sub> = 4.096 V For ±12-V operation: R1 = 10 kΩ R2 = 49 kΩ V<sub>tail</sub> = 2.45 V V<sub>REF</sub> = 4.096 V

### 8.2.1.2 Detailed Design Procedure

Use Equation 2 to calculate the output voltage of the configuration.

$$V_{OUT} = V_{REF} \left(\frac{R2}{R1} + 1\right) \frac{SDIN}{4096} - V_{tail} \left(\frac{R2}{R1}\right)$$

(2)

Fixed R1 and R2 resistors can be used to coarsely set the gain required in the first term of the equation. When R2 and R1 set the gain to include some minimal over-range gain, a single DAC7551-Q1 device can be used to set the required offset voltages. Residual errors are not an issue for loop accuracy because offset and gain errors can be tolerated. One DAC7551-Q1 device can provide the  $V_{tail}$  voltages, while four additional DAC7551-Q1 devices can provide the  $V_{dac}$  voltages to generate four high-voltage outputs. A single SPI is sufficient to control all five DAC7551-Q1 devices in a daisy-chain configuration.

### Typical Application (continued)

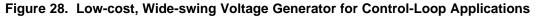

### 8.2.1.3 Application Curves

## 9 Power Supply Recommendations

The power applied to the V<sub>DD</sub> pin should be well regulated and low noise. Switching power supplies and DC-DC converters often have high frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high-frequency spikes as the internal logic switches states. This noise can easily couple into the DAC output voltage through various paths between power connections and analog output. As with the GND connection, the V<sub>DD</sub> pin should be connected to a power-supply plane of trace that is separate from the connection for digital logic until they are connected at the power-entry point. In addition, the use of a 1- $\mu$ F and 10- $\mu$ F capacitor and a 0.1- $\mu$ F bypass capacitor is strongly recommended. In some situations, additional bypassing may be required, such as a 100- $\mu$ F electrolytic capacitor or even a Pi filter made up of inductors and capacitors. These bypassing methods are all designed to low-pass filter the supply and remove the high-frequency noise.

Copyright © 2011–2015, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

### 10 Layout

### **10.1 Layout Guidelines**

A precision analog component requires careful layout, adequate bypassing, and clean, well-regulated power supplies. The DAC7551-Q1 device offers single-supply operation, and is often used in close proximity with digital logic, microcontrollers, microprocessors, digital signal processors, or a combination. The more digital logic present in the design and the higher the switching speed, the more difficult it is to prevent digital noise from appearing at the output. As a result of the single ground pin of the DAC7551-Q1 device, all return currents (including digital and analog return currents for the DAC) must flow through a single point. Ideally, the GND should be connected directly to an analog ground plane. This plane should be separate from the ground connection for the digital components until these components were connected at the power-entry point of the system.

### 10.2 Layout Example

) Via to power ground plane

$\rightarrow$  Connection to MCU, MPU, or DSP

Figure 32. DAC7551-Q1 Layout Example

## **11** Device and Documentation Support

### **11.1 Documentation Support**

#### 11.1.1 Related Documentation

For related documentation, see the following:

- OPA4130 Low Power, Precision FET-INPUT OPERATIONAL AMPLIFIERS, SBOS053

- REF02 +5V Precision VOLTAGE REFERENCE, SBVS003

- REF3140 15ppm/°C Max, 100µA, SOT23-3 SERIES VOLTAGE REFERENCE, SBVS046

### 11.2 Trademarks

SPI, QSPI are trademarks of Motorola, Inc. All other trademarks are the property of their respective owners.

### 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.4 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| DAC7551TDRNRQ1   | ACTIVE        | USON         | DRN                | 12   | 3000           | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -40 to 105   | RAN                     | Samples |

| DAC7551ZTDRNRQ1  | ACTIVE        | USON         | DRN                | 12   | 3000           | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -40 to 105   | SJT                     | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### OTHER QUALIFIED VERSIONS OF DAC7551-Q1 :

Catalog: DAC7551

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

Texas

NSTRUMENTS

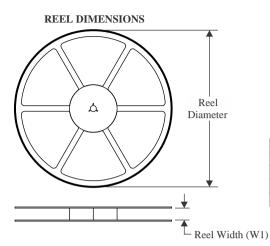

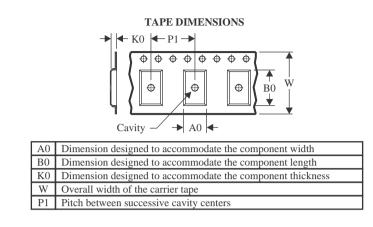

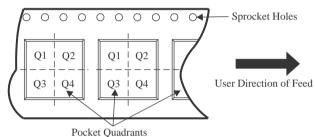

### TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | U U  | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DAC7551TDRNRQ1              | USON | DRN                | 12 | 3000 | 330.0                    | 12.4                     | 2.3        | 3.3        | 0.7        | 4.0        | 12.0      | Q1               |

| DAC7551ZTDRNRQ1             | USON | DRN                | 12 | 3000 | 330.0                    | 12.4                     | 2.3        | 3.3        | 0.7        | 4.0        | 12.0      | Q1               |

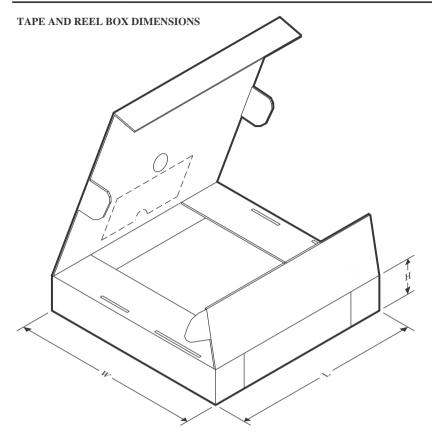

# PACKAGE MATERIALS INFORMATION

6-May-2023

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC7551TDRNRQ1  | USON         | DRN             | 12   | 3000 | 338.0       | 355.0      | 50.0        |

| DAC7551ZTDRNRQ1 | USON         | DRN             | 12   | 3000 | 338.0       | 355.0      | 50.0        |

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. SON (Small Outline No-Lead) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. Package complies to JEDEC MO-229.

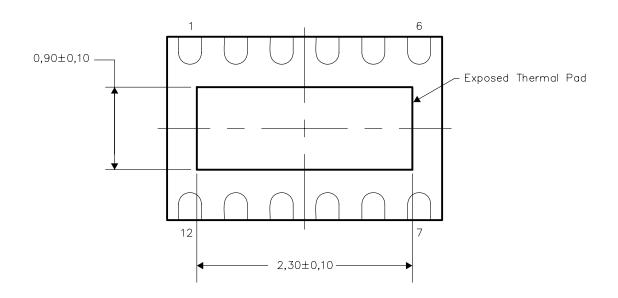

## THERMAL PAD MECHANICAL DATA

## DRN (R-PDSO-N12)

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, Quad Flatpack No-Lead Logic Packages, Texas Instruments Literature No. SCBA017. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

DRN (R-PUSON-N12)

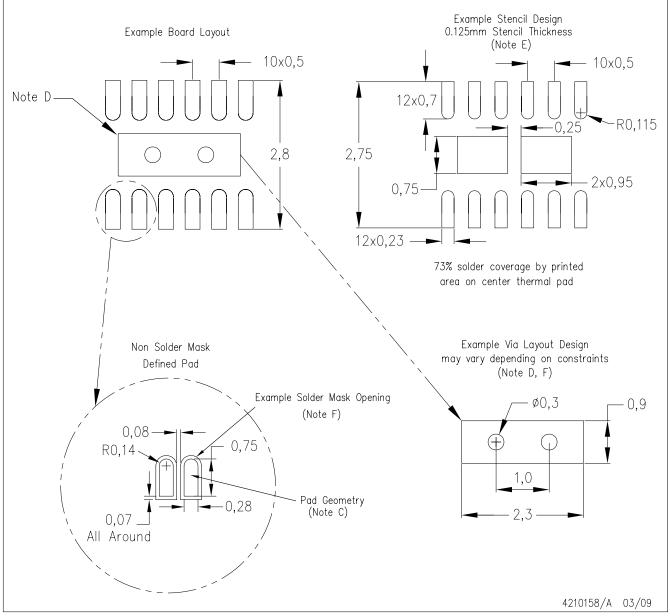

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- $\mathsf{F}. \quad \mathsf{Customers \ should \ contact \ their \ board \ fabrication \ site \ for \ minimum \ solder \ mask \ web \ tolerances \ between \ signal \ pads.}$

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated