# LM74680 Ideal Diode Bridge Controller for Low Loss Rectification

### 1 Features

- Input operating voltage range: 5V to 80V

- 100V absolute maximum

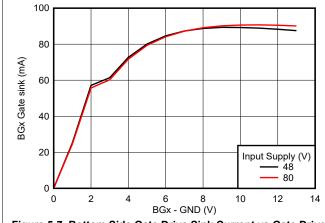

- 4× integrated gate drive control

- 165µA gate pull-up strength

- 100mA gate pull-down strength

- Linear gate regulation control for supply ORing applications

- V<sub>TG REG</sub> = 11mV

- Enable pin for user-controlled device on/off

- -40°C to 125°C operating junction temperature

- Small footprint: 3mm × 3mm VQFN-12

- Meets IPC-9592 spacing rules

# 2 Applications

- Video door bell

- IP cameras

- **Thermostat**

- Power distribution systems (24Vac)

- Polarity agnostic power inputs

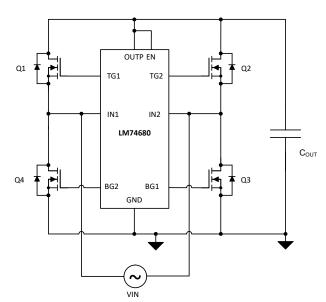

**Typical Application Schematic**

## 3 Description

The LM74680 is an ideal diode bridge controller that provides voltage rectification by driving four N-channel MOSFETs in a full-bridge configuration. LM74680 enables lower voltage drop and reduced power dissipation as compared to conventional diode bridge rectifiers. This helps to simplify the power supply design, eliminate heat sinks, and reduce PCB area. The integrated charge pump allows use of N-channel MOSFETs, which are smaller and more cost-effective than P-channel MOSFETs for the same power level. It also offers fast response to reverse current conditions for protection against input short events. The LM74680 has an enable pin which allows for the gate driver to be either enabled or disabled by an external signal. The LM74680 supports voltage rectification from DC to 1kHz.

This device is characterized for operation over a junction temperature range of -40°C to +125°C.

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| LM74680     | DRR (WSON, 12)         | 3mm × 3mm                   |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

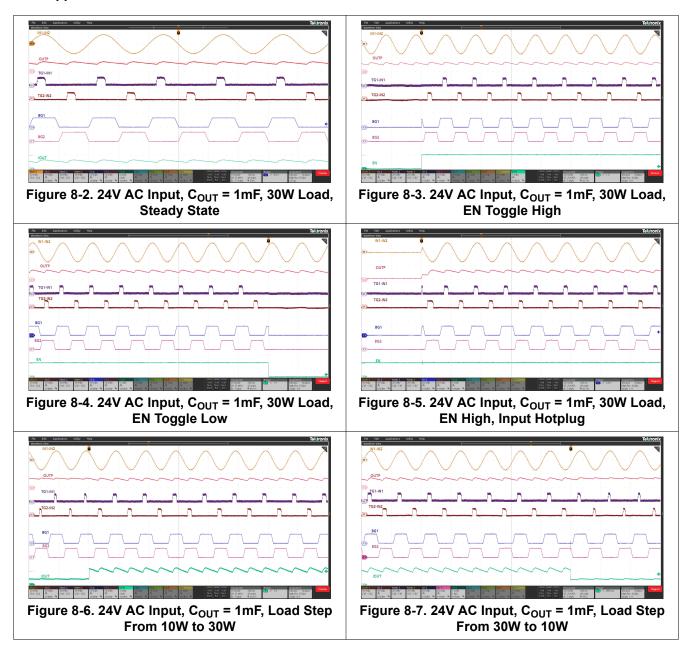

24V AC Input, C<sub>OUT</sub> = 1mF, 30W Load, Steady State

# **Table of Contents**

| 1 Features                           | 1              | 7.3 Feature Description                             | 11 |

|--------------------------------------|----------------|-----------------------------------------------------|----|

| 2 Applications                       | 1              | 7.4 Device Functional Modes                         | 13 |

| 3 Description                        | 1              | 8 Application and Implementation                    | 14 |

| 4 Pin Configuration and Functions    | 3              | 8.1 Application Information                         | 14 |

| 5 Specifications                     | 4              | 8.2 Typical Application                             |    |

| 5.1 Absolute Maximum Ratings         | 4              | 8.3 Power Supply Recommendations                    |    |

| 5.2 ESD Ratings                      | 4              | 8.4 Layout                                          | 17 |

| 5.3 Recommended Operating Conditions |                | 9 Device and Documentation Support                  |    |

| 5.4 Thermal Information              |                | 9.1 Receiving Notification of Documentation Updates |    |

| 5.5 Electrical Characteristics       | <mark>5</mark> | 9.2 Support Resources                               | 19 |

| 5.6 Switching Characteristics        |                | 9.3 Trademarks                                      | 19 |

| 5.7 Typical Characteristics          |                | 9.4 Electrostatic Discharge Caution                 | 19 |

| 6 Parameter Measurement Information  |                | 9.5 Glossary                                        |    |

| 7 Detailed Description               | 10             | 10 Revision History                                 |    |

| 7.1 Overview                         | 10             | 11 Mechanical, Packaging, and Orderable             |    |

| 7.2 Functional Block Diagram         |                | Information                                         | 19 |

| •                                    |                |                                                     |    |

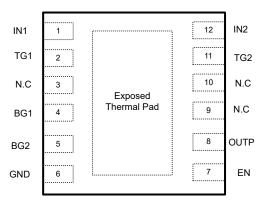

# 4 Pin Configuration and Functions

Figure 4-1. DRR Package, 12-Pin WSON (Top View)

**Table 4-1. Pin Functions**

|     | PIN  | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                            |

|-----|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME | 1/0(-/             | DESCRIPTION                                                                                                                            |

| 1   | IN1  | I                  | Bridge rectifier input 1. Connect to top side MOSFET Q1 source and bottom side MOSFET Q4 drain.                                        |

| 2   | TG1  | 0                  | Top side MOSFET gate drive 1.                                                                                                          |

| 3   | N.C  | _                  | No connection.                                                                                                                         |

| 4   | BG1  | 0                  | Bottom side MOSFET gate drive 1.                                                                                                       |

| 5   | BG2  | 0                  | Bottom side MOSFET gate drive 2.                                                                                                       |

| 6   | GND  | G                  | Device ground. Connect to bottom side MOSFETs Q3 and Q4 source and output ground.                                                      |

| 7   | EN   | I                  | Enable pin. Can be connected to OUTP for always ON operation                                                                           |

| 8   | OUTP | I                  | Bridge rectifier output. Connect to top side MOSFETs Q1 and Q2 drain. Connect a minimum of 0.1µF between OUTP and GND close to the IC. |

| 9   | N.C  | _                  | No connection.                                                                                                                         |

| 10  | N.C  | _                  | No connection.                                                                                                                         |

| 11  | TG2  | 0                  | Top side MOSFET gate drive 2.                                                                                                          |

| 12  | IN2  | I                  | Bridge rectifier input 2. Connect to top side MOSFET Q2 source and bottom side MOSFET Q3 drain.                                        |

<sup>(1)</sup> I = input, O = output, G = ground

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                               |                           | MIN  | MAX    | UNIT |

|-----------------------------------------------|---------------------------|------|--------|------|

|                                               | OUTP to GND               | -0.3 | 100    |      |

| Input Pine                                    | IN1, IN2 to GND           | -2   | OUTP+2 | V    |

| Input Pins                                    | EN to GND                 | -0.3 | OUTP   | V    |

|                                               | IN1-IN2                   | -100 | 100    |      |

| Output Pins                                   | BG1, BG2 to GND           | -0.3 | 15     | V    |

| Output Pilis                                  | TG1 to IN1 and TG2 to IN2 | -0.3 | 15     | V    |

| Operating junction temperature <sup>(2)</sup> |                           | -40  | 150    | °C   |

| Storage temperature, T <sub>stg</sub>         |                           | -40  | 150    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                    |                          |                                                                           | VALUE | UNIT                                  |

|--------------------|--------------------------|---------------------------------------------------------------------------|-------|---------------------------------------|

| V                  | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/ JEDEC JS-001 <sup>(1)</sup>        | ±2000 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| V <sub>(ESD)</sub> | Liectiostatic discriarge | Charged device model (CDM), per JEDEC specification JS-002 <sup>(2)</sup> | ±500  | '                                     |

<sup>1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                                                  |                                                     | MIN | NOM MAX | UNIT |

|--------------------------------------------------|-----------------------------------------------------|-----|---------|------|

| Input Pins                                       | OUTP to GND                                         | 5   | 80      | V    |

| Imput Filis                                      | EN to GND                                           | 0   | OUTP    | V    |

| Input to Output pins                             | OUTP to INx                                         | -80 |         | V    |

| External<br>MOSFET max<br>V <sub>GS</sub> rating | GATE to SOURCE                                      | 15  |         | V    |

| TJ                                               | Operating junction temperature range <sup>(2)</sup> | -40 | 150     | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see Section 5.5.

### 5.4 Thermal Information

|                       |                                              | LM74680    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DRR (WSON) | UNIT |

|                       |                                              | 12 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 60.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 48         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 31.5       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.2        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 31.4       | °C/W |

Product Folder Links: LM74680

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# 5.4 Thermal Information (continued)

| THERMAL METRIC <sup>(1)</sup> |                                              | LM74680    |      |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | DRR (WSON) | UNIT |

|                               |                                              | 12 PINS    |      |

| R <sub>0</sub> JC(bot)        | Junction-to-case (bottom) thermal resistance | 7.1        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **5.5 Electrical Characteristics**

$T_J = -40$ °C to +125°C; typical values at  $T_J = 25$ °C, OUTP = 24 V,  $V_{EN} = OUTP$ ,  $C_{OUT}$ : 1  $\mu F$  over operating free-air temperature range (unless otherwise noted)

|                                      | PARAMETER                              | TEST CONDITIONS                                                                            | MIN   | TYP  | MAX   | UNIT |

|--------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------|-------|------|-------|------|

| SUPPLY VOLTA                         | GE                                     | 1                                                                                          |       |      | -     |      |

| V <sub>OUTP</sub>                    | OUTP voltage range                     |                                                                                            | 5     |      | 80    | V    |

| V <sub>OUTP_PORR</sub>               | OUTP POR rising threshold              |                                                                                            | 3.72  | 4.3  | 4.8   | V    |

| V <sub>OUTP_PORF</sub>               | OUTP POR falling threshold             |                                                                                            | 3.4   | 4.0  | 4.5   | V    |

| V <sub>OUTP_POR_Hys</sub>            | OUTP POR Hysteresis                    |                                                                                            |       | 0.3  |       | V    |

| IQ                                   | Operating Quiescent Current            | OUTP = 24V                                                                                 |       | 270  | 450   | μA   |

| I <sub>SHDN</sub>                    | Shutdown Supply Current                | V <sub>EN</sub> = 0 V                                                                      |       | 0.27 | 3.82  | μA   |

| I <sub>INx</sub>                     | Input pin current                      | V <sub>INx</sub> – V <sub>OUTP</sub> = 30mV                                                |       | 10   | 16    | μA   |

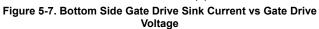

| ENABLE INPUT                         |                                        |                                                                                            |       |      | '     |      |

| V <sub>EN_IL</sub>                   | Enable input low threshold             |                                                                                            | 0.413 | 0.7  | 0.96  | V    |

| V <sub>EN_IH</sub>                   | Enable input high threshold            |                                                                                            | 0.631 | 0.9  | 1.15  | V    |

| V <sub>EN_Hys</sub>                  | Enable Hysteresis                      |                                                                                            | 0.134 | 0.2  | 0.265 | V    |

| I <sub>EN</sub>                      | Enable sink current                    | V <sub>EN</sub> = 48 V                                                                     |       | 72   | 241   | nA   |

| V <sub>IN</sub> to V <sub>OUTP</sub> |                                        |                                                                                            |       |      | '     |      |

| $V_{FWD}$                            | Reverse to forward turn ON threshold   |                                                                                            | 169   | 195  | 226   | mV   |

| $V_{REV}$                            | Threshold for reverse current blocking |                                                                                            | -17   | -11  | -5    | mV   |

| V <sub>TG_REG</sub>                  | Top side gate regulation voltage       |                                                                                            | 7     | 11   | 16    | mV   |

| V <sub>TG_REG_SINK</sub>             | Top side regulation sink current       |                                                                                            | 5     | 10   | 16    | μA   |

| V <sub>TG_FC</sub>                   | Full conduction threshold              |                                                                                            |       | 56   |       | mV   |

| GATE DRIVE                           |                                        |                                                                                            | '     |      |       |      |

| $V_{TGx} - V_{INx}$                  | Top Gate Drive Voltage                 |                                                                                            | 8.7   | 10   | 11.1  | V    |

| $V_{BGx} - V_{GND}$                  | Bottom Gate Drive Voltage              |                                                                                            | 11.96 | 13   | 13.85 | V    |

| 1                                    | Peak source current                    | V <sub>INx</sub> – V <sub>GND</sub> = 100 mV,<br>V <sub>TGx</sub> – V <sub>INx</sub> = 5 V | 124   | 165  | 210   | μΑ   |

| I <sub>TGx</sub>                     | Peak sink current                      | $V_{INx} - V_{GND} = -50 \text{ mV},$<br>$V_{TGx} - V_{INx} = 5 \text{ V}$                 |       | 100  |       | mA   |

| 1                                    | Peak source current                    | V <sub>BGx</sub> – V <sub>GND</sub> = 5 V                                                  | 1.8   | 2.5  | 3.5   | mA   |

| I <sub>BGx</sub>                     | Peak sink current                      | V <sub>BGx</sub> – V <sub>GND</sub> = 5 V                                                  |       | 80   |       | mA   |

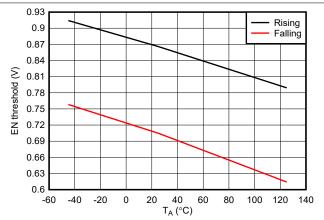

# 5.6 Switching Characteristics

$T_J = -40^{\circ}$ C to +125°C; typical values at  $T_J = 25^{\circ}$ C, OUTP = 24 V,  $V_{EN} = OUTP$ ,  $C_{OUT}$ : 1uF over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------------------------|-----------------|-----|-----|-----|------|

| EN <sub>TDLY</sub> | Enable (low to high) to TGx Turn On delay |                 |     | 175 | 300 | μs   |

| EN <sub>TDLY</sub> | Enable (low to high) to BGx Turn On delay |                 |     | 6.5 | 11  | μs   |

Copyright © 2024 Texas Instruments Incorporated

# **5.6 Switching Characteristics (continued)**

$T_J$  = -40°C to +125°C; typical values at  $T_J$  = 25°C, OUTP = 24 V,  $V_{EN}$  = OUTP,  $C_{OUT}$ : 1uF over operating free-air temperature range (unless otherwise noted)

|                                  | PARAMETER                                       | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT |

|----------------------------------|-------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

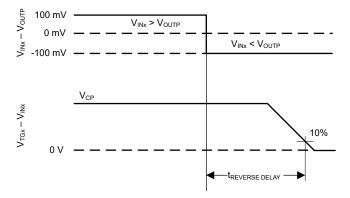

| t <sub>Reverse Delay</sub>       | Reverse voltage detection to TGx Turn Off delay | V <sub>(IN)</sub> – V <sub>(OUTP)</sub> = 100 mV to –100 mV  |     | 2   | 3.5 | μs   |

| t <sub>Forward</sub><br>Recovery | Forward voltage detection to TGx Turn On delay  | $V_{(IN)} - V_{(OUTP)} = -100 \text{ mV to } 700 \text{ mV}$ |     | 5   | 9.1 | μs   |

${\it Copyright @ 2024 Texas Instruments Incorporated}$  Product Folder Links:  ${\it LM74680}$

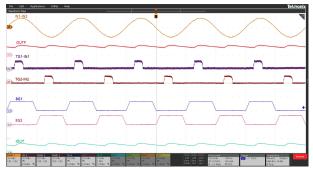

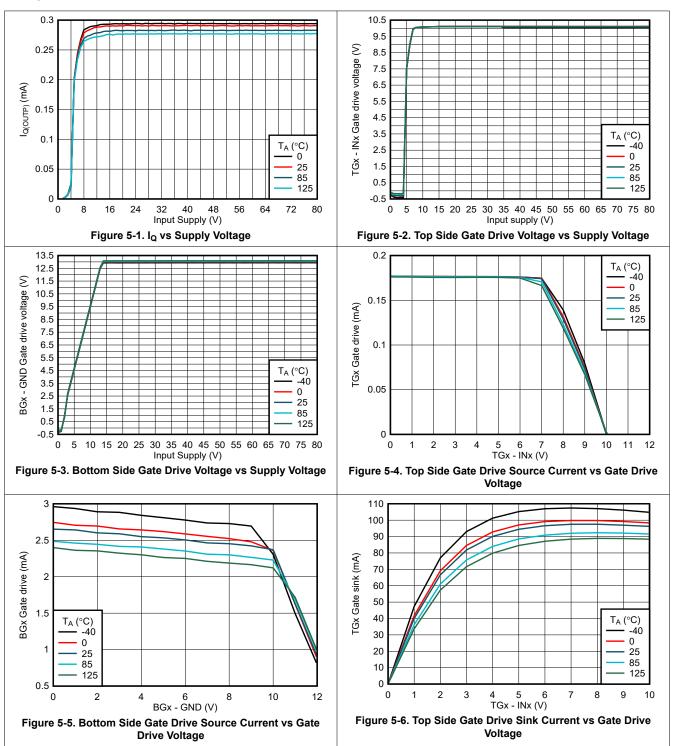

# 5.7 Typical Characteristics

# **5.7 Typical Characteristics (continued)**

Figure 5-8. Enable Threshold vs Temperature

# **6 Parameter Measurement Information**

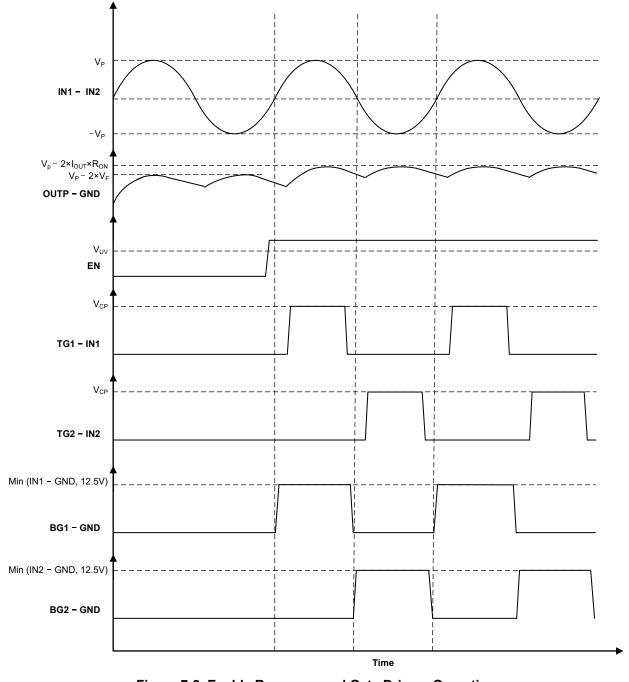

Figure 6-1. Timing Waveforms

# 7 Detailed Description

### 7.1 Overview

The LM74680 is an ideal diode bridge controller designed for efficient input voltage rectification in applications requiring high performance and low power loss. It operates by driving four external N-channel MOSFETs in a full-bridge configuration. During startup, the MOSFET body diodes conduct and rectify the input voltage. Once the output voltage is above the power-on-reset threshold ( $V_{OUTP\_PORR}$ ) and the EN pin voltage is above high threshold ( $V_{EN\_IH}$ ), the LM74680 transitions to active control mode.

In active mode, the controller utilizes an internal charge pump to drive the MOSFET gates high, enabling low voltage drop forward conduction. Internal comparators monitor current flow to ensure the MOSFETs are turned off during reverse current conditions, effectively emulating an ideal diode bridge. The LM74680 is well suited for power critical applications such as video surveillance systems, building automation, and other electronics requiring robust and efficient power delivery.

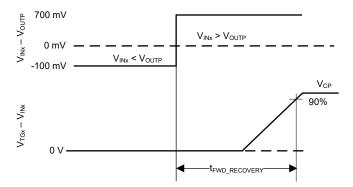

### 7.2 Functional Block Diagram

Product Folder Links: *LM74680*

Copyright © 2024 Texas Instruments Incorporated

### 7.3 Feature Description

### 7.3.1 Input and Output Voltage

LM74680 supports power sources with wide input voltage range enabling both AC power source (12VAC, 24VAC) or a DC polarity-agnostic power source to be connected to its IN1 and IN2 pins. LM74680 is designed to operate with IN1 and IN2 designed to vary from 80V to -80V.

The OUTP pin is used to power the LM74680 internal circuitry, typically drawing  $I_Q$  when enabled and  $I_{SHDN}$  when disabled. If the OUTP pin voltage is greater than the power-on-reset rising threshold, then LM74680 operates in either shutdown mode or active mode in accordance with the EN pin voltage. LM74680 supports an OUTP voltage up to 80V during normal operation and can withstand voltage transients up to 100V ensuring protection against surges.

### 7.3.2 Charge Pump

The internal charge pump supplies the voltage necessary to drive the gate of the external N-channel MOSFETs. The charge pump is activated once the EN pin voltage is above the specified input high threshold,  $V_{EN\_IH}$ . If EN pin is pulled low, then the charge pump remains disabled. By enabling and disabling the charge pump, the operating guiescent current of the LM74680 can be optimized as per system requirements.

#### 7.3.3 Gate Drivers

The gate drivers are used to control the external N-Channel MOSFETs by setting the GATE to SOURCE voltage to the corresponding mode of operation. The FETs on the top side Q1 and Q2 are driven by gates TG1 and TG2 and the FETs on the bottom side Q3 and Q4 are driven by gates BG1 and BG2 respectively.

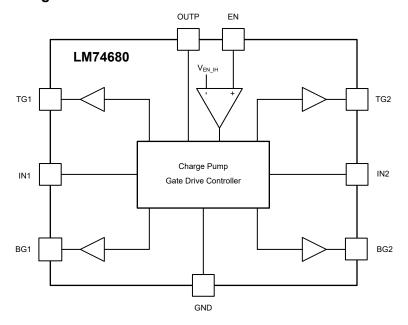

The internal charge pump powers the top side gate drivers and depending on the DRAIN to SOURCE voltage of each MOSFET, LM74680 has three defined modes of operation the gate driver operates under which are forward regulation, full conduction mode and reverse current protection. These modes are described in more detail in Section 7.4.1.1, Section 7.4.1.2, and Section 7.4.2. Figure 7-1 depicts how the modes of operation vary according to the DRAIN to SOURCE voltage. The threshold between forward regulation and conduction modes is when the DRAIN to SOURCE voltage is  $V_{TG\_REG}$ . The threshold between forward regulation mode and reverse current protection mode is when the DRAIN to SOURCE voltage is  $V_{TG\_REG}$ .

Figure 7-1. Gate Driver Mode Transitions

The bottom-side gate drivers of the LM74680 are powered directly from the IN1 or IN2 voltage and operate in two distinct modes which are forward full conduction and reverse current blocking. These gate drivers are controlled by the following logic to ensure efficient power flow and protection against reverse current.

- BG1 is enabled and in full conduction when the voltage at IN1 is greater than that GND+2V and is disabled when IN1 falls below IN2 to block reverse current flow.

- Similarly, BG2 is enabled when IN2 exceeds GND+2V and is disabled when IN2 is lower than IN1.

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

### 7.3.4 Enable

The LM74680 has an enable pin, EN. The enable pin allows for the gate driver to be either enabled or disabled by an external signal. If the EN pin voltage is greater than the rising threshold, the gate driver and charge pump are activated as described in Section 7.3.3 and Section 7.3.2. If the enable pin voltage is less than the input low threshold, the charge pump and gate drivers are disabled placing the LM74680 in shutdown mode.

If the application doesn't need external ON/OFF control, the EN pin can be connected directly to OUTP pin.

Figure 7-2. Enable Response and Gate Drivers Operation

### 7.4 Device Functional Modes

#### 7.4.1 Conduction Mode

Conduction mode occurs when the top gate drivers are enabled and there are two regions of operating in this mode based on the source to drain voltage of the FETs driven by LM74680. The modes are described in Section 7.4.1.1 and Section 7.4.1.2.

#### 7.4.1.1 Regulated Conduction Mode

For the LM74680 to operate its top gates TG1 and TG2 in regulated conduction mode, the gate driver must be enabled as described in Section 7.3.3 and the current from source to drain of the external MOSFET must be within the range to result in an INx to OUTP voltage drop of  $V_{REV}$  to  $V_{TG\_FC}$ . During forward regulation mode, the INx to OUTP voltage is regulated to  $V_{TG\_REG}$  by adjusting the gate to source voltage. This closed loop regulation scheme enables graceful turn-off of the MOSFET at very light loads and ensures zero DC reverse current flow.

#### 7.4.1.2 Full Conduction Mode

For the LM74680 to operate its top gates TG1 and TG2 in full conduction mode the gate driver must be enabled as described in Section 7.3.3 and the current from source to drain of the external MOSFET must be large enough to result in an INx to OUTP voltage drop of greater than  $V_{TG\_FC}$ . If these conditions are achieved the GATE pin is internally connected to the charge pump resulting in the INx to OUTP voltage being equal to  $V_{TGx} - V_{INx}$ . By connecting the internal charge pump to GATE the external MOSFET  $R_{DS(ON)}$  is minimized reducing the power loss of the external MOSFET when forward currents are large.

#### 7.4.2 Reverse Current Protection Mode

For the LM74680 to operate in reverse current protection mode, the gate driver must be enabled as described in Section 7.3.3 and the current of the external MOSFET must be flowing from the drain to the source. When the INx to OUTP voltage is typically less than  $V_{REV}$ , reverse current protection mode is entered and the FET gates is internally connected to the source. This connection of the TGx to INx pin disables the external MOSFET. The body diode of the MOSFET blocks any reverse current from flowing from the drain to source.

Copyright © 2024 Texas Instruments Incorporated

# 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

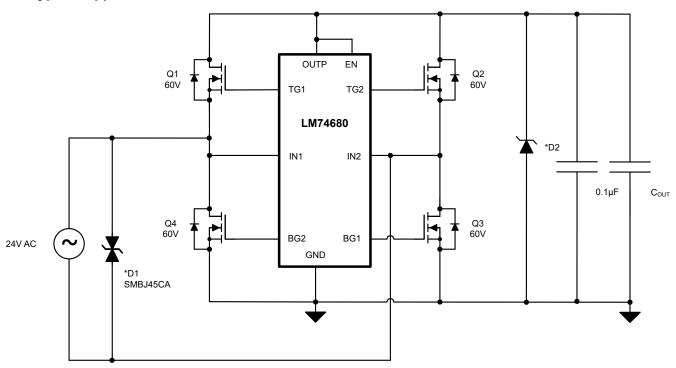

# 8.1 Application Information

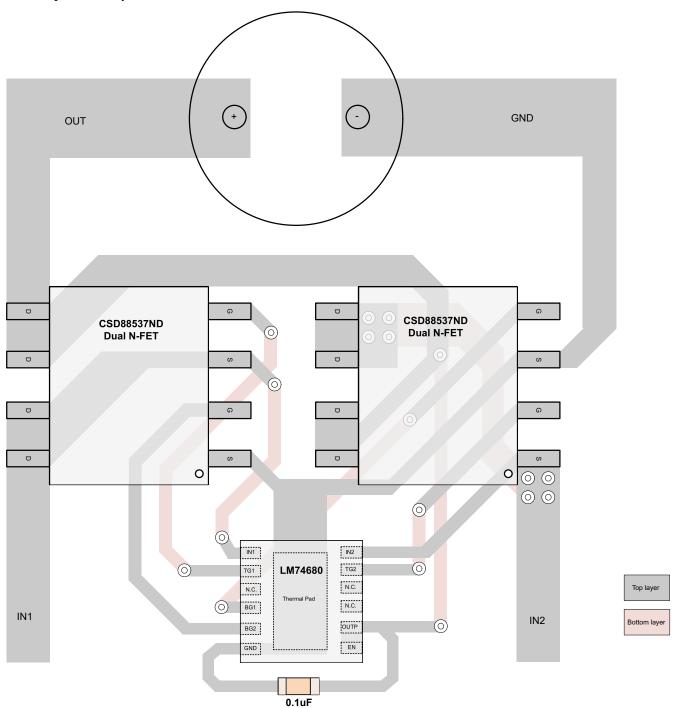

The LM74680 drives four external N-channel MOSFETs in a diode bridge configuration, making it ideal for rectifying an AC power supplies or polarity-agnostic DC power supplies. By replacing traditional diodes with MOSFETs, the device minimizes conduction losses, resulting in improved thermal performance and increased overall system efficiency. This makes it suitable for applications such as video door bell, industrial automation, HVAC systems, and other AC-powered equipment where low power loss and high reliability are critical. The schematic for a 24V AC input application is shown in Figure 8-1 where the LM74680 is driving the high side MOSFETs Q1, Q2 and low side MOSFETs Q3, Q4 in diode bridge configuration.

## 8.2 Typical Application

\*Optional components for transient protection

Figure 8-1. Typical Application Circuit

### 8.2.1 Design Requirements

A design example, with system design parameters listed in Table 8-1 is presented.

Table 8-1. Design Parameters

| DESIGN PARAMETER        | EXAMPLE VALUE      |

|-------------------------|--------------------|

| Input voltage and range | 24V AC ±10%        |

| Maximum load current    | 2A                 |

| Output voltage ripple   | 10V <sub>p-p</sub> |

Product Folder Links: LM74680

### 8.2.2 Detailed Design Procedure

### 8.2.2.1 Design Considerations

- Input operating voltage range, including line transients

- Maximum load current

- · Maximum ripple of output voltage

### 8.2.2.2 MOSFET Selection

The important MOSFET electrical parameters are the maximum continuous drain current  $I_D$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the maximum gate-to-source voltage  $V_{GS(MAX)}$ , and the drain-to-source ON resistance  $R_{DS(ON)}$ .

The  $V_{DS(MAX)}$  rating of the MOSFET must be high enough to withstand the highest differential voltage seen in the application, including any anticipated transients during fault conditions. For a 24V AC system, a MOSFET with a voltage rating of 60V is recommended. The LM74680 can drive a maximum gate-to-source voltage of 13.8V. A MOSFET with a minimum  $V_{GS(MAX)}$  rating of 15V should be selected. For MOSFETs with lower  $V_{GS}$  ratings, a Zener diode can be used to clamp the voltage to a safe level.

The MOSFET  $I_D$  rating must exceed the maximum continuous load current to ensure reliable operation under full load conditions. Additionally, the MOSFET thermal resistance should be considered to ensure the junction temperature  $(T_J)$  remains within safe limits under the expected maximum power dissipation including the initial inrush phase when the output capacitors are charged through the MOSFETs body diode. This helps maintain reliability and performance in the application.

To reduce the MOSFET conduction losses, the lowest possible  $R_{DS(ON)}$  is preferred, but selecting a MOSFET based on low  $R_{DS(ON)}$  may not always be beneficial. Higher  $R_{DS(ON)}$  will provide increased voltage information to LM74680 reverse comparator at a lower reverse current. Reverse current detection is better with increased  $R_{DS(ON)}$ . Choosing a MOSFET with  $R_{DS(ON)}$  that develops <30mV forward voltage drop at maximum current is a good starting point. Usually,  $R_{DS(ON)}$  increases drastically below 4.5V  $V_{GS}$  and  $R_{DS(ON)}$  is highest when  $V_{GS}$  is close to MOSFET  $V_{th}$ . For stable regulation at light load conditions, it is recommended to operate the MOSFET close to 4.5V  $V_{GS}$ , that is, much higher than the MOSFET gate threshold voltage. It is recommended to choose MOSFET gate threshold voltage  $V_{th}$  of 2.5V to 3.5V maximum. Choosing a lower  $V_{th}$  MOSFET also reduces the turn ON time.

CSD88537ND Dual N-channel MOSFET from Texas Instruments is selected to meet this 24VAC bridge rectifier design and it is rated at:

- V<sub>DS(MAX)</sub>: 60V

- V<sub>GS(MAX)</sub>: ±20V

- $R_{DS(ON)}$ : 12.5m $\Omega$  (typical) and 15m $\Omega$  (maximum) at 10V  $V_{GS}$

#### 8.2.2.3 Output Capacitance

A minimum ceramic capacitor of  $0.1\mu F$  is recommended to be placed across the OUTP and GND pins as close to the LM74680 as possible for decoupling. Additional output capacitance  $C_{OUT}$  may be required to ensure that the rectified output voltage remains within the recommended operating range of the LM74680 and also to meet the output voltage ripple requirements of downstream circuitry depending on the system's tolerance.

The additional capacitance required between OUTP and GND is based on the downstream power demands and the allowable voltage ripple.  $C_{OUT}$  in the hundreds to thousands of microfarads is common. A good starting point is selecting  $C_{OUT}$  such that:

$$C_{OUT} \ge I_{LOAD} / (V_{RIPPLE} \times 2 \times Freq)$$

(1)

Where.

- I<sub>LOAD</sub> is the average output load current

- V<sub>RIPPLE</sub> is the maximum tolerable output ripple voltage

- Freq is the frequency of the input AC source

For example, in a 50Hz, 24V AC application where the load current is 1A and the tolerable ripple is 1V, choose  $C_{OUT} \ge 1A/(10V \times 2 \times 50Hz) = 1mF$ .

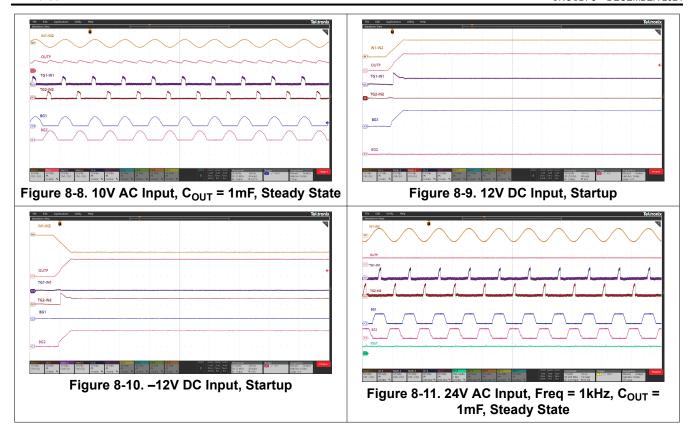

## 8.2.3 Application Curves

# 8.3 Power Supply Recommendations

### 8.3.1 Transient Protection

The TVS at input or output is not required for the LM74680 to operate, but it may be required to clamp the voltage transients caused by lightning, switching surges, or power disturbances that can exceed the voltage ratings of MOSFETs and the controller possibly causing damage. A TVS diode protects against such events by clamping the transient voltages to safe levels. For 24V AC systems, a bidirectional TVS with a standoff voltage above the AC peak and a clamping voltage below the MOSFET's maximum rating is recommended. In well-regulated applications with minimal transient risks, a TVS diode may not be necessary.

To avoid output voltage buildup during input hotplug conditions due to coupling from MOSFET gate capacitance using MOSFETs with input capacitance of at least 1nF is recommended. If the input capacitance of the selected MOSFET is less than 1nF, add a 1nF capacitor between the gate and source of the top-side MOSFETs.

### 8.4 Layout

# 8.4.1 Layout Guidelines

- Place the decoupling capacitor close to the OUTP pin and IC GND.

- For the top side MOSFETs, connect the INx, TGx, and OUTP pins of LM74680 close to the MOSFET SOURCE, GATE, and DRAIN pins.

- The high current path is through the MOSFETs, therefore it is important to use thick and short traces for the source and drain of the MOSFET to minimize resistive losses.

- The TGx and BGx pins of the LM74680 must be connected to the respective MOSFET gate with a short trace.

- Place transient suppression components close to LM74680.

- Obtaining acceptable performance with alternate layout schemes is possible, however the layout shown in Section 8.4.2 is intended as a guideline and to produce good results.

# 8.4.2 Layout Example

Figure 8-12. LM74680 Example Layout

# 9 Device and Documentation Support

# 9.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Notifications* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 9.2 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

### 9.3 Trademarks

TI E2E™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

## 9.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 9.5 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

## 10 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2024 | *        | Initial Release |

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated