**PCM1809** SBASB12 - MAY 2024

# PCM1809 Stereo Channel, 102dB Dynamic Range Audio ADC

#### 1 Features

- Stereo low power ADC:

- 2-channel analog microphones or line-in

- ADC line and microphone differential and singleended input performance:

- PCM1809 dynamic range:

- Differential Input: 104dB

- Single-ended Input: 102dB

- THD+N: –95 dB

- 2-V<sub>RMS</sub> differential full-scale input

- **Direct Coupling**

- Wide Input Common Mode support

- AC/DC Coupling support

- ADC sample rate ( $f_S$ ) = 8 kHz to 192 kHz

- Hardware pin control configurations

- Linear-phase or low-latency filter selection

- Flexible audio serial data interface:

- Controller or target interface selection

- 32-bits, 2-channel TDM

- 32-bits, 2-channel I<sup>2</sup>S

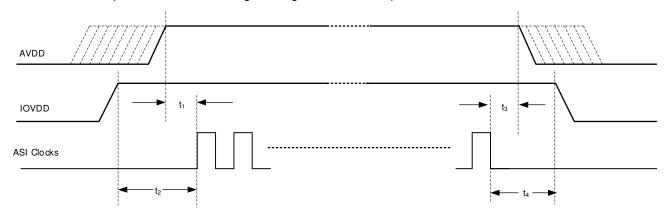

- Automatic power-down upon loss of audio clocks

- Integrated high-performance audio PLL

- Single-supply operation: 3.3 V

- I/O-supply operation: 3.3 V or 1.8 V

- Power consumption for 3.3-V AVDD supply:

- 19.6 mW/channel at 16-kHz sample rate

- 21.3 mW/channel at 48-kHz sample rate

# 2 Applications

- **Smart Speakers**

- **DVD** recorders and players

- **AV** receivers

- Video conference systems

- IP network cameras

## 3 Description

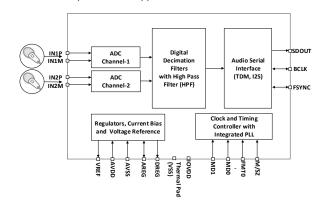

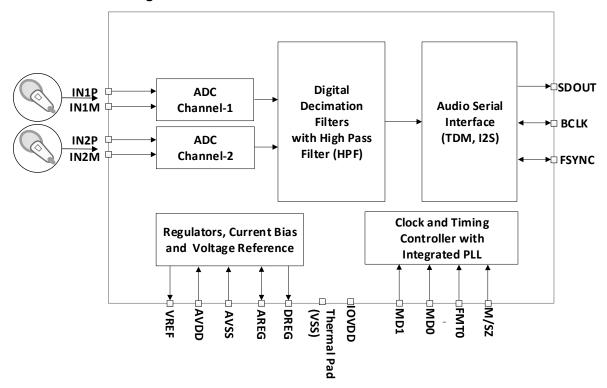

The PCM1809 is a low power audio analog-to-digital converter (ADC) that supports simultaneous sampling of up to two analog channels. The device supports single-ended and differential line and microphone inputs with a 2V<sub>RMS</sub> full-scale differential signal. The device integrates a phase-locked loop (PLL), a DC removal high-pass filter (HPF), and supports sample rates up to 192kHz. The device supports time-division multiplexing (TDM) or I2S audio formats, selectable with the hardware pin level. Additionally, the PCM1809 supports Controller and target mode selection for the audio bus interface operation. These integrated features, along with the ability to be powered from a single supply of 3.3V, make the device an excellent choice for cost-sensitive, spaceconstrained audio systems in microphone recording applications.

The PCM1809 is specified from -40°C to +105°C, and is offered in a 20-pin WQFN package.

### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE(2)                     |

|-------------|------------------------|-------------------------------------|

| PCM1809     | WQFN (20)              | 3.00mm × 3.00mm<br>with 0.5mm pitch |

- For all available packages, see the package option addendum at the end of the data sheet.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

Simplified Block Diagram

# **Table of Contents**

| 1 Features1                                                      |

|------------------------------------------------------------------|

| 2 Applications1                                                  |

| 3 Description1                                                   |

| 4 Pin Configuration and Functions3                               |

| 5 Specifications4                                                |

| 5.1 Absolute Maximum Ratings4                                    |

| 5.2 ESD Ratings4                                                 |

| 5.3 Recommended Operating Conditions4                            |

| 5.4 Thermal Information4                                         |

| 5.5 Electrical Characteristics5                                  |

| 5.6 Timing Requirements: TDM, I <sup>2</sup> S or LJ Interface 6 |

| 5.7 Switching Characteristics: TDM, I <sup>2</sup> S or LJ       |

| Interface7                                                       |

| 5.8 Typical Characteristics8                                     |

| 6 Detailed Description9                                          |

| 6.1 Overview9                                                    |

| 6.2 Functional Block Diagram9                                    |

| 6.3 Feature Description 10                                       |

| 6.4 Device Functional Modes                        | 22                 |

|----------------------------------------------------|--------------------|

| 7 Application and Implementation                   | 23                 |

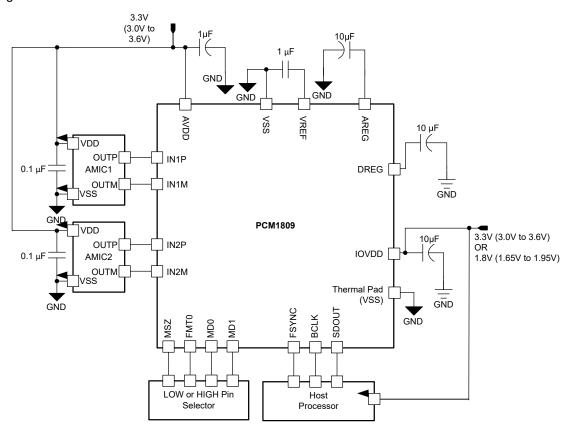

| 7.1 Application Information                        | 23                 |

| 7.2 Typical Application                            |                    |

| 8 Power Supply Recommendations                     |                    |

| 9 Layout                                           | 26                 |

| 9.1 Layout Guidelines                              |                    |

| 9.2 Layout Example                                 | 26                 |

| 10 Device and Documentation Support                | <mark>27</mark>    |

| 10.1 Receiving Notification of Documentation Updat | es <mark>27</mark> |

| 10.2 Support Resources                             | 27                 |

| 10.3 Trademarks                                    | 27                 |

| 10.4 Electrostatic Discharge Caution               | <mark>27</mark>    |

| 10.5 Glossary                                      | <mark>27</mark>    |

| 11 Revision History                                |                    |

| 12 Mechanical, Packaging, and Orderable            |                    |

| Information                                        | 27                 |

|                                                    |                    |

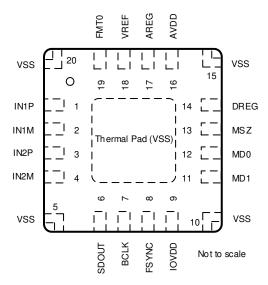

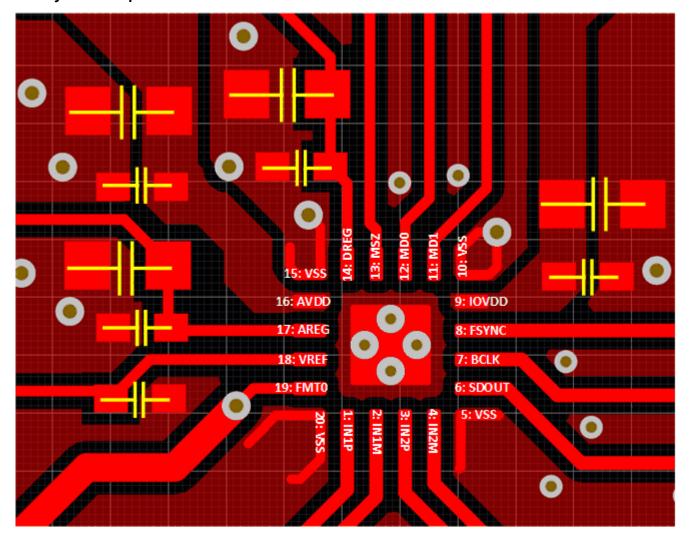

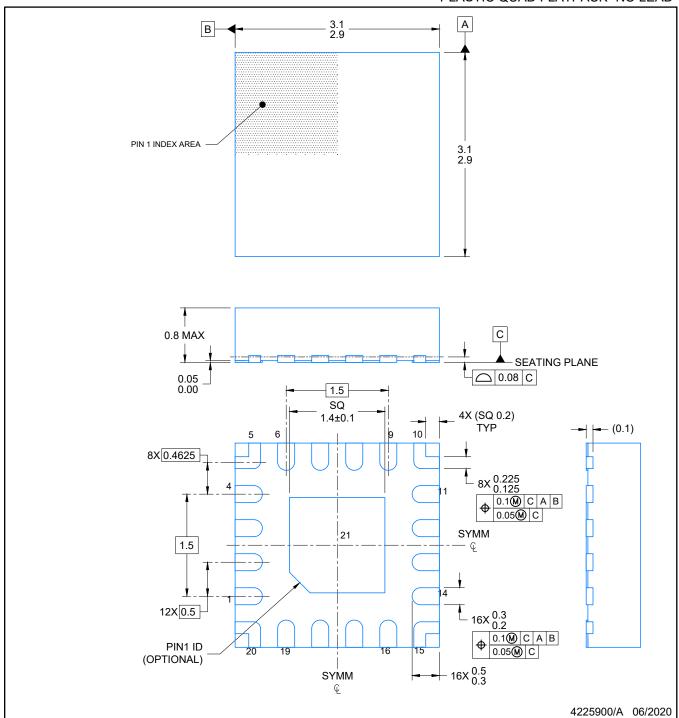

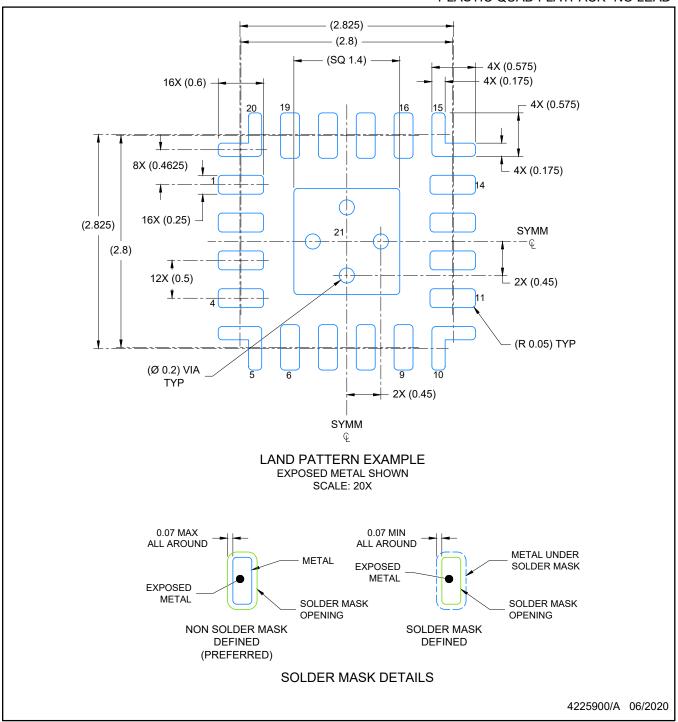

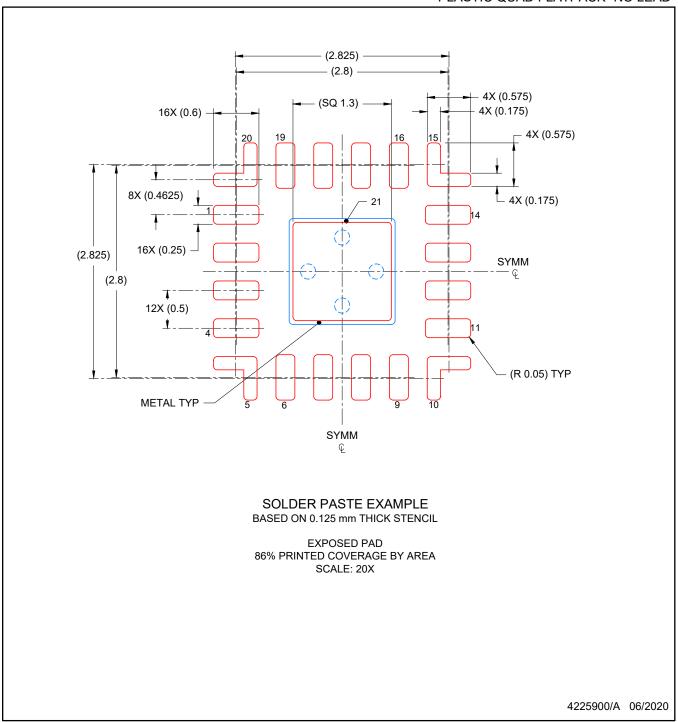

# **4 Pin Configuration and Functions**

Figure 4-1. RTE Package, 20-Pin WQFN With Exposed Thermal Pad, Top View

**Table 4-1. Pin Functions**

|        | PIN          | TYPE           | DESCRIPTION                                                                                      |  |  |  |

|--------|--------------|----------------|--------------------------------------------------------------------------------------------------|--|--|--|

| NO.    | NAME         | - ITPE         | BESSAII NON                                                                                      |  |  |  |

| 1      | IN1P         | Analog input   | Analog input 1P pin.                                                                             |  |  |  |

| 2      | IN1M         | Analog input   | Analog input 1M pin.                                                                             |  |  |  |

| 3      | IN2P         | Analog input   | Analog input 2P pin.                                                                             |  |  |  |

| 4      | IN2M         | Analog input   | Analog input 2M pin.                                                                             |  |  |  |

| 5      | VSS          | Analog Supply  | Short this pin directly to the board ground plane.                                               |  |  |  |

| 6      | SDOUT        | Digital output | Audio serial data interface bus output.                                                          |  |  |  |

| 7      | BCLK         | Digital I/O    | Audio serial data interface bus bit clock.                                                       |  |  |  |

| 8      | FSYNC        | Digital I/O    | Audio serial data interface bus frame synchronization signal.                                    |  |  |  |

| 9      | IOVDD        | Digital supply | Digital I/O power supply (1.8 V or 3.3 V, nominal).                                              |  |  |  |

| 10     | VSS          | Analog supply  | Short this pin directly to the board ground plane.                                               |  |  |  |

| 11     | MD1          | Digital input  | Device configuration mode select 1 pin.                                                          |  |  |  |

| 12     | MD0          | Digital input  | Device configuration mode select 0 pin.                                                          |  |  |  |

| 13     | MSZ          | Digital input  | Audio interface bus controller or target select pin.                                             |  |  |  |

| 14     | DREG         | Digital supply | Digital regulator output voltage for digital core supply (1.5 V, nominal).                       |  |  |  |

| 15     | VSS          | Analog supply  | Short this pin directly to the board ground plane.                                               |  |  |  |

| 16     | AVDD         | Analog supply  | Analog power (3.3 V, nominal).                                                                   |  |  |  |

| 17     | AREG         | Analog supply  | Analog on-chip regulator output voltage for analog supply (1.8 V, nominal).                      |  |  |  |

| 18     | VREF         | Analog         | Analog reference voltage filter output.                                                          |  |  |  |

| 19     | FMT0         | Digital input  | Audio interface format select pin referred to AVDD supply.                                       |  |  |  |

| 20     | VSS          | Analog supply  | Short this pin directly to the board ground plane.                                               |  |  |  |

| Therma | al Pad (VSS) | Ground supply  | Thermal pad shorted to internal device ground. Short thermal pad directly to board ground plane. |  |  |  |

# **5 Specifications**

### 5.1 Absolute Maximum Ratings

over the operating ambient temperature range (unless otherwise noted)(1)

|                            |                                                 | MIN  | MAX         | UNIT |

|----------------------------|-------------------------------------------------|------|-------------|------|

|                            | AVDD to AVSS                                    | -0.3 | 3.9         |      |

| Supply voltage             | AREG to AVSS                                    | -0.3 | 2.0         | V    |

|                            | IOVDD to VSS (thermal pad)                      | -0.3 | 3.9         |      |

| Ground voltage differences | AVSS to VSS (thermal pad)                       | -0.3 | 0.3         | V    |

| Analog input voltage       | Analog input pins voltage to AVSS               | -0.3 | AVDD + 0.3  | V    |

| Digital input voltage      | Digital input pins voltage to VSS (thermal pad) | -0.3 | IOVDD + 0.3 | V    |

|                            | Operating ambient, T <sub>A</sub>               | -40  | 105         |      |

| Temperature                | Junction, T <sub>J</sub>                        | -40  | 150         | °C   |

|                            | Storage, T <sub>stg</sub>                       | -65  | 150         |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                    |                                              |                                                                                | VALUE | UNIT                                  |

|--------------------|----------------------------------------------|--------------------------------------------------------------------------------|-------|---------------------------------------|

| V                  | V <sub>(ESD)</sub>   Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | \/                                    |

| V <sub>(ESD)</sub> |                                              | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

|                              |                                                                                                      | MIN  | NOM | MAX    | UNIT |

|------------------------------|------------------------------------------------------------------------------------------------------|------|-----|--------|------|

| POWER                        |                                                                                                      |      |     |        |      |

| AVDD,<br>AREG <sup>(1)</sup> | Analog supply voltage AVDD to AVSS (AREG is generated using onchip regulator) - AVDD 3.3-V operation | 3.0  | 3.3 | 3.6    | V    |

| IOVDD                        | IO supply voltage to VSS (thermal pad) - IOVDD 3.3-V operation                                       | 3.0  | 3.3 | 3.6    | V    |

| IOVDD                        | IO supply voltage to VSS (thermal pad) - IOVDD 1.8-V operation                                       | 1.65 | 1.8 | 1.95   |      |

| INPUTS                       |                                                                                                      |      |     |        |      |

|                              | Analog input pins and FMT0 voltage to VSS                                                            | 0    |     | AVDD   | V    |

|                              | Digital input pins voltage(except FMT0) to VSS (thermal pad)                                         | 0    |     | IOVDD  | V    |

| TEMPERA                      | TURE                                                                                                 |      |     |        |      |

| T <sub>A</sub>               | Operating ambient temperature                                                                        | -40  |     | 105    | °C   |

| OTHERS                       |                                                                                                      |      |     | '      |      |

|                              | Digital input pin used as MCLK input clock frequency                                                 |      |     | 36.864 | MHz  |

| CL                           | Digital output load capacitance                                                                      |      | 20  | 50     | pF   |

<sup>(1)</sup> AVSS and VSS (thermal pad): all ground pins must be tied together and must not differ in voltage by more than 0.2 V.

#### **5.4 Thermal Information**

|                               |                                           | PCM1809    |      |

|-------------------------------|-------------------------------------------|------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                           | RTE (WQFN) | UNIT |

|                               |                                           | 20 PINS    |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance    | 55.9       | °C/W |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance | 33.1       | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance      | 23.4       | °C/W |

|                        |                                              | PCM1809    |      |

|------------------------|----------------------------------------------|------------|------|

| THERMAL METRIC(1)      |                                              | RTE (WQFN) | UNIT |

|                        |                                              | 20 PINS    |      |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.6        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 23.3       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 16.7       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the spra953 application report.

### 5.5 Electrical Characteristics

at  $T_A$  = 25°C, AVDD = 3.3 V, IOVDD = 3.3 V,  $f_{IN}$  = 1-kHz sinusoidal signal,  $f_S$  = 48 kHz, 32-bit audio data, BCLK = 256 ×  $f_S$ , TDM target mode (unless otherwise noted)

|          | PARAMETER                                            | TEST CONDITIONS                                                                                        | MIN TYP | MAX | UNIT             |

|----------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------|-----|------------------|

| ADC CONF | FIGURATION                                           |                                                                                                        |         |     |                  |

|          | AC input impedance<br>(PCM1821)                      | Input pins INxP or INxM                                                                                | 10      |     | kΩ               |

| ADC PERF | FORMANCE FOR LINE, MICRO                             | PHONE INPUT RECORDING : AVDD 3.3-V OPERATION                                                           |         |     |                  |

|          | Differential input full-scale<br>AC signal voltage   | AC-coupled input                                                                                       | 2       |     | V <sub>RMS</sub> |

| SNR      | Signal-to-noise ratio, A-weighted <sup>(1)</sup> (2) | IN1 differential input selected and AC signal shorted to ground                                        | 104     |     | dB               |

| DR       | Dynamic range, A-weighted <sup>(1)</sup> (2)         | IN1 differential input selected and –60-dB full-scale AC signal input                                  | 104     |     | dB               |

| THD+N    | Total harmonic distortion <sup>(2)</sup>             | IN1 differential input selected and –1-dB full-scale AC signal input                                   | -95     |     | dB               |

|          | Differential input full-scale<br>AC signal voltage   | DC-coupled input                                                                                       | 2       |     | V <sub>RMS</sub> |

| SNR      | Signal-to-noise ratio, A-weighted <sup>(1)</sup> (2) | IN1 differential input with DC coupling selected and AC signal shorted to ground                       | 104     |     | dB               |

| DR       | Dynamic range, A-<br>weighted <sup>(1)</sup> (2)     | IN1 differential input with DC coupling selected and –60-dB full-scale AC signal input                 | 104     |     | dB               |

| THD+N    | Total harmonic distortion <sup>(2)</sup>             | IN1 differential input with DC coupling selected and –1-dB full-scale AC signal input                  | -95     |     | dB               |

|          | Single Ended input full-<br>scale AC signal voltage  | AC-coupled input                                                                                       | 1       |     | $V_{RMS}$        |

| SNR      | Signal-to-noise ratio, A-weighted <sup>(1)</sup> (2) | IN1 Single ended input with AC coupling on IN1P with IN1M ground and AC signal shorted to ground       | 100 102 |     | dB               |

| DR       | Dynamic range, A-weighted <sup>(1)</sup> (2)         | IN1 Single ended input with AC coupling on IN1P with IN1M ground and –60-dB full-scale AC signal input | 102     |     | dB               |

| THD+N    | Total harmonic distortion <sup>(2)</sup>             | IN1 Single ended input with AC coupleing on IN1P with IN1M ground and -1-dB full-scale AC signal input | -88     |     | dB               |

|          | Single Ended input full-<br>scale AC signal voltage  | DC-coupled input                                                                                       | 1       |     | $V_{RMS}$        |

| SNR      | Signal-to-noise ratio, A-weighted <sup>(1)</sup> (2) | IN1 Single ended input with DC coupling on IN1P with IN1M ground and AC signal shorted to ground       | 102     |     | dB               |

| DR       | Dynamic range, A-<br>weighted <sup>(1)</sup> (2)     | IN1 Single ended input with DC coupling on IN1P with IN1M ground and –60-dB full-scale AC signal input | 102     |     | dB               |

| THD+N    | Total harmonic distortion <sup>(2)</sup>             | IN1 Single ended input with DC coupling on IN1P with IN1M ground and -1-dB full-scale AC signal input  | -88     |     | dB               |

| ADC OTHE | ER PARAMETERS                                        |                                                                                                        |         |     |                  |

|          | Output data sample rate                              |                                                                                                        | 7.35    | 192 | kHz              |

|          | Output data sample word length                       |                                                                                                        |         | 32  | Bits             |

|          | Interchannel isolation                               | -1-dB full-scale AC-signal input to non measurement channel                                            | -124    |     | dB               |

|          | Interchannel gain mismatch                           | -6-dB full-scale AC-signal input                                                                       | 0.1     |     | dB               |

|          | Gain drift <sup>(4)</sup>                            | Across temperature range -40°C to 105°C                                                                | 40.5    |     | ppm/°C           |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

at  $T_A$  = 25°C, AVDD = 3.3 V, IOVDD = 3.3 V,  $f_{IN}$  = 1-kHz sinusoidal signal,  $f_S$  = 48 kHz, 32-bit audio data, BCLK = 256 ×  $f_S$ , TDM target mode (unless otherwise noted)

|                    | PARAMETER                                                       | TEST CONDITIONS                                                                                        | MIN             | TYP    | MAX             | UNIT       |  |

|--------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|--------|-----------------|------------|--|

|                    | Interchannel phase mismatch                                     | 1-kHz sinusoidal signal                                                                                |                 | 0.02   |                 | Degrees    |  |

|                    | Phase drift <sup>(5)</sup>                                      | 1-kHz sinusoidal signal, across temperature range -40°C to 105°C                                       |                 | 0.0005 |                 | Degrees/°C |  |

| PSRR               | Power-supply rejection ratio                                    | 100-mV <sub>PP</sub> , 1-kHz sinusoidal signal on AVDD, differential input selected, 0-dB channel gain |                 | 102    |                 | dB         |  |

| PSRR               | Power-supply rejection ratio                                    | 100-mV <sub>PP</sub> , 1-kHz sinusoidal signal on AVDD, single ended input selected, 0-dB channel gain |                 | 102    |                 | dB         |  |

| DIGITAL I/O        | )                                                               |                                                                                                        |                 |        |                 |            |  |

|                    | Low-level digital input logic                                   | All digital pins except FMT0, IOVDD 1.8-V operation                                                    | -0.3            |        | 0.30 ×<br>IOVDD | V          |  |

| $V_{IL}$           | voltage threshold                                               | All digital pins except FMT0, IOVDD 3.3-V operation                                                    | -0.3            |        | 0.8             |            |  |

|                    |                                                                 | FMT0 Pin                                                                                               | -0.3            |        | 0.8             | V          |  |

|                    |                                                                 | All digital pins except FMT0, IOVDD 1.8-V operation                                                    | 0.7 × IOVDD     | IC     | OVDD + 0.3      | V          |  |

| V <sub>IH</sub>    | High-level digital input logic voltage threshold                | All digital pins except FMT0, IOVDD 3.3-V operation                                                    | 2.1             | IC     | OVDD + 0.3      | V          |  |

|                    | Vollage unconoid                                                | FMT0 Pin                                                                                               | 2.1             |        | AVDD + 0.3      | V          |  |

| .,                 | Low-level digital output                                        | All digital pins, I <sub>OL</sub> = –2 mA, IOVDD 1.8-V operation                                       |                 |        | 0.45            | V          |  |

| V <sub>OL</sub>    | voltage                                                         | All digital pins, I <sub>OL</sub> = –2 mA, IOVDD 3.3-V operation                                       |                 |        | 0.4             | V          |  |

| V <sub>OH</sub>    | High-level digital output voltage                               | All digital pins, I <sub>OH</sub> = 2 mA, IOVDD 1.8-V operation                                        | IOVDD –<br>0.45 |        |                 | V          |  |

| VOH                |                                                                 | All digital pins, I <sub>OH</sub> = 2 mA, IOVDD 3.3-V operation                                        | 2.4             |        |                 |            |  |

| I <sub>IH</sub>    | Input logic-high leakage for digital inputs                     | All digital pins, input = IOVDD                                                                        | -5              | 0.1    | 5               | μA         |  |

| I <sub>IL</sub>    | Input logic-low leakage for digital inputs                      | All digital pins, input = 0 V                                                                          | -5              | 0.1    | 5               | μА         |  |

| C <sub>IN</sub>    | Input capacitance for digital inputs                            | All digital pins                                                                                       |                 | 5      |                 | pF         |  |

| R <sub>PD</sub>    | Pulldown resistance for digital I/O pins when asserted on       |                                                                                                        |                 | 20     |                 | kΩ         |  |

| TYPICAL S          | UPPLY CURRENT CONSUMP                                           | TION                                                                                                   |                 |        |                 |            |  |

| I <sub>AVDD</sub>  |                                                                 | AVDD = 3.3 V, internal AREG                                                                            |                 | 0.5    |                 | mA         |  |

| I <sub>IOVDD</sub> | Current consumption with all Clocks disabled                    | All external clocks stopped, IOVDD = 3.3 V                                                             |                 | 0.5    |                 |            |  |

| I <sub>IOVDD</sub> | all Clocks disabled                                             | All external clocks stopped, IOVDD = 1.8 V                                                             |                 | 0.3    |                 | μA         |  |

| I <sub>AVDD</sub>  | Current consumption with                                        | AVDD = 3.3 V, internal AREG                                                                            |                 | 11.9   |                 |            |  |

| I <sub>IOVDD</sub> | ADC 2-channel operating<br>at f <sub>S</sub> 16-kHz, BCLK = 256 | IOVDD = 3.3 V                                                                                          |                 | 0.05   |                 | mA         |  |

| I <sub>IOVDD</sub> | × f <sub>S</sub>                                                | IOVDD = 1.8 V                                                                                          |                 | 0.02   |                 |            |  |

| I <sub>AVDD</sub>  | Current consumption with                                        | AVDD = 3.3 V, internal AREG                                                                            |                 | 12.9   |                 |            |  |

| I <sub>IOVDD</sub> | ADC 2-channel operating<br>at f <sub>S</sub> 48-kHz, BCLK = 256 | IOVDD = 3.3 V                                                                                          |                 | 0.1    |                 | mA         |  |

| I <sub>IOVDD</sub> | × f <sub>S</sub>                                                | IOVDD = 1.8 V                                                                                          |                 | 0.05   |                 |            |  |

- (1) Ratio of output level with 1-kHz full-scale sine-wave input, to the output level with the AC signal input shorted to ground, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

- (2) All performance measurements done with a 20-kHz, low-pass filter and, where noted, an A-weighted filter. Failure to use such a filter may result in higher THD and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

- (3) For best distortion performance, use input AC-coupling capacitors with a low-voltage-coefficient.

- (4) Gain drift =gain\_variation(in temperature range)/ typical gain value(gain at room temperature) / temperature range × 10<sup>6</sup> measured with gain in linear scale.

- (5) Phase drift =phase deviation(in temperature range)/ (temperature range).

# 5.6 Timing Requirements: TDM, I<sup>2</sup>S or LJ Interface

at T<sub>A</sub> = 25°C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see for timing diagram

|                     |             | MIN | NOM MAX | UNIT |

|---------------------|-------------|-----|---------|------|

| t <sub>(BCLK)</sub> | BCLK period | 40  |         | ns   |

at T = 25°C IOVDD = 2.2 V at 1.9 V and 20 pF lead an all outputs (upless attack); and for timing diagram

|--|

|                              |                                                                             | MIN                                                                                                   | NOM                                                                                                                                                                                                                       | MAX                                                                                                                                                                                                                                   | UNIT                                                                                                                                                                                                                                 |

|------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK high pulse duration (1) |                                                                             | 25                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                   |

| BCLK low pulse duration (1)  |                                                                             | 25                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                   |

| FSYNC setup time             |                                                                             | 8                                                                                                     |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                   |

| FSYNC hold time              |                                                                             | 8                                                                                                     |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                   |

| BCLK rise time               | 10% - 90% rise time <sup>(2)</sup>                                          |                                                                                                       |                                                                                                                                                                                                                           | 10                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                   |

| BCLK fall time               | 90% - 10% fall time <sup>(2)</sup>                                          |                                                                                                       |                                                                                                                                                                                                                           | 10                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                   |

|                              | BCLK low pulse duration (1) FSYNC setup time FSYNC hold time BCLK rise time | BCLK low pulse duration (1)  FSYNC setup time  FSYNC hold time  BCLK rise time 10% - 90% rise time(2) | BCLK high pulse duration (1)         25           BCLK low pulse duration (1)         25           FSYNC setup time         8           FSYNC hold time         8           BCLK rise time         10% - 90% rise time(2) | BCLK high pulse duration (1)         25           BCLK low pulse duration (1)         25           FSYNC setup time         8           FSYNC hold time         8           BCLK rise time         10% - 90% rise time <sup>(2)</sup> | BCLK high pulse duration (1)         25           BCLK low pulse duration (1)         25           FSYNC setup time         8           FSYNC hold time         8           BCLK rise time         10% - 90% rise time(2)         10 |

<sup>(1)</sup> The BCLK minimum high or low pulse duration must be higher than 25 ns (to meet the timing specifications), if the SDOUT data line is latched on the opposite BCLK edge polarity than the edge used by the device to transmit SDOUT data.

# 5.7 Switching Characteristics: TDM, I<sup>2</sup>S or LJ Interface

at  $T_A = 25$ °C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see for timing diagram

|                             | PARAMETER                                                                | TEST CONDITIONS              | MIN | TYP MAX | UNIT |

|-----------------------------|--------------------------------------------------------------------------|------------------------------|-----|---------|------|

| t <sub>d(SDOUT-BCLK)</sub>  | BCLK to SDOUT delay                                                      | 50% of BCLK to 50% of SDOUT  | 3   | 18      | ns   |

| $t_{d(SDOUT\text{-}FSYNC)}$ | FSYNC to SDOUT delay in TDM or LJ mode (for MSB data with TX_OFFSET = 0) | 50% of FSYNC to 50% of SDOUT |     | 18      | ns   |

| f <sub>(BCLK)</sub>         | BCLK output clock frequency: controller mode (1)                         |                              |     | 24.576  | MHz  |

| t <sub>H(BCLK)</sub>        | BCLK high pulse duration: controller mode                                |                              | 14  |         | ns   |

| t <sub>L(BCLK)</sub>        | BCLK low pulse duration: controller mode                                 |                              | 14  |         | ns   |

| t <sub>d(FSYNC)</sub>       | BCLK to FSYNC delay: controller mode                                     | 50% of BCLK to 50% of FSYNC  | 3   | 18      | ns   |

| t <sub>r(BCLK)</sub>        | BCLK rise time: controller mode                                          | 10% - 90% rise time          |     | 8       | ns   |

| t <sub>f(BCLK)</sub>        | BCLK fall time: controller mode                                          | 90% - 10% fall time          |     | 8       | ns   |

<sup>(1)</sup> The BCLK output clock frequency must be lower than 18.5 MHz (to meet the timing specifications), if the SDOUT data line is latched on the opposite BCLK edge polarity than the edge used by the device to transmit SDOUT data.

<sup>(2)</sup> BCLK maximum rise and fall time can be relaxed to 13ns if BCLK frequency used in the system is below 20MHz. This can cause noise increase due to higher clock jitter.

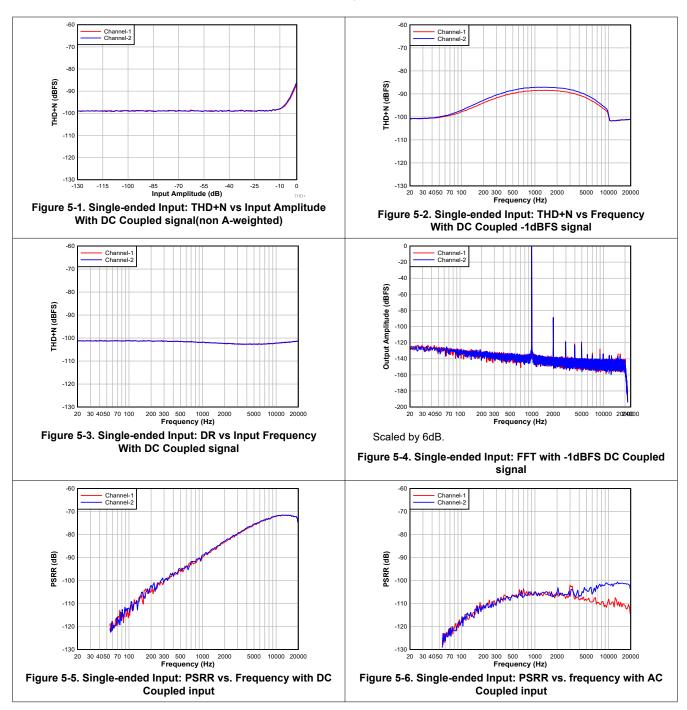

### 5.8 Typical Characteristics

at  $T_A$  = 25°C, AVDD = 3.3 V, IOVDD = 3.3 V,  $f_{IN}$  = 1-kHz sinusoidal signal,  $f_S$  = 48 kHz, 32-bit audio data, BCLK = 256 ×  $f_S$ , TDM target mode, PLL on, channel gain = 0 dB, and linear phase decimation filter (unless otherwise noted); all performance measurements are done with a 20-kHz, low-pass filter, an A-weighted filter and scaled to 0dBFS

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

# 6 Detailed Description

#### 6.1 Overview

The PCM1809 is a high-performance, low-power, stereo-channel, audio analog-to-digital converter (ADC) with flexible audio interface control options. This device is intended for applications in voice-activated systems, AV receivers, tv and blu-ray players, professional microphones, audio conferencing, portable computing, communication, and entertainment applications. The high dynamic range of the device enables far-field audio recording with high fidelity. This device integrates a host of features that reduces cost, board space, and power consumption in space-constrained applications. The device features are controlled through hardware by pulling pins high or low with resistors or a controller general-purpose inut/output (GPIO). The PCM1809 also supports a power-down and reset function by means of halting the system clock.

The PCM1809 consists of the following blocks and features:

- Stereo-channel, multibit, low-power delta-sigma (ΔΣ) ADC

- Differential audio inputs with a 2-V<sub>RMS</sub> full-scale signal

- Hardware pin control operation to select the device features

- · Audio bus serial interface controller or target select option

- Audio bus serial interface format select option

- · Target mode supports the audio bus serial interface up to 192 kHz sampling

- Target mode supports decimation filters with linear-phase or low-latency filter selection

- Controller mode operation supported using a system clock of 256 × f<sub>S</sub> or 512 × f<sub>S</sub>

- · Power-down function by means of halting the audio clocks

- Integrated high-pass filter (HPF) that removes the DC component of the input signal

- · Integrated low-jitter phase-locked loop (PLL) supporting a wide range of system clocks

- Integrated digital and analog voltage regulators to support single-supply, 3.3-V operation

# 6.2 Functional Block Diagram

### 6.3 Feature Description

#### 6.3.1 Hardware Control

The device supports simple hardware-pin-controlled options to select a specific mode of operation and audio interface for a given system. The MSZ, MD0, MD1, and FMT0 pins allow the device to be controlled by either pullup or pulldown resistors.

#### 6.3.2 Audio Serial Interfaces

Digital audio data flows between the host processor and the PCM1809 on the digital audio serial interface (ASI), or audio bus. This highly flexible ASI bus includes a TDM mode for multichannel operation, support for the I<sup>2</sup>S, and the pin-selectable controller-target configurability for bus clock lines.

The device supports an audio bus controller or target mode of operation using the hardware pin MSZ. In target mode, FSYNC and BCLK work as input pins whereas in controller mode, FSYNC and BCLK work as output pins generated by the device. Table 6-1 shows the controller and target mode selection using the MSZ pin.

Table 6-1. Controller and Target Mode Selection

| MSZ  | CONTROLLER AND TARGET SELECTION |  |  |

|------|---------------------------------|--|--|

| Low  | Target mode of operation        |  |  |

| High | Controller ode of operation     |  |  |

The bus protocol TDM or I<sup>2</sup>S format can be selected by using the FMT0 pin. As shown in Table 6-2, these modes are all most significant byte (MSB)-first, pulse code modulation (PCM) data format, with an output channel data word-length of 32 bits.

Table 6-2. Audio Serial Interface Format

| FMT0 | FMT0 AUDIO SERIAL INTERFACE FORMAT                           |  |

|------|--------------------------------------------------------------|--|

| Low  | 2-channel output with inter IC sound (I <sup>2</sup> S) mode |  |

| High | 2-channel output with time division multiplexing (TDM) mode  |  |

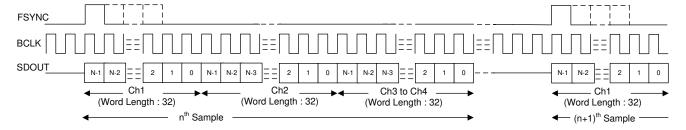

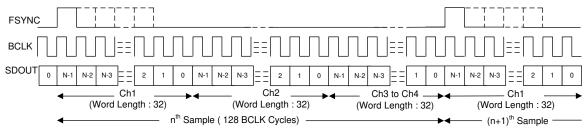

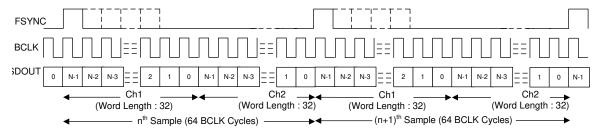

### 6.3.2.1 Time Division Multiplexed Audio (TDM) Interface

In TDM mode, also known as DSP mode, the rising edge of FSYNC starts the data transfer with the slot 0 data first. Immediately after the slot 0 data transmission, the remaining slot data are transmitted in order. FSYNC and each data bit (except the MSB of slot 0 when TX\_OFFSET equals 0) is transmitted on the rising edge of BCLK. Figure 6-1 to Figure 6-4 illustrate the protocol timing for TDM operation with various configurations.

Figure 6-1. TDM Mode Protocol Timing (FMT0 = LOW) In Target Mode

Figure 6-2. TDM Mode Protocol Timing (FMT0 = HIGH) In Target Mode

Figure 6-3. TDM Mode Protocol Timing (FMT0 = LOW) In Controller Mode

Figure 6-4. TDM Mode Protocol Timing (FMT0 = HIGH) In Controller Mode

For proper operation of the audio bus in TDM mode, the number of bit clocks per frame must be greater than or equal to the number of active output channels times the 32-bits word length of the output channel data. The device transmits a zero data value on SDOUT for the extra unused bit clock cycles. The device supports FSYNC as a pulse with a 1-cycle-wide bit clock, but also supports multiples as well.

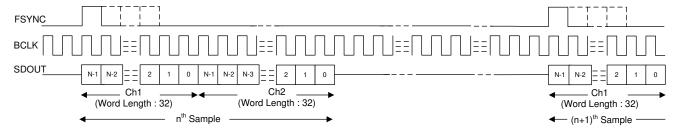

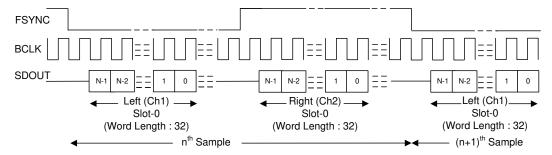

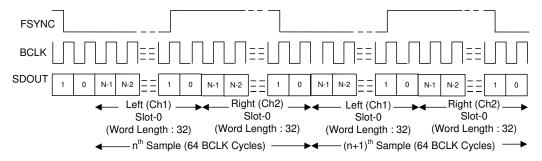

### 6.3.2.2 Inter IC Sound (I2S) Interface

The standard I<sup>2</sup>S protocol is defined for only two channels: left and right. In I<sup>2</sup>S mode, the MSB of the left slot 0 is transmitted on the falling edge of BCLK in the second cycle after the *falling* edge of FSYNC. The MSB of the right slot 0 is transmitted on the falling edge of BCLK in the second cycle after the *rising* edge of FSYNC. Each subsequent data bit is transmitted on the falling edge of BCLK. In controller mode, FSYNC is transmitted on the rising edge of BCLK. Figure 6-5 and Figure 6-6 show the protocol timing for I<sup>2</sup>S operation in target and controller mode of operation.

Figure 6-5. I<sup>2</sup>S Mode Protocol Timing in Target Mode

Figure 6-6. I<sup>2</sup>S Protocol Timing In Controller Mode

Copyright © 2024 Texas Instruments Incorporated

For proper operation of the audio bus in I<sup>2</sup>S mode, the number of bit clocks per frame must be greater than or equal to the number of active output channels (including left and right slots) times the 32-bits word length of the output channel data. The device FSYNC low pulse must be a number of BCLK cycles wide that is greater than or equal to the number of active left slots times the 32-bits data word length. Similarly, the FSYNC high pulse must be a number of BCLK cycles wide that is greater than or equal to the number of active right slots times the 32-bits data word length. The device transmit zero data value on SDOUT for the extra unused bit clock cycles.

### 6.3.3 Phase-Locked Loop (PLL) and Clock Generation

The device uses an integrated, low-jitter, phase-locked loop (PLL) to generate internal clocks required for the ADC modulator and digital filter engine, as well as other control blocks.

In target mode of operation, the device supports the various output data sample rates (of the FSYNC signal frequency) and the BCLK to FSYNC ratio to configure all clock dividers, including the PLL configuration, internally without host programming. Table 6-3 and Table 6-4 list the supported FSYNC and BCLK frequencies.

Table 6-3. Supported FSYNC (Multiples or Submultiples of 48kHz) and BCLK Frequencies

|                        | BCLK (MHz)      |                  |                  |                  |                  |                  |                   |

|------------------------|-----------------|------------------|------------------|------------------|------------------|------------------|-------------------|

| BCLK TO<br>FSYNC RATIO | FSYNC<br>(8kHz) | FSYNC<br>(16kHz) | FSYNC<br>(24kHz) | FSYNC<br>(32kHz) | FSYNC<br>(48kHz) | FSYNC<br>(96kHz) | FSYNC<br>(192kHz) |

| 16                     | Reserved        | 0.256            | 0.384            | 0.512            | 0.768            | 1.536            | 3.072             |

| 24                     | Reserved        | 0.384            | 0.576            | 0.768            | 1.152            | 2.304            | 4.608             |

| 32                     | 0.256           | 0.512            | 0.768            | 1.024            | 1.536            | 3.072            | 6.144             |

| 48                     | 0.384           | 0.768            | 1.152            | 1.536            | 2.304            | 4.608            | 9.216             |

| 64                     | 0.512           | 1.024            | 1.536            | 2.048            | 3.072            | 6.144            | 12.288            |

| 96                     | 0.768           | 1.536            | 2.304            | 3.072            | 4.608            | 9.216            | 18.432            |

| 128                    | 1.024           | 2.048            | 3.072            | 4.096            | 6.144            | 12.288           | 24.576            |

| 192                    | 1.536           | 3.072            | 4.608            | 6.144            | 9.216            | 18.432           | Reserved          |

| 256                    | 2.048           | 4.096            | 6.144            | 8.192            | 12.288           | 24.576           | Reserved          |

| 384                    | 3.072           | 6.144            | 9.216            | 12.288           | 18.432           | Reserved         | Reserved          |

| 512                    | 4.096           | 8.192            | 12.288           | 16.384           | 24.576           | Reserved         | Reserved          |

Table 6-4. Supported FSYNC (Multiples or Submultiples of 44.1kHz) and BCLK Frequencies

| Table                  | 0-4. Supported F3 INC (Multiples of Submultiples of 44. IND2) and BCLN Frequencies |                    |                     |                    |                    |                    |                     |

|------------------------|------------------------------------------------------------------------------------|--------------------|---------------------|--------------------|--------------------|--------------------|---------------------|

|                        | BCLK (MHz)                                                                         |                    |                     |                    |                    |                    |                     |

| BCLK TO<br>FSYNC RATIO | FSYNC<br>(7.35kHz)                                                                 | FSYNC<br>(14.7kHz) | FSYNC<br>(22.05kHz) | FSYNC<br>(29.4kHz) | FSYNC<br>(44.1kHz) | FSYNC<br>(88.2kHz) | FSYNC<br>(176.4kHz) |

| 16                     | Reserved                                                                           | Reserved           | 0.3528              | 0.4704             | 0.7056             | 1.4112             | 2.8224              |

| 24                     | Reserved                                                                           | 0.3528             | 0.5292              | 0.7056             | 1.0584             | 2.1168             | 4.2336              |

| 32                     | Reserved                                                                           | 0.4704             | 0.7056              | 0.9408             | 1.4112             | 2.8224             | 5.6448              |

| 48                     | 0.3528                                                                             | 0.7056             | 1.0584              | 1.4112             | 2.1168             | 4.2336             | 8.4672              |

| 64                     | 0.4704                                                                             | 0.9408             | 1.4112              | 1.8816             | 2.8224             | 5.6448             | 11.2896             |

| 96                     | 0.7056                                                                             | 1.4112             | 2.1168              | 2.8224             | 4.2336             | 8.4672             | 16.9344             |

| 128                    | 0.9408                                                                             | 1.8816             | 2.8224              | 3.7632             | 5.6448             | 11.2896            | 22.5792             |

| 192                    | 1.4112                                                                             | 2.8224             | 4.2336              | 5.6448             | 8.4672             | 16.9344            | Reserved            |

| 256                    | 1.8816                                                                             | 3.7632             | 5.6448              | 7.5264             | 11.2896            | 22.5792            | Reserved            |

| 384                    | 2.8224                                                                             | 5.6448             | 8.4672              | 11.2896            | 16.9344            | Reserved           | Reserved            |

| 512                    | 3.7632                                                                             | 7.5264             | 11.2896             | 15.0528            | 22.5792            | Reserved           | Reserved            |

In the controller mode of operation, the device uses the MD1 pin (as the system clock, MCLK) as the reference input clock source with a supported system clock frequency option of either 256  $\times$  f<sub>S</sub> or 512  $\times$  f<sub>S</sub> as configured using the MD0 pin. controller mode supports f<sub>S</sub> rates of 44.1kHz and 48kHz. Table 6-5 shows the system clock selection for the controller mode using the MD0 pin.

| Table 6-5. System Clock Selection for the Controller Mo | de |

|---------------------------------------------------------|----|

|---------------------------------------------------------|----|

| MD0                                                                                    | SYSTEM CLOCK SELECTION (Valid for Controller Mode Only) |  |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| LOW System clock with frequency 256 × f <sub>S</sub> connected to the MD1 pin as MCLK  |                                                         |  |  |  |

| HIGH System clock with frequency 512 × f <sub>S</sub> connected to the MD1 pin as MCLK |                                                         |  |  |  |

See Table 6-7 and for the MD0 and MD1 pin function in the target mode of operation.

### 6.3.4 Input Channel Configurations

The device consists of two pairs of analog input pins (INxP and INxM). These pins can be configured as differential or single-ended inputs for the recording channel. The device supports simultaneous recording of up to two channels using the high-performance stereo ADC. The input source for the analog pins can be from electret condenser analog microphones, micro electrical-mechanical system (MEMS) analog microphones, or line-in (auxiliary) inputs from the system board.

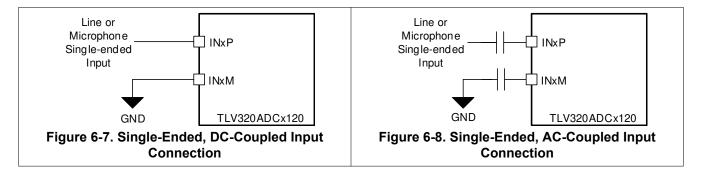

The voice or audio signal inputs can be capacitively coupled (AC-coupled) or DC-coupled to the device. For best distortion performance in AC-coupled mode, use the low-voltage coefficient capacitors. The typical input impedance for the PCM1809 is 10 k $\Omega$  for the INxP or INxM pins. The value of the coupling capacitor in AC-coupled mode must be chosen so that the high-pass filter formed by the coupling capacitor and the input impedance do not affect the signal content. Before proper recording can begin, this coupling capacitor must be charged up to the common-mode voltage at power-up. To enable quick charging, the device has a quick charge scheme to speed up the charging of the coupling capacitor at power-up. The value of the quick-charge timing is set for a coupling capacitor up to 1  $\mu$ F.

The INxM pin can be directly grounded in single-ended mode (see Figure 6-7 for DC-coupled) and (see Figure 6-8 for AC-coupled) for the single-ended input configuration. For the best dynamic range performance, the differential AC-coupled input must be used.

#### 6.3.5 Reference Voltage

All audio data converters require a DC reference voltage. The PCM1809 achieves low-noise performance by internally generating a low-noise reference voltage. This reference voltage is generated using a band-gap circuit with high PSRR performance. This audio converter reference voltage must be filtered externally using a minimum 1- $\mu$ F capacitor connected from the VREF pin to analog ground (AVSS). The value of this reference voltage, VREF, is set to 2.75 V, which in turn supports a 2- $V_{RMS}$  differential full-scale input to the device. The required minimum AVDD voltage for this VREF voltage is 3 V. Do not connect any external load to a VREF pin.

#### 6.3.6 Signal-Chain Processing

The PCM1809 signal chain is comprised of very-low-noise, and low-power analog blocks and highly flexible and configurable digital processing blocks. The high performance and flexibility combined with a compact package makes the PCM1809 optimized for a variety of end-equipments and applications that require multichannel audio capture. Figure 6-9 shows a conceptual block diagram for the PCM1809 that highlights the various building blocks used in the signal chain, and how the blocks interact in the signal chain.

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

Figure 6-9. Signal-Chain Processing Flowchart

Configurable high-performance multistage digital decimation filter sharply cuts off any out-of-band frequency noise with high stop-band attenuation.

#### 6.3.6.1 Digital High-Pass Filter

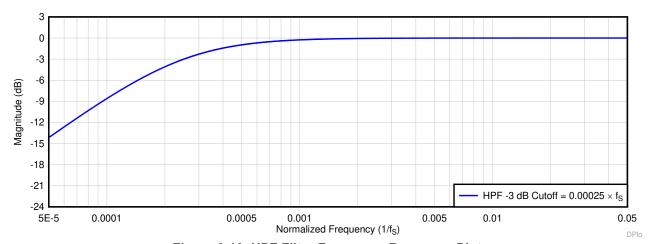

To remove the DC offset component and attenuate the undesired low-frequency noise content in the record data, the device supports a fixed high-pass filter (HPF) with -3-dB cut-off frequency of  $0.00025 \times f_S$ . The HPF is not a channel-independent filter but is globally applicable for all the ADC channels. This HPF is constructed using the first-order infinite impulse response (IIR) filter, and is efficient enough to filter out possible DC components of the signal. Table 6-6 shows the fixed -3-dB cutoff frequency value. Figure 6-10 shows a frequency response plot for the HPF filter.

Table 6-6. HPF Cutoff Frequency Value

| -3-dB CUTOFF FREQUENCY VALUE | -3-dB CUTTOFF FREQUENCY AT 16 kHz<br>SAMPLE RATE | -3-dB CUTTOFF FREQUENCY AT 48 kHz<br>SAMPLE RATE |

|------------------------------|--------------------------------------------------|--------------------------------------------------|

| 0.00025 × f <sub>S</sub>     | 4 Hz                                             | 12 Hz                                            |

Figure 6-10. HPF Filter Frequency Response Plot

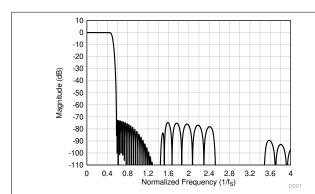

### 6.3.6.2 Configurable Digital Decimation Filters

The device record channel includes a high dynamic range, built-in digital decimation filter to process the oversampled data from the multibit delta-sigma ( $\Delta\Sigma$ ) modulator to generate digital data at the same Nyquist sampling rate as the FSYNC rate. The decimation filter can be chosen from two different types only in target mode, depending on the required frequency response, group delay, and phase linearity requirements for the target application. The selection of the decimation filter option can be done by the MD0 pin. Table 6-7 shows the decimation filter mode selection for the record channel.

Table 6-7. Decimation Filter Mode Selection for the Record Channel

| MD0 | DECIMATION FILTER MODE SELECTION (Supported Only in Target Mode)                                                                                     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Linear phase filters are used for the decimation in target mode. For controller mode, the device always use linear phase filters for the decimation. |

|     | Low latency filters are used for the decimation in target mode. For controller mode, the device always use linear phase filters for the decimation.  |

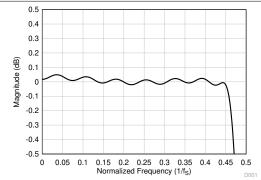

#### 6.3.6.2.1 Linear Phase Filters

The linear phase decimation filters are the default filters set by the device and can be used for all applications that require a perfect linear phase with zero-phase deviation within the pass-band specification of the filter. The filter performance specifications and various plots for all supported output sampling rates are listed in this section.

### 6.3.6.2.1.1 Sampling Rate: 8 kHz or 7.35 kHz

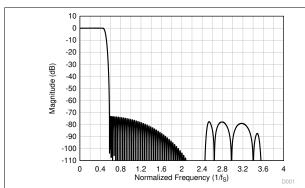

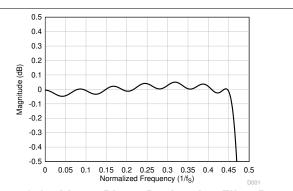

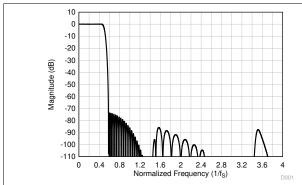

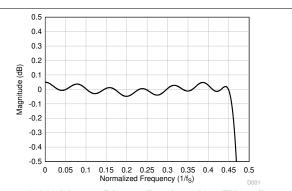

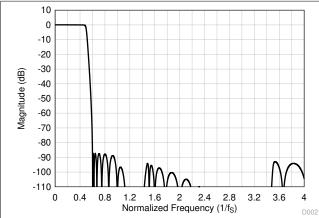

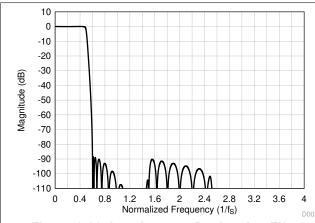

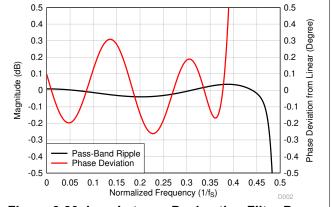

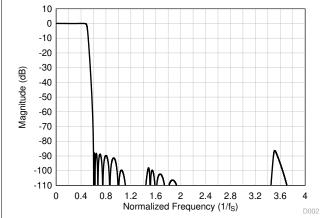

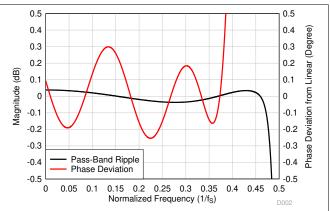

Figure 6-11 and Figure 6-12 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 8 kHz or 7.35 kHz. Table 6-8 lists the specifications for a decimation filter with an

8-kHz or 7.35-kHz sampling rate.

Copyright © 2024 Texas Instruments Incorporated

Figure 6-11. Linear Phase Decimation Filter

Magnitude Response

Figure 6-12. Linear Phase Decimation Filter Pass-Band Ripple

Table 6-8. Linear Phase Decimation Filter Specifications

| PARAMETER              | TEST CONDITIONS                                                | MIN   | TYP  | MAX  | UNIT             |

|------------------------|----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.454 × f <sub>S</sub>                 | -0.05 |      | 0.05 | dB               |

| Otan hand attancestion | Frequency range is 0.58 × f <sub>S</sub> to 4 × f <sub>S</sub> | 72.7  |      |      | dB               |

| Stop-band attenuation  | Frequency range is 4 × f <sub>S</sub> onwards                  | 81.2  |      |      | uБ               |

| Group delay or latency | Frequency range is 0 to 0.454 × f <sub>S</sub>                 |       | 17.1 |      | 1/f <sub>S</sub> |

### 6.3.6.2.1.2 Sampling Rate: 16 kHz or 14.7 kHz

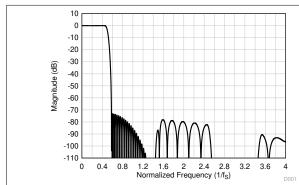

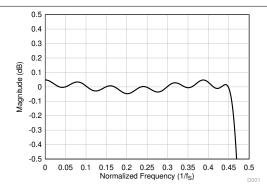

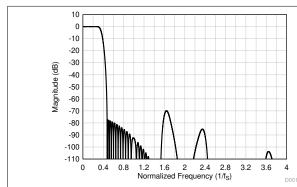

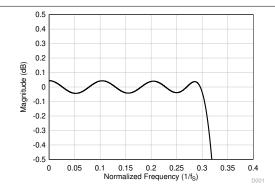

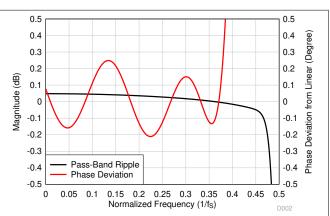

Figure 6-13 and Figure 6-14 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 16 kHz or 14.7 kHz. Table 6-9 lists the specifications for a decimation filter with an 16-kHz or 14.7-kHz sampling rate.

Figure 6-13. Linear Phase Decimation Filter Magnitude Response

Figure 6-14. Linear Phase Decimation Filter Pass-Band Ripple

**Table 6-9. Linear Phase Decimation Filter Specifications**

| PARAMETER              | TEST CONDITIONS                                                | MIN   | TYP  | MAX  | UNIT             |

|------------------------|----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.454 × f <sub>S</sub>                 | -0.05 |      | 0.05 | dB               |

| Stop-band attenuation  | Frequency range is 0.58 × f <sub>S</sub> to 4 × f <sub>S</sub> | 73.3  |      |      | dB               |

| Stop-parid attenuation | Frequency range is 4 × f <sub>S</sub> onwards                  | 95.0  |      |      |                  |

| Group delay or latency | Frequency range is 0 to 0.454 × f <sub>S</sub>                 |       | 15.7 |      | 1/f <sub>S</sub> |

#### 6.3.6.2.1.3 Sampling Rate: 24 kHz or 22.05 kHz

Figure 6-15 and Figure 6-16 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 24 kHz or 22.05 kHz. Table 6-10 lists the specifications for a decimation filter with an 24-kHz or 22.05-kHz sampling rate.

Figure 6-15. Linear Phase Decimation Filter

Magnitude Response

Figure 6-16. Linear Phase Decimation Filter Pass-Band Ripple

Table 6-10. Linear Phase Decimation Filter Specifications

| PARAMETER               | TEST CONDITIONS                                                | MIN   | TYP  | MAX  | UNIT             |

|-------------------------|----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple        | Frequency range is 0 to 0.454 × f <sub>S</sub>                 | -0.05 |      | 0.05 | dB               |

| Stop-band attenuation   | Frequency range is 0.58 × f <sub>S</sub> to 4 × f <sub>S</sub> | 73.0  |      |      |                  |

| Stop-barid atteridation | Frequency range is 4 × f <sub>S</sub> onwards                  | 96.4  |      |      | dB               |

| Group delay or latency  | Frequency range is 0 to 0.454 × f <sub>S</sub>                 |       | 16.6 |      | 1/f <sub>S</sub> |

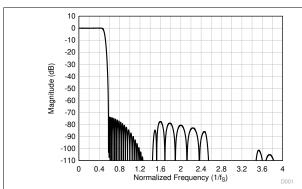

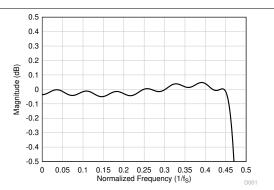

#### 6.3.6.2.1.4 Sampling Rate: 32 kHz or 29.4 kHz

Figure 6-17 and Figure 6-18 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 32 kHz or 29.4 kHz. Table 6-11 lists the specifications for a decimation filter with an 32-kHz or 29.4-kHz sampling rate.

Figure 6-17. Linear Phase Decimation Filter Magnitude Response

Figure 6-18. Linear Phase Decimation Filter Pass-Band Ripple

**Table 6-11. Linear Phase Decimation Filter Specifications**

| PARAMETER              | TEST CONDITIONS                                                | MIN   | TYP  | MAX  | UNIT             |

|------------------------|----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.454 × f <sub>S</sub>                 | -0.05 |      | 0.05 | dB               |

| Ctan hand attanuation  | Frequency range is 0.58 × f <sub>S</sub> to 4 × f <sub>S</sub> | 73.7  |      |      | JD.              |

| Stop-band attenuation  | Frequency range is 4 × f <sub>S</sub> onwards                  | 107.2 |      |      | dB               |

| Group delay or latency | Frequency range is 0 to 0.454 × f <sub>S</sub>                 |       | 16.9 |      | 1/f <sub>S</sub> |

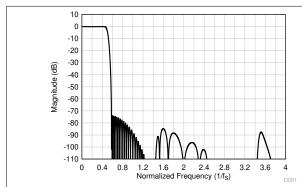

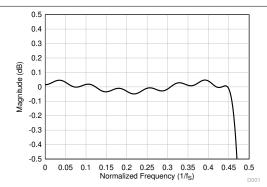

#### 6.3.6.2.1.5 Sampling Rate: 48 kHz or 44.1 kHz

Figure 6-19 and Figure 6-20 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 48 kHz or 44.1 kHz. Table 6-12 lists the specifications for a decimation filter with an 48-kHz or 44.1-kHz sampling rate.

Figure 6-19. Linear Phase Decimation Filter

Magnitude Response

Figure 6-20. Linear Phase Decimation Filter Pass-Band Ripple

Table 6-12. Linear Phase Decimation Filter Specifications

| PARAMETER              | TEST CONDITIONS                                                | MIN   | TYP  | MAX  | UNIT             |

|------------------------|----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.454 × f <sub>S</sub>                 | -0.05 |      | 0.05 | dB               |

| Stop-band attenuation  | Frequency range is 0.58 × f <sub>S</sub> to 4 × f <sub>S</sub> | 73.8  |      |      | dB               |

| Stop-parid attenuation | Frequency range is 4 × f <sub>S</sub> onwards                  | 98.1  |      |      | ив               |

| Group delay or latency | Frequency range is 0 to 0.454 × f <sub>S</sub>                 |       | 17.1 |      | 1/f <sub>S</sub> |

#### 6.3.6.2.1.6 Sampling Rate: 96 kHz or 88.2 kHz

Figure 6-21 and Figure 6-22 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 96 kHz or 88.2 kHz. Table 6-13 lists the specifications for a decimation filter with an 96-kHz or 88.2-kHz sampling rate.

Figure 6-21. Linear Phase Decimation Filter Magnitude Response

Figure 6-22. Linear Phase Decimation Filter Pass-**Band Ripple**

**Table 6-13. Linear Phase Decimation Filter Specifications**

| PARAMETER              | TEST CONDITIONS                                                | MIN   | TYP  | MAX  | UNIT             |

|------------------------|----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.454 × f <sub>S</sub>                 | -0.05 |      | 0.05 | dB               |

| Stan hand attenuation  | Frequency range is 0.58 × f <sub>S</sub> to 4 × f <sub>S</sub> | 73.6  |      |      | .ID              |

| Stop-band attenuation  | Frequency range is 4 × f <sub>S</sub> onwards                  | 97.9  |      |      | dB               |

| Group delay or latency | Frequency range is 0 to 0.454 × f <sub>S</sub>                 |       | 17.1 |      | 1/f <sub>S</sub> |

#### 6.3.6.2.1.7 Sampling Rate: 192 kHz or 176.4 kHz

Figure 6-23 and Figure 6-24 respectively show the magnitude response and the pass-band ripple for a decimation filter with a sampling rate of 192 kHz or 176.4 kHz. Table 6-14 lists the specifications for a decimation filter with an 192-kHz or 176.4-kHz sampling rate.

Figure 6-23. Linear Phase Decimation Filter Magnitude Response

Figure 6-24. Linear Phase Decimation Filter Pass-**Band Ripple**

**Table 6-14. Linear Phase Decimation Filter Specifications**

| PARAMETER              | TEST CONDITIONS                                                 | MIN   | TYP  | MAX  | UNIT             |

|------------------------|-----------------------------------------------------------------|-------|------|------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.3 × f <sub>S</sub>                    | -0.05 |      | 0.05 | dB               |

| Stop-band attenuation  | Frequency range is 0.473 × f <sub>S</sub> to 4 × f <sub>S</sub> | 70.0  |      |      | 40               |

| Stop-parid attenuation | Frequency range is 4 × f <sub>S</sub> onwards                   | 111.0 |      |      | dB               |

| Group delay or latency | Frequency range is 0 to 0.3 × f <sub>S</sub>                    |       | 11.9 |      | 1/f <sub>S</sub> |

### 6.3.6.2.2 Low-Latency Filters

For applications where low latency with minimal phase deviation (within the audio band) is critical, the low-latency decimation filters on the PCM1809 can be used. The device supports these filters with a group delay of approximately seven samples with an almost linear phase response within the  $0.365 \times f_S$  frequency band. This section provides the filter performance specifications and various plots for all supported output sampling rates for the low-latency filters.

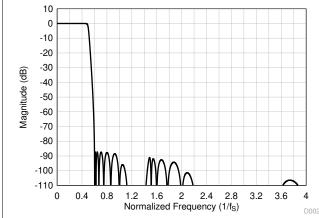

### 6.3.6.2.2.1 Sampling Rate: 16 kHz or 14.7 kHz

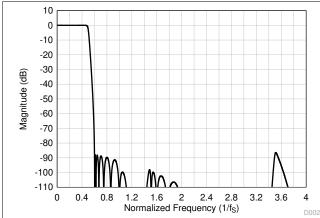

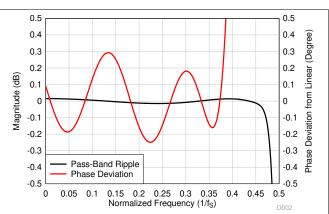

Figure 6-25 shows the magnitude response and Figure 6-26 shows the pass-band ripple and phase deviation for a decimation filter with a sampling rate of 16 kHz or 14.7 kHz. Table 6-15 lists the specifications for a decimation filter with a 16-kHz or 14.7-kHz sampling rate.

Figure 6-25. Low-Latency Decimation Filter

Magnitude Response

Figure 6-26. Low-Latency Decimation Filter Pass-Band Ripple and Phase Deviation

Table 6-15. Low-Latency Decimation Filter Specifications

| PARAMETER              | TEST CONDITIONS                                  | MIN    | TYP | MAX   | UNIT             |

|------------------------|--------------------------------------------------|--------|-----|-------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.451 × f <sub>S</sub>   | -0.05  |     | 0.05  | dB               |

| Stop-band attenuation  | Frequency range is 0.61 × f <sub>S</sub> onwards | 87.3   |     |       | dB               |

| Group delay or latency | Frequency range is 0 to 0.363 × f <sub>S</sub>   |        | 7.6 |       | 1/f <sub>S</sub> |

| Group delay deviation  | Frequency range is 0 to 0.363 × f <sub>S</sub>   | -0.022 |     | 0.022 | 1/f <sub>S</sub> |

| Phase deviation        | Frequency range is 0 to 0.363 × f <sub>S</sub>   | -0.21  |     | 0.25  | Degrees          |

### 6.3.6.2.2.2 Sampling Rate: 24 kHz or 22.05 kHz

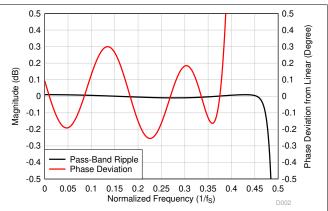

Figure 6-27 shows the magnitude response and Figure 6-28 shows the pass-band ripple and phase deviation for a decimation filter with a sampling rate of 24 kHz or 22.05 kHz. Table 6-16 lists the specifications for a decimation filter with a 24-kHz or 22.05-kHz sampling rate.

Normalized Frequency (1/fs)

Figure 6-27. Low-Latency Decimation Filter

Magnitude Response

Figure 6-28. Low-Latency Decimation Filter Pass-Band Ripple and Phase Deviation

Table 6-16. Low-Latency Decimation Filter Specifications

| PARAMETER              | TEST CONDITIONS                                 | MIN    | TYP | MAX   | UNIT             |

|------------------------|-------------------------------------------------|--------|-----|-------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.459 × f <sub>S</sub>  | -0.01  |     | 0.01  | dB               |

| Stop-band attenuation  | Frequency range is 0.6 × f <sub>S</sub> onwards | 87.2   |     |       | dB               |

| Group delay or latency | Frequency range is 0 to 0.365 × f <sub>S</sub>  |        | 7.5 |       | 1/f <sub>S</sub> |

| Group delay deviation  | Frequency range is 0 to 0.365 × f <sub>S</sub>  | -0.026 |     | 0.026 | 1/f <sub>S</sub> |

| Phase deviation        | Frequency range is 0 to 0.365 × f <sub>S</sub>  | -0.26  |     | 0.30  | Degrees          |

### 6.3.6.2.2.3 Sampling Rate: 32 kHz or 29.4 kHz

Figure 6-29 shows the magnitude response and Figure 6-30 shows the pass-band ripple and phase deviation for a decimation filter with a sampling rate of 32 kHz or 29.4 kHz. Table 6-17 lists the specifications for a decimation filter with a 32-kHz or 29.4-kHz sampling rate.

Figure 6-29. Low-Latency Decimation Filter

Magnitude Response

Figure 6-30. Low-Latency Decimation Filter Pass-Band Ripple and Phase Deviation

Table 6-17. Low-Latency Decimation Filter Specifications

| PARAMETER              | TEST CONDITIONS                                 | MIN    | TYP | MAX   | UNIT             |

|------------------------|-------------------------------------------------|--------|-----|-------|------------------|

| Pass-band ripple       | Frequency range is 0 to 0.457 × f <sub>S</sub>  | -0.04  |     | 0.04  | dB               |

| Stop-band attenuation  | Frequency range is 0.6 × f <sub>S</sub> onwards | 88.3   |     |       | dB               |

| Group delay or latency | Frequency range is 0 to 0.368 × f <sub>S</sub>  |        | 8.7 |       | 1/f <sub>S</sub> |

| Group delay deviation  | Frequency range is 0 to 0.368 × f <sub>S</sub>  | -0.026 |     | 0.026 | 1/f <sub>S</sub> |

| Phase deviation        | Frequency range is 0 to 0.368 × f <sub>S</sub>  | -0.26  |     | 0.31  | Degrees          |

#### 6.3.6.2.2.4 Sampling Rate: 48 kHz or 44.1 kHz

Figure 6-31 shows the magnitude response and Figure 6-32 shows the pass-band ripple and phase deviation for a decimation filter with a sampling rate of 48 kHz or 44.1 kHz. Table 6-18 lists the specifications for a decimation filter with a 48-kHz or 44.1-kHz sampling rate.

Figure 6-31. Low-Latency Decimation Filter Magnitude Response

Figure 6-32. Low-Latency Decimation Filter Pass-Band Ripple and Phase Deviation

**Table 6-18. Low-Latency Decimation Filter Specifications**

| PARAMETER              | TEST CONDITIONS                                 | MIN    | TYP | MAX   | UNIT             |