TPS2231 TPS2236

www.ti.com

#### SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

ExpressCard<sup>™</sup> POWER INTERFACE SWITCH

Check for Samples: TPS2231 TPS2236

### FEATURES

- Meets the ExpressCard<sup>™</sup> Standard (ExpressCard|34 or ExpressCard|54)

- Compliant with the ExpressCard™ Compliance Checklists

- Fully Satisfies the ExpressCard™ Implementation Guidelines

- Supports Systems with WAKE Function

- TTL-Logic Compatible Inputs

- Short Circuit and Thermal Protection

- -40°C to 85°C Ambient Operating Temperature Range

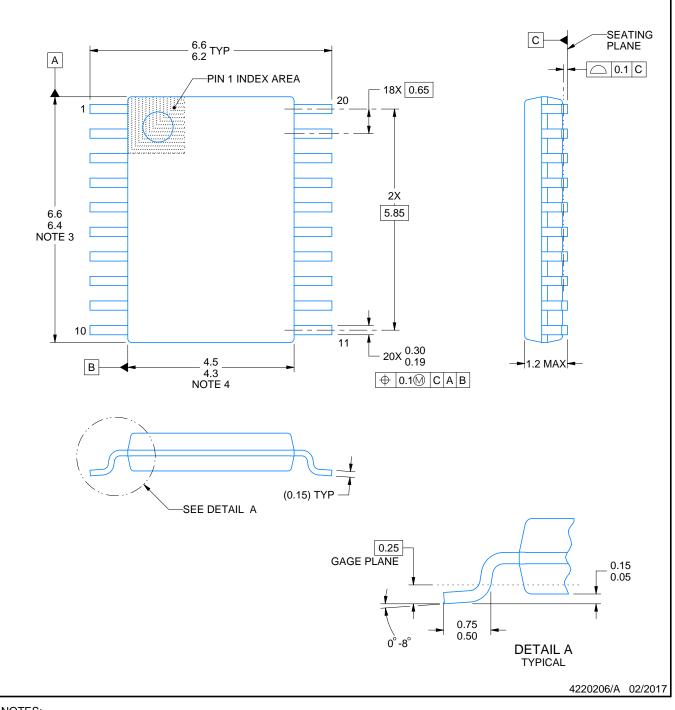

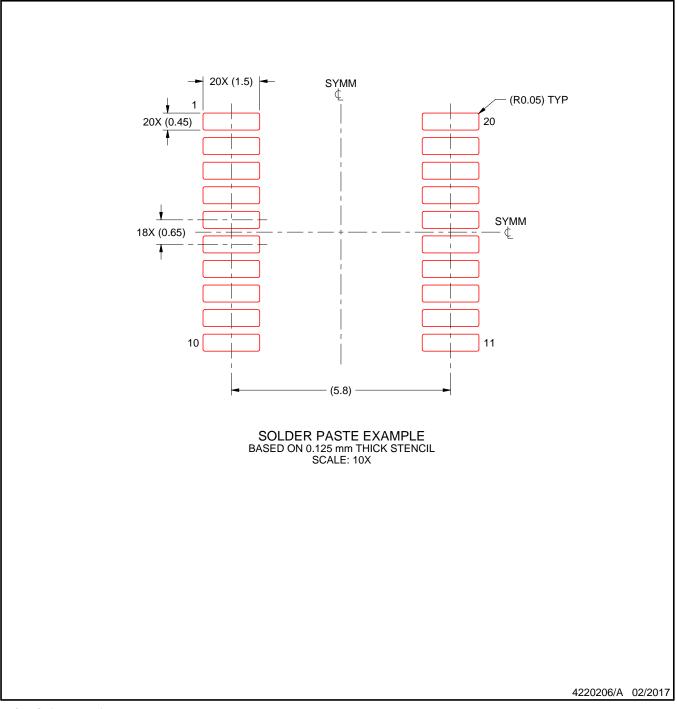

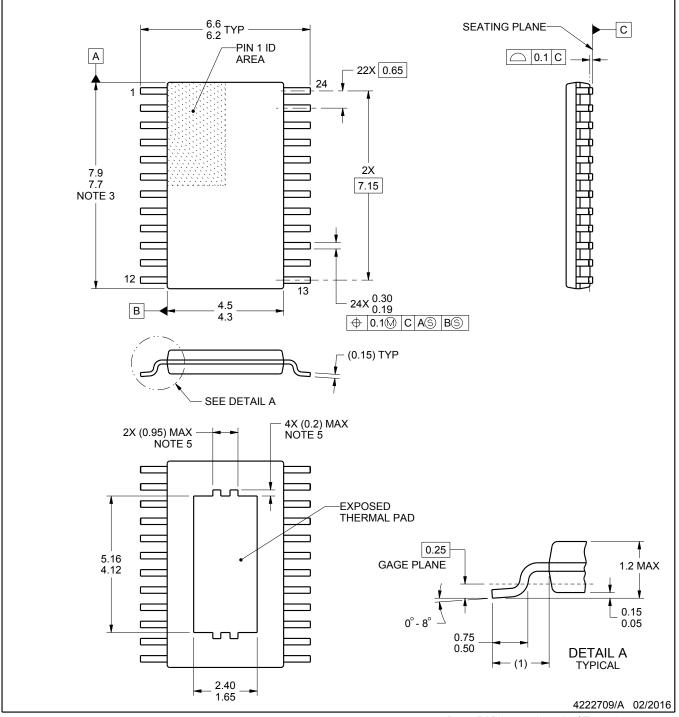

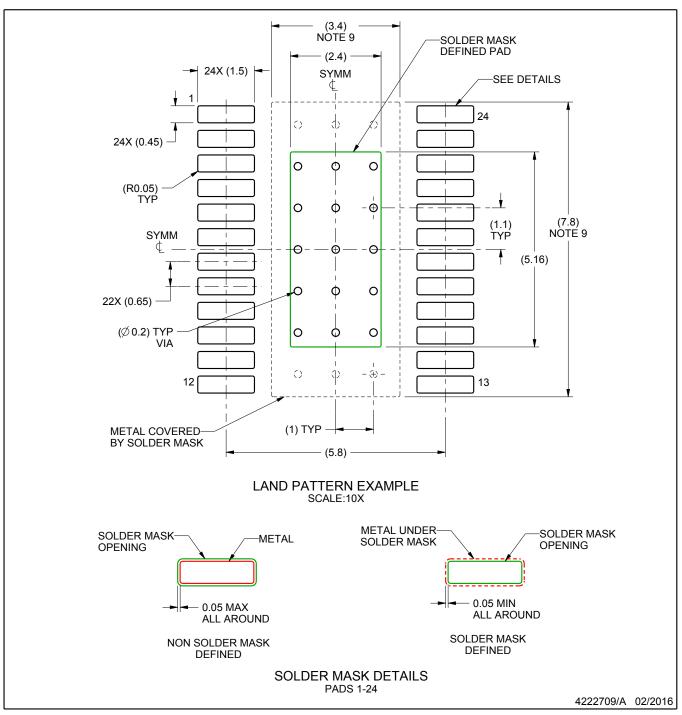

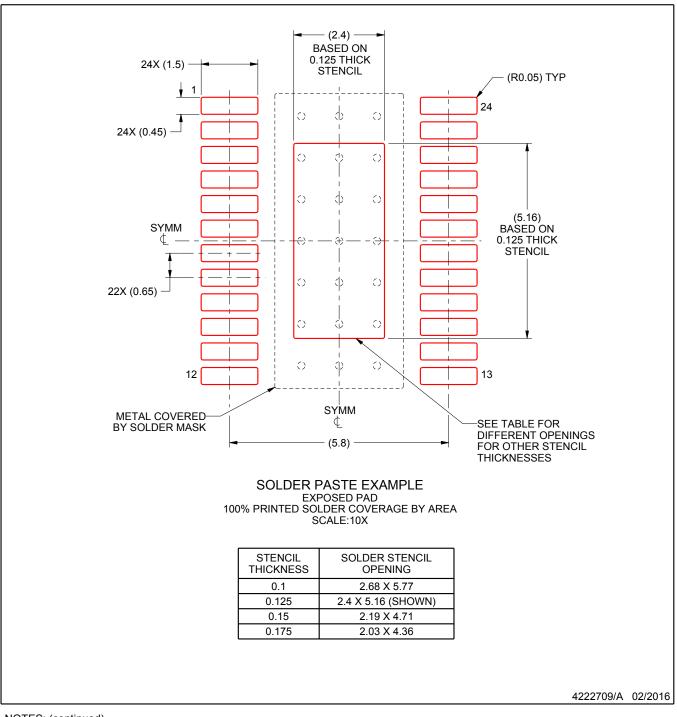

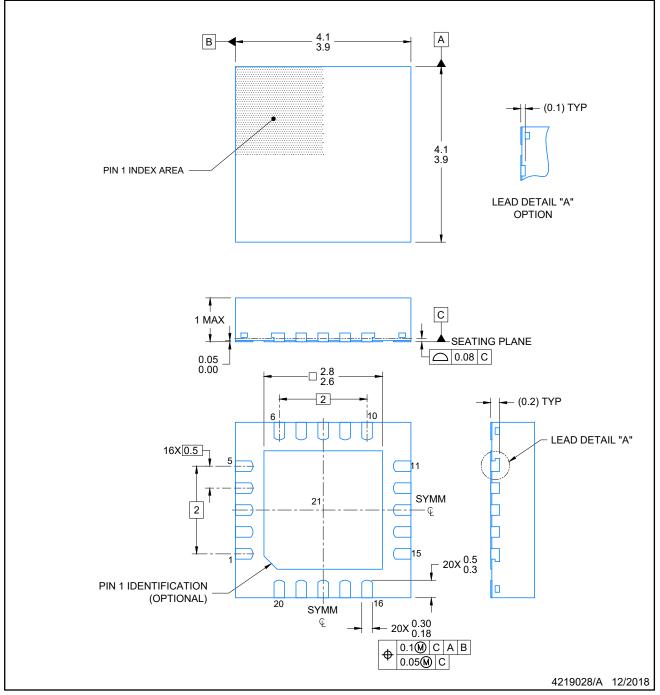

- Available in a 20-pin TSSOP, a 20-pin QFN, or 24-pin PowerPAD<sup>™</sup> HTSSOP (Single)

- Available in a 32-pin PowerPAD<sup>™</sup> HTSSOP (Dual)

#### **APPLICATIONS**

- Notebook Computers

- Desktop Computers

- Personal Digital Assistants (PDAs)

- Digital Cameras

- TV and Set Top Boxes

### DESCRIPTION

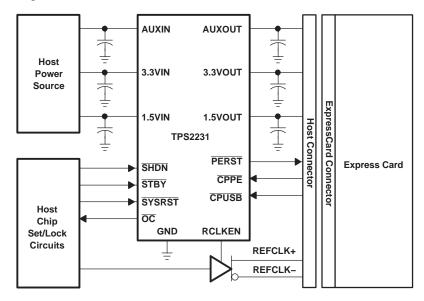

The TPS2231 and TPS2236 ExpressCard power interface switches provide the total power management solution required by the ExpressCard specification. The TPS2231 and TPS2236 ExpressCard power interface switches distribute 3.3 V, AUX, and 1.5 V to the ExpressCard socket. Each voltage rail is protected with integrated current-limiting circuitry.

The TPS2231 supports systems with single-slot ExpressCard|34 or ExpressCard|54 sockets. The TPS2236 supports systems with dual-slot ExpressCard sockets.

End equipment for the TPS2231 and TPS2236 include notebook computers, desktop computers, personal digital assistants (PDAs), and digital cameras.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

ExpressCard is a trademark of Personal Computer Memory Card International Association.

### TPS2231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| <b>–</b>       |                    | PACKAGED DEVICES <sup>(1)</sup> <sup>(2)</sup> |                 |                              |  |  |  |

|----------------|--------------------|------------------------------------------------|-----------------|------------------------------|--|--|--|

| T <sub>A</sub> | NUMBER OF CHANNELS | TSSOP                                          | PowerPAD HTSSOP | QFN                          |  |  |  |

|                |                    | TPS2231PW                                      | TPS2231PWP      | TPS2231RGP                   |  |  |  |

|                | Single             |                                                |                 | TPS2231MRGP <sup>(3)</sup>   |  |  |  |

| –40°C to 85°C  |                    |                                                |                 | TPS2231MRGP-1 <sup>(4)</sup> |  |  |  |

|                |                    |                                                |                 | TPS2231MRGP-2 <sup>(5)</sup> |  |  |  |

|                |                    |                                                |                 | TPS2231MRGP-3 <sup>(6)</sup> |  |  |  |

|                | Dual               |                                                | TPS2236DAP      |                              |  |  |  |

#### AVAILABLE OPTIONS

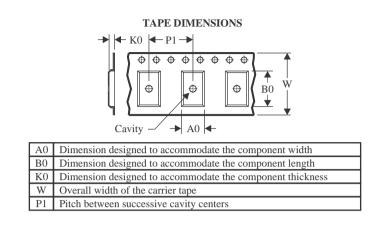

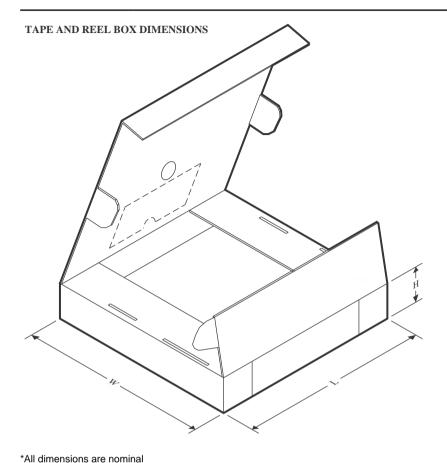

(1) The package is available taped and reeled. Add an R suffix to device types (e.g., TPS2231PWPR).

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

(4) The TPS2231MRGP-1 is identical to the TPS2231MGRP with the exception that the orientation of the part in the reel is rotated 180°. See the Package Materials Information portion of this data sheet for specific information.

(5) The TPS2231MRGP-2 is identical to the TPS2231MRGP with the exception that the orientation of the part in the reel is rotated 90° and does not have an internal pull-up resistor between AUX IN and SYSRST. See the Package Materials Information portion of this data sheet for specific information.

(6) The TPS2231MRGP-3 is identical to the TPS2231MRGP with the exception that the 1.5VIN and 3.3VIN UVLO circuits are independent.

### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                       |                                        |                                            | TPS223x            | UNIT |  |

|------------------|---------------------------------------|----------------------------------------|--------------------------------------------|--------------------|------|--|

|                  |                                       | V <sub>I(3.3VIN)</sub>                 |                                            | -0.3 to 6          | V    |  |

| VI               | Input voltage range for card<br>power | V <sub>I(1.5VIN)</sub>                 |                                            | -0.3 to 6          | V    |  |

|                  | ponol                                 | V <sub>I(AUXIN)</sub>                  |                                            | -0.3 to 6          | V    |  |

|                  | Logic input/output voltage            |                                        |                                            | -0.3 to 6          | V    |  |

|                  |                                       | V <sub>O(3.3VOUT)</sub>                |                                            | -0.3 to 6          | V    |  |

| Vo               | Output voltage range                  | V <sub>O(1.5VOUT)</sub>                |                                            | -0.3 to 6          | V    |  |

|                  |                                       | V <sub>O(AUXOUT)</sub>                 |                                            | -0.3 to 6          | V    |  |

|                  | Continuous total power dissipat       |                                        | See Dissipation Rating                     | J Table            |      |  |

|                  |                                       | I <sub>O(3.3VOUT)</sub>                |                                            | Internally limited |      |  |

| lo               | Output current                        | I <sub>O(AUXOUT)</sub>                 |                                            | Internally limited |      |  |

|                  |                                       | I <sub>O(1.5VOUT)</sub>                |                                            | Internally limited |      |  |

|                  | OC sink current                       |                                        |                                            | 10                 | mA   |  |

|                  | PERST sink/source current             |                                        |                                            | 10                 | mA   |  |

| TJ               | Operating virtual junction tempe      | erature range                          |                                            | -40 to 120         | °C   |  |

| T <sub>stg</sub> | Storage temperature range             |                                        |                                            | -55 to 150         | °C   |  |

|                  | Lead temperature 1,6 mm (1/16         | 6 inch) from case for 10 sec           | conds                                      | 260                | °C   |  |

|                  |                                       |                                        | TPS2231                                    |                    |      |  |

| ESD              | Electrostatic discharge               | Human body model<br>(HBM) MIL-STD-883C | TPS2236, all pins except<br>PERSTx and OCx | 2                  | kV   |  |

|                  | protection                            |                                        | TPS2236, PERSTx and OCx                    | 1.5                | kV   |  |

|                  |                                       | Charge device model (C                 | CDM)                                       | 500                | V    |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

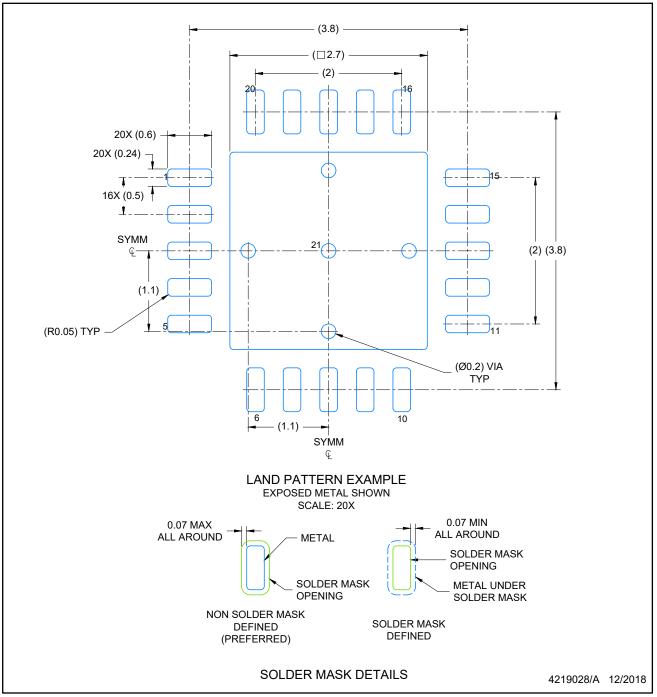

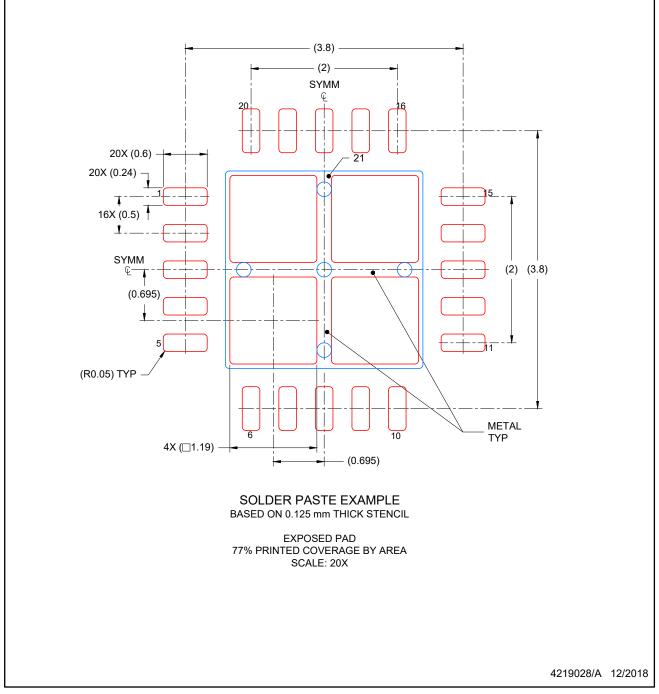

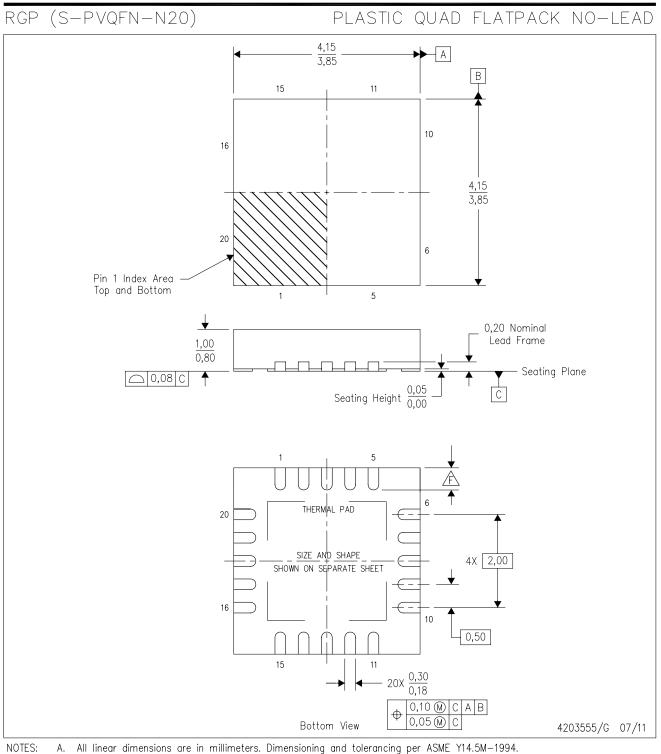

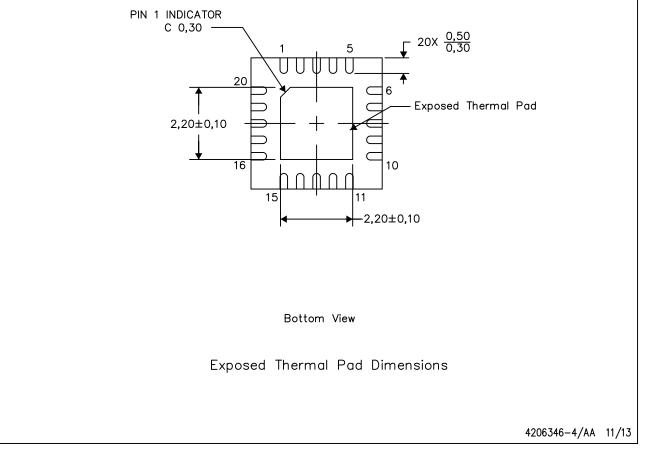

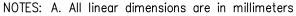

<sup>(3)</sup> The TPS2231MRGP is identical to the TPS2231 with the exception of the PowerPAD dimensions. See the Thermal Pad Mechanical data portion of this data sheet for specific information. The thermal pad for the TPS2231MRGP and TPS2231MRGP-1 is 2,2 mm x 2,2 mm; the thermal pad for the TPS2231RGP is 2,7 mm x 2,7 mm.

#### **DISSIPATION RATINGS (Thermal Resistance = °C/W)**

| PACKAGE                                               | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|-------------------------------------------------------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| PW (20) <sup>(1)</sup>                                | 704.2 mW                              | 7.41 mW/°C                                     | 370.6 mW                              | 259.5 mW                              |

| PWP (24) <sup>(1)</sup>                               | 3153 mW                               | 33.19 mW/°C                                    | 1659.5 mW                             | 1161.6 mW                             |

| RGP (20) <sup>(2)</sup>                               | 3277.5 mW                             | 34.5 mW/°C                                     | 1725 mW                               | 1207.3 mW                             |

| DAP (32) <sup>(1)</sup><br>PowerPAD not soldered down | 993.4 mW                              | 10.46 mW/°C                                    | 522.8 mW                              | 366 mW                                |

| DAP (32) <sup>(1)</sup>                               | 4040.8 mW                             | 42.55 mW/°C                                    | 2126.8 mW                             | 1488.7 mW                             |

(1) These devices are mounted on an JEDEC low-k board (2-oz. traces on surface), (The table is assuming that the maximum junction temperature is 120°C). The power pad on the device must be soldered down to the power pad on the board if best thermal performance is needed.

(2) This device is mounted on a JEDEC JESO51.5 high-k board (2 signal, 2 plane). The values assume a maximum junction temperature of 120°C.

#### **RECOMMENDED OPERATING CONDITIONS**

|                         |                                 |                                                      | MIN  | MAX  | UNIT |

|-------------------------|---------------------------------|------------------------------------------------------|------|------|------|

| V <sub>I(3.3VIN)</sub>  |                                 | 3.3VIN is only required for its respective functions | 3    | 3.6  |      |

| V <sub>I(1.5VIN)</sub>  | Input voltage                   | 1.5VIN is only required for its respective functions | 1.35 | 1.65 | V    |

| V <sub>I(AUXIN)</sub>   |                                 | AUXIN is required for all circuit operations         | 3    | 3.6  |      |

| I <sub>O(3.3VOUT)</sub> |                                 |                                                      | 0    | 1.3  | А    |

| I <sub>O(1.5VOUT)</sub> | Continuous output current       | $T_{\rm J} = 120^{\circ}{\rm C}$                     | 0    | 650  | mA   |

| I <sub>O(AUXOUT)</sub>  |                                 |                                                      | 0    | 275  | mA   |

| TJ                      | Operating virtual junction temp | erature                                              | -40  | 120  | °C   |

### **ELECTRICAL CHARACTERISTICS**

$\begin{array}{l} T_{J}=25^{\circ}C, \ V_{I(3.3VIN)}=V_{I(AUXIN)}=3.3 \ V, \ V_{I(1.5VIN)}=1.5 \ V, \ V_{I(/SHDNx)}, \ V_{I(/STBYx)}=3.3 \ V, \ V_{I(/CPPEx)}=V_{I(/CPUSBx)}=0 \ V, \\ V_{I(/SYSRST)}=3.3 \ V, \ OCx \ and \ RCLKENx \ and \ PERSTx \ are \ open, \ all \ voltage \ outputs \ unloaded \ (unless \ otherwise \ noted) \end{array}$

|                        | I                                                     | PARAMETER                                          | TEST CONDITIONS                                          | MIN  | TYP     | MAX | UNIT  |

|------------------------|-------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|------|---------|-----|-------|

| POWER S                | SWITCH                                                |                                                    |                                                          |      |         |     |       |

|                        |                                                       | 3.3VIN to 3.3VOUT with two switches                | $T_{J} = 25^{\circ}C, I = 1300 \text{ mA each}$          |      | 45      |     | mΩ    |

|                        |                                                       | on for dual                                        | T <sub>J</sub> = 100°C, I = 1300 mA each                 |      |         | 68  | mu    |

|                        | Power switch                                          | 1.5VIN to 1.5VOUT With two switches                | $T_J = 25^{\circ}C$ , I = 650 mA each                    |      | 46      |     | mΩ    |

|                        | resistance                                            | on for dual $T_J = 100^{\circ}$ C, I = 650 mA each |                                                          |      |         | 70  | 11122 |

|                        |                                                       | AUXIN to AUXOUT with two switches                  | $T_J = 25^{\circ}C$ , I = 275 mA each                    |      | 120     |     | mΩ    |

|                        |                                                       | on for dual                                        | $T_J = 100^{\circ}C$ , I = 275 mA each                   |      |         | 200 | mu    |

| R <sub>(DIS_FET)</sub> | IS_FET) Discharge resistance on 3.3V/1.5V/AUX outputs |                                                    | $V_{I(/SHDNx)} = 0 V, I_{(discharge)} = 1 mA$            | 100  |         | 500 | Ω     |

|                        |                                                       | I <sub>OS(3.3VOUT)</sub> (steady-state value)      |                                                          | 1.35 | 2       | 2.5 | А     |

| los                    | Short-circuit<br>output current <sup>(1)</sup>        | I <sub>OS(1.5VOUT)</sub> (steady-state value)      | T <sub>J</sub> (–40, 120°C]. Output powered into a short | 0.67 | 1       | 1.3 | А     |

|                        |                                                       | I <sub>OS(AUXOUT)</sub> (steady-state value)       |                                                          | 275  | 450     | 600 | mA    |

|                        |                                                       |                                                    | Rising temperature, not in overcurrent condition         | 155  | 155 165 |     | °C    |

|                        | Thermal shutdown                                      | Trip point, T <sub>J</sub>                         | Overcurrent condition                                    | 120  | 130     |     | C     |

|                        |                                                       | Hysteresis                                         |                                                          |      | 10      |     |       |

|                        |                                                       |                                                    | $V_{O(3.3VOUT)}$ with 100-m $\Omega$ short               |      | 43      | 100 |       |

|                        | Current-limit response time                           |                                                    | $V_{O(1.5VOUT)}$ with 100-m $\Omega$ short, TPS2231      |      | 100     |     |       |

|                        |                                                       |                                                    | $V_{O(1.5VOUT)}$ with 100-m $\Omega$ short, TPS2236      |      | 110     | 150 | μs    |

|                        |                                                       |                                                    | $V_{O(AUXOUT)}$ with 100-m $\Omega$ short                |      | 38      | 100 |       |

(1) Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

TPS2231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

www.ti.com

## ELECTRICAL CHARACTERISTICS (continued)

$T_{J} = 25^{\circ}\text{C}, \ V_{I(3.3\text{VIN})} = V_{I(\text{AUXIN})} = 3.3 \text{ V}, \ V_{I(1.5\text{VIN})} = 1.5 \text{ V}, \ V_{I(/\text{SHDNx})}, \ V_{I(/\text{STBYx})} = 3.3 \text{ V}, \ V_{I(/\text{CPPEx})} = V_{I(/\text{CPUSBx})} = 0 \text{ V}, \ V_{I(/\text{SYSRST})} = 3.3 \text{ V}, \ OCx \text{ and RCLKENx and PERSTx} are open, all voltage outputs unloaded (unless otherwise noted) }$

|                                               | F                                                                                         | PARAMETER                                        |                                                          | TEST CONI                                                                 | DITIONS                                  | MIN | TYP  | MAX  | UNI |

|-----------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------|-----|------|------|-----|

|                                               |                                                                                           |                                                  | I <sub>I(AUXIN)</sub>                                    |                                                                           |                                          |     | 125  | 200  |     |

|                                               |                                                                                           | Normal operation of<br>TPS2236                   | I <sub>I(3.3VIN)</sub>                                   |                                                                           |                                          |     | 17.5 | 25   | μA  |

|                                               | Operation input                                                                           |                                                  | I <sub>I(1.5VIN)</sub>                                   | Outputs are unloaded,<br>T, [–40, 120°C] (does not in                     | aluda CDDEv and                          |     | 5.5  | 15   |     |

| l                                             | quiescent current                                                                         |                                                  | I <sub>I(AUXIN)</sub>                                    | CPUSBx logic pullup curren                                                |                                          |     | 85   | 150  |     |

|                                               |                                                                                           | Normal operation of<br>TPS2231                   | I <sub>I(3.3VIN)</sub>                                   |                                                                           |                                          |     | 10   | 15   | μA  |

|                                               |                                                                                           | 11 02201                                         | I <sub>I(1.5VIN)</sub>                                   |                                                                           |                                          |     | 2.5  | 10   |     |

|                                               |                                                                                           |                                                  | I <sub>I(AUXIN)</sub>                                    |                                                                           |                                          |     | 200  | 320  | μA  |

|                                               |                                                                                           | Normal operation of<br>TPS2236                   | I <sub>I(3.3VIN)</sub>                                   | -                                                                         |                                          |     | 17.5 | 25   |     |

|                                               |                                                                                           |                                                  | I <sub>I(1.5VIN)</sub>                                   | Outputs are unloaded, T <sub>J</sub> [-4                                  | 0, 120°C] (include                       |     | 5.5  | 15   |     |

|                                               |                                                                                           |                                                  | I <sub>I(AUXIN)</sub>                                    | CPPEx and CPUSBx logic p                                                  |                                          |     | 120  | 210  |     |

|                                               |                                                                                           | Normal operation of<br>TPS2231                   | I <sub>I(3.3VIN)</sub>                                   | -                                                                         |                                          |     | 10   | 15   | μA  |

|                                               | Total input                                                                               | 11 02201                                         | I <sub>I(1.5VIN)</sub>                                   | -                                                                         |                                          |     | 2.5  | 10   |     |

| 1                                             | quiescent current                                                                         |                                                  | I <sub>I(AUXIN)</sub>                                    |                                                                           |                                          |     | 250  | 440  |     |

|                                               |                                                                                           | Shutdown mode of<br>TPS2236                      | I <sub>I(3.3VIN)</sub>                                   |                                                                           |                                          |     | 3.5  | 20   | μA  |

|                                               |                                                                                           | TF 32230                                         | I <sub>I(1.5VIN)</sub>                                   | CPUSB = CPPE = 0 V SHD<br>FETs are on) (include CPPE                      | N = 0 V (discharge<br>x and CPUSBx logic |     | 0.1  | 20   |     |

|                                               |                                                                                           |                                                  | I <sub>I(AUXIN)</sub>                                    | pullup currents and SHDN p                                                |                                          |     | 144  | 270  |     |

|                                               | Shutdown mode of<br>TPS2231                                                               | I <sub>I(3.3VIN)</sub>                           | 120°C]                                                   |                                                                           |                                          | 3.5 | 10   | μA   |     |

|                                               |                                                                                           | 1F32231                                          | I <sub>I(1.5VIN)</sub>                                   | 1                                                                         |                                          |     | 0.5  | 10   |     |

|                                               |                                                                                           |                                                  |                                                          |                                                                           |                                          |     | 40   | 100  | )   |

|                                               |                                                                                           | TPS2236                                          | I <sub>I(3.3VIN)</sub>                                   |                                                                           |                                          |     | 0.1  | 100  | -   |

| Forward leakage<br><sup>kg(FWD)</sup> current |                                                                                           | I <sub>I(1.5VIN)</sub>                           | - SHDN = 3.3 V, CPUSB = C<br>present, discharge FETs are |                                                                           |                                          | 0.1 | 100  |      |     |

|                                               | 0                                                                                         |                                                  |                                                          | at input pins, T <sub>J</sub> = 120°C, in                                 |                                          |     | 20   | 50   |     |

|                                               |                                                                                           | TPS2231                                          |                                                          | current                                                                   |                                          |     | 0.1  | 50   | μA  |

|                                               |                                                                                           |                                                  | I <sub>I(1.5VIN)</sub>                                   | -                                                                         |                                          |     | 0.1  | 50   | •   |

|                                               |                                                                                           |                                                  | $T_J = 25^{\circ}C$                                      |                                                                           |                                          |     | 0.1  | 10   |     |

|                                               |                                                                                           | I <sub>I(AUXOUT)</sub>                           | T <sub>.1</sub> = 120°C                                  | -                                                                         |                                          |     | 50   | μA   |     |

|                                               | Reverse leakage<br>current                                                                |                                                  | T <sub>.1</sub> = 25°C                                   | $V_{O(AUXOUT)} = V_{O(3.3VOUT)} = 3.3$                                    |                                          | 0.1 | 10   |      |     |

| I <sub>lkg(RVS)</sub>                         | (TPS2236 and                                                                              | I <sub>I(3.3VOUT)</sub>                          | T <sub>.1</sub> = 120°C                                  | V <sub>O(1.5VOUT)</sub> = 1.5 V; All volta<br>(current measured from out) |                                          |     | 50   | μA   |     |

|                                               | TPS2231)                                                                                  |                                                  | T <sub>J</sub> = 25°C                                    |                                                                           |                                          |     | 0.1  | 10   |     |

|                                               |                                                                                           | $I_{I(1.5VOUT)}$ $T_{J} = 120^{\circ}C$          |                                                          | -                                                                         |                                          |     |      | 50   | μA  |

| LOGIC S                                       | ECTION (SYSRST.                                                                           | SHDNx, STBYx, PERS                               |                                                          | x, CPUSBx, CPPEx)                                                         |                                          |     |      |      |     |

|                                               | , , , , , , , , , , , , , , , , , , ,                                                     |                                                  |                                                          | SYSRST = 3.6 V, sinking                                                   |                                          |     | 0    | 1    |     |

|                                               | Logic input                                                                               | I(SYSRST)                                        | Input                                                    |                                                                           | TPS2231-2                                |     | 0    | 1    | μA  |

|                                               | supply current                                                                            |                                                  |                                                          | SYSRST = 0 V, sourcing                                                    | TPS2231, TPS2231-1                       | 10  | -    | 30   | r - |

|                                               |                                                                                           |                                                  |                                                          | SHDNx = 3.6 V, sinking                                                    | ,, .                                     |     | 0    | 1    |     |

|                                               |                                                                                           | I <sub>(SHDNx)</sub>                             | Input                                                    | SHDNx = 0 V, sourcing                                                     |                                          | 10  | -    | 30   | μA  |

|                                               |                                                                                           |                                                  |                                                          | $\overline{\text{STBYx}} = 3.6 \text{ V}, \text{ sinking}$                |                                          |     | 0    | 1    |     |

|                                               |                                                                                           | I <sub>(STBYx)</sub>                             | Input                                                    | $\overline{\text{STBYx}} = 0 \text{ V}$ , sourcing                        |                                          | 10  | -    | 30   | μA  |

|                                               |                                                                                           | I <sub>(RCLKENx)</sub>                           | Input                                                    | RCLKENx = 0 V, sourcing                                                   |                                          | 10  |      | 30   | μA  |

|                                               |                                                                                           |                                                  |                                                          | $\overline{\text{CPUSB}}$ or $\overline{\text{CPPE}} = 0$ V, sinl         | kina                                     |     | 0    | 1    | . F |

|                                               |                                                                                           | I <sub>(CPUSBx)</sub> or<br>I <sub>(CPPEx)</sub> | Inputs                                                   | $\overline{\text{CPUSB}}$ or $\overline{\text{CPPE}} = 3.6 \text{ V}$ , s | 0                                        | 10  | v    | 30   | μA  |

|                                               |                                                                                           | High level                                       |                                                          |                                                                           |                                          | 2   |      | 50   |     |

|                                               | Logic input<br>voltage High level   Low level Low level   RCLEN output low voltage Output |                                                  |                                                          |                                                                           |                                          | -   |      | 0.8  | V   |

|                                               |                                                                                           |                                                  | I <sub>O(RCLKEN)</sub> = 60 μA                           |                                                                           |                                          |     | 0.0  | V    |     |

|                                               |                                                                                           |                                                  | Culpul                                                   | 3.3VOUT falling                                                           |                                          | 2.7 |      | 3    | v   |

|                                               |                                                                                           | threshold of output volt                         |                                                          | -                                                                         |                                          | 2.7 |      | 3    | v   |

|                                               | asserted when an                                                                          | y output voltage falls be                        | elow the threshold)                                      | AUXOUT falling<br>1.5VOUT falling<br>3.3VOUT, AUXOUT, or 1.5VOUT falling  |                                          | 1.2 |      |      | v   |

|                                               |                                                                                           |                                                  |                                                          |                                                                           |                                          |     |      | 1.35 |     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$T_{J} = 25^{\circ}C, V_{I(3.3VIN)} = V_{I(AUXIN)} = 3.3 \text{ V}, V_{I(1.5VIN)} = 1.5 \text{ V}, V_{I(/SHDNx)}, V_{I(/STBYx)} = 3.3 \text{ V}, V_{I(/CPPEx)} = V_{I(/CPUSBx)} = 0 \text{ V}, \\ V_{I(/SYSRST)} = 3.3 \text{ V}, \text{ OCx and RCLKENx and PERSTx are open, all voltage outputs unloaded (unless otherwise noted) }$

|                       | PARAMETER                                    | TEST CONDITIONS                                                                | MIN | TYP | MAX  | UNIT |

|-----------------------|----------------------------------------------|--------------------------------------------------------------------------------|-----|-----|------|------|

|                       | PERST de-assertion delay from output voltage | 3.3VOUT, AUXOUT, and 1.5VOUT rising within tolerance                           | 4   | 10  | 20   | ms   |

|                       | PERST assertion delay from SYSRST            | Max time from SYSRST asserted or de-asserted                                   |     |     | 500  | ns   |

| t <sub>W(PERST)</sub> | PERST minimum pulse width                    | 3.3VOUT, AUXOUT, or 1.5VOUT falling out of<br>tolerance or triggered by SYSRST | 100 | 250 |      | μs   |

|                       | PERST output low voltage                     | L 500 A                                                                        |     |     | 0.4  | V    |

|                       | PERST output high voltage                    |                                                                                |     |     |      | V    |

|                       | OC output low voltage                        | $I_{O(/OC)} = 2 \text{ mA}$                                                    |     |     | 0.4  | V    |

|                       | OC leakage current                           | V <sub>O(/OC)</sub> = 3.6 V                                                    |     |     | 1    | μA   |

|                       | OC deglitch                                  | Falling into or out of an overcurrent condition                                | 6   |     | 20   | mS   |

| UNDERV                | OLTAGE LOCKOUT (UVLO)                        | 1                                                                              | -1  |     | 1    |      |

|                       | 3.3VIN UVLO                                  | 3.3VIN level, below which 3.3VIN and 1.5VIN switches are off                   |     |     |      |      |

|                       | 3.3VIN UVLO                                  | 3.3VIN level, below which 3.3VIN switch is off (TPS2231-3 only)                | 2.6 |     | 2.9  |      |

|                       | 1.5VIN UVLO                                  | 1.5VIN level, below which 3.3VIN and 1.5VIN switches are off                   |     |     | 1.25 | V    |

|                       |                                              | 1.5VIN level, below which 1.5VIN switch is off (TPS2231-3 only)                |     |     | 1.25 |      |

|                       | AUXIN UVLO                                   | AUXIN level, below which all switches are off                                  | 2.6 |     | 2.9  | ]    |

|                       | UVLO hysteresis                              |                                                                                |     | 100 |      | m٧   |

### SWITCHING CHARACTERISTICS

$T_J = 25^{\circ}C$ ,  $V_{I(3.3VIN)} = V_{I(AUXIN)} = 3.3 V$ ,  $V_{I(1.5VIN)} = 1.5 V$ ,  $V_{I(/SHDNx)}$ ,  $V_{I(/STBYx)} = 3.3 V$ ,  $V_{I(/CPPEx)} = V_{I(/CPUSBx)} = 0 V$ ,  $V_{I(/SYSPET)} = 3.3 V$ , OCx and RCI KENx and PERSTx are open, all voltage outputs unloaded (unless otherwise noted)

| PARAMETI             |                                      | ER                                                                                         | TEST CONDITIONS                                                              | MIN  | TYP MAX | UNIT |  |

|----------------------|--------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|---------|------|--|

|                      |                                      | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(3.3VOUT)} = 0 \ \text{A}$        | 0.1  | 3       |      |  |

|                      |                                      | AUXIN to AUXOUT                                                                            | $C_{L(AUXOUT)} = 0.1 \ \mu\text{F}, \ I_{O(AUXOUT)} = 0 \ \text{A}$          | 0.1  | 3       |      |  |

| •                    | Output rice times                    | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(1.5VOUT)} = 0 \ \text{A}$        | 0.1  | 3       |      |  |

| t <sub>r</sub>       | Output rise times                    | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(3.3VIN)}/1 \ \text{A}$     | 0.1  | 6       | ms   |  |

|                      |                                      | AUXIN to AUXOUT                                                                            | $C_{L(AUXOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(AUXIN)}/0.250 \ \text{A}$   | 0.1  | 6       |      |  |

|                      |                                      | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(1.5VIN)}/0.500 \ \text{A}$ | 0.1  | 6       |      |  |

|                      |                                      | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(3.3VOUT)} = 0 \ \text{A}$        | 10   | 150     |      |  |

|                      | Output fall times                    | AUXIN to VAUXOUT                                                                           | $C_{L(AUXOUT)} = 0.1 \ \mu\text{F}, \ I_{O(AUXOUT)} = 0 \ \text{A}$          | 10   | 150     | μs   |  |

| t <sub>f</sub>       | when card removed                    |                                                                                            |                                                                              | 10   | 150     |      |  |

| 4                    | (both CPUSB and<br>CPPE de-asserted) | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 20 \ \mu F, \ I_{O(3.3VOUT)} = 0 \ A$                      | 2    | 30      |      |  |

|                      |                                      | AUXIN to VAUXOUT                                                                           | $C_{L(AUXOUT)} = 20 \ \mu F, \ I_{O(AUXOUT)} = 0 \ A$                        | 2    | 30      | ms   |  |

|                      |                                      | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 20 \ \mu F, \ I_{O(1.5VOUT)} = 0 \ A$                      | 2    | 30      |      |  |

|                      | 3.3VIN to 3.3VOUT                    | $C_{L(3.3VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(3.3VOUT)} = 0 \ \text{A}$                      | 10                                                                           | 150  |         |      |  |

|                      | Output fall times                    | AUXIN to VAUXOUT                                                                           | $C_{L(AUXOUT)} = 0.1 \ \mu\text{F}, \ I_{O(AUXOUT)} = 0 \ \text{A}$          | 10   | 150     | μs   |  |

| t <sub>f</sub>       | when SHDN                            | hen SHDN 1.5VIN to 1.5VOUT C <sub>L(1.5VOUT)</sub> = 0.1 μF, I <sub>O(1.5VOUT)</sub> = 0 A |                                                                              | 10   | 150     |      |  |

| 4                    | asserted (card is<br>present)        | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(3.3VIN)}/1 \ A$            | 0.1  | 5       |      |  |

|                      | present)                             | AUXIN to VAUXOUT $C_{L(AUXOUT)} = 100 \ \mu F R_L = V_{I(AUXIN)}/0.250$                    |                                                                              | 0.1  | 5       | ms   |  |

|                      |                                      | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(1.5VIN)}/0.500 \ \text{A}$ | 0.1  | 5       |      |  |

|                      |                                      | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(3.3VOUT)} = 0 \ \text{A}$        | 0.1  | 1       |      |  |

|                      |                                      | AUXIN to VAUXOUT                                                                           | $C_{L(AUXOUT)} = 0.1 \ \mu\text{F}, \ I_{O(AUXOUT)} = 0.4$                   | 0.05 | 0.5     |      |  |

| t                    | Turn-on propagation                  | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(1.5VOUT)} = 0 \ \text{A}$        | 0.1  | 1       | ms   |  |

| t <sub>pd(on)</sub>  | delay                                | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(3.3VIN)}/1 \ A$            | 0.1  | 1.5     | 1113 |  |

|                      |                                      | AUXIN to VAUXOUT                                                                           | $C_{L(AUXOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(AUXIN)}/0.250 \ \text{A}$   | 0.05 | 1       |      |  |

|                      |                                      | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(1.5VIN)}/0.500 \ \text{A}$ | 0.1  | 1.5     |      |  |

|                      |                                      | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(3.3VOUT)} = 0 \ \text{A}$        | 0.1  | 1.5     |      |  |

|                      |                                      | AUXIN to VAUXOUT $C_{L(AUXOUT)} = 0.1 \ \mu\text{F}, I_{O(AUXOUT)} = 0 \ A$ 0.05           |                                                                              | 0.5  |         |      |  |

| •                    | Turn-off propagation                 | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 0.1 \ \mu\text{F}, \ I_{O(1.5VOUT)} = 0 \ \text{A}$        | 0.1  | 1.5     | -    |  |

| t <sub>pd(off)</sub> | delay                                | 3.3VIN to 3.3VOUT                                                                          | $C_{L(3.3VOUT)} = 100 \ \mu F, R_L = V_{I(3.3VIN)}/1 \ A$                    | 0.1  | 1.5     | ms   |  |

|                      |                                      | AUXIN to VAUXOUT                                                                           | $C_{L(AUXOUT)} = 100 \ \mu\text{F}, \ R_L = V_{I(AUXIN)}/0.250 \ \text{A}$   | 0.05 | 0.5     |      |  |

|                      |                                      | 1.5VIN to 1.5VOUT                                                                          | $C_{L(1.5VOUT)} = 100 \ \mu\text{F}, R_L = V_{I(1.5VIN)}/0.500 \ \text{A}$   | 0.1  | 1       |      |  |

Copyright © 2004–2009, Texas Instruments Incorporated

#### Copyright © 2004–2009, Texas Instruments Incorporated

## TPS2231 TPS2236

SLVS536J-JULY 2004-REVISED SEPTEMBER 2009

www.ti.com

INSTRUMENTS

Texas

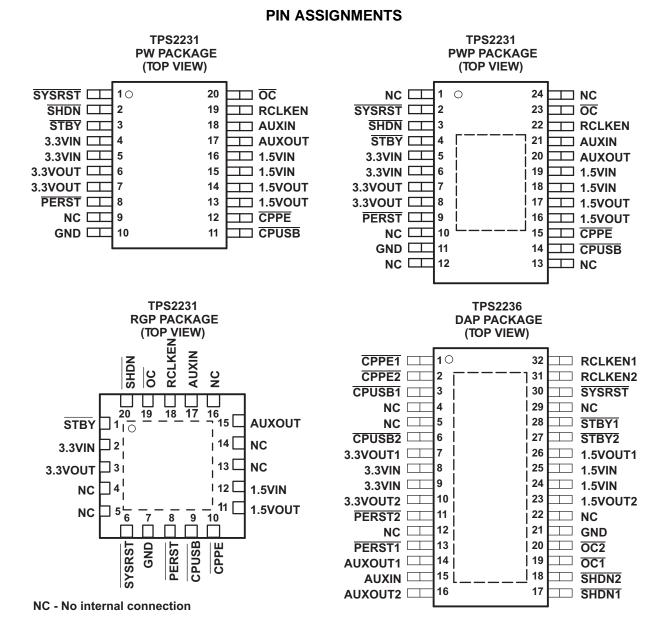

#### **TERMINAL FUNCTIONS**

|         | TERMI  | NAL                     |                        |          |                        |     |                                                                                                                                                                                                                                          |

|---------|--------|-------------------------|------------------------|----------|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | TPS2   |                         |                        | TPS22    | 36                     |     |                                                                                                                                                                                                                                          |

| NAME    |        | NO.                     |                        | NAME     | NO.                    | I/O | DESCRIPTION                                                                                                                                                                                                                              |

|         | PW     | PWP                     | RGP                    |          | DAP                    |     |                                                                                                                                                                                                                                          |

| 3.3VIN  | 4, 5   | 5, 6                    | 2                      | 3.3VIN   | 8, 9                   | I   | 3.3-V input for 3.3VOUT                                                                                                                                                                                                                  |

| 1.5VIN  | 15, 16 | 18, 19                  | 12                     | 1.5VIN   | 24, 25                 | I   | 1.5-V input for 1.5VOUT                                                                                                                                                                                                                  |

| AUXIN   | 18     | 21                      | 17                     | AUXIN    | 15                     | I   | AUX input for AUXOUT and chip power                                                                                                                                                                                                      |

| GND     | 10     | 11                      | 7                      | GND      | 21                     |     | Ground                                                                                                                                                                                                                                   |

| 3.3VOUT | 6, 7   | 7, 8                    | 3                      | 3.3VOUT1 | 7                      | 0   | Switched output that delivers 0 V, 3.3 V or high impedance to card                                                                                                                                                                       |

| 1.5VOUT | 13, 14 | 16, 17                  | 11                     | 1.5VOUT1 | 26                     | 0   | Switched output that delivers 0 V, 1.5 V or high impedance to card                                                                                                                                                                       |

| AUXOUT  | 17     | 20                      | 15                     | AUXOUT1  | 14                     | 0   | Switched output that delivers 0 V, AUX or high impedance to card                                                                                                                                                                         |

|         |        |                         |                        | 3.3VOUT2 | 10                     | 0   | Switched output that delivers 0 V, 3.3 V or high impedance to card                                                                                                                                                                       |

|         |        |                         |                        | 1.5VOUT2 | 23                     | 0   | Switched output that delivers 0 V, 1.5 V or high impedance to card                                                                                                                                                                       |

|         |        |                         |                        | AUXOUT2  | 16                     | 0   | Switched output that delivers 0 V, AUX or high impedance to card                                                                                                                                                                         |

| SYSRST  | 1      | 2                       | 6                      | SYSRST   | 30                     | I   | System Reset input – active low, logic level signal. Internally pulled up to AUXIN.                                                                                                                                                      |

| CPPE    | 12     | 15                      | 10                     | CPPE1    | 1                      | I   | Card Present input for PCI Express cards. Internally pulled up to AUXIN                                                                                                                                                                  |

| CPUSB   | 11     | 14                      | 9                      | CPUSB1   | 3                      | Ι   | Card Present input for USB cards. Internally pulled up to AUXIN.                                                                                                                                                                         |

|         |        |                         |                        | CPPE2    | 2                      | I   | Card Present input for PCI Express cards. Internally pulled up to AUXIN.                                                                                                                                                                 |

|         |        |                         |                        | CPUSB2   | 6                      | Ι   | Card Present input for USB cards. Internally pulled up to AUXIN.                                                                                                                                                                         |

| PERST   | 8      | 9                       | 8                      | PERST1   | 13                     | 0   | A logic level power good to slot 0 (with delay)                                                                                                                                                                                          |

|         | n.     | n.                      |                        | PERST2   | 11                     | 0   | A logic level power good to slot 1 (with delay)                                                                                                                                                                                          |

| SHDN    | 2      | 3                       | 20                     | SHDN1    | 17                     | I   | Shutdown input – active low, logic level signal. Internally pulled up to AUXIN.                                                                                                                                                          |

|         |        |                         |                        | SHDN2    | 18                     | I   | Shutdown input – active low, logic level signal. Internally pulled up to AUXIN.                                                                                                                                                          |

| STBY    | 3      | 4                       | 1                      | STBY1    | 28                     | I   | Standby input – active low, logic level signal. Internally pulled up to AUXIN.                                                                                                                                                           |

|         |        |                         |                        | STBY2    | 27                     | I   | Standby input – active low, logic level signal. Internally pulled up to AUXIN.                                                                                                                                                           |

| RCLKEN  | 19     | 22                      | 18                     | RCLKEN1  | 32                     | I/O | Reference Clock Enable signal. As an output, a logic level power good to host for slot 0 (no delay – open drain). As an input, if kept inactive (low) by the host, prevents PERST from being de-asserted. Internally pulled up to AUXIN. |

|         |        |                         |                        | RCLKEN2  | 31                     | I/O | Reference Clock Enable signal. As an output, a logic level power good to host for slot 1 (no delay – open drain). As an input, if kept inactive (low) by the host, prevents PERST from being de-asserted. Internally pulled up to AUXIN. |

| OC      | 20     | 23                      | 19                     | OC1      | 19                     | 0   | Overcurrent status output for slot 0 (open drain)                                                                                                                                                                                        |

|         |        |                         |                        | OC2      | 20                     | 0   | Overcurrent status output for slot 1 (open drain)                                                                                                                                                                                        |

| NC      | 9      | 1, 10,<br>12, 13,<br>24 | 4, 5,<br>13, 14,<br>16 | NC       | 4, 5,<br>12, 22,<br>29 |     | No connection                                                                                                                                                                                                                            |

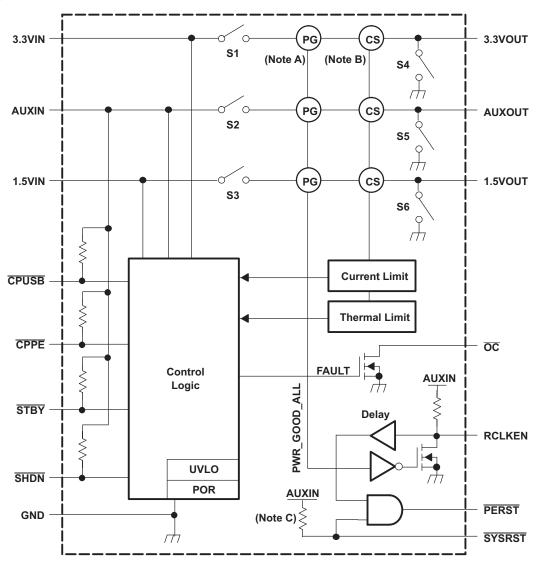

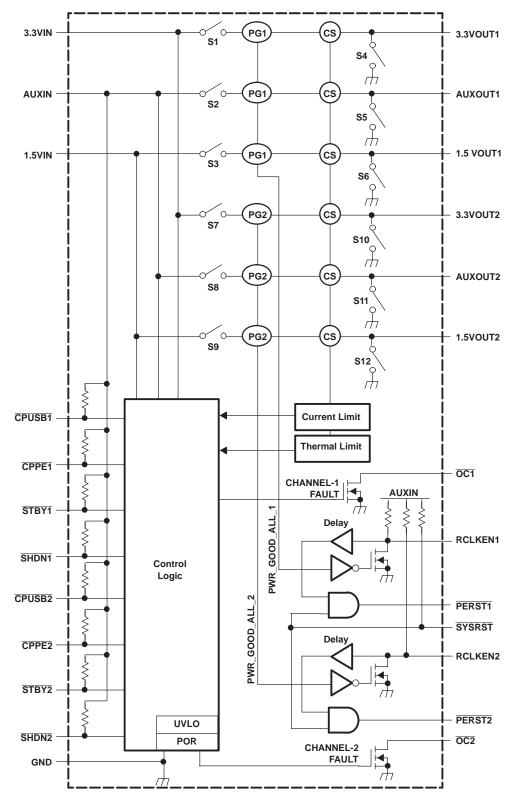

#### FUNCTIONAL BLOCK DIAGRAM

## Single ExpressCard Power Switch

Note A: PG = power good

Note B: CS = current sense

Note C: TPS2231MRGP-2 does not have a pull-up resistor.

#### Dual ExpressCard Power Switch

## DETAILED PIN DESCRIPTIONS

## CPPE

A logic low level on this input indicates that the card present supports <u>PCI</u> Express functions. <u>CPPE</u> connects to the AUXIN input through an internal pullup. When a card is inserted, <u>CPPE</u> is physically connected to ground if the card supports PCI Express functions.

## CPUSB

A logic low level on this input indicates that the card present supports USB functions. CPUSB connects to the AUXIN input through an internal pullup. When a card is inserted, CPUSB is physically connected to ground if the card supports USB functions.

### SHDN

When asserted (logic low), this input instructs the power switch to turn off all voltage outputs and the discharge FETs are activated. SHDN has an internal pullup connected to AUXIN.

## STBY

When asserted (logic low) after the card is inserted, this input places the power switch in standby mode by turning off the 3.3-V and 1.5-V power switches and keeping the AUX switch on. If asserted prior to the card being <u>present</u>, STBY places the power switch in OFF Mode by turning off the AUX, 3.3-V, and 1.5-V power switches. STBY has an internal pullup connected to AUXIN.

#### RCLKEN

This pin serves as both an input and an output. On power up, a discharge FET keeps this signal at a low state as long as any of the output power rails are out of their tolerance range. Once all output power rails are within tolerance, the switch releases RCLKEN allowing it to transition to a high state (internally pulled up to AUXIN). The transition of RCLKEN from a low to a high state starts an internal timer for the purpose of deasserting PERST. As an input, RCLKEN can be kept low to delay the start of the PERST internal timer.

Because RCLKEN is internally connected to a discharge FET, this pin can only be driven low and should never be driven high as a logic input. When an external circuit drives this pin low, RCLKEN becomes an input; otherwise, this pin is an output.

RCLKEN can be used by the host system to enable a clock driver.

### PERST

On power up, this output remains asserted (logic level low) until all power rails are within tolerance. Once all power rails are within tolerance and RCLKEN has been released (logic high), PERST is deasserted (logic high) after a time delay as shown in the parametric table. On power down, this output is asserted whenever any of the power rails drop below their voltage tolerance.

The PERST signal is an output from the host system and an input to the ExpressCard module. This signal is only used by PCI Express-based modules and its function is to place the ExpressCard module in a reset state.

During power up, power down, or whenever power to the ExpressCard module is not stable or not within voltage tolerance limits, the ExpressCard standard requires that PERST be asserted. As a result, this signal also serves as a power-good indicator to the ExpressCard module, and the relationship between the power rails and PERST are explicitly defined in the ExpressCard standard.

The host can also place the ExpressCard module in a reset state by asserting a system reset SYSRST. This system reset generates a PERST to the ExpressCard module without disrupting the voltage rails. This is what is normally called a *warm* reset. However, in a *cold* start situation, the system reset can also be used to extend the length of time that PERST is asserted.

TPS2231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

### SYSRST

This input is driven by the host system and directly affects <u>PERST</u>. Asserting <u>SYSRST</u> (logic low) forces <u>PERST</u> to assert. RCLKEN is not affected by the assertion of <u>SYSRST</u>. <u>SYSRST</u> has an internal pullup connected to AUXIN.

## <u>0C</u>

This pin is an open-drain output. When any of the three power switches (AUX, 3.3V, and 1.5V) is in an overcurrent condition,  $\overline{OC}$  is asserted (logic low) by an internal discharge FET with a deglitch delay. Otherwise, the discharge FET is open, and the pin can be pulled up to a power supply through an external resistor.

### FUNCTIONAL TRUTH TABLES

| VOI   | LTAGE INPL | JTS <sup>(1)</sup> | L    | LOGIC INPUTS |        |        | AGE OUTPUT | S <sup>(2)</sup> | MODE <sup>(3)</sup> |

|-------|------------|--------------------|------|--------------|--------|--------|------------|------------------|---------------------|

| AUXIN | 3.3VIN     | 1.5VIN             | SHDN | STBY         | CP (4) | AUXOUT | 3.3VOUT    | 1.5VOUT          |                     |

| Off   | х          | х                  | х    | х            | х      | Off    | Off        | Off              | OFF                 |

| On    | х          | х                  | 0    | х            | х      | GND    | GND        | GND              | Shutdown            |

| On    | х          | х                  | 1    | х            | 1      | GND    | GND        | GND              | No Card             |

| On    | On         | On                 | 1    | 0            | 0      | On     | Off        | Off              | Standby             |

| On    | On         | On                 | 1    | 1            | 0      | On     | On         | On               | Card Inserted       |

#### Truth Table for Voltage Outputs

(1) For input voltages, On means the respective input voltage is higher than its turnon threshold voltage; otherwise, the voltage is Off (for AUX input, Off means the voltage is close to zero volt).

(2) For output voltages, On means the respective power switch is turned on so the input voltage is connected to the output; Off means the power switch and its output discharge FET are both off; GND means the power switch is off but the output discharge FET is on so the voltage on the output is pulled down to 0 V.

(3) *Mode* assigns each set of input conditions and respective output voltage results to a different name. These modes are referred to as input conditions in the following *Truth Table for Logic Outputs*.

(4)  $\overrightarrow{CP} = \overrightarrow{CPUSB}$  and  $\overrightarrow{CPPE} - \overrightarrow{equal}$  to 1 when both  $\overrightarrow{CPUSB}$  and  $\overrightarrow{CPPE}$  signals are logic high, or equal to 0 when either  $\overrightarrow{CPUSB}$  or  $\overrightarrow{CPPE}$  is low.

|               | INPUT CONDITIONS | In Table for Logic OL | LOGIC OUTPUTS |                       |  |  |

|---------------|------------------|-----------------------|---------------|-----------------------|--|--|

| MODE          | SYSRST           | RCLKEN <sup>(1)</sup> | PERST         | RCLKEN <sup>(2)</sup> |  |  |

| OFF           |                  |                       |               |                       |  |  |

| Shutdown      | Y                | Y                     | 0             |                       |  |  |

| No Card       | Х                | X                     | 0             | 0                     |  |  |

| Standby       |                  |                       |               |                       |  |  |

|               | 0                | Hi-Z                  | 0             | 1                     |  |  |

|               | 0                | 0                     | 0             | 0                     |  |  |

| Card Inserted | 1                | Hi-Z                  | 1             | 1                     |  |  |

|               | 1                | 0                     | 0             | 0                     |  |  |

#### Truth Table for Logic Outputs

(1) RCLKEN as a logic input in this column. RCLKEN is an I/O pin and it can be driven low externally, left open, or connected to high-impedance terminals, such as the gate of a MOSFET. It must not be driven high externally.

(2) RCLKEN as a logic output in this column.

#### **POWER STATES**

If AUXIN is not present, then all input-to-output power switches are kept off (*OFF* mode).

If AUXIN is present and SHDN is asserted (logic low), then <u>all input-to-output</u> power switches are kept off and the output discharge FETs are turned on (*Shutdown* mode). If SHDN is asserted and then de-asserted, the state on the outputs is restored to the state prior to SHDN assertion.

If 3.3VIN, AUXIN and 1.5VIN are present at the input of the power switch and no card is inserted, then all input-to-output power switches are kept off and the output discharge FETs are turned on (*No Card* mode).

If 3.3VIN, AUXIN and 1.5VIN are present at the input of the power switch prior to a card being inserted, then all input-to-output power switches are turned on once a card-present signal (CPUSB and/or CPPE) is detected (*Card Inserted* mode).

If a card is present and all output voltages are being applied, then the STBY is asserted (logic low); the AUXOUT voltage is provided to the card, and the 3.3VOUT and 1.5VOUT switches are turned off (*Standby* mode).

If a card is present and all output voltages are being applied, then the 1.5VIN, or 3.3VIN is removed from the input of the power switch; the AUXOUT voltage is provided to the card and the 3.3VOUT and 1.5VOUT switches are turned off (*Standby* mode). TPS2231-3 only: If 3.3VIN is removed, the 3.3VOUT switch is turned off; and, the 1.5VOUT switch is unaffected. If 1.5VIN is removed, the 1.5VOUT switch is turned off; and, the 3.3VOUT switch is unaffected.

If prior to the insertion of a card, the AUXIN is available at the input of the power switch and 3.3VIN and/or 1.5VIN are not, or if STBY is asserted (logic low), then no power is made available to the card (*OFF* mode). If 1.5VIN and 3.3VIN are made available at the input of the power switch after the card is inserted and STBY is not asserted, all the output voltages are made available to the card (*Card Inserted* mode). TPS2231-3 only: If 1.5VIN or 3.3VIN is made available at the input of the power switch after the card is inserted and STBY is not asserted, all switches above their individual UVLO thresholds will turn on.

### DISCHARGE FETs

The discharge FETs on the outputs are activated whenever the device detects that a card is not present (*No Card* mode). Activation occurs after the input-to-output power switches are turned off (break before make). The discharge FETs de-activate if either of the card-present lines go active low, unless the SHDN pin is asserted.

The discharge FETs are also activated whenever the SHDN input is asserted and stay asserted until SHDN is de-asserted.

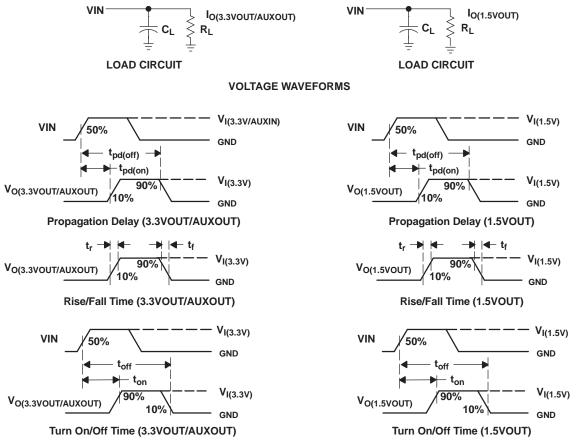

Figure 1. Test Circuits and Voltage Waveforms

## **TYPICAL CHARACTERISTICS**

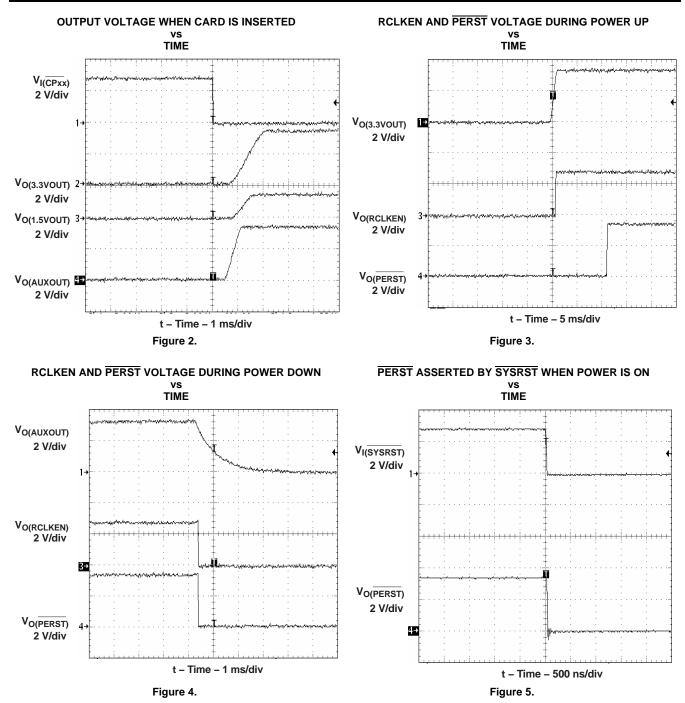

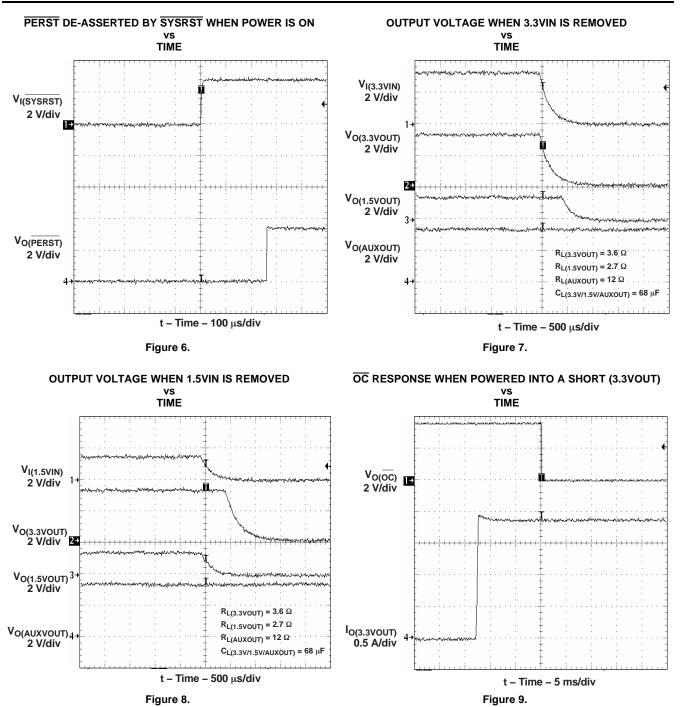

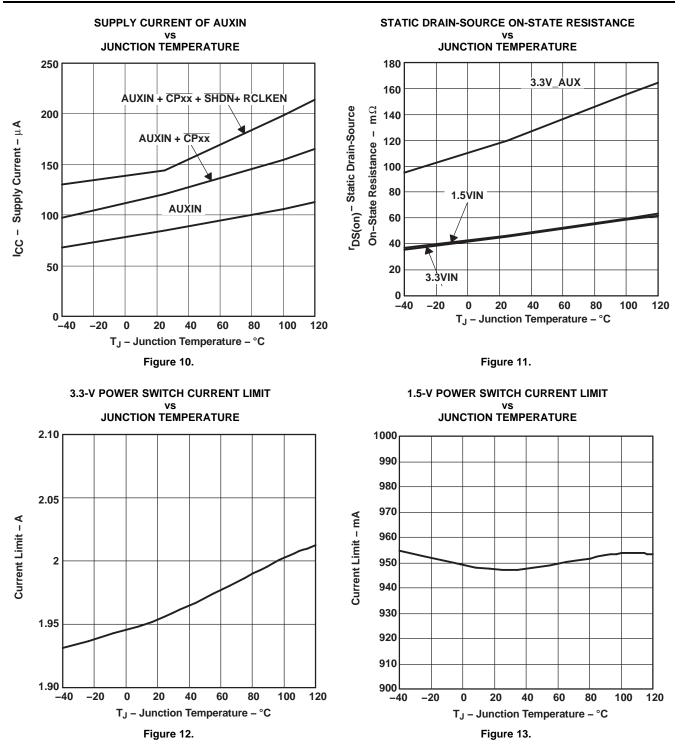

#### Table 1. Table of Graphs

|                                                 |                         | FIGURE |

|-------------------------------------------------|-------------------------|--------|

| Output voltage when card is inserted            | vs Time                 | 2      |

| RCLKEN and PERST voltage during power up        | vs Time                 | 3      |

| RCLKEN and PERST voltage during power down      | vs Time                 | 4      |

| PERST asserted by SYSRST when power is on       | vs Time                 | 5      |

| PERST de-asserted by SYSRST when power is on    | vs Time                 | 6      |

| Output voltage when 3.3VIN is removed           | vs Time                 | 7      |

| Output voltage when 1.5VIN is removed           | vs Time                 | 8      |

| OC response when powered into a short (3.3VOUT) | vs Time                 | 9      |

| Supply current of AUXIN                         | vs Junction temperature | 10     |

| Static drain-source on-state resistance         | vs Junction temperature | 11     |

| 3.3-V power switch current limit                | vs Junction temperature | 12     |

| 1.5-V power switch current limit                | vs Junction temperature | 13     |

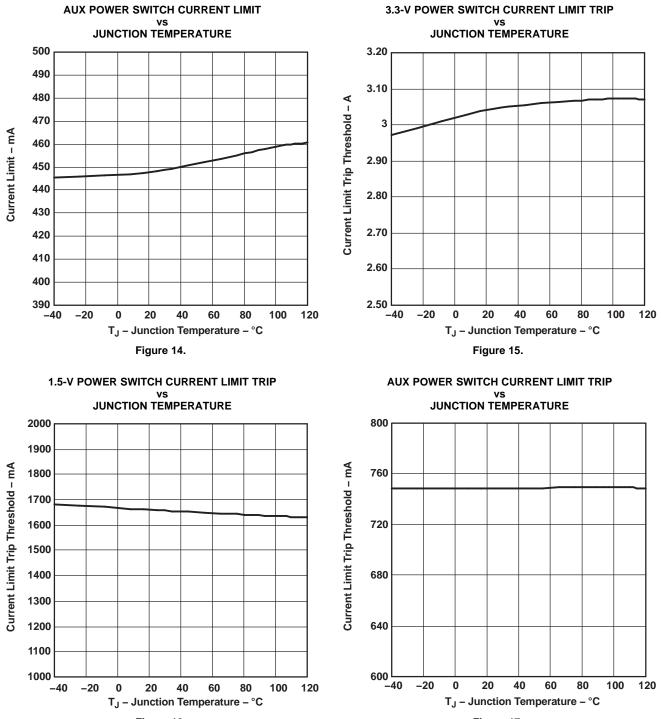

| AUX power switch current limit                  | vs Junction temperature | 14     |

| 3.3-V power switch current limit trip           | vs Junction temperature | 15     |

| 1.5-V power switch current limit trip           | vs Junction temperature | 16     |

| AUX power switch current limit trip             | vs Junction temperature | 17     |

### TPS2231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

www.ti.com

IP52231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

Copyright © 2004–2009, Texas Instruments Incorporated

## TPS2231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

www.ti.com

Figure 16.

Figure 17.

### **APPLICATION INFORMATION**

#### INTRODUCTION TO ExpressCard

An ExpressCard module is an add-in card with a serial interface based on PCI Express and/or Universal Serial Bus (USB) technologies. An ExpressCard comes in two form factors defined as ExpressCard|34 or ExpressCard|54. The difference, as defined by the name, is the width of the module, 34 mm or 54 mm, respectively. Host systems supporting the ExpressCard module can support either the ExpressCard|34 or ExpressCard|54 or both.

#### ExpressCard POWER REQUIREMENTS

Regardless of which ExpressCard module is used, the power requirements as defined in the ExpressCard Standard apply to both on an individual slot basis. The host system is required to supply 3.3 V, 1.5 V, and AUX to each of the ExpressCard slots. However, the voltage is only applied after an ExpressCard is inserted into the slot.

The ExpressCard connector has two pins, CPPE and CPUSB, that are used to signal the host when a card is inserted. If the ExpressCard module itself connects the CPPE to ground, the logic low level on that signal indicates to the host that a card supporting PCI Express has been inserted. If CPUSB is connected to ground, then the ExpressCard module supports the USB interface. If both PCI Express and USB are supported by the ExpressCard module, then both signals, CPPE and CPUSB, must be connected to ground.

In addition to the Card Present signals (CPPE and CPUSB), the host system determines when to apply power to the ExpressCard module based on the state of the system. The state of the system is defined by the state of the 3.3 V, 1.5 V, and AUX input voltage rails. For the sake of simplicity, the 3.3-V and 1.5-V rails are defined as the primary voltage rails as oppose to the auxiliary voltage rail, AUX.

#### ExpressCard POWER SWITCH OPERATION

The ExpressCard power switch resides on the host, and its main function is to control when to send power to the ExpressCard slot. The ExpressCard power switch makes decisions based on the Card Present inputs and on the state of the host system as defined by the primary and auxiliary voltage rails.

The following conditions define the operation of the host power controller:

- 1. When both primary power and auxiliary power at the input of the ExpressCard power switch are off, then all power to the ExpressCard connector is off regardless of whether a card is present.

- 2. When both primary power and auxiliary power at the input of the ExpressCard power switch are on, then power is only applied to the ExpressCard after the ExpressCard power switch detects that a card is present.

- 3. When primary power (either +3.3 V or +1.5 V) at the input of the ExpressCard power switch is off and auxiliary power at the input of the ExpressCard power switch is on, then the ExpressCard power switch behaves in the following manner:

- (a) If neither of the Card Present inputs is detected (no card inserted), then no power is applied to the ExpressCard slot.

- (b) If the card is inserted after the system has entered this power state, then no power is applied to the ExpressCard slot.

- (c) If the card is inserted prior to the removal of the primary power (either +3.3 V or +1.5 V or both) at the input of the ExpressCard power switch, then only the primary power (both +3.3 V and +1.5 V) is removed and the auxiliary power is sent to the ExpressCard slot.

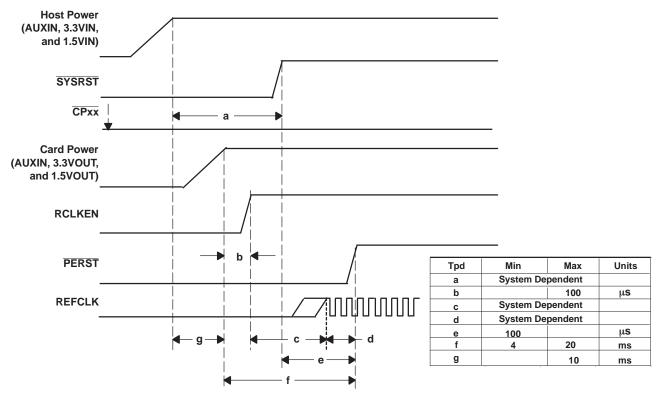

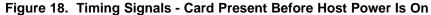

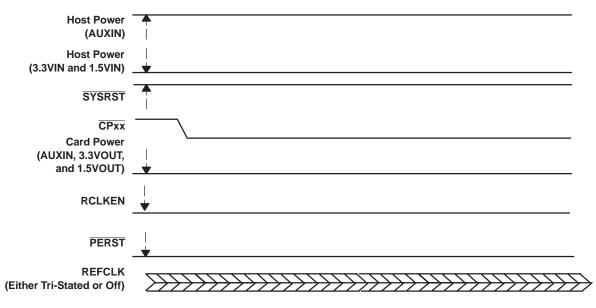

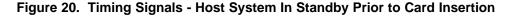

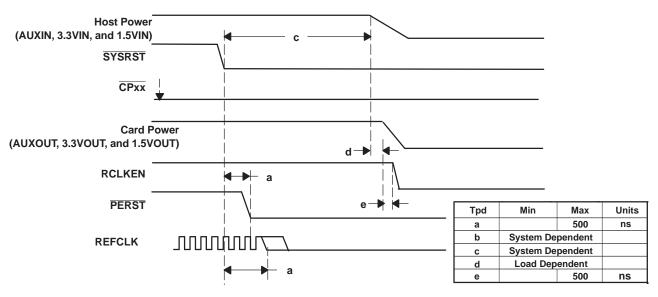

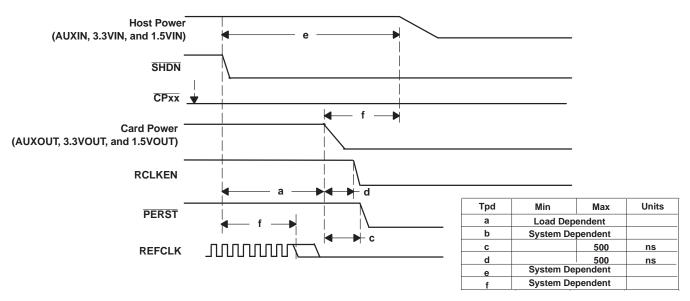

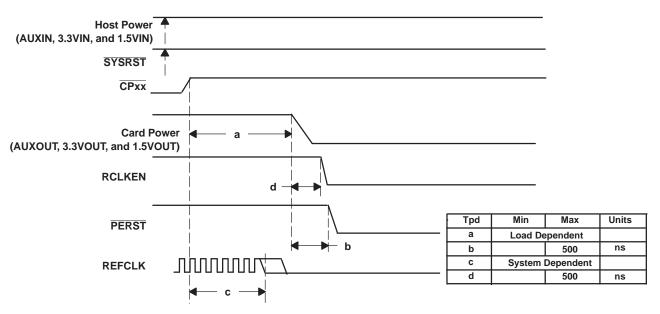

Figure 18 through Figure 23 illustrate the timing relationships between power/logic inputs and outputs of ExpressCard.

TEXAS INSTRUMENTS

www.ti.com

### EXPRESS CARD TIMING DIAGRAMS

Note: Once 3.3 V and 1.5 V are applied, the power switch follows the power-up sequence of Figure 18 or Figure 19.

Figure 21. Timing Signals - Host-Controlled Power Down

TPS2231 TPS2236 SLVS536J – JULY 2004 – REVISED SEPTEMBER 2009

www.ti.com

Figure 22. Timing Signals - Controlled Power Down When SHDN Asserted

Figure 23. Timing Signals - Surprise Card Removal