# TPS62240, TPS62242, TPS62243

SLVS762C -JUNE 2007-REVISED JULY 2015

# TPS6224x 2.25-MHz 300-mA Step-Down Converter in 2 x 2 WSON and SOT Package

#### **Features**

- High Efficiency Greater Than 94%

- Output Current up to 300 mA

- VIN Range from 2 V to 6 V for Li-ion Batteries With Extended Voltage Range

- 2.25-MHz Fixed-Frequency Operation

- Power Save Mode at Light Load Currents

- Output Voltage Accuracy in PWM Mode ±1.5%

- Adjustable Output Voltage from 0.6 V to VIN

- Typical 15-µA Quiescent Current

- 100% Duty Cycle for Lowest Dropout

- Available in a SOT (5) and 2-mm  $\times$  2-mm  $\times$  0.8mm WSON (6) Package

- Allows <1-mm Solution Height

# **Applications**

- Bluetooth™ Headsets

- Mobile Phones, Smart Phones

- **WLAN**

- Low Power DSP Supplies

- Portable Media Players

- **Digital Cameras**

# Description

TPS6224x device is a highly efficient synchronous step-down DC-DC converter. The device provides up to 300-mA output current from a single Li-Ion cell and is ideal for battery powered portable applications like mobile phones and other portable equipment.

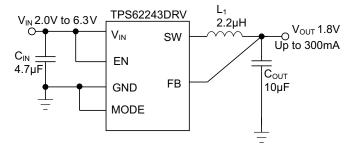

# **Typical Application Schematic**

With an wide input voltage range of 2 V to 6 V, the device also supports two- and three-cell alkaline, 3.3-V and 5-V input voltage rails.

The TPS6224x operates at 2.25-MHz fixed switching frequency and enters power save mode operation at light load currents to maintain high efficiency over the entire load current range.

The power save mode is optimized for low output voltage ripple. For low-noise applications, the device can be forced into fixed-frequency pulse width modulation (PWM) mode by pulling the MODE pin high. In shutdown mode, the current consumption is reduced to less than 1 µA. The TPS6224x allows the use of small inductors and capacitors to achieve a small solution size.

The TPS6224x operates over a free-air temperature range of -40°C to 85°C. The device is available in a 5-pin SOT and a 6-pin 2-mm × 2-mm WSON package.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |

|-------------|----------|-------------------|--|

| TD00004     | WSON (6) | 2.00 mm × 2.00 mm |  |

| TPS6224x    | SOT (5)  | 2.90 mm × 1.60 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

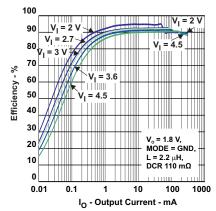

#### **Efficiency vs Output Current**

#### **Table of Contents**

| 1 | Features 1                           |    | 8.4 Device Functional Modes                      | 8  |

|---|--------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                       | 9  | Application and Implementation                   | 10 |

| 3 | Description 1                        |    | 9.1 Application Information                      | 10 |

| 4 | Revision History2                    |    | 9.2 Typical Application                          | 10 |

| 5 | Device Options                       |    | 9.3 System Examples                              | 17 |

| 6 | Pin Configuration and Functions      | 10 | Power Supply Recommendations                     | 17 |

| 7 | Specifications                       | 11 | Layout                                           | 18 |

| • | 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines                           | 18 |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Examples                             | 18 |

|   | 7.3 Recommended Operating Conditions | 12 | Device and Documentation Support                 | 19 |

|   | 7.4 Thermal Information              |    | 12.1 Device Support                              | 19 |

|   | 7.5 Electrical Characteristics       |    | 12.2 Related Links                               | 19 |

|   | 7.6 Typical Characteristics          |    | 12.3 Community Resources                         | 19 |

| 8 | Detailed Description 7               |    | 12.4 Trademarks                                  | 19 |

| ٠ | 8.1 Overview                         |    | 12.5 Electrostatic Discharge Caution             | 19 |

|   | 8.2 Functional Block Diagram         |    | 12.6 Glossary                                    | 19 |

|   | 8.3 Feature Description              | 13 | Mechanical, Packaging, and Orderable Information | 19 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

# 5 Device Options

| PART NUMBER (1)                     | OUTPUT VOLTAGE <sup>(2)</sup> |  |

|-------------------------------------|-------------------------------|--|

| TPS62240                            | adjustable                    |  |

| TPS62240                            | adjustable                    |  |

| TPS62242                            | 1.2 V fixed output voltage    |  |

| TPS62243 1.8 V fixed output voltage |                               |  |

- (1) The DDC (SOT 5 pin) and DRV (WSON 6 pin) packages are available in tape on reel. Add R suffix to order quantities of 3000 parts per reel.

- (2) Contact TI for other fixed output voltage options.

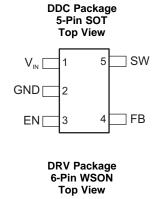

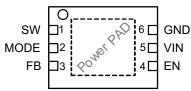

# 6 Pin Configuration and Functions

**Pin Functions**

|      | PIN  |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                  |

|------|------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | WSON | SOT | 1/0 | DESCRIPTION                                                                                                                                                                                                                                  |

| EN   | 4    | 3   | I   | This is the enable pin of the device. Pulling this pin to low forces the device into shutdown mode. Pulling this pin to high enables the device. This pin must be terminated.                                                                |

| GND  | 6    | 2   | PWR | GND supply pin.                                                                                                                                                                                                                              |

| FB   | 3    | 4   | I   | Feedback pin for the internal regulation loop. Connect the external resistor divider to this pin. In case of fixed output voltage option, connect this pin directly to the output capacitor.                                                 |

| MODE | 2    | _   | -   | This pin is only available at WSON package option. MODE pin = High forces the device to operate in fixed-frequency PWM mode. MODE pin = Low enables the power save mode with automatic transition from PFM mode to fixed-frequency PWM mode. |

| sw   | 1    | 5   | 0   | This is the switch pin and is connected to the internal MOSFET switches. Connect the inductor to this terminal.                                                                                                                              |

| VIN  | 5    | 1   | PWR | V <sub>IN</sub> power supply pin.                                                                                                                                                                                                            |

Copyright © 2007–2015, Texas Instruments Incorporated

Submit Documentation Feedback

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                        | MIN    | MAX                      | UNIT |

|------------------|----------------------------------------|--------|--------------------------|------|

| $V_{IN}$         | Input voltage (2)                      | -0.3   | 7                        | V    |

|                  | Voltage at EN, MODE                    | -0.3   | V <sub>IN</sub> +0.3, ≤7 | V    |

|                  | Voltage on SW                          | -0.3   | 7                        | V    |

|                  | Peak output current                    | Intern | ally limited             | Α    |

| $T_{J}$          | Maximum operating junction temperature | -40    | 125                      | °C   |

| T <sub>stg</sub> | Storage temperature                    | -65    | 150                      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                                        |                                                                               | VALUE | UNIT |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                                        | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (2)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge <sup>(1)</sup> | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (3) | ±1000 | V    |

<sup>(1)</sup> The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

# 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                 |                                       | MIN | NOM I | MAX             | UNIT |

|-----------------|---------------------------------------|-----|-------|-----------------|------|

| $V_{\text{IN}}$ | Supply voltage, VIN                   | 2   |       | 6               | V    |

|                 | Output voltage for adjustable voltage | 0.6 |       | $V_{\text{IN}}$ | V    |

| $T_A$           | Operating ambient temperature         | -40 |       | 85              | °C   |

| $T_{J}$         | Operating junction temperature        | -40 |       | 125             | °C   |

#### 7.4 Thermal Information

|                      |                                              | TPS        |           |      |

|----------------------|----------------------------------------------|------------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DRV [WSON] | DDC [SOT] | UNIT |

|                      |                                              | 6 PINS     | 5 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 67.8       | 226.9     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 88.5       | 40.7      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 37.2       | 48.8      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 2.0        | 0.5       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 37.6       | 48.1      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 7.9        | N/A       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: TPS62240 TPS62242 TPS62243

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>3)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.5 Electrical Characteristics

Over full operating ambient temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for condition  $V_{IN}$  = EN = 3.6 V. External components  $C_{IN}$  = 4,7  $\mu F$  0603,  $C_{OUT}$  = 10  $\mu F$  0603, L = 2.2  $\mu H$ , refer to parameter

|                       | PARAMETER                                               | TEST CONDITIONS                                                                                                                     | MIN   | TYP  | MAX      | UNIT  |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|------|----------|-------|

| SUPPLY                |                                                         |                                                                                                                                     |       |      | ·        |       |

| V <sub>IN</sub>       | Input voltage range                                     |                                                                                                                                     | 2     |      | 6        | V     |

|                       | Outside some of                                         | 2.3 V ≤ V <sub>IN</sub> ≤ 6 V                                                                                                       |       |      | 300      | A     |

| I <sub>OUT</sub>      | Output current                                          | $2 \text{ V} \leq \text{V}_{\text{IN}} \leq 2.3 \text{ V}$                                                                          |       |      | 150      | mA    |

|                       |                                                         | I <sub>OUT</sub> = 0 mA. PFM mode enabled (MODE = GND) device not switching                                                         |       | 15   |          |       |

| $I_Q$                 | Operating quiescent current                             | $I_{OUT}$ = 0 mA. PFM mode enabled (MODE = GND) device switching, $V_{OUT}$ = 1.8 V, <sup>(1)</sup>                                 |       | 18.5 |          | μA    |

|                       |                                                         | $I_{OUT}$ = 0 mA, switching with no load (MODE = $V_{IN}$ ), PWM operation , $V_{OUT}$ = 1.8 V, $V_{IN}$ = 3 V                      |       | 3.8  |          | mA    |

| $I_{SD}$              | Shutdown current                                        | EN = GND                                                                                                                            |       | 0.1  | 1        | μΑ    |

| UVLO                  | Undervoltage lockout threshold                          | Falling                                                                                                                             |       | 1.85 |          | V     |

| OVLO                  | Ondervoltage lockout tilleshold                         | Rising                                                                                                                              |       | 1.95 |          | v     |

| ENABLE,               | MODE                                                    |                                                                                                                                     |       |      |          |       |

| $V_{IH}$              | High level input voltage, EN, MODE                      | $2 \text{ V} \leq \text{V}_{\text{IN}} \leq 6 \text{ V}$                                                                            | 1     |      | $V_{IN}$ | V     |

| $V_{IL}$              | Low level input voltage, EN, MODE                       | $2 \text{ V} \leq \text{V}_{\text{IN}} \leq 6 \text{ V}$                                                                            | 0     |      | 0.4      | V     |

| I <sub>IN</sub>       | Input bias current, EN, MODE                            | EN, MODE = GND or $V_{IN}$                                                                                                          |       | 0.01 | 1        | μΑ    |

| POWER S               | WITCH                                                   |                                                                                                                                     |       |      |          |       |

| D                     | High-side MOSFET ON-resistance                          | V <sub>IN</sub> = V <sub>GS</sub> = 3.6 V, T <sub>A</sub> = 25°C                                                                    |       | 240  | 480      | mΩ    |

| R <sub>DS(on)</sub>   | Low-side MOSFET ON-resistance                           |                                                                                                                                     |       | 180  | 380      | 11122 |

| I <sub>LIMF</sub>     | Forward current-limit MOSFET high-<br>side and low-side | V <sub>IN</sub> = V <sub>GS</sub> = 3.6 V                                                                                           | 0.56  | 0.7  | 0.84     | Α     |

| TSD                   | Thermal shutdown                                        | Increasing junction temperature                                                                                                     |       | 140  |          | °C    |

|                       | Thermal shutdown hysteresis                             | Decreasing junction temperature                                                                                                     |       | 20   |          | °C    |

| OSCILLAT              | TOR                                                     |                                                                                                                                     |       |      |          |       |

| $f_{SW}$              | Oscillator frequency                                    | 2 V ≤ V <sub>IN</sub> ≤ 6 V                                                                                                         | 2     | 2.25 | 2.5      | MHz   |

| OUTPUT                |                                                         |                                                                                                                                     |       |      |          |       |

| $V_{OUT}$             | Adjustable output voltage range                         |                                                                                                                                     | 0.6   |      | $V_{IN}$ | V     |

| V <sub>REF</sub>      | Reference voltage                                       |                                                                                                                                     |       | 600  |          | mV    |

|                       | Feedback voltage                                        | MODE = $V_{IN}$ , PWM operation, 2 V $\leq$ $V_{IN}$ $\leq$ 6 V, in fixed output voltage versions $V_{FB} = V_{OUT}$ , see $^{(2)}$ | -1.5% | 0%   | 1.5%     |       |

| $V_{FB}$              | Feedback voltage PFM mode                               | MODE = GND, device in PFM mode                                                                                                      |       | 0%   |          |       |

|                       | Load regulation                                         | PWM mode                                                                                                                            |       | -0.5 |          | %/A   |

| t <sub>Start Up</sub> | Start-up Time                                           | Time from active EN to reach 95% of V <sub>OUT</sub> nominal                                                                        |       | 500  |          | μs    |

| t <sub>Ramp</sub>     | V <sub>OUT</sub> ramp-up time                           | Time to ramp from 5% to 95% of V <sub>OUT</sub>                                                                                     |       | 250  |          | μs    |

| I <sub>lkg</sub>      | Leakage current into SW pin                             | $V_{IN} = 3.6 \text{ V}, V_{IN} = V_{OUT} = V_{SW}, EN = GND,^{(3)}$                                                                |       | 0.1  | 1        | μA    |

See the parameter measurement information.

Submit Documentation Feedback

<sup>(2)</sup>

For  $V_{\text{IN}} = V_{\text{OUT}} + 0.6$ . In fixed output voltage versions, the internal resistor divider network is disconnected from FB pin.

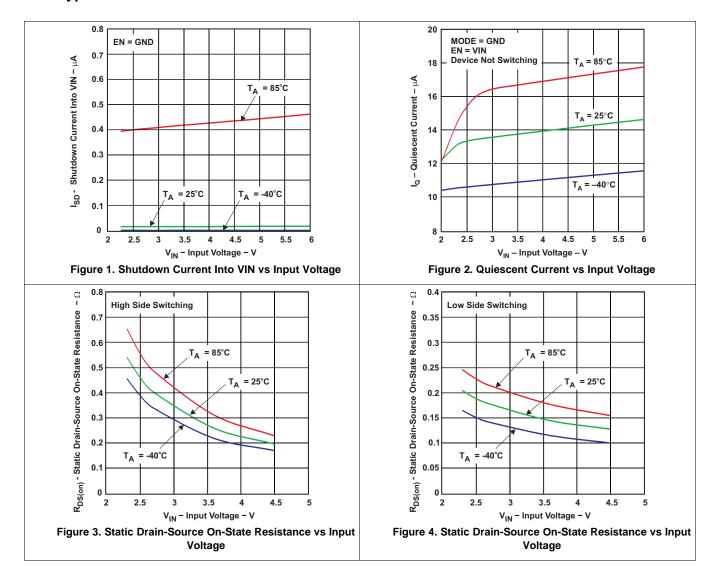

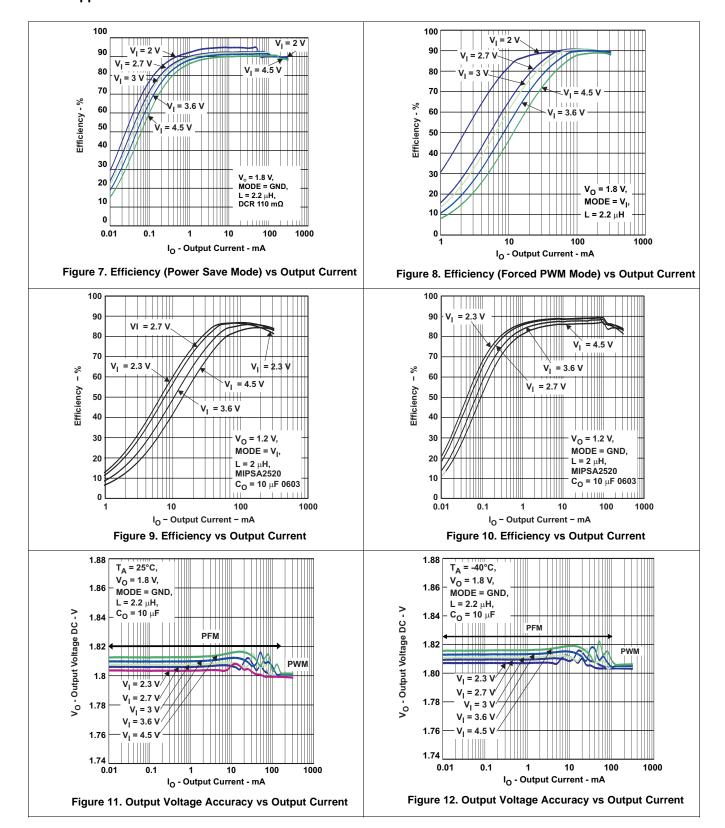

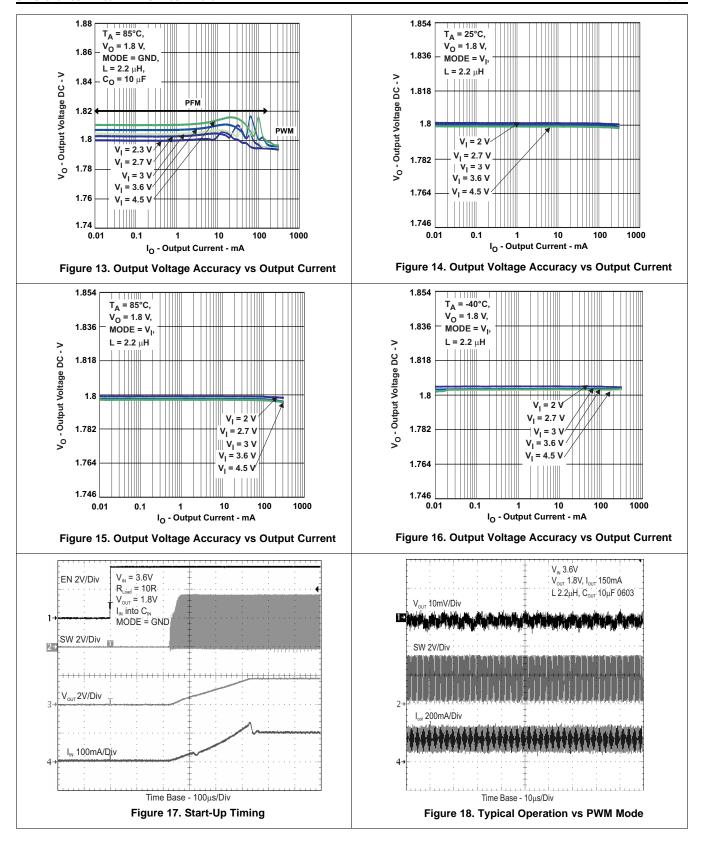

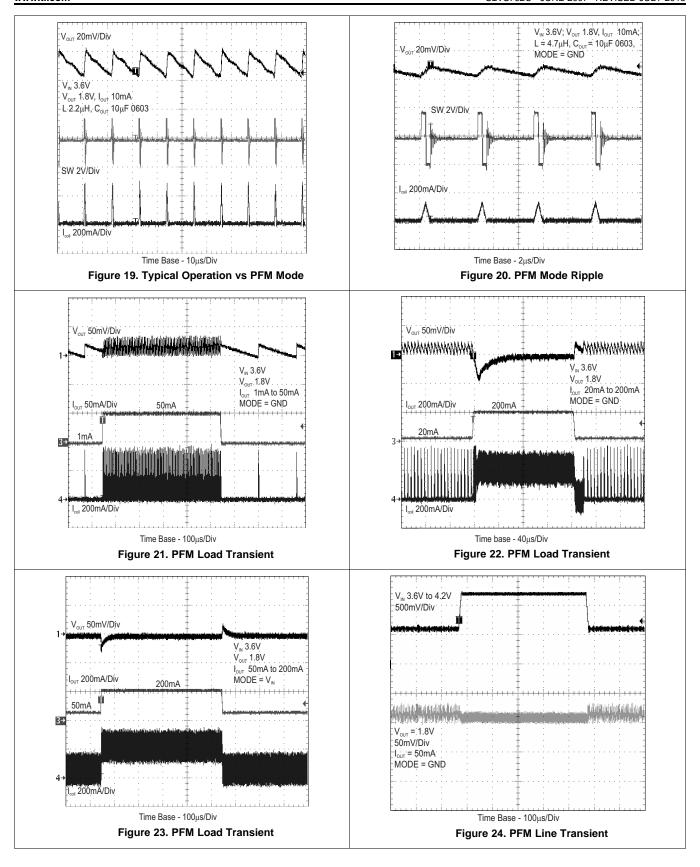

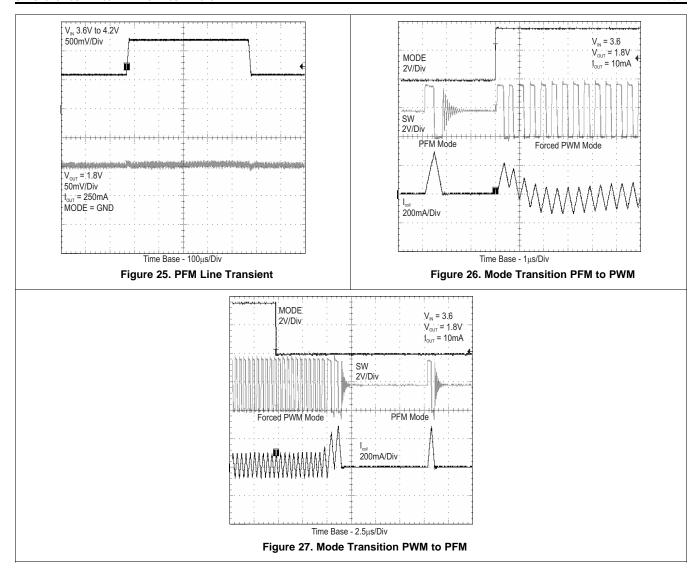

# 7.6 Typical Characteristics

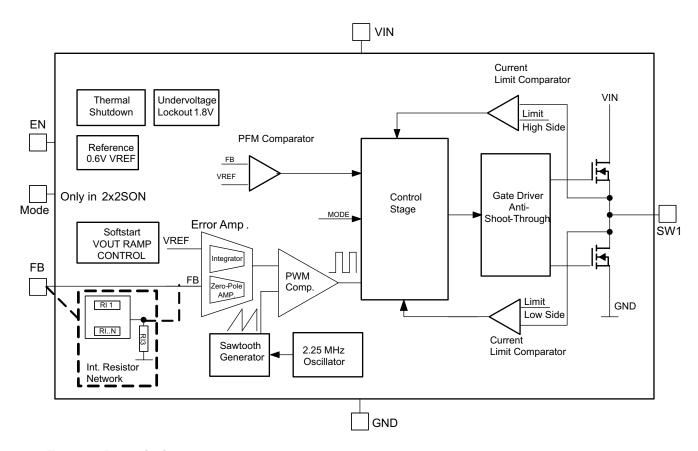

## 8 Detailed Description

#### 8.1 Overview

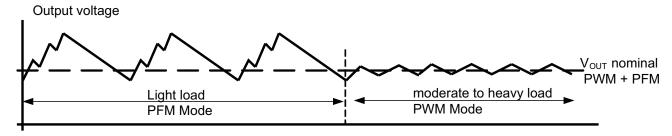

The TPS6224x step-down converter operates with typically 2.25-MHz fixed-frequency pulse width modulation (PWM) at moderate to heavy load currents. At light load currents, the converter can automatically enter power save mode and operates then in pulse frequency modulation (PFM) mode.

During PWM operation, the converter uses a unique fast response voltage mode control scheme with input voltage feed-forward to achieve good line and load regulation, allowing the use of small ceramic input and output capacitors. At the beginning of each clock cycle initiated by the clock signal, the high-side MOSFET switch is turned on. The current then flows from the input capacitor through the high-side MOSFET switch through the inductor to the output capacitor and load. During this phase, the current ramps up until the PWM comparator trips and the control logic turns off the switch. The current-limit comparator also turns off the switch if the current limit of the high-side MOSFET switch is exceeded. After a dead time preventing shoot-through current, the low-side MOSFET rectifier is turned on and the inductor current ramps down. The current then flows from the inductor to the output capacitor and to the load. It returns back to the inductor through the low-side MOSFET rectifier.

The next cycle is initiated by the clock signal again turning off the low-side MOSFET rectifier and turning on the high-side MOSFET switch.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

# 8.3.1 Undervoltage Lockout

The undervoltage lockout circuit prevents the device from malfunctioning at low input voltages and from excessive discharge of the battery and disables the output stage of the converter. The undervoltage lockout threshold is typically 1.85 V with falling  $V_{\rm IN}$ .

Copyright © 2007–2015, Texas Instruments Incorporated

Submit Documentation Feedback

## **Feature Description (continued)**

#### 8.3.2 Mode Selection

The MODE pin allows mode selection between forced PWM mode and power save mode.

Connecting this pin to GND enables the power save mode with an automatic transition between PWM and PFM mode. Pulling the MODE pin high forces the converter to operate in fixed-frequency PWM mode even at light load currents. This allows simple filtering of the switching frequency for noise sensitive applications. In this mode, the efficiency is lower compared to the power save mode during light loads.

The condition of the MODE pin can be changed during operation and allows efficient power management by adjusting the operation mode of the converter to the specific system requirements.

#### 8.3.3 **Enable**

The device is enabled by setting the EN pin to high. During the start up time  $t_{Start\ Up}$ , the internal circuits are settled and the soft start circuit is activated. The EN input can be used to control power sequencing in a system with various DC-DC converters. The EN pin can be connected to the output of another converter, to drive the EN pin high and getting a sequencing of supply rails. With EN pin = GND, the device enters shutdown mode in which all circuits are disabled. In fixed output voltage versions, the internal resistor divider network is then disconnected from FB pin.

#### 8.3.4 Thermal Shutdown

As soon as the junction temperature,  $T_J$ , exceeds 140°C (typical) the device goes into thermal shutdown. In this mode, the high-side and low-side MOSFETs are turned off. The device continues its operation when the junction temperature falls below the thermal shutdown hysteresis.

#### 8.4 Device Functional Modes

#### 8.4.1 Soft Start

The TPS6224x has an internal soft-start circuit that controls the ramp up of the output voltage. The output voltage ramps up from 5% to 95% of its nominal value within typical 250 µs. This limits the inrush current in the converter during ramp up and prevents possible input voltage drops when a battery or high impedance power source is used. The soft-start circuit is enabled within the start-up time, t<sub>Start up</sub>.

#### 8.4.2 Power Save Mode

The power save mode is enabled with MODE pin set to low level. If the load current decreases, the converter will enter power save mode operation automatically. During power save mode, the converter skips switching and operates with reduced frequency in PFM mode with a minimum quiescent current to maintain high efficiency.

The transition from PWM mode to PFM mode occurs once the inductor current in the low-side MOSFET switch becomes zero, which indicates discontinuous conduction mode.

During the power save mode, the output voltage is monitored with a PFM comparator. As the output voltage falls below the PFM comparator threshold of  $V_{OUT}$  nominal, the device starts a PFM current pulse. The high-side MOSFET switch will turn on, and the inductor current ramps up. After the on-time expires, the switch is turned off and the low-side MOSFET switch is turned on until the inductor current becomes zero.

The converter effectively delivers a current to the output capacitor and the load. If the load is below the delivered current, the output voltage will rise. If the output voltage is equal to or greater than the PFM comparator threshold, the device stops switching and enters a sleep mode with typical 15-µA current consumption.

If the output voltage is still below the PFM comparator threshold, a sequence of further PFM current pulses are generated until the PFM comparator threshold is reached. The converter starts switching again once the output voltage drops below the PFM comparator threshold.

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

#### **Device Functional Modes (continued)**

With a fast single-threshold comparator, the output voltage ripple during PFM mode operation can be kept to a minimum. The PFM pulse is time controlled, which allows to modify the charge transferred to the output capacitor by the value of the inductor. The resulting PFM output voltage ripple and PFM frequency both depend on the size of the output capacitor and the inductor value. Increasing output capacitor values and inductor values will minimize the output ripple. The PFM frequency decreases with smaller inductor values and increases with larger values.

If the output current cannot be supported in PFM mode, the device exits PFM mode and enters PWM mode. The power save mode can be disabled through the MODE pin set to high. The converter will then operate in fixedfrequency PWM mode.

Figure 5. Power Save Mode

# 8.4.3 100% Duty Cycle Low Dropout Operation

The device starts to enter 100% duty cycle mode once the input voltage comes close to the nominal output voltage. To maintain the output voltage, the high-side MOSFET switch is turned on 100% for one or more cycles.

With further decreasing V<sub>IN</sub> the high-side MOSFET switch is turned on completely. In this case the converter offers a low input-to-output voltage difference. This is particularly useful in battery-powered applications to achieve longest operation time by taking full advantage of the entire battery voltage range.

The minimum input voltage to maintain regulation depends on the load current and output voltage, and can be calculated as:

$V_{IN}min = V_{OUT}max + I_{OUT}max \times R_{DS(on)}max + R_{L}$

#### where

- I<sub>OUT</sub>max = Maximum output current plus inductor ripple current

- $R_{DS(on)}$ max = Maximum P-channel switch  $R_{DS(on)}$

- $R_1 = DC$  resistance of the inductor

- V<sub>OUT</sub>max = Nominal output voltage plus maximum output voltage tolerance

#### 8.4.4 Short-Circuit Protection

The high-side and low-side MOSFET switches are short-circuit protected with maximum switch current equal to I<sub>I IMF</sub>. The current in the switches is monitored by current-limit comparators. Once the current in the high-side MOSFET switch exceeds the threshold of its current-limit comparator, it turns off and the low-side MOSFET switch is activated to ramp down the current in the inductor and high-side MOSFET switch. The high-side MOSFET switch can only turn on again, once the current in the low-side MOSFET switch has decreased below the threshold of its current-limit comparator.

Copyright © 2007-2015, Texas Instruments Incorporated

(1)

# 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The TPS6224x device is a high-efficiency synchronous step-down DC-DC converter featuring power save mode or 2.25-MHz fixed-frequency operation.

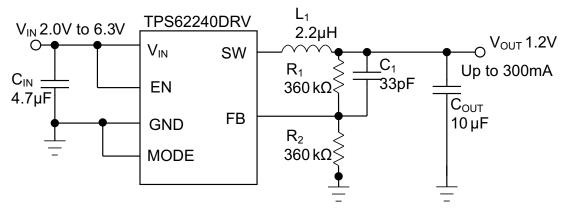

# 9.2 Typical Application

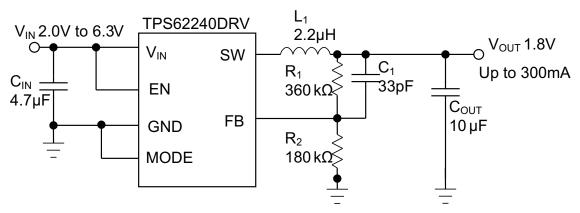

Figure 6. TPS62240DRV Adjustable 1.2 V

# 9.2.1 Design Requirements

The device operates over an input voltage range from 2 V to 6 V. The output voltage is adjustable using an external feedback divider.

#### 9.2.2 Detailed Design Procedure

Table 1 shows the list of components for the Application Curves.

**Table 1. List of Components**

| COMPONENT REFERENCE             | PART NUMBER                                       | MANUFACTURER | VALUE                      |  |  |

|---------------------------------|---------------------------------------------------|--------------|----------------------------|--|--|

| C <sub>IN</sub>                 | GRM188R60J475K                                    | Murata       | 4.7 µF, 6.3 V. X5R Ceramic |  |  |

| C <sub>OUT</sub>                | GRM188R60J106M                                    | Murata       | 10 μF, 6.3 V. X5R Ceramic  |  |  |

| C <sub>1</sub>                  |                                                   | Murata       | 22 pF, COG Ceramic         |  |  |

| L <sub>1</sub>                  | LPS3015                                           | Coilcraft    | 2.2 μH, 110 mΩ             |  |  |

| R <sub>1</sub> , R <sub>2</sub> | Values depending on the programmed output voltage |              |                            |  |  |

#### 9.2.2.1 Output Voltage Setting

The output voltage can be calculated to:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_1}{R_2}\right)_{\text{with an internal reference voltage } V_{REF} \text{ typical 0.6 V.}}$$

(2)

To minimize the current through the feedback divider network,  $R_2$  should be 180 k $\Omega$  or 360 k $\Omega$ . The sum of  $R_1$  and  $R_2$  should not exceed approximately 1 M $\Omega$ , to keep the network robust against noise.

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

An external feedforward capacitor  $C_1$  is required for optimum load transient response. The value of  $C_1$  should be in the range from 22 pF to 33 pF.

Route the FB line away from noise sources, such as the inductor or the SW line.

#### 9.2.2.2 Output Filter Design (Inductor and Output Capacitor)

The TPS6224x is designed to operate with inductors in the range of 1.5  $\mu$ H to 4.7  $\mu$ H and with output capacitors in the range of 4.7  $\mu$ F to 22  $\mu$ F. The device is optimized for operation with a 2.2- $\mu$ H inductor and 10- $\mu$ F output capacitor.

Larger or smaller inductor values can be used to optimize the performance of the device for specific operation conditions. For stable operation, the L and C values of the output filter may not fall below 1-µH effective inductance and 3.5-µF effective capacitance. Selecting larger capacitors is less critical because the corner frequency of the L-C filter moves to lower frequencies with fewer stability problems.

#### 9.2.2.2.1 Inductor Selection

The inductor value has a direct effect on the ripple current. The selected inductor must be rated for its DC resistance and saturation current. The inductor ripple current ( $\Delta I_L$ ) decreases with higher inductance and increases with higher  $V_{IN}$  or  $V_{OUT}$ .

The inductor selection also has an impact on the output voltage ripple in the PFM mode. Higher inductor values will lead to lower output voltage ripple and higher PFM frequency, and lower inductor values will lead to a higher output voltage ripple but lower PFM frequency.

Equation 3 calculates the maximum inductor current in PWM mode under static load conditions. The saturation current of the inductor should be rated higher than the maximum inductor current as calculated with Equation 4. This is recommended because during heavy load transients the inductor current will rise above the calculated value.

$$\Delta I_{L} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f}$$

$$I_{Lmax} = I_{OUTmax} + \frac{\Delta I_{L}}{2}$$

(3)

#### where

- f = Switching frequency (2.25-MHz typical)

- L = Inductor value

- $\Delta I_L$  = Peak-to-peak inductor ripple current

A more conservative approach is to select the inductor current rating just for the maximum switch current limit  $I_{\text{LIME}}$  of the converter.

Accepting larger values of ripple current allows the use of low inductance values, but results in higher output voltage ripple, greater core losses, and lower output current capability.

The total losses of the coil have a strong impact on the efficiency of the DC-DC conversion and consist of both the losses in the DC resistance ( $R_{(DC)}$ ) and the following frequency-dependent components:

- The losses in the core material (magnetic hysteresis loss, especially at high switching frequencies)

- Additional losses in the conductor from the skin effect (current displacement at high frequencies)

- Magnetic field losses of the neighboring windings (proximity effect)

- Radiation losses

Copyright © 2007–2015, Texas Instruments Incorporated

Submit Documentation Feedback

| Table | 2 | l ist | Ωf | Indi | ictors |

|-------|---|-------|----|------|--------|

|       |   |       |    |      |        |

| DIMENSIONS (mm <sup>3</sup> ) | INDUCTANCE (µH) | INDUCTOR TYPE    | SUPPLIER       |

|-------------------------------|-----------------|------------------|----------------|

| 2.5 × 2 × 1                   | 2               | MIPS2520D2R2     | FDK            |

| 2.5 × 2 × 1.2                 | 2               | MIPSA2520D2R2    | FDK            |

| 2.5 × 2 × 1                   | 2.2             | KSLI-252010AG2R2 | Hitachi Metals |

| 2.5 × 2 × 1.2                 | 2.2             | LQM2HPN2R2MJ0L   | Murata         |

| 3 × 3 × 1.4                   | 2.2             | LPS3015          | Coilcraft      |

#### 9.2.2.2.2 Output Capacitor Selection

The advanced fast-response voltage mode control scheme of the TPS6224x allows the use of tiny ceramic capacitors. Ceramic capacitors with low ESR values have the lowest output voltage ripple and are recommended. The output capacitor requires either an X7R or X5R dielectric. Y5V and Z5U dielectric capacitors, aside from their wide variation in capacitance overtemperature, become resistive at high frequencies.

At nominal load current, the device operates in PWM mode and the RMS ripple current is calculated as:

$$I_{RMSC_{OUT}} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

(5)

At nominal load current, the device operates in PWM mode and the overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

$$\Delta V_{OUT} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \left(\frac{1}{8 \times C_{OUT} \times f} + ESR\right)$$

(6)

At light load currents, the converter operates in power save mode and the output voltage ripple depends on the output capacitor and inductor value. Larger output capacitor and inductor values minimize the voltage ripple in PFM mode and tighten DC output accuracy in PFM mode.

#### 9.2.2.2.3 Input Capacitor Selection

The buck converter has a natural pulsating input current; therefore, a low ESR input capacitor is required for best input voltage filtering, and minimizing the interference with other circuits caused by high input voltage spikes. For most applications, a 4.7- $\mu$ F to 10- $\mu$ F ceramic capacitor is recommended. Because ceramic capacitors lose up to 80% of their initial capacitance at 5 V, it is recommended that a 10- $\mu$ F input capacitor be used for input voltages greater than 4.5 V. The input capacitor can be increased without any limit for better input voltage filtering.

Take care when using only small ceramic input capacitors. When a ceramic capacitor is used at the input, and the power is being supplied through long wires, such as from a wall adapter, a load step at the output, or  $V_{IN}$  step on the input, can induce ringing at the VIN pin. The ringing can couple to the output and be mistaken as loop instability, or could even damage the part by exceeding the maximum ratings

Table 3. List of Capacitors

| CAPACITANCE | TYPE              | SIZE                                           | SUPPLIER |

|-------------|-------------------|------------------------------------------------|----------|

| 4.7 µF      | GRM188R60J475K    | 0603: $1.6 \times 0.8 \times 0.8 \text{ mm}^3$ | Murata   |

| 10 μF       | GRM188R60J106M69D | 0603: 1.6 × 0.8 × 0.8 mm <sup>3</sup>          | Murata   |

Submit Documentation Feedback

## 9.2.3 Application Curves

Submit Documentation Feedback

#### 9.3 System Examples

# 9.3.1 TPS62240, Adjustable Output Voltage 1.8 V

Figure 28. TPS62240DRV 1.8 V

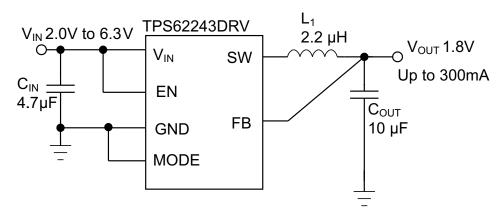

# 9.3.2 TPS62243, Fixed Output Voltage 1.8 V

Figure 29. TPS62243 Fixed 1.8 V

# 10 Power Supply Recommendations

The TPS6224x device has no special requirements for its input power supply. The input power supply output current must be rated according to the supply voltage, output voltage, and output current of the TPS6224x.

# 11 Layout

#### 11.1 Layout Guidelines

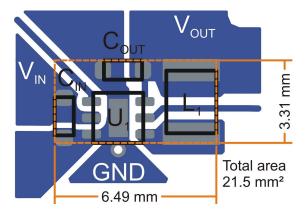

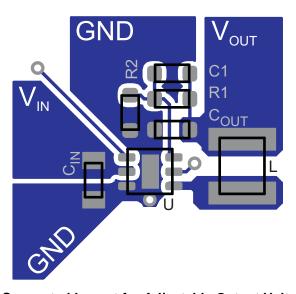

As for all switching power supplies, the layout is an important step in the design. Proper function of the device demands careful attention to PCB layout. Care must be taken in board layout to get the specified performance. If the layout is not carefully done, the regulator could show poor line and/or load regulation, and additional stability issues as well as EMI problems. It is critical to provide a low inductance, impedance ground path. Therefore, use wide and short traces for the main current paths. The input capacitor should be placed as close as possible to the IC pins as well as the inductor and output capacitor.

Connect the GND pin of the device to the PowerPAD™ land of the PCB and use this pad as a star point. Use a common power GND node and a different node for the signal GND to minimize the effects of ground noise. Connect these ground nodes together to the PowerPAD land (star point) underneath the IC. Keep the common path to the GND pin, which returns the small signal components, and the high current of the output capacitors as short as possible to avoid ground noise. The FB line should be connected right to the output capacitor and routed away from noisy components and traces (for example, the SW line).

# 11.2 Layout Examples

Figure 30. Suggested Layout for Fixed Output Voltage Options

Figure 31. Suggested Layout for Adjustable Output Voltage Version

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

# 12 Device and Documentation Support

#### 12.1 Device Support

#### 12.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 12.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 4. Related Links

| PARTS    | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |  |  |

|----------|----------------|--------------|---------------------|---------------------|---------------------|--|--|

| TPS62240 | Click here     | Click here   | Click here          | Click here          | Click here          |  |  |

| TPS62242 | Click here     | Click here   | Click here          | Click here          | Click here          |  |  |

| TPS62243 | Click here     | Click here   | Click here          | Click here          | Click here          |  |  |

## 12.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.4 Trademarks

PowerPAD, E2E are trademarks of Texas Instruments. Bluetooth is a trademark of Bluetooth SIG, Inc.

All other trademarks are the property of their respective owners.

#### 12.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 12.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2007–2015, Texas Instruments Incorporated

www.ti.com 1-Mar-2024

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                         |         |

| TPS62240DDCR     | ACTIVE | SOT-23-THIN  | DDC                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | ВУО                     | Samples |

| TPS62240DDCRG4   | ACTIVE | SOT-23-THIN  | DDC                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | ВУО                     | Samples |

| TPS62240DDCT     | ACTIVE | SOT-23-THIN  | DDC                | 5    | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | ВУО                     | Samples |

| TPS62240DRVR     | ACTIVE | WSON         | DRV                | 6    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | BYJ                     | Samples |

| TPS62240DRVRG4   | ACTIVE | WSON         | DRV                | 6    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | BYJ                     | Samples |

| TPS62240DRVT     | ACTIVE | WSON         | DRV                | 6    | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | BYJ                     | Samples |

| TPS62242DRVR     | ACTIVE | WSON         | DRV                | 6    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | CCY                     | Samples |

| TPS62242DRVT     | ACTIVE | WSON         | DRV                | 6    | 250            | RoHS & Green | Call TI   NIPDAU              | Level-1-260C-UNLIM | -40 to 85    | CCY                     | Samples |

| TPS62243DRVR     | ACTIVE | WSON         | DRV                | 6    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | CBQ                     | Samples |

| TPS62243DRVT     | ACTIVE | WSON         | DRV                | 6    | 250            | RoHS & Green | Call TI   NIPDAU              | Level-1-260C-UNLIM | -40 to 85    | CBQ                     | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: Til defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 1-Mar-2024

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS62242, TPS62243:

Automotive: TPS62242-Q1, TPS62243-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 28-Dec-2024

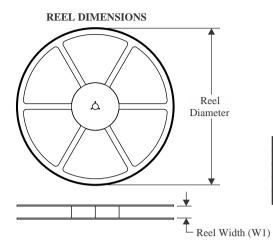

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO BO Cavity AO

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

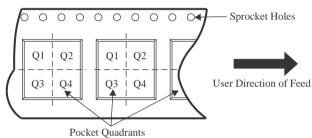

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS62240DDCR | SOT-23-<br>THIN | DDC                | 5 | 3000 | 179.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS62240DDCT | SOT-23-<br>THIN | DDC                | 5 | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS62240DRVR | WSON            | DRV                | 6 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62240DRVT | WSON            | DRV                | 6 | 250  | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

| TPS62240DRVT | WSON            | DRV                | 6 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62242DRVR | WSON            | DRV                | 6 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

| TPS62242DRVR | WSON            | DRV                | 6 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62242DRVT | WSON            | DRV                | 6 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62242DRVT | WSON            | DRV                | 6 | 250  | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

| TPS62243DRVR | WSON            | DRV                | 6 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62243DRVT | WSON            | DRV                | 6 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62243DRVT | WSON            | DRV                | 6 | 250  | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

www.ti.com 28-Dec-2024

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS62240DDCR | SOT-23-THIN  | DDC             | 5    | 3000 | 200.0       | 183.0      | 25.0        |

| TPS62240DDCT | SOT-23-THIN  | DDC             | 5    | 250  | 200.0       | 183.0      | 25.0        |

| TPS62240DRVR | WSON         | DRV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62240DRVT | WSON         | DRV             | 6    | 250  | 200.0       | 183.0      | 25.0        |

| TPS62240DRVT | WSON         | DRV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| TPS62242DRVR | WSON         | DRV             | 6    | 3000 | 200.0       | 183.0      | 25.0        |

| TPS62242DRVR | WSON         | DRV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62242DRVT | WSON         | DRV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| TPS62242DRVT | WSON         | DRV             | 6    | 250  | 203.0       | 203.0      | 35.0        |

| TPS62243DRVR | WSON         | DRV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62243DRVT | WSON         | DRV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| TPS62243DRVT | WSON         | DRV             | 6    | 250  | 203.0       | 203.0      | 35.0        |

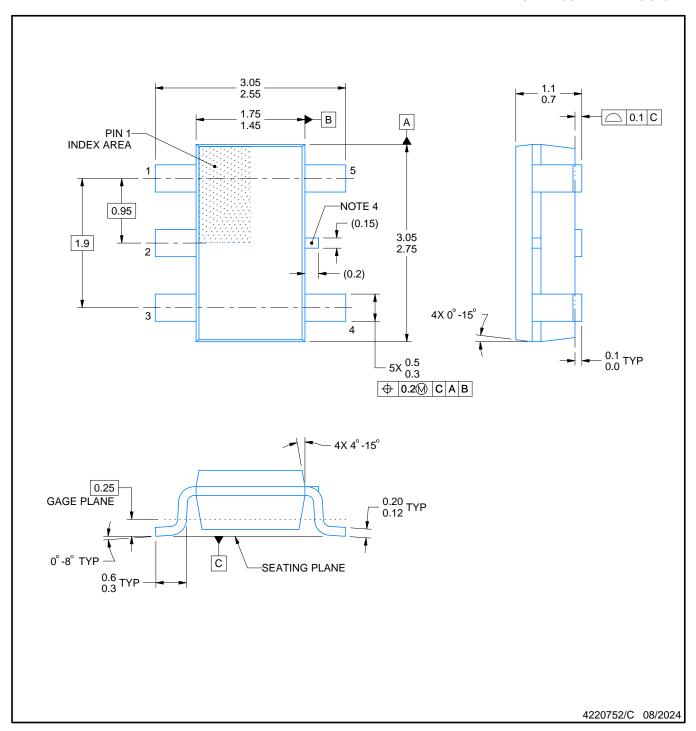

SMALL OUTLINE TRANSISTOR

## NOTES:

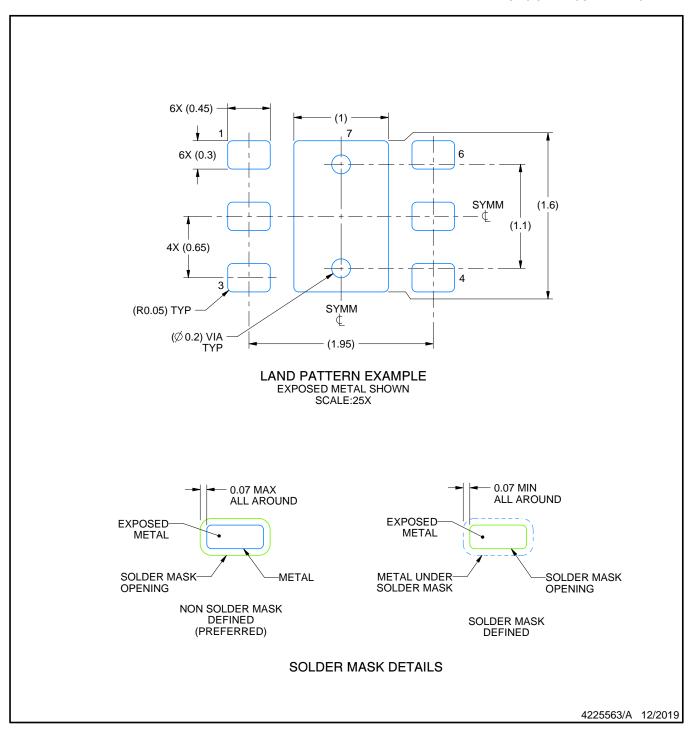

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC MO-193.

- 4. Support pin may differ or may not be present.

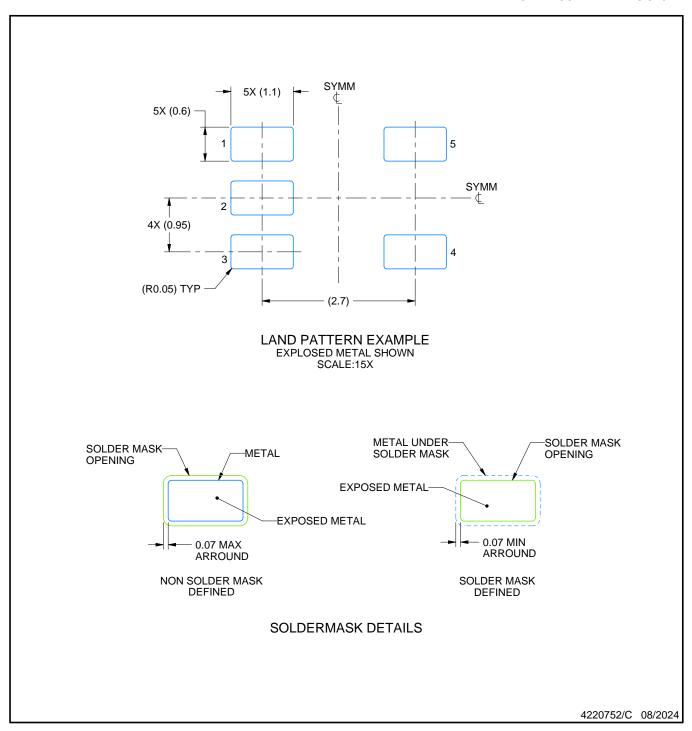

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 4. Publication IPC-7351 may have alternate designs.

- 5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

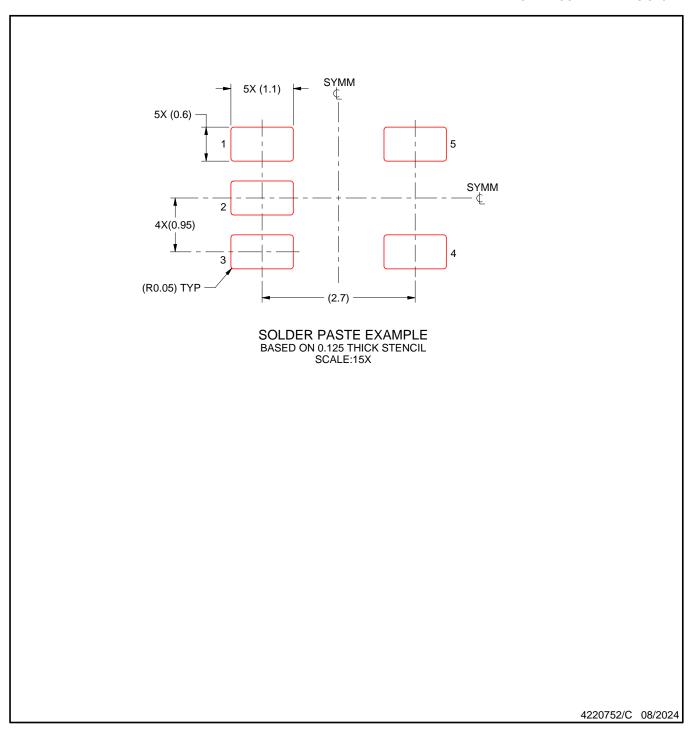

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4206925/F

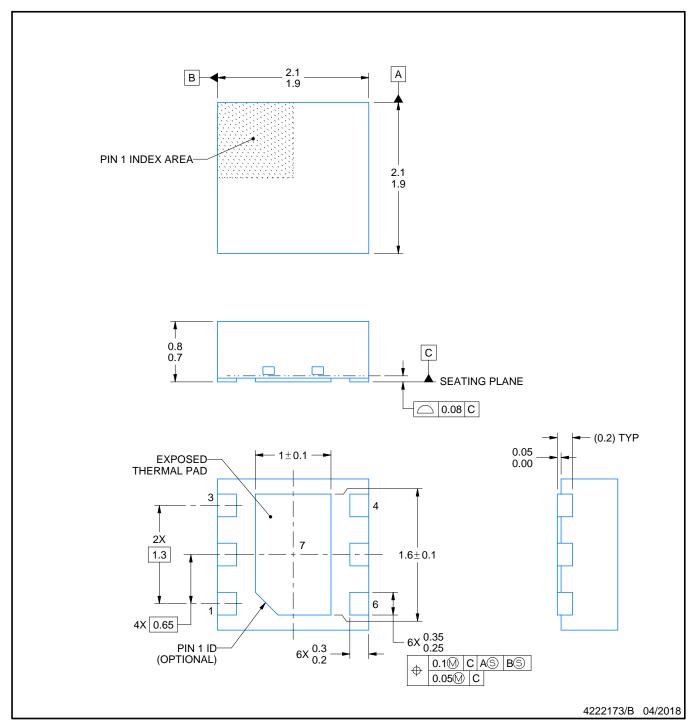

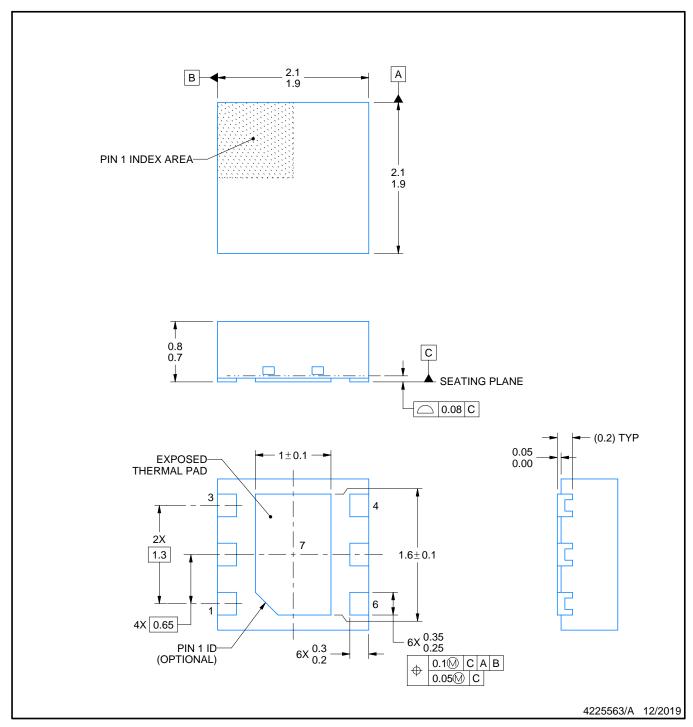

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

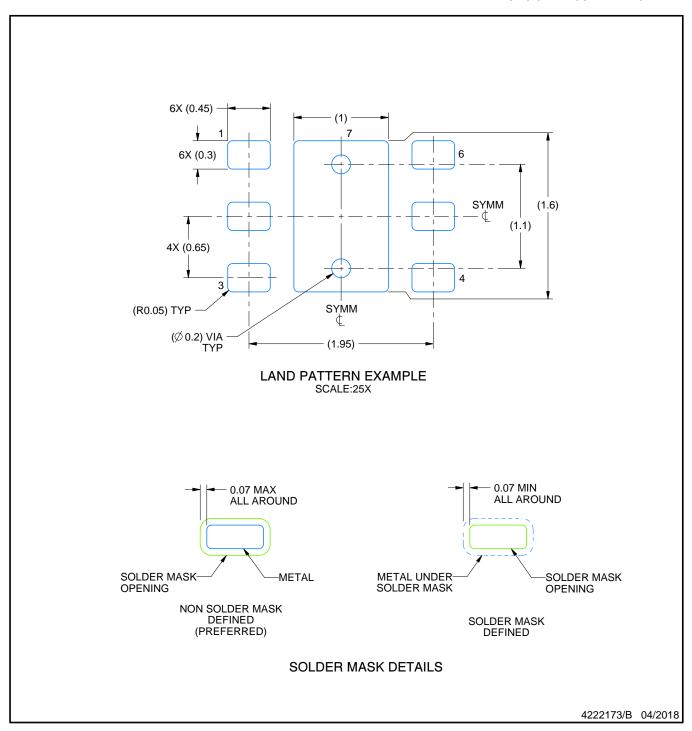

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature

- number SLUA271 (www.ti.com/lit/slua271).

5. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

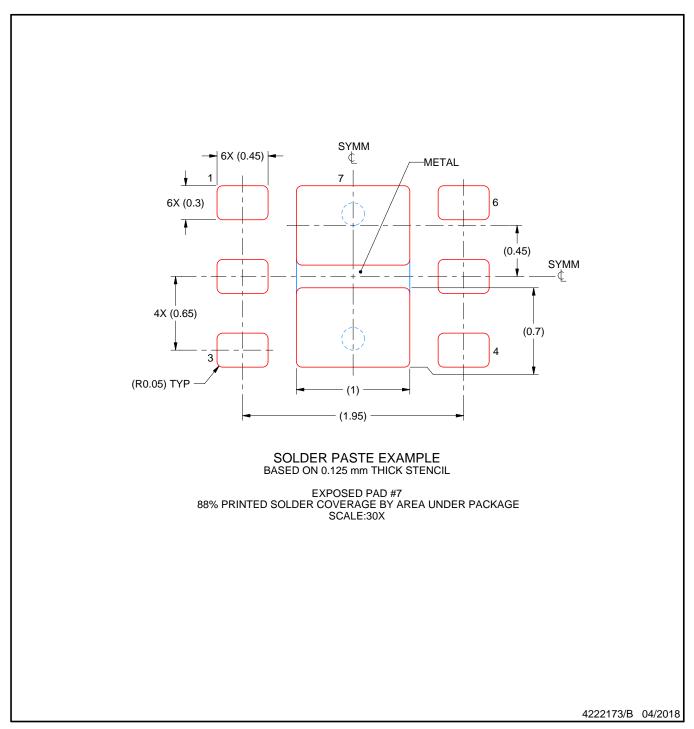

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

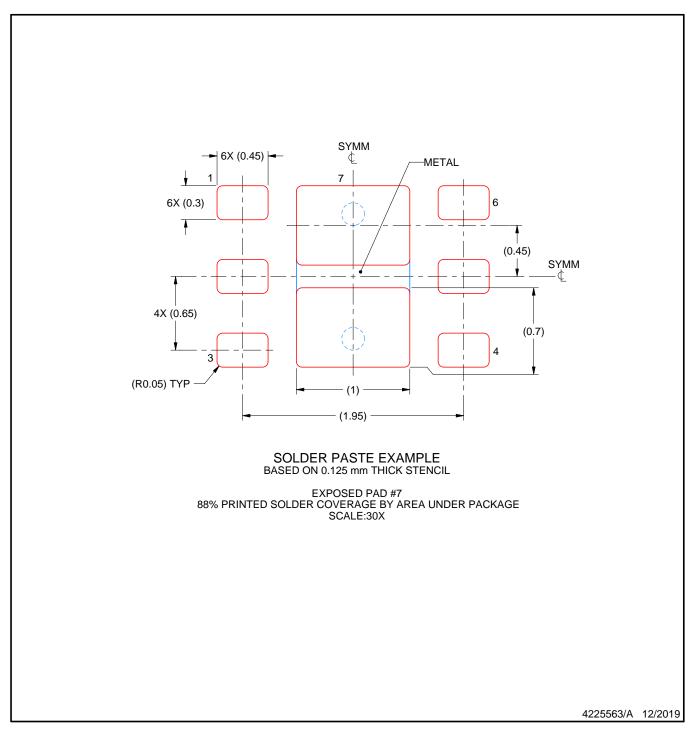

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated