SNAS740B -OCTOBER 2017-REVISED JANUARY 2019

LMX2572

# LMX2572 6.4-GHz Low power wideband RF synthesizer with phase synchronization and JESD204B support

## 1 Features

- Output frequency: 12.5 MHz to 6.4 GHz

- Low power consumption: 75 mA at 3.3-V supply

- -106-dBc/Hz Phase noise at 100-kHz offset with 6.4-GHz carrier

- PLL figure of merit: -232 dBc/Hz

- PLL normalized 1/f noise: -123.5 dBc/Hz

- · 32-Bit Fractional-N divider

- Remove integer boundary spurs with programmable input multiplier

- Synchronization of output phase across multiple devices

- Support for JESD204B SYSREF with programmable delay

- Support for ramp and chirp functions

- Support for FSK direct digital modulation

- Two programmable output power level differential outputs

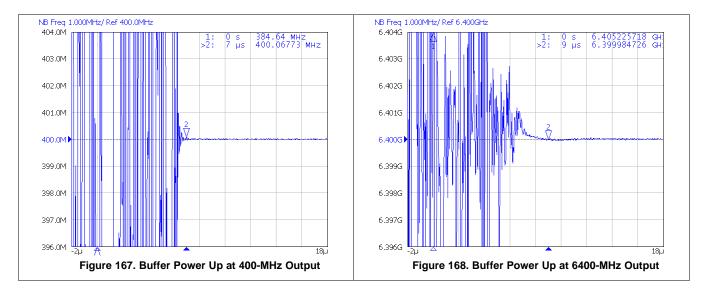

- Fast VCO calibration speed: < 20 μs</li>

- Single 3-V to 3.5-V power supply

# 2 Applications

- Test and measurement equipment

- Digital 2-way radios

- Low power radio communication systems

- Satellite communication

- · Wireless microphones

- · Propriety wireless connectivity

- MIMO

- RADAR

- High-speed data converter clocking

# 3 Description

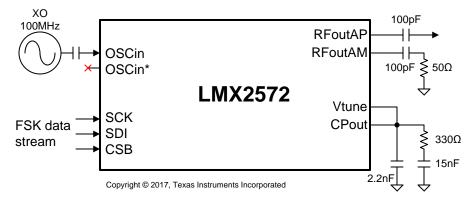

The LMX2572 is a low-power, high-performance wideband synthesizer that can generate any frequency from 12.5 MHz to 6.4 GHz without using an internal doubler. The PLL delivers excellent performance while consuming just 75 mA from a single 3.3-V supply.

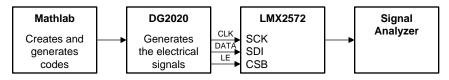

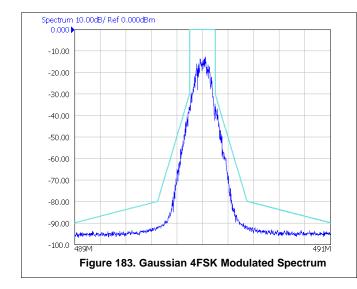

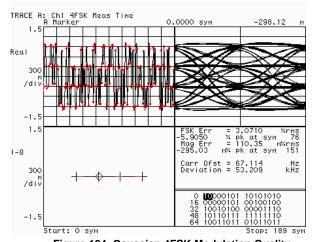

For applications like digital mobile radio (DMR) and wireless microphones, the LMX2572 supports FSK modulation. Discrete level FSK and pulse-shaping FSK are supported. Direct digital FSK modulation is achievable through programming or pins.

The LMX2572 allows users to synchronize the output of multiple devices and also enables applications that need deterministic delay between input and output. The LMX2572 provides an option to adjust the phase with fine granularity to account for delay mismatch on the board or within devices. A frequency ramp generator can synthesize up to two segments of ramp in an automatic ramp generation option or a manual option for maximum flexibility. The fast calibration algorithm allows the user to change frequencies faster than 20 µs. The LMX2572 also supports generating or repeating SYSREF (compliant to JESD204B standard) making it an ideal low-power, low-noise clock source for clocking high-speed data converters. Fine delay adjustment is provided in this configuration to account for delay differences of board

The LMX2572 integrates LDOs from a single 3.3-V supply, thus eliminating the need for onboard lownoise LDOs.

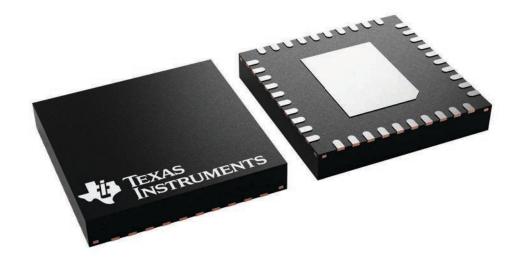

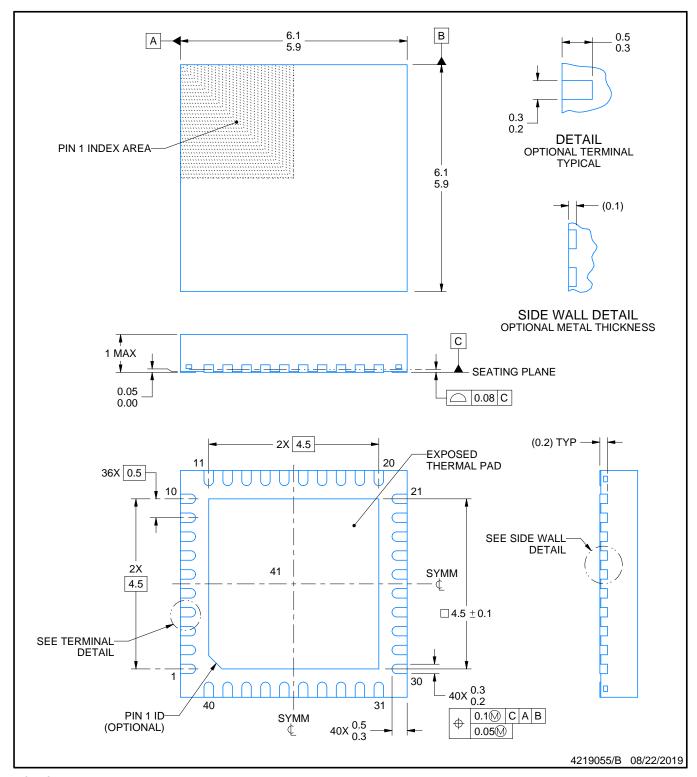

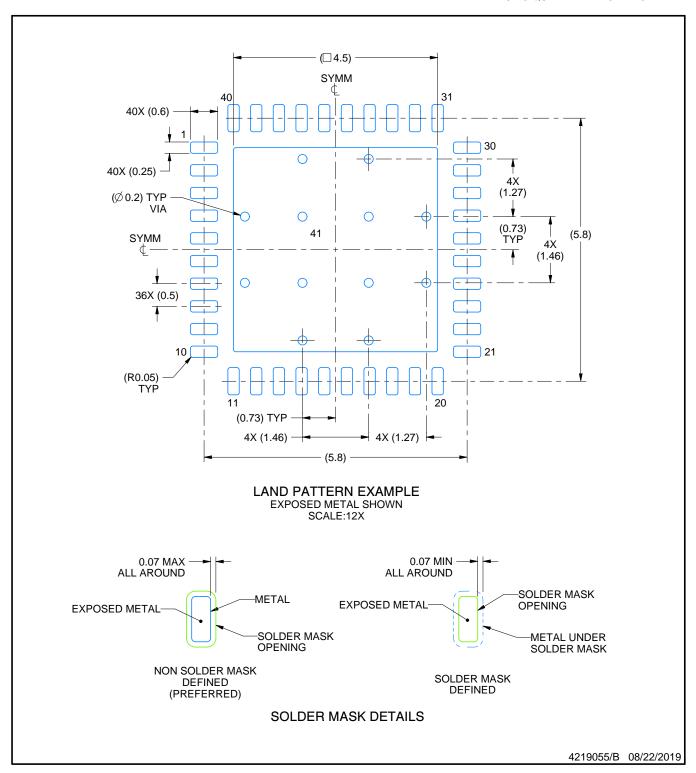

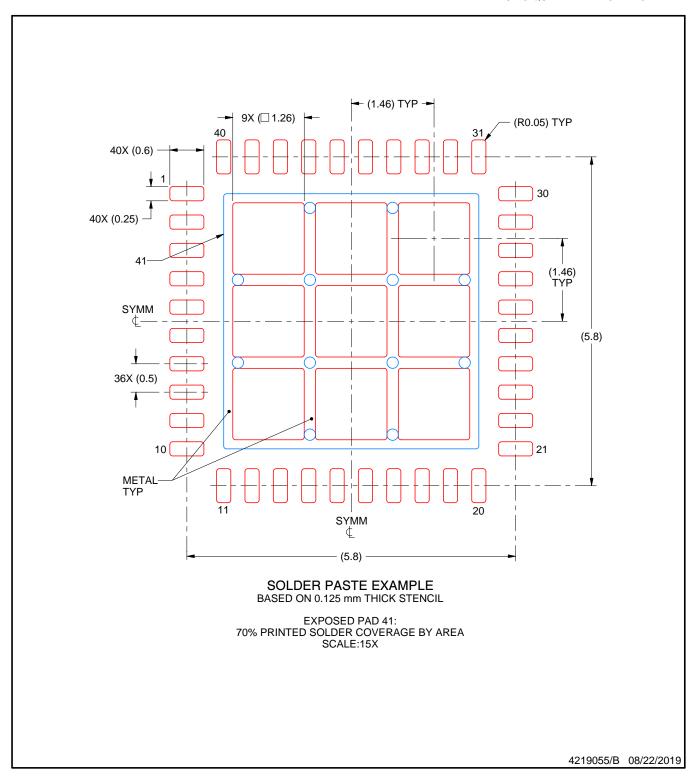

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| LMX2572     | VQFN (40) | 6.00 mm × 6.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

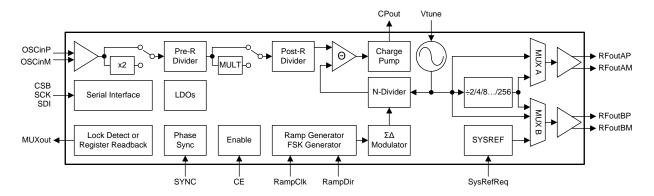

#### **Functional Block Diagram** CPout Vtune OSCinP Charge Θ ▶ RFoutAP OSCinM Divider 4MULT HO Divider Pump x2 ▶ RFoutAM CSB N-Divider -2/4/8 /256 LDOs Serial Interface SCK ▶ RFoutBP ▶ RFoutBM Lock Detect or Phase Ramp Generator ΣΔ MUXout ◀ Enable SYSREF Register Readback Sync **FSK Generator** Modulato SYNC ĊE RampClk RampDir SysRefReq

# **Table of Contents**

| 1 | Features 1                           |    | 7.5 Programming                                     | 2              |

|---|--------------------------------------|----|-----------------------------------------------------|----------------|

| 2 | Applications 1                       |    | 7.6 Register Maps                                   | 24             |

| 3 | Description 1                        | 8  | Application and Implementation                      | 64             |

| 4 | Revision History2                    |    | 8.1 Application Information                         | 64             |

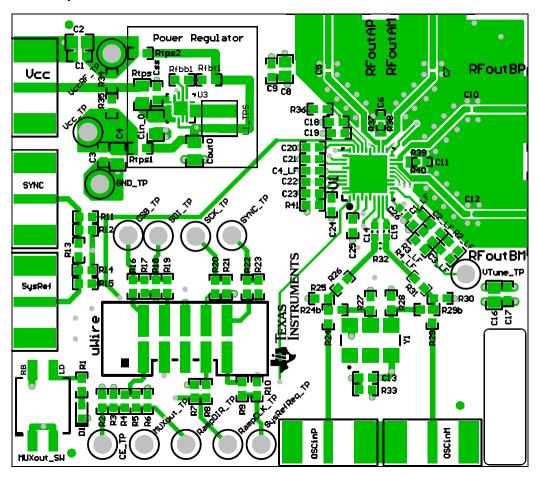

| 5 | Pin Configuration and Functions 4    |    | 8.2 Typical Application                             | 76             |

| 6 | Specifications5                      |    | 8.3 Do's and Don'ts                                 | 78             |

| U | 6.1 Absolute Maximum Ratings         | 9  | Power Supply Recommendations                        | 79             |

|   | 6.2 ESD Ratings                      | 10 | Layout                                              | 80             |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines                              | 80             |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example                                 | 80             |

|   | 6.5 Electrical Characteristics 6     | 11 | Device and Documentation Support                    | 8′             |

|   | 6.6 Timing Requirements 8            |    | 11.1 Device Support                                 | 8              |

|   | 6.7 Timing Diagrams                  |    | 11.2 Documentation Support                          | 8              |

|   | 6.8 Typical Characteristics          |    | 11.3 Receiving Notification of Documentation Update | es 8           |

| 7 | Detailed Description 15              |    | 11.4 Community Resources                            | 8              |

| • | 7.1 Overview                         |    | 11.5 Trademarks                                     | 8              |

|   | 7.2 Functional Block Diagram         |    | 11.6 Electrostatic Discharge Caution                | 8              |

|   | 7.3 Feature Description              |    | 11.7 Glossary                                       | 8              |

|   | 7.4 Device Functional Modes          |    | Mechanical, Packaging, and Orderable Information    | 8 <sup>.</sup> |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Revision A (October 2017) to Revision B                                                                                                                                                                                                                                                                        | Page |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed RampDir pin description from:ramp size selection to:ramp segment selection                                                                                                                                                                                                                                         | 4    |

| •  | Changed RFoutAM pin description from: High impedance to: Low impedance                                                                                                                                                                                                                                                     | 4    |

| •  | Changed RFoutAP pin description from: High impedance to: Low impedance                                                                                                                                                                                                                                                     | 4    |

| •  | Changed RFoutBM pin description from: High impedance to: Low impedance                                                                                                                                                                                                                                                     | 4    |

| •  | Changed RFoutBP pin description from: High impedance to: Low impedance                                                                                                                                                                                                                                                     | 4    |

| •  | Changed VbiasVCO pin decoupling capacitor requirement                                                                                                                                                                                                                                                                      | 5    |

| •  | Changed VbiasVCO2 pin decoupling capacitor requirement                                                                                                                                                                                                                                                                     | 5    |

| •  | Changed VccMASH pin decoupling capacitor requirement                                                                                                                                                                                                                                                                       | 5    |

| •  | Changed VccVCO pin decoupling capacitor requirement                                                                                                                                                                                                                                                                        | 5    |

| •  | Changed VccVCO2 pin decoupling capacitor requirement                                                                                                                                                                                                                                                                       | 5    |

| •  | Changed VregVCO pin decoupling capacitor requirement                                                                                                                                                                                                                                                                       | 5    |

| •  | Added Vtune pin shunt capacitor requirement                                                                                                                                                                                                                                                                                | 5    |

| •  | Changed V <sub>OH</sub> and V <sub>OL</sub> data in Electrical Characteristics                                                                                                                                                                                                                                             | 8    |

| •  | Changed SCK to CSB low time symbol                                                                                                                                                                                                                                                                                         | 8    |

| •  | Changed Figure 28                                                                                                                                                                                                                                                                                                          | 13   |

| •  | Added charge pump gain table                                                                                                                                                                                                                                                                                               | 16   |

| •  | Deleted sentence 'When the device comes out of the powered down state, either by resuming the POWERDOWN bit to zero or by pulling back CE pin HIGH (if it was powered down by CE pin), it is required that register R0 with FCAL_EN = 1 be programmed again to re-calibrate the device.' from the <i>Powerdown</i> section | 18   |

| •  | Added sentence 'The wake-up time for the device to come out of the powered state is adjustable.' to the  Powerdown section                                                                                                                                                                                                 |      |

| •  | Changed Programming Sequence step from: Wait 100 µs to: Wait 500 µs                                                                                                                                                                                                                                                        | 21   |

| •  | Changed R6 initial programming from: No to: Depends                                                                                                                                                                                                                                                                        | 21   |

| •  | Changed R52 initial programming from: No to: Yes                                                                                                                                                                                                                                                                           | 22   |

Submit Documentation Feedback

Copyright © 2017–2019, Texas Instruments Incorporated

# **Revision History (continued)**

| •        | Changed Advance Information to Production Data Release                                                                                                                                                                                                                                                                                                                                                                       | 1    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Cł       | nanges from Original (August 2017) to Revision A                                                                                                                                                                                                                                                                                                                                                                             | Page |

| <u>•</u> | Added an application section for powerup wake up time                                                                                                                                                                                                                                                                                                                                                                        | 75   |

| •        | Added an application section for external loop filter                                                                                                                                                                                                                                                                                                                                                                        |      |

| •        | Changed ADR_HOLD = 1 to ADD_HOLD = 1                                                                                                                                                                                                                                                                                                                                                                                         |      |

| •        | Deleted paragraph 'For ramping that are not calibration free, the ramp waveform is more like a staircase ramp. For all automatic ramping waveforms, be aware that there is a very small phase disturbance as the VCO crosses over the integer boundary, so one might consider using the input Multiplier to avoid these or timing the VCO calibration at integer boundaries.' from the <i>Automatic Ramping Mode</i> section |      |

| •        | Changed RAMP_THRESH value suggestion                                                                                                                                                                                                                                                                                                                                                                                         | 69   |

| •        | Changed RAMP_MODE = 1 to RAMP_MANUAL = 1 in the Manual Ramping Mode section                                                                                                                                                                                                                                                                                                                                                  |      |

| •        | Changed setup procedure step from:divide N to:set N = N' / 2                                                                                                                                                                                                                                                                                                                                                                 | 68   |

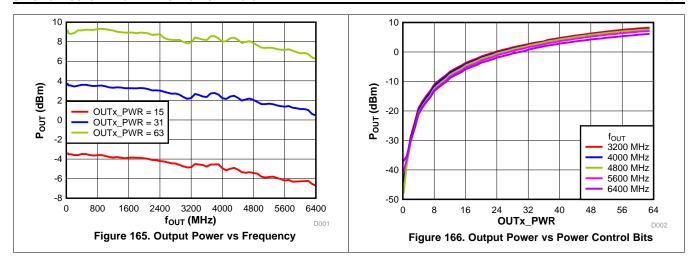

| •        | Changed Figure 165 and Figure 166                                                                                                                                                                                                                                                                                                                                                                                            | 65   |

| •        | Changed register R114, FSK_MODE_SEL value definition                                                                                                                                                                                                                                                                                                                                                                         | 61   |

| •        | Changed VCO_CAPCTRL_STRT reset value                                                                                                                                                                                                                                                                                                                                                                                         | 51   |

| •        | Changed from: MASH reset count to: This register                                                                                                                                                                                                                                                                                                                                                                             |      |

| •        | Changed register R58, INPIN_LVL value definition                                                                                                                                                                                                                                                                                                                                                                             |      |

| •        | Changed register R52 programming value                                                                                                                                                                                                                                                                                                                                                                                       |      |

| •        | Changed register R46, OUTB_MUX value definition                                                                                                                                                                                                                                                                                                                                                                              |      |

| •        | Deleted VCO_SEL_STRT_EN = 1 in Register 20 Field Descriptions                                                                                                                                                                                                                                                                                                                                                                |      |

| •        | Changed register R20 default value                                                                                                                                                                                                                                                                                                                                                                                           |      |

| •        | Changed R15[0] from: 1 to: 0                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| •        | Changed register R14 default value                                                                                                                                                                                                                                                                                                                                                                                           |      |

| •        | Changed MULT bit description from:30 MHz to:40 MHz                                                                                                                                                                                                                                                                                                                                                                           |      |

| •        | Added LDO_DLY in register R6                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| •        | Changed register R0, FCAL_HPFD_ADJ value definition                                                                                                                                                                                                                                                                                                                                                                          |      |

| •        | Changed R52[0] from: 0 to: 1                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| •        | Changed R20[14] from: 0 to: 1                                                                                                                                                                                                                                                                                                                                                                                                |      |

| •        | Changed R15 POR value                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| •        | Changed R15[0] from: 1 to: 0                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| •        | Added LDO_DLY in register R6                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

Submit Documentation Feedback

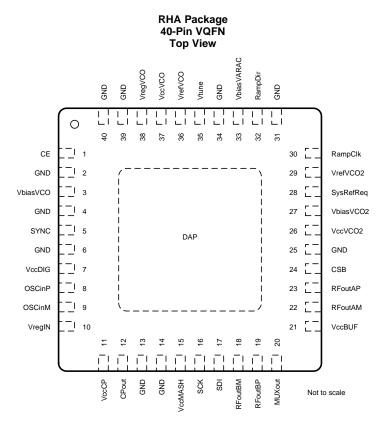

# 5 Pin Configuration and Functions

# **Pin Functions**

|         | PIN                     |        |                                                                                                                                           |  |

|---------|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO.                     | I/O    | DESCRIPTION                                                                                                                               |  |

| CE      | 1                       | Input  | Chip enable. High impedance CMOS input. 1.8-V to 3.3-V logic. Active HIGH powers on the device.                                           |  |

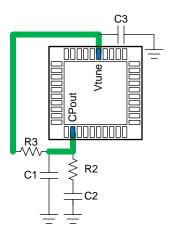

| CPout   | 12                      | Output | Charge pump output. Place C1 of loop filter close to this pin.                                                                            |  |

| CSB     | 24                      | Input  | SPI latch. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                               |  |

| DAP     | _                       | Ground | RF ground.                                                                                                                                |  |

|         | 2, 4, 25, 31,<br>34, 39 | Ground | VCO ground.                                                                                                                               |  |

| GND     | 6, 14, 40               | Ground | Digital ground.                                                                                                                           |  |

|         | 13                      | Ground | Charge pump ground.                                                                                                                       |  |

| MUXout  | 20                      | Output | Multiplexed output pin. Configurable between lock detect and register readback.                                                           |  |

| OSCinM  | 9                       | Input  | Reference input clock (–). High impedance self-biasing pin. Requires AC-coupling.                                                         |  |

| OSCinP  | 8                       | Input  | Reference input clock (+). High impedance self-biasing pin. Requires AC-coupling.                                                         |  |

| RampClk | 30                      | Input  | Ramp trigger in automatic ramping mode or ramp clock in manual ramping mode. High impedance CMOS input. 1.8-V to 3.3-V logic.             |  |

| RampDir | 32                      | Input  | Ramp trigger in automatic ramping mode or ramp segment selection in manual ramping mode. High impedance CMOS input. 1.8-V to 3.3-V logic. |  |

| RFoutAM | 22                      | Output | Differential output A (–). Low impedance output. Requires AC-coupling.                                                                    |  |

| RFoutAP | 23                      | Output | Differential output A (+). Low impedance output. Requires AC-coupling.                                                                    |  |

| RFoutBM | 18                      | Output | Differential output B (–). Low impedance output. Requires AC-coupling. Configurable between RF output or SYSREF output.                   |  |

| RFoutBP | 19                      | Output | Differential output B (+). Low impedance output. Requires AC-coupling. Configurable between RF output or SYSREF output.                   |  |

#### Pin Functions (continued)

| PIN I/O    |     | 1/0    | DECORPORTION                                                                                                              |  |

|------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO. | 1/0    | DESCRIPTION                                                                                                               |  |

| SCK        | 16  | Input  | SPI clock. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                               |  |

| SDI        | 17  | Input  | SPI data. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                |  |

| SYNC       | 5   | Input  | Phase synchronization trigger. Configurable to accept CMOS input (1.8-V to 3.3-V logic) or differential input.            |  |

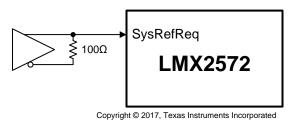

| SysRefReq  | 28  | Input  | SYSREF request for JESD204B support. Configurable to accept CMOS input (1.8-V to 3.3-V logic) or differential input.      |  |

| VbiasVARAC | 33  | Bypass | VCO Varactor bias. Connect a 10-μF decoupling capacitor to VCO ground.                                                    |  |

| VbiasVCO   | 3   | Bypass | VCO bias. Connect a 470-nF (X7R) decoupling capacitor to VCO ground as close to this pin as possible.                     |  |

| VbiasVCO2  | 27  | Bypass | VCO bias. Connect a 100-nF (X7R) decoupling capacitor to VCO ground.                                                      |  |

| VccBUF     | 21  | Supply | Supply for output buffers. Connect a 0.1-µF decoupling capacitor to RF ground.                                            |  |

| VccCP      | 11  | Supply | Supply for charge pump. Connect a 0.1-µF decoupling capacitor to charge pump ground.                                      |  |

| VccDIG     | 7   | Supply | Digital power supply. Connect a 0.1-µF decoupling capacitor to digital ground.                                            |  |

| VccMASH    | 15  | Supply | Digital power supply. Connect a 1-µF decoupling capacitor to digital ground.                                              |  |

| VccVCO     | 37  | Supply | Supply for VCO. Connect a 1-µF decoupling capacitor to VCO ground.                                                        |  |

| VccVCO2    | 26  | Supply | Supply for VCO. Connect a 1-µF decoupling capacitor to VCO ground.                                                        |  |

| VrefVCO    | 36  | Bypass | VCO supply reference. Connect a 10-µF decoupling capacitor to VCO ground.                                                 |  |

| VrefVCO2   | 29  | Bypass | VCO supply reference. Connect a 10-μF decoupling capacitor to VCO ground.                                                 |  |

| VregIN     | 10  | Bypass | Input reference path regulator output. Connect a 1-µF decoupling capacitor to RF ground as close to this pin as possible. |  |

| VregVCO    | 38  | Bypass | VCO regulator node. Connect a 10-nF decoupling capacitor to VCO ground.                                                   |  |

| Vtune      | 35  | Input  | VCO tuning voltage input. Connect a 1.5-nF or more capacitor to VCO ground. See <i>External Loop Filter</i> for details.  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                          | MIN  | MAX            | UNIT |

|------------------|--------------------------|------|----------------|------|

| $V_{CC}$         | Power supply voltage     | -0.3 | 3.6            | V    |

| $V_{IN}$         | Digital IO input voltage |      | $V_{CC} + 0.3$ | V    |

| TJ               | Junction temperature     |      | 150            | °C   |

| T <sub>stg</sub> | Storage temperature      | -65  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            |                                                                               |                                                                             | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|

| V                                          | Electrostatio discharge                                                       | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500                                                                        | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                      | MIN | NOM MAX | UNIT |

|----------------|----------------------|-----|---------|------|

| T <sub>A</sub> | Ambient temperature  | -40 | 85      | °C   |

| $T_{J}$        | Junction temperature |     | 125     | °C   |

# 6.4 Thermal Information

|                      |                                              | LMX2572    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHA (VQFN) | UNIT |

|                      |                                              | 40 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 25.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 14.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.0        | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.2        | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 7.9        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.2        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.5 Electrical Characteristics

$3.0 \text{ V} \le \text{V}_{CC} \le 3.5 \text{ V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{A} \le 85^{\circ}\text{C}$ . Typical values are at  $\text{V}_{CC} = 3.3 \text{ V}$ ,  $25^{\circ}\text{C}$  (unless otherwise noted)

|                      | PARAMETER                               | TEST CONDITION                                         | IS                           | MIN  | TYP  | MAX | UNIT    |  |

|----------------------|-----------------------------------------|--------------------------------------------------------|------------------------------|------|------|-----|---------|--|

| POWER S              | UPPLY                                   |                                                        |                              |      |      |     |         |  |

| V <sub>CC</sub>      | Supply voltage                          |                                                        |                              | 3    | 3.3  | 3.5 | V       |  |

|                      |                                         | f <sub>PD</sub> = 20 MHz; I <sub>CPout</sub> = 1.25 mA | Direct VCO                   |      | 75   |     |         |  |

|                      | Supply current                          | f <sub>PD</sub> = 100 MHz; I <sub>CPout</sub> = 2.5 mA | output <sup>(1)</sup>        |      | 79   |     |         |  |

| I <sub>CC</sub>      | Зирріу сипепі                           | f <sub>PD</sub> = 20 MHz; I <sub>CPout</sub> = 1.25 mA | Divided down                 |      | 82   |     | mA      |  |

|                      |                                         | f <sub>PD</sub> = 100 MHz; I <sub>CPout</sub> = 2.5 mA | output <sup>(2)</sup>        |      | 86   |     |         |  |

| I <sub>CC</sub> PD   | Power down current                      |                                                        |                              |      | 2.5  |     |         |  |

| INPUT SIG            | SNAL PATH                               |                                                        |                              |      |      |     |         |  |

| 4                    | OSCin input frequency                   | OSC_2X = 0 (Doubler bypassed)                          | )                            | 5    |      | 250 | NAL I-  |  |

| f <sub>OSCin</sub>   | OSCIII input frequency                  | OSC_2X = 1 (Doubler enabled)                           | OSC_2X = 1 (Doubler enabled) |      |      | 125 | MHz     |  |

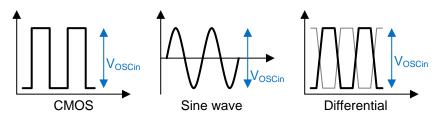

| \/                   | OSCin input voltage (3)                 | Single-ended input buffer                              |                              | 0.3  |      | 3.6 | V       |  |

| $V_{OSCin}$          | OSCIII input voitage V                  | Differential input buffer                              | Differential input buffer    |      |      | 1   |         |  |

| f <sub>MULTin</sub>  | Multiplier input frequency              | MULT ≥ 3                                               |                              | 10   |      | 40  | MHz     |  |

| f <sub>MULTout</sub> | Multiplier output frequency             | WOLT 23                                                |                              | 60   |      | 150 | IVII IZ |  |

| PLL                  |                                         |                                                        |                              |      |      |     |         |  |

|                      |                                         | Integer channel                                        |                              | 0.25 |      | 250 |         |  |

|                      | 51 (4)                                  | 1 <sup>st</sup> and 2 <sup>nd</sup> order modulator    |                              | 5    |      | 200 | MHz     |  |

| f <sub>PD</sub>      | Phase detector frequency <sup>(4)</sup> | 3 <sup>rd</sup> order modulator                        |                              | 5    |      | 160 |         |  |

|                      |                                         | 4 <sup>th</sup> order modulator                        |                              | 5    |      | 120 |         |  |

|                      |                                         | CPG = 1                                                |                              |      | 625  |     |         |  |

|                      |                                         | CPG = 2                                                |                              |      | 1250 |     |         |  |

| I <sub>CPout</sub>   | Charge pump current                     | CPG = 3                                                |                              |      | 1875 |     | μΑ      |  |

|                      |                                         |                                                        |                              |      |      |     |         |  |

|                      |                                         | CPG = 15 66                                            |                              | 6875 |      |     |         |  |

$<sup>\</sup>begin{aligned} &f_{OSCin} = 100 \text{ MHz; } f_{VCO} = f_{OUT} = 6.4 \text{ GHz; } P_{OUT} = 0 \text{ dBm; } OSC\_2X = 0; \text{ MULT} = 1; \text{ one RF output.} \\ &f_{OSCin} = 100 \text{ MHz; } f_{VCO} = 6.4 \text{ GHz; } f_{OUT} = 3.2 \text{ GHz; } P_{OUT} = 0 \text{ dBm; } OSC\_2X = 0; \text{ MULT} = 1; \text{ one RF output.} \\ &See \underbrace{OSCin}_{Configuration} \text{ for definition of OSCin input voltage.} \end{aligned}$

For lower VCO frequencies, the N-divider minimum value can limit the phase detector frequency. (4)

# **Electrical Characteristics (continued)**

3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  3.5 V,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85 $^{\circ}$ C. Typical values are at V<sub>CC</sub> = 3.3 V, 25 $^{\circ}$ C (unless otherwise noted)

|                        | PARAMETER                                  | TEST CONDITION                                                                        | IS                          | MIN TYP | MAX  | UNIT   |

|------------------------|--------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|---------|------|--------|

| PN <sub>PLL_1/f</sub>  | Normalized PLL 1/f noise <sup>(5)</sup>    |                                                                                       |                             | -123.5  |      |        |

|                        | Namedia d DLL maio floor(5)                | Integer channel <sup>(6)</sup>                                                        |                             | -232    |      | dBc/Hz |

| PN <sub>PLL_Flat</sub> | Normalized PLL noise floor (5)             | Fractional channel (7)                                                                |                             | -232    |      |        |

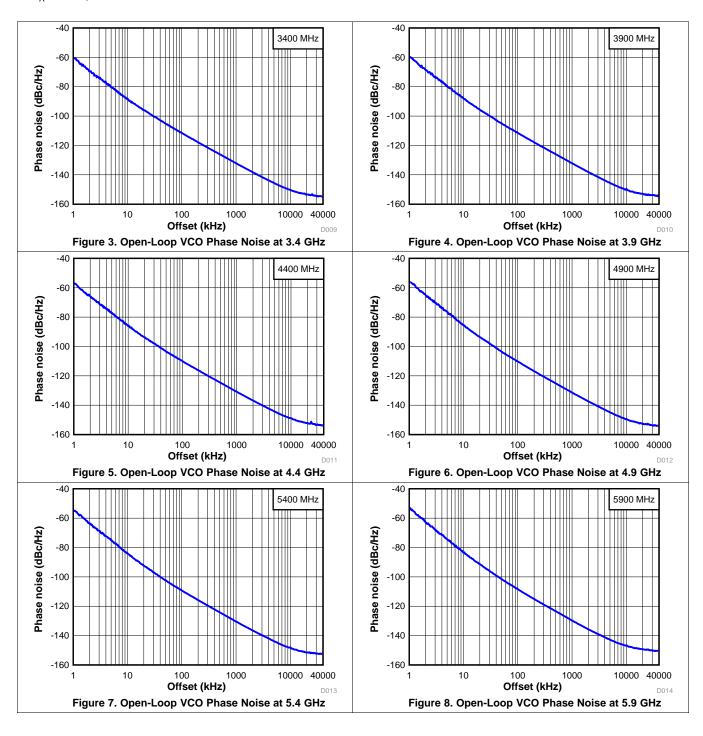

| vco                    |                                            |                                                                                       |                             |         |      |        |

| f <sub>VCO</sub>       | VCO frequency                              |                                                                                       |                             | 3200    | 6400 | MHz    |

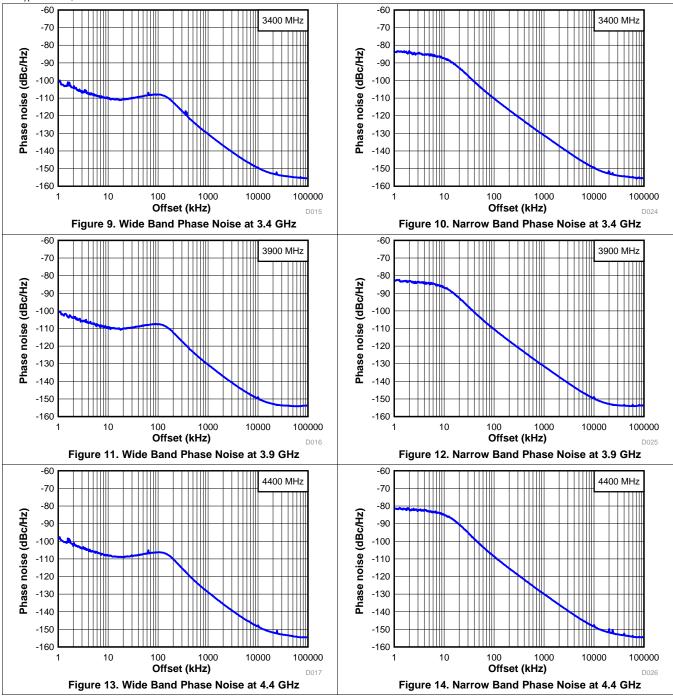

|                        |                                            |                                                                                       | 10 kHz                      | -88     |      |        |

|                        |                                            | 4 24015                                                                               | 100 kHz                     | -111    |      |        |

| PN <sub>VCO</sub> C    |                                            | $f_{VCO} = 3.4 \text{ GHz}$                                                           | 1 MHz                       | -131    |      |        |

|                        |                                            |                                                                                       | 10 MHz                      | -150    |      |        |

|                        |                                            | £ 20 CH-                                                                              | 10 kHz                      | -87.5   |      |        |

|                        |                                            |                                                                                       | 100 kHz                     | -111    |      |        |

|                        |                                            | $f_{VCO} = 3.9 \text{ GHz}$                                                           | 1 MHz                       | -131.5  |      |        |

|                        |                                            |                                                                                       | 10 MHz                      | -150    |      |        |

|                        |                                            | f <sub>VCO</sub> = 4.4 GHz                                                            | 10 kHz                      | -86.5   |      |        |

|                        | Open loop VCO phase noise                  |                                                                                       | 100 kHz                     | -111    |      | dBc/Hz |

|                        |                                            |                                                                                       | 1 MHz                       | -131    |      |        |

|                        |                                            |                                                                                       | 10 MHz                      | -150    |      |        |

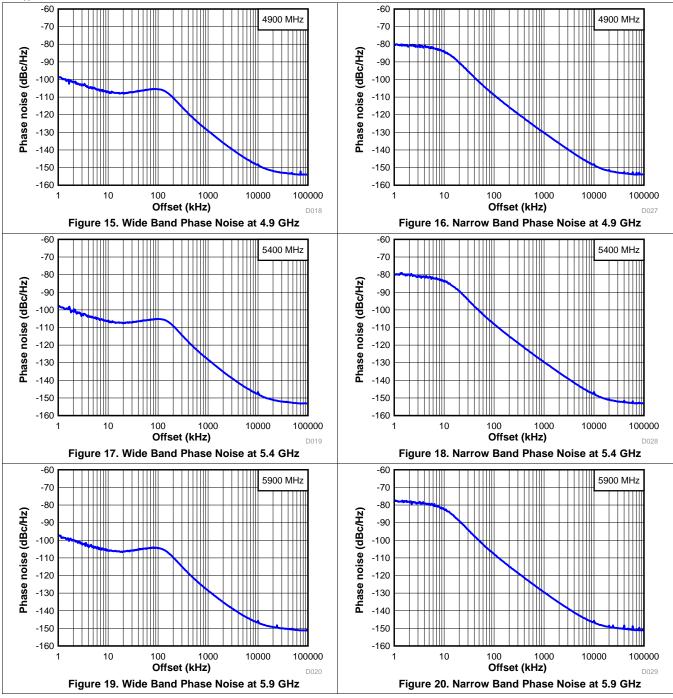

|                        |                                            | f <sub>VCO</sub> = 4.9 GHz                                                            | 10 kHz                      | -85     |      |        |

|                        |                                            |                                                                                       | 100 kHz                     | -110    |      |        |

|                        |                                            |                                                                                       | 1 MHz                       | -130.5  |      |        |

|                        |                                            |                                                                                       | 10 MHz                      | -149.5  |      |        |

|                        |                                            | f <sub>VCO</sub> = 5.4 GHz                                                            | 10 kHz                      | -84.5   |      |        |

|                        |                                            |                                                                                       | 100 kHz                     | -109    |      |        |

|                        |                                            |                                                                                       | 1 MHz                       | -129.5  |      |        |

|                        |                                            |                                                                                       | 10 MHz                      | -149    |      |        |

|                        |                                            | ( 50 QU-                                                                              | 10 kHz                      | -84     |      |        |

|                        |                                            |                                                                                       | 100 kHz                     | -108.5  |      |        |

|                        |                                            | $f_{VCO} = 5.9 \text{ GHz}$                                                           | 1 MHz                       | -129    |      |        |

|                        |                                            |                                                                                       | 10 MHz                      | -148    |      |        |

|                        |                                            | f <sub>VCO</sub> = 3.4 GHz                                                            |                             | 39      |      |        |

|                        |                                            | f <sub>VCO</sub> = 3.9 GHz                                                            |                             | 44      |      |        |

| <b>K</b>               | VCO gain                                   | f <sub>VCO</sub> = 4.4 GHz                                                            |                             | 55      |      | MU-A   |

| K <sub>VCO</sub>       | VCO gain                                   | f <sub>VCO</sub> = 4.9 GHz                                                            |                             | 60      |      | MHz/V  |

|                        |                                            | f <sub>VCO</sub> = 5.4 GHz                                                            |                             | 69      |      |        |

|                        |                                            | f <sub>VCO</sub> = 5.9 GHz                                                            |                             | 62      |      |        |

|                        |                                            |                                                                                       | No assist                   | 130     |      |        |

| t <sub>VCOcal</sub>    | VCO calibration-time (8)                   | f <sub>OSCin</sub> = f <sub>PD</sub> = 100 MHz; Switch<br>between 3.2 GHz and 6.4 GHz | Partial assist              | 50      |      | μs     |

|                        |                                            | 55.770011 5.2 Of 12 and 0.4 Of 12                                                     | Full assist                 | 5       |      |        |

| Δ <sub>TCL</sub>       | Allowable temperature drift <sup>(9)</sup> | VCO not being re-calibrated, -40                                                      | 0°C ≤ T <sub>A</sub> ≤ 85°C |         | 125  | °C     |

<sup>(5)</sup> Measured with a clean OSCin signal with a high slew rate using a wide loop bandwidth. The noise metrics model the PLL noise for an infinite loop bandwidth as: PLL\_Total = 10\*log[10<sup>(PLL\_Flat/10)</sup>+10<sup>(PLL\_Flicker/10)</sup>]; PLL\_Flat = PN1 Hz + 20\*log(N) + 10\*log(f<sub>PD</sub>); PLL\_Flicker = PN10 kHz - 10\*log(Offset/10 kHz) + 20\*log(f<sub>OUT</sub>/1 GHz)

$f_{OSCin} = 200 \text{ MHz; } f_{PD} = 100 \text{ MHz; } f_{VCO} = f_{OUT} = 6 \text{ GHz}$   $f_{OSCin} = 200 \text{ MHz; } f_{PD} = 100 \text{ MHz; } f_{VCO} = f_{OUT} = 6.001 \text{ GHz; } Fractional denominator = 1000.$ (7)

See VCO Calibration for details.

Not tested in production. Ensured by characterization. Allowable temperature drift refers to programming the device at an initial temperature and allowing this temperature to drift WITHOUT reprogramming the device, and still have the device stay at lock. This change could be up or down in temperature and the specification does not apply to temperatures that go outside the recommended operating temperatures of the device.

# **Electrical Characteristics (continued)**

$3.0 \text{ V} \le \text{V}_{\text{CC}} \le 3.5 \text{ V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$ . Typical values are at  $\text{V}_{\text{CC}} = 3.3 \text{ V}$ ,  $25^{\circ}\text{C}$  (unless otherwise noted)

|                         | PARAMETER                  | TEST CONDITION                                                                       | S                | MIN                   | TYP | MAX      | UNIT   |

|-------------------------|----------------------------|--------------------------------------------------------------------------------------|------------------|-----------------------|-----|----------|--------|

| RF OUTPUT               |                            |                                                                                      |                  |                       |     |          |        |

| f <sub>OUT</sub>        | RF output frequency        |                                                                                      |                  | 12.5                  |     | 6400     | MHz    |

| P <sub>OUT</sub>        | Single-ended output power  | $f_{OUT} = 6.4GHz$                                                                   |                  |                       | 4.5 |          | dBm    |

| Un                      | Second harmonic            | $f_{VCO} = f_{OUT} = 6.4 \text{ GHz}$                                                |                  |                       | -20 |          |        |

| H2 <sub>OUT</sub>       | Second narmonic            | $f_{VCO} = 6.4 \text{ GHz}, f_{OUT} = 3.2 \text{ GHz}$                               | OUTx_PWR<br>= 50 |                       | -37 |          | dBc    |

| Пэ                      | Third harmonic             | $f_{VCO} = f_{OUT} = 6.4 \text{ GHz}$                                                |                  |                       | -25 |          | UDC    |

| H3 <sub>OUT</sub>       | Third narmonic             | $f_{VCO} = 6.4 \text{ GHz}, f_{OUT} = 3.2 \text{ GHz}$                               |                  |                       | -13 |          |        |

| t <sub>skew</sub> CH    | Channel to channel skew    | f <sub>OUT</sub> = 3.2 GHz                                                           |                  |                       | 14  |          | ps     |

| PHASE SYN               | CHRONIZATION               |                                                                                      |                  |                       |     |          |        |

| f CVNC                  | OSCin input frequency with | Category 3                                                                           |                  | 5                     |     | 100      | MHz    |

| f <sub>OSCin</sub> SYNC | SYNC                       | Categories 1 and 2                                                                   |                  | 5                     |     | 200      | IVITIZ |

| t <sub>skew</sub> SYNC  | OSCin to RFout skew        | After phase synchronization;<br>f <sub>OSCin</sub> SYNC = f <sub>OUT</sub> = 100 MHz |                  |                       | 2   |          | ns     |

| DIGITAL INT             | ERFACE                     | •                                                                                    |                  | •                     |     | ·        |        |

| V <sub>IH</sub>         | High-level input voltage   |                                                                                      |                  | 1.4                   |     | $V_{CC}$ | V      |

| V <sub>IL</sub>         | Low-level input voltage    |                                                                                      |                  |                       |     | 0.4      | V      |

| I <sub>IH</sub>         | High-level input current   |                                                                                      |                  | -25                   |     | 25       |        |

| I <sub>IL</sub>         | Low-level input current    |                                                                                      |                  | -25                   |     | 25       | μA     |

| V <sub>OH</sub>         | High-level output voltage  | Load current = -5 mA                                                                 | MI IVout nin     | V <sub>CC</sub> - 0.5 |     |          | V      |

| V <sub>OL</sub>         | Low-level output voltage   | Load current = 5 mA                                                                  | MUXout pin       |                       |     | 0.5      | V      |

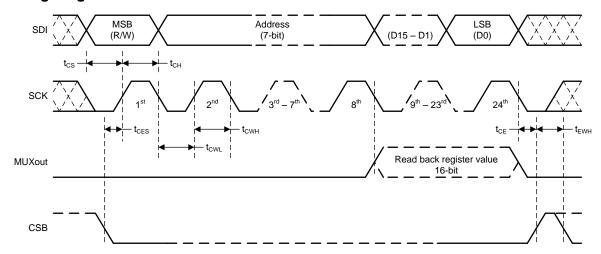

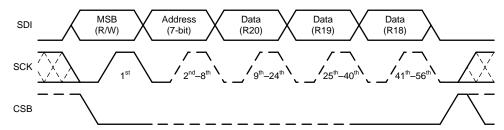

# 6.6 Timing Requirements

$3.0 \text{ V} \le V_{CC} \le 3.5 \text{ V}, -40 ^{\circ}\text{C} \le T_{A} \le 85 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = 3.3 \text{ V}, 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                  |                         |                                            | MIN | NOM | MAX | UNIT |

|------------------|-------------------------|--------------------------------------------|-----|-----|-----|------|

| SERIA            | INTERFACE WRITE TIMING  | -                                          |     |     |     |      |

| f <sub>SCK</sub> | SCK frequency           | 1 / (t <sub>CWL</sub> + t <sub>CWH</sub> ) |     |     | 75  | MHz  |

| t <sub>CE</sub>  | SCK to CSB low time     |                                            | 5   |     |     | ns   |

| t <sub>CS</sub>  | SDI to SCK setup time   |                                            | 2   |     |     | ns   |

| t <sub>CH</sub>  | SDI to SCK hold time    |                                            | 2   |     |     | ns   |

| t <sub>CWH</sub> | SCK pulse width high    | Figure 1                                   | 5   |     |     | ns   |

| t <sub>CWL</sub> | SCK pulse width low     |                                            | 5   |     |     | ns   |

| t <sub>CES</sub> | CSB to SCK setup time   |                                            | 5   |     |     | ns   |

| t <sub>EWH</sub> | CSB pulse width high    |                                            | 2   |     |     | ns   |

| SERIAI           | L INTERFACE READ TIMING |                                            |     |     |     |      |

| $f_{SCK}$        | SCK frequency           | 1 / (t <sub>CWL</sub> + t <sub>CWH</sub> ) |     |     | 50  | MHz  |

| t <sub>CE</sub>  | SCK to CSB low time     |                                            | 10  |     |     | ns   |

| t <sub>CS</sub>  | SDI to SCK setup time   |                                            | 10  |     |     | ns   |

| t <sub>CH</sub>  | SDI to SCK hold time    |                                            | 10  |     |     | ns   |

| t <sub>CWH</sub> | SCK pulse width high    | Figure 1                                   | 10  |     |     | ns   |

| t <sub>CWL</sub> | SCK pulse width low     |                                            | 10  |     |     | ns   |

| t <sub>CES</sub> | CSB to SCK setup time   |                                            | 10  |     |     | ns   |

| t <sub>EWH</sub> | CSB pulse width high    |                                            | 10  |     |     | ns   |

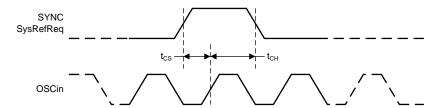

| SYNC             | AND SYSREFREQ TIMING    |                                            |     | ·   |     |      |

| t <sub>CS</sub>  | Pin to OSCin setup time | Figure 2                                   | 2.5 |     |     | ns   |

| t <sub>CH</sub>  | Pin to OSCin hold time  | Figure 2                                   | 2   |     |     | ns   |

# 6.7 Timing Diagrams

Figure 1. Serial Interface Timing Diagram

Figure 2. Trigger Signals Timing Diagram

Copyright © 2017–2019, Texas Instruments Incorporated

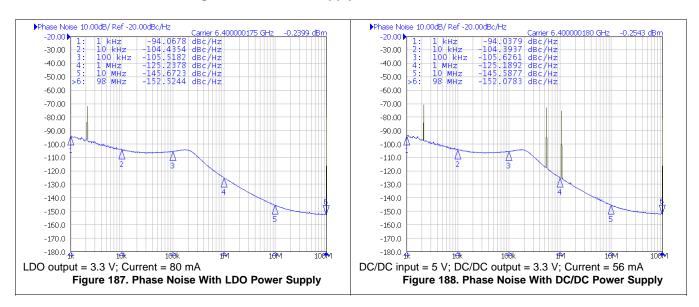

# 6.8 Typical Characteristics

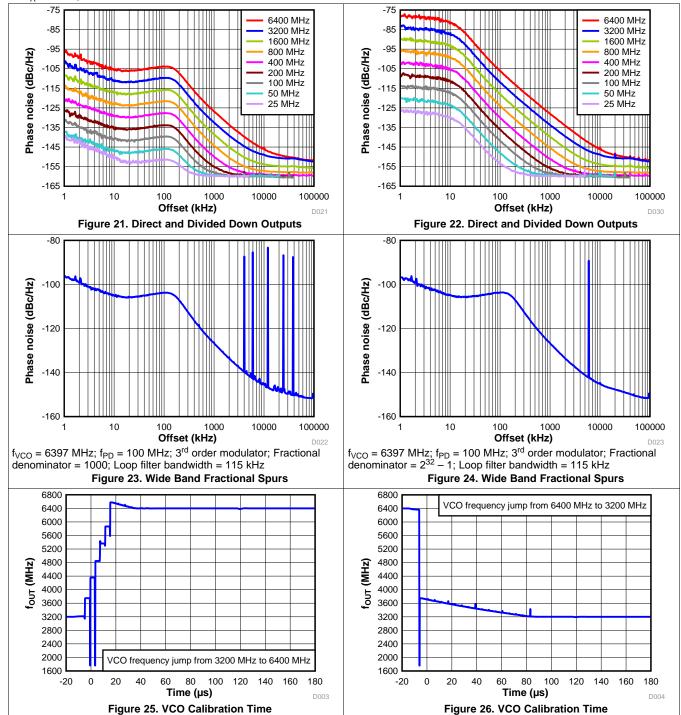

At  $T_A = 25$ °C, unless otherwise noted

At  $T_A = 25$ °C, unless otherwise noted

Copyright © 2017–2019, Texas Instruments Incorporated

At  $T_A = 25$ °C, unless otherwise noted

Submit Documentation Feedback

Copyright © 2017–2019, Texas Instruments Incorporated

At  $T_A = 25$ °C, unless otherwise noted

Copyright © 2017–2019, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

The LMX2572 is a low-power, high-performance, wideband frequency synthesizer with integrated VCO and output divider. The VCO operates from 3.2 to 6.4 GHz, and this can be combined with the output divider to produce any frequency in the range of 12.5 MHz to 6.4 GHz. Within the input path, there are two dividers and a multiplier for flexible frequency planning. The multiplier also allows reduction of spurs by moving the frequencies away from the integer boundary.

The PLL is a fractional-N PLL with a programmable delta-sigma modulator up to 4<sup>th</sup> order. The fractional denominator is a programmable 32-bit long that can supply fine frequency steps easily below the 1-Hz resolution. The denominator can also be used to do exact fractions like 1/3, 7/1000, and many others.

For applications where deterministic or adjustable phase is desired, the SYNC pin can be used to get the phase relationship between the OSCin and RFout pins deterministic. Once this is done, the phase can be adjusted in very fine steps of the VCO period divided by the fractional denominator.

The ultra-fast VCO calibration is ideal for applications where the frequency must be swept or abruptly changed. The frequency can be manually programmed, or the device can be set up to do ramps and chirps.

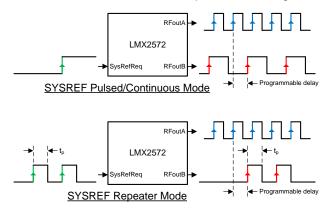

The JESD204B support includes using the RFoutB output to create a differential SYSREF output that can be either a single pulse, series of pulse, or a continuous stream of pulses. These pulses are synchronous with the RFoutA signal with an adjustable delay.

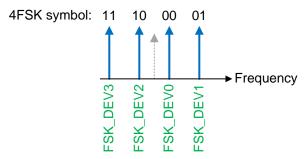

The FSK generator can support FSK generation in discrete 2-, 4-, or 8-level FSK, or it can any arbitrary level FSK making it ideal to support pulse-shaped FSK modulation such as GFSK.

The LMX2572 device requires only a single 3.3-V power supply and uses very low current. The internal power supplies are provided by integrated LDOs, eliminating the need for high performance external LDOs.

Digital logic interface is compatible with 1.8-V input. The user can program the device through the serial interface. The device can be powered down through register programming or by toggling the Chip Enable (CE) pin.

## 7.2 Functional Block Diagram

# 7.3 Feature Description

#### 7.3.1 Reference Oscillator Input

The OSCin pins are used as a frequency reference input to the device. The input is high impedance and requires AC-coupling capacitors at the pin. The OSCin pins can be driven single-ended with a CMOS clock, XO, or single-ended differential clock. Differential clock input is also supported, which makes the device easier to interface with high-performance system clock devices such as TI's LMK series clock devices. As the OSCin signal is used as a clock for the VCO calibration, a proper reference signal must be applied at the OSCin pin at the time of programming FCAL EN.

## **Feature Description (continued)**

#### 7.3.2 Reference Path

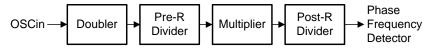

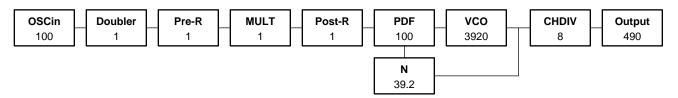

The reference path consists of an OSCin doubler (OSC\_2X), Pre-R divider (PLL\_R\_PRE), Multiplier (MULT), and a Post-R divider (PLL\_R).

Figure 31. Reference Path

The Doubler allows one to double the input reference frequency up to 250 MHz. The Doubler adds minimal noise and is useful for raising the phase detector frequency for better phase noise. The Doubler can also be used to avoid spurs. The Doubler uses both the rising and falling edges of the input signal, so the input signal must have 50% duty cycle if the Doubler is enabled. Note that the Multiplier cannot be used if the Doubler is engaged.

The Pre-R divider can help reduce input frequency so that the Multiplier can be used and the maximum 200-MHz input frequency limitation of the Post-R divider can be met.

The Multiplier multiplies the frequency up under the allowable multiplications of 3, 4, 5, 6, and 7. In combination with the Pre-R and Post-R dividers, the Multiplier offers the flexibility to shift the phase detector frequency away from frequencies that may create integer boundary spurs with the VCO and the output frequencies. Be aware that unlike the Doubler, the Multiplier degrades the PLL figure of merit. This degradation would only matter, however, for a very clean reference oscillator input and if the loop bandwidth was wide. The user should not use the Doubler while using the Multiplier. The Multiplier is bypassed if its value is set to 1.

The Post-R divider can be used to further divide down the frequency to the phase detector frequency. When it is used (PLL\_R > 1), the input frequency to this divider is limited to 200 MHz.

Use Equation 1 to calculate the phase detector frequency, f<sub>PD</sub>.

$$f_{PD} = f_{OSCin} \times OSC_2X \times MULT / (PLL_R_PRE \times PLL_R)$$

(1)

Table 1 summarizes the usage boundaries of these functional blocks in the reference path.

**Table 1. Reference Path Boundaries**

| PARAMETER      | VALUE                         | INF<br>FREQI<br>(M |     | FREQ | TPUT<br>UENCY<br>Hz) | NOTES                                                              |

|----------------|-------------------------------|--------------------|-----|------|----------------------|--------------------------------------------------------------------|

|                |                               | MIN                | MAX | MIN  | MAX                  |                                                                    |

| OSCin          | N/A                           | 5                  | 250 |      |                      |                                                                    |

| Doubler        | 0 (Bypassed), 1 (x2)          | 5                  | 125 | 10   | 250                  | When OSC_2X = 1, Multiplier cannot be used at the same time.       |

| Pre-R divider  | 1 (Bypassed), 2, 3,, 254, 255 | 5                  | 200 | 0.25 | 200                  | Keep it equals 1 unless when necessary.                            |

| Multiplier     | 1 (Bypassed), 3, 4, 5, 6, 7   | 10                 | 40  | 60   | 150                  | When the output frequency is greater than 100MHz, set MULT_HI = 1. |

| Post-R divider | 1 (Bypass), 2, 3,, 254, 255   | 5                  | 200 | 0.25 | 200                  |                                                                    |

## 7.3.3 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the Post-R divider and N divider and generates a correction current corresponding to the phase error until the two signals are aligned in phase. This charge-pump current is software programmable to many different levels, allowing modification of the closed-loop bandwidth of the PLL.

**Table 2. Charge Pump Gain**

| CGP  | 0         | 1   | 2    | 3    | 4 or 8 | 5 or 9 | 6 or 10 | 7 or 11 | 12   | 13   | 14   | 15   | UNIT |

|------|-----------|-----|------|------|--------|--------|---------|---------|------|------|------|------|------|

| Gain | Tri-state | 625 | 1250 | 1875 | 2500   | 3125   | 3750    | 4375    | 5000 | 5625 | 6250 | 6875 | μA   |

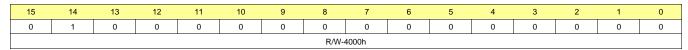

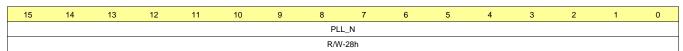

#### 7.3.4 PLL N Divider and Fractional Circuitry

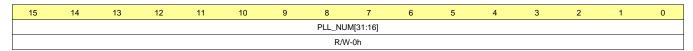

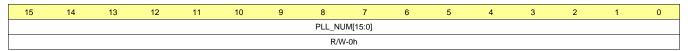

The N divider includes fractional compensation and can achieve any fractional denominator (PLL\_DEN) from 1 to  $(2^{32}-1)$ . The integer portion of N (PLL\_N) is the whole part of the N divider value, and the fractional portion,  $N_{frac} = PLL_NUM / PLL_DEN$ , is the remaining fraction. PLL\_N, PLL\_NUM and PLL\_DEN are software programmable. The higher the denominator, the finer the resolution step of the output. For example, even when using  $f_{PD} = 200$  MHz, the output can increment in steps of 200 MHz /  $(2^{32}-1) = 0.0466$  Hz. Equation 2 shows the relationship between the phase detector and VCO frequencies. Note that in SYNC mode, there is an extra divider that is not shown in Equation 2.

$$f_{VCO} = f_{PD} \times [PLL_N + (PLL_NUM / PLL_DEN)]$$

(2)

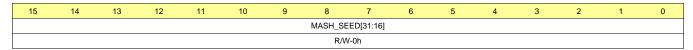

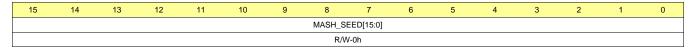

The multi-stage noise-shaping (MASH) sigma-delta modulator that controls the fractional division is also programmable from integer mode to fourth order. All of these settings work for integer channel where PLL\_NUM = 0. To make the fractional spurs consistent, the modulator is reset any time that the R0 register is programmed.

The N divider has minimum value restrictions based on the modulator order. Furthermore, the PFD\_DLY\_SEL bit must be programmed in accordance to Table 3.

| VCO                       |    |             |     |             | MA  | ASH ORDER   |    |             |     |             |

|---------------------------|----|-------------|-----|-------------|-----|-------------|----|-------------|-----|-------------|

| FREQUENCY                 |    | INTEGER     | FII | RST ORDER   | SEC | OND ORDER   | TH | IRD ORDER   | FOL | JRTH ORDER  |

| (GHz)                     | N  | PFD_DLY_SEL | N   | PFD_DLY_SEL | N   | PFD_DLY_SEL | N  | PFD_DLY_SEL | N   | PFD_DLY_SEL |

| f <sub>VCO</sub> < 4      | 20 | 0           | 25  | 1           | 26  | 1           | 32 | 2           | 44  | 4           |

| $4 \le f_{VCO} < 4.9$     | 24 | 1           | 29  | 2           | 30  | 2           | 32 | 2           | 44  | 4           |

| $4.9 \le f_{VCO} \le 6.4$ | 24 | 1           | 29  | 2           | 30  | 2           | 36 | 3           | 48  | 5           |

**Table 3. Minimum N Divider Restrictions**

#### 7.3.5 Voltage-Controlled Oscillator

The LMX2572 includes a fully integrated VCO. The VCO generates a frequency which varies with the tuning voltage from the loop filter. The entire VCO frequency range, 3.2 to 6.4 GHz, covers an octave that allows the channel divider to take care of frequencies below the lower bound.

To reduce the VCO tuning gain, thus improving the VCO phase noise performance, the VCO frequency range is divided into 6 different frequency bands. This creates the need for frequency calibration to determine the correct frequency band given in a desired output frequency. The VCO is also calibrated for amplitude to optimize phase noise. These calibration routines are activated any time that the R0 register is programmed with the FCAL\_EN bit equals one. It is important that a valid OSCin signal must present before VCO calibration begins. This device will support a full sweep of the valid temperature range of 125°C (–40°C to 85°C) without having to re-calibrate the VCO. This is important for continuous operation of the synthesizer under the most extreme temperature variation.

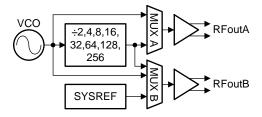

#### 7.3.6 Channel Divider

To go below the VCO lower bound of 3.2 GHz, the channel divider can be used. The channel divider consists of several segments, and the total division value is equal to the multiplication of them. Therefore, not all values are valid.

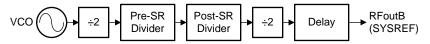

Figure 32. Channel Divider

The channel divider is automatically powered up whenever the MUXs have selected divided down output or SYSREF output, regardless of whether the RF output buffers are turned on or not. When an output is not used, TI recommends selecting the VCO output (OUTx\_MUX = 1) to ensure that the channel divider is not unnecessarily powered up.

#### Table 4. Channel Divider

| OUTA_MUX                  | OUTB_MUX                                      | CHANNEL DIVIDER |

|---------------------------|-----------------------------------------------|-----------------|

| 0: Channel divider output | Don't care                                    |                 |

| Don't care                | 0: Channel divider output<br>2: SYSREF output | Powered up      |

| All other                 | r cases                                       | Powered down    |

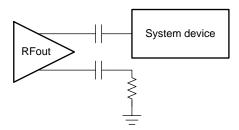

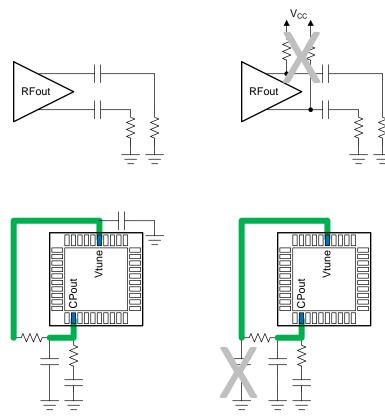

#### 7.3.7 Output Buffer

The output buffers are differential push-pull type buffers, thus no external pullup to  $V_{CC}$  is required. The output impedance of the buffer is very small, and as such, the buffer can be AC-coupled to drive a 50- $\Omega$  load. Output power of the buffer can be programed to various levels. The buffer can be disabled while still keeping the PLL in lock. Buffer A supports direct VCO output or divided down output. Buffer B supports direct VCO output, divided down output or SYSREF output.

#### 7.3.8 Lock Detect

The MUXout pin can be configured to output a signal that gives an indication for the PLL being locked. If the MUXout pin is configured as a lock detect output (MUXOUT\_LD\_SEL = 1), the MUXout pin output is a logic HIGH voltage when the device is locked. When the device is unlocked, the MUXout pin output is a logic LOW voltage.

There are options to select the definition of PLL being locked. If LD\_TYPE = 0, lock detect asserts a HIGH output after the VCO has finished calibration and the LD\_DLY timeout counter is finished. If LD\_TYPE = 1, in addition to the VCO calibration and counter check, lock detect will assert a HIGH output if the VCO tuning voltage is also within an acceptable limits.

#### 7.3.9 Register Readback

The MUXout pin can also be configured to read back useful information from the device. Common uses for readback are:

- Read back registers to ensure that they have been programmed to the correct value. LMX2572 allows any of its registers to be read back.

- · Read back the lock detect status to determine if the PLL is in lock.

- Read back VCO calibration information so that it can be used to improve the lock time.

#### 7.3.10 Powerdown

The LMX2572 can be powered up and down using the CE pin or the POWERDOWN bit. All registers are preserved in memory while the device is powered down.

The wake-up time for the device to come out of the powered state is adjustable. See Power-Up, Wake-Up Time for details.

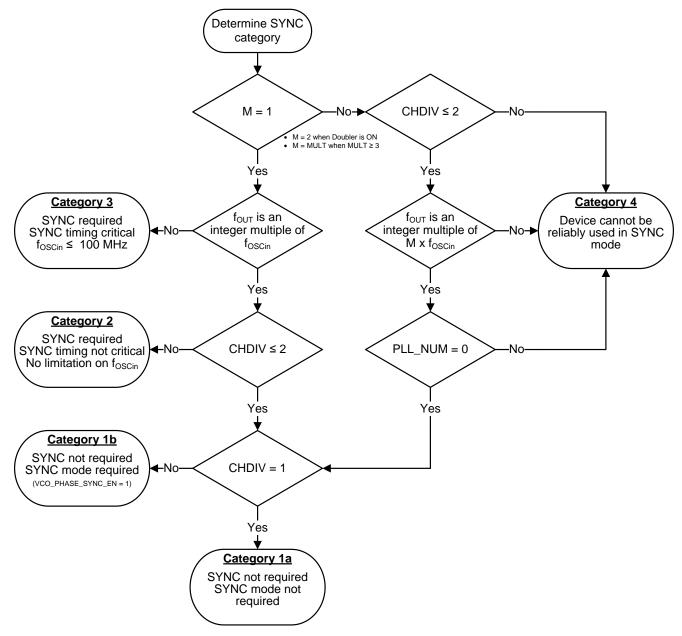

#### 7.3.11 Phase Synchronization

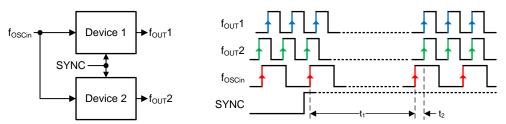

The SYNC pin allows the user to synchronize the LMX2572 such that the delay from the rising edge of th OSCin signal to the RF output signal is deterministic. Phase synchronization is especially useful if there are multiple LMX2572 devices in a system and it is desirable to have all the RF outputs aligned in phase.

Figure 33. Phase Synchronization

Copyright © 2017–2019, Texas Instruments Incorporated Product Folder Links: *LMX2572*

Initially, the devices are locked to the input but are not synchronized. The user sends a synchronization pulse that is re-clocked to the next rising edge of the OSCin pulse. After a given time,  $t_1$ , the devices are synchronized. This time is dominated by the sum of the VCO calibration time, the analog settling time of the PLL loop, and the MASH\_RST\_COUNT, if used in fractional mode. After synchronization, both devices will have a deterministic delay of  $t_2$ , related to OSCin.

#### 7.3.12 Phase Adjustment

The LMX2572 can use the sigma-delta modulator to adjust the output signal phase with respect to the input reference. The phase shift every time you write the value of MASH\_SEED is Equation 3:

Phase shift in degree = 360° x (MASH\_SEED / PLL\_DEN) x (P / CHDIV)

where

For example, if

- MASH SEED = 800

- PLL\_DEN = 1000

- CHDIV = 32

- VCO\_PHASE\_SYNC\_EN = 0

Phase shift =  $360^{\circ} \times (800 / 1000) \times (1 / 32) = 9^{\circ}$ . If we write 800 to MASH\_SEED 40 times, then we will shift the phase by  $360^{\circ}$ .

There are a couple of restrictions when using phase adjustment:

- Phase adjustment does not work with MASH ORDER equals 0 (Integer mode) or 1 (First order).

- Phase adjustment is possible with integer channels (PLL\_NUM = 0) as long as MASH\_ORDER is greater than 1.

- PLL DEN must be greater than PLL NUM + MASH SEED.

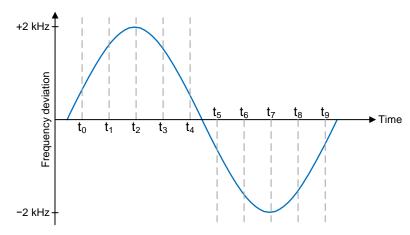

#### 7.3.13 Ramping Function

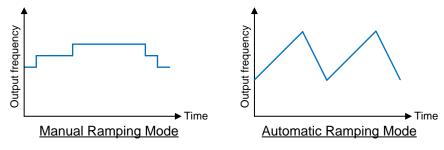

The LMX2572 supports the ability to make frequency ramping waveforms using manual mode or automatic mode.

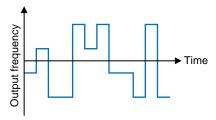

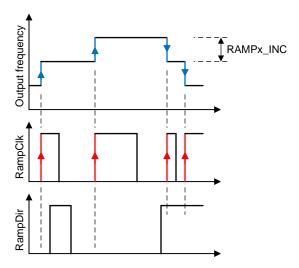

In manual ramping mode, the user defines a step and uses the RampClk and RampDir pins to create the ramp. The output frequency jumps from one frequency to another frequency on each ramp.

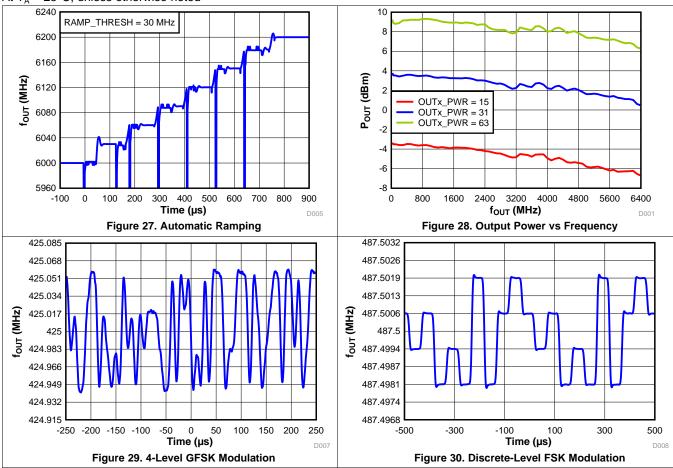

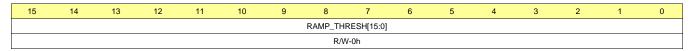

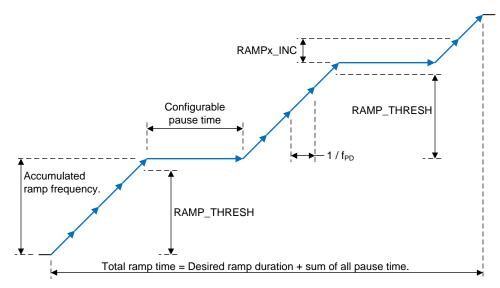

In automatic ramping mode, the user sets up the ramp with up to two linear segments in advance and the device automatically creates this ramp. The output waveform is a continuous frequency sweep between the start and end frequencies. If the frequency ramping range is small (approximately 10 MHz), no VCO calibration break is necessary in the middle of the ramp.

When using ramp, the following must be set accordingly:

- Phase detector frequency must be between  $f_{OSCin}$  /  $2^{CAL\_CLK\_DIV}$  and 125 MHz.

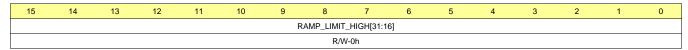

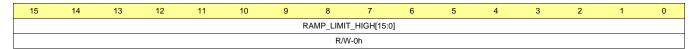

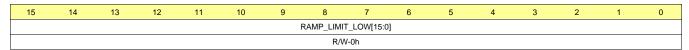

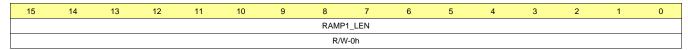

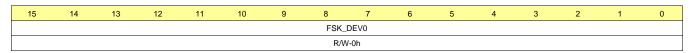

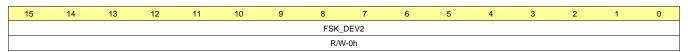

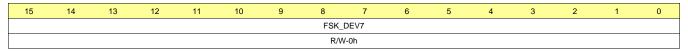

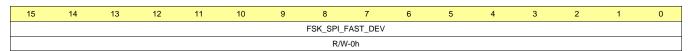

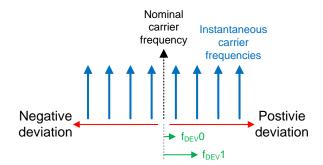

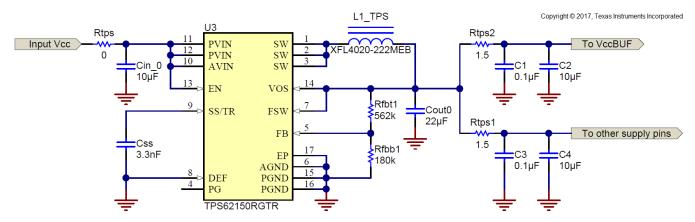

- OUT FORCE = 1 to force the RF outputs not to be automatically muted during VCO calibration.