SNVSAJ7D - FEBRUARY 2016-REVISED MARCH 2018

LM36272

# LM36272 Two-Channel LCD Backlight Driver With Integrated Bias Power

#### **Features**

- Drives up to Two Parallel White LED Strings (29-V Maximum V<sub>OUT</sub>)

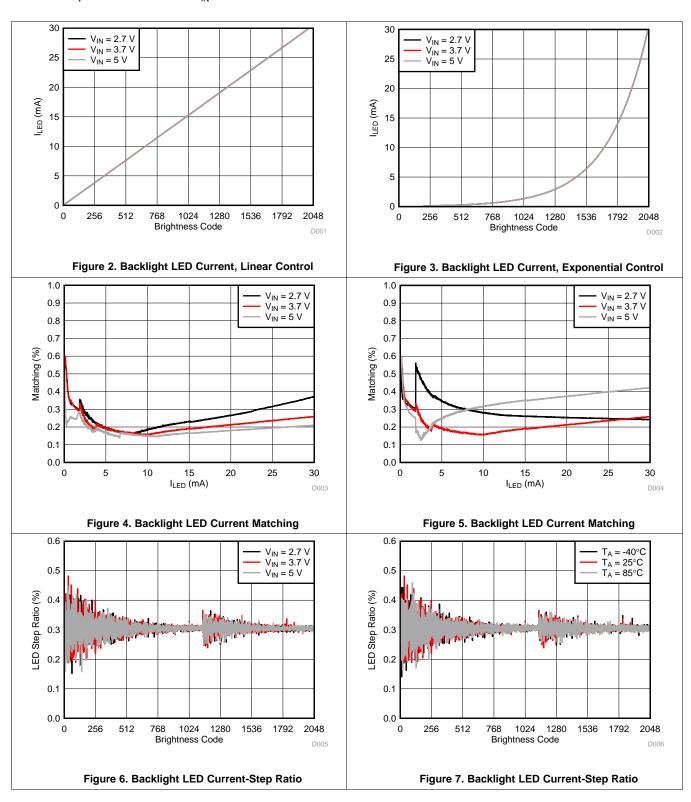

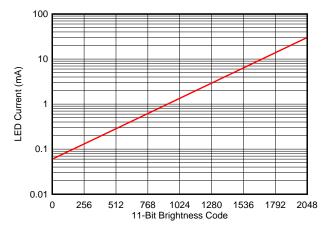

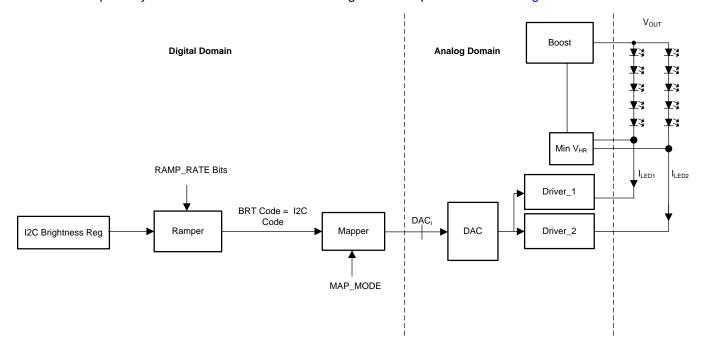

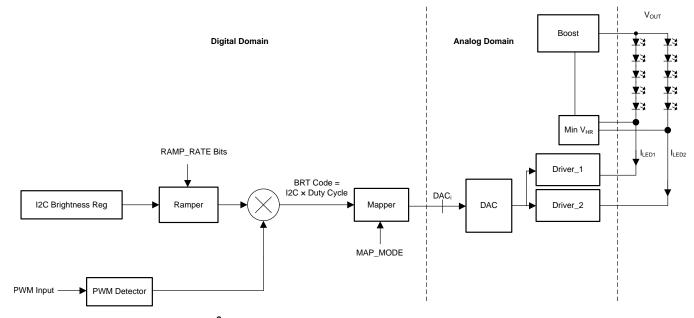

- 11-Bit Exponential and Linear Dimming Control

- PWM and I<sup>2</sup>C Brightness Control

- Backlight Operation With 4.7-µH to 15-µH Inductor

- Backlight and LCD Bias Efficiency up to 92%

- Programmable LCD Bias Voltages (±4 V to ±6.5 V With 50-mV resolution) With Up to 80-mA per Output

- 0.2% Matched LED Current From 60 µA to 30 mA

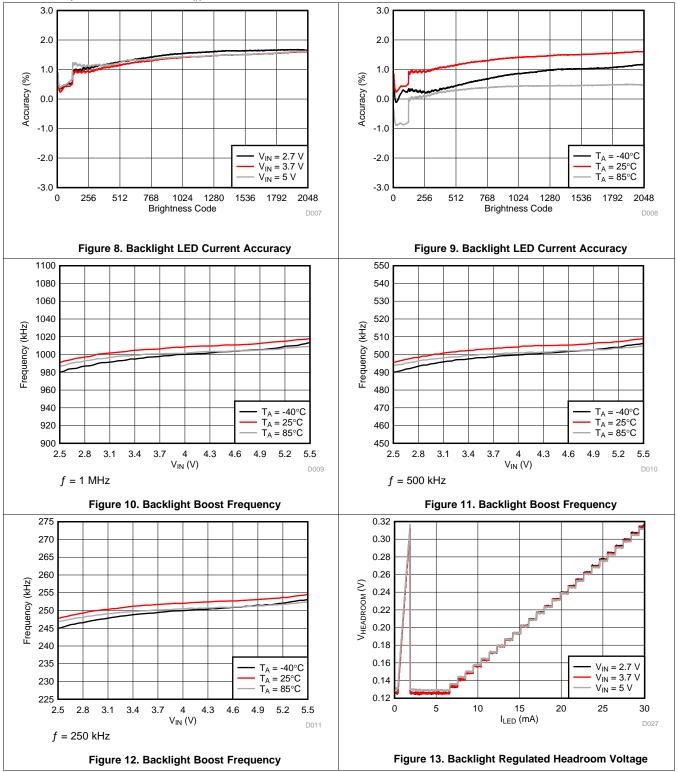

- 1% Accurate LED Current From 60 µA to 30 mA

- 2.7-V to 5-V Input Voltage Range

## **Applications**

- LCD Panels With up to 16 LEDs

- **Smart Phones**

- **Tablets and Gaming Tablets**

- Home Automation Panels

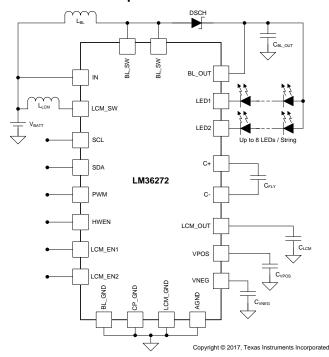

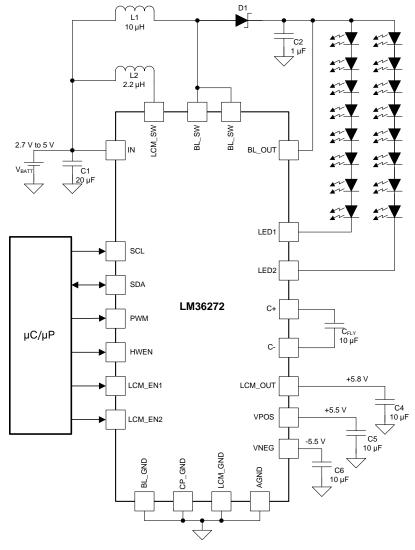

## Simplified Schematic

## 3 Description

The LM36272 is an integrated two-channel WLED driver and LCD bias supply. The ultra-compact size, high efficiency, high level of integration, and programmability allow the LM36272 to address a variety of applications without the need for hardware changes while minimizing the overall solution area.

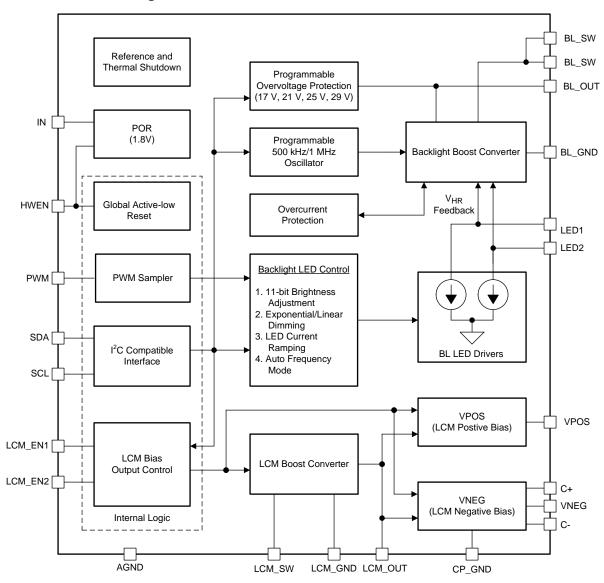

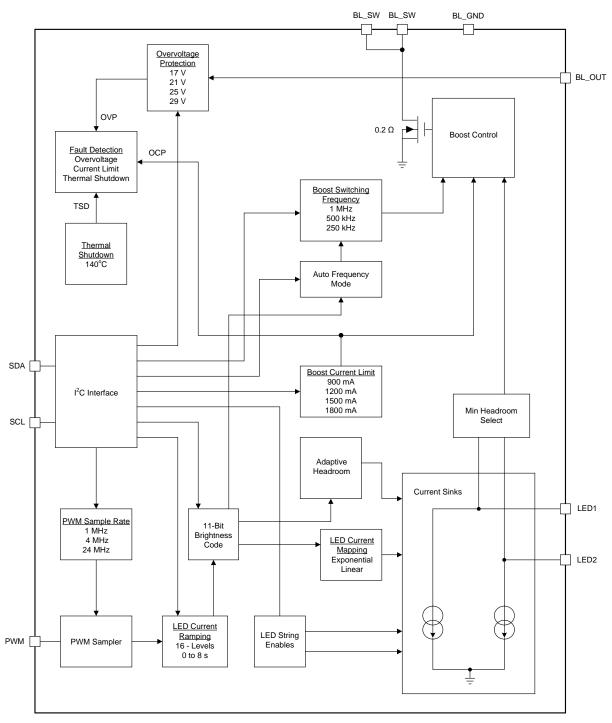

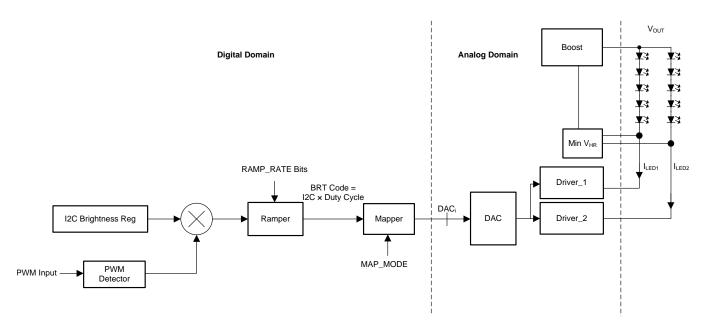

The backlight boost provides the power to bias two parallel LED strings with up to 29-V total output voltage. The 11-bit LED current is programmable via the I<sup>2</sup>C bus and/or controlled via a logic level PWM input from 60 µA to 30 mA. Each LED string can be independently enabled or disabled to provide zone dimming capabilities. The backlight boost can be operated efficiently with an inductance range from 4.7 µH to 15 µH, allowing for efficiency and solution size optimization.

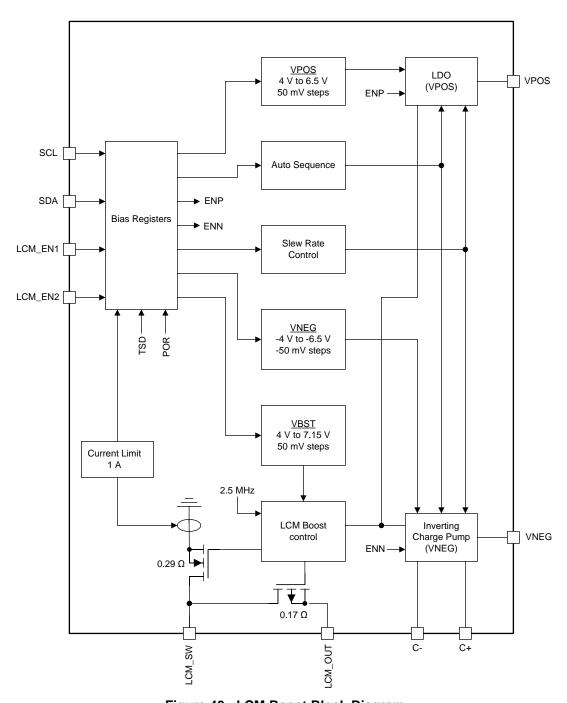

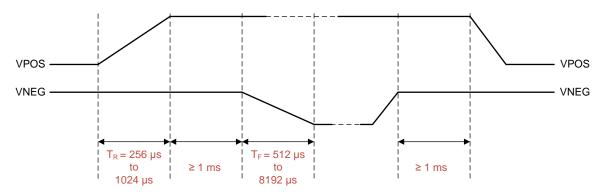

The LCD bias boost provides the power to both a positive LDO and an inverting charge pump. Both and negative bias supplies programmable output voltages of ±4 V to ±6.5 V with 50-mV steps and up to ±80 mA of current capability. An auto-sequencing feature provides a programmed delay from positive to negative bias activation, with additional programmable voltage slew rate control. Two wake-up modes allow both bias outputs to be controlled with a single external signal and stay active while consuming very low quiescent current.

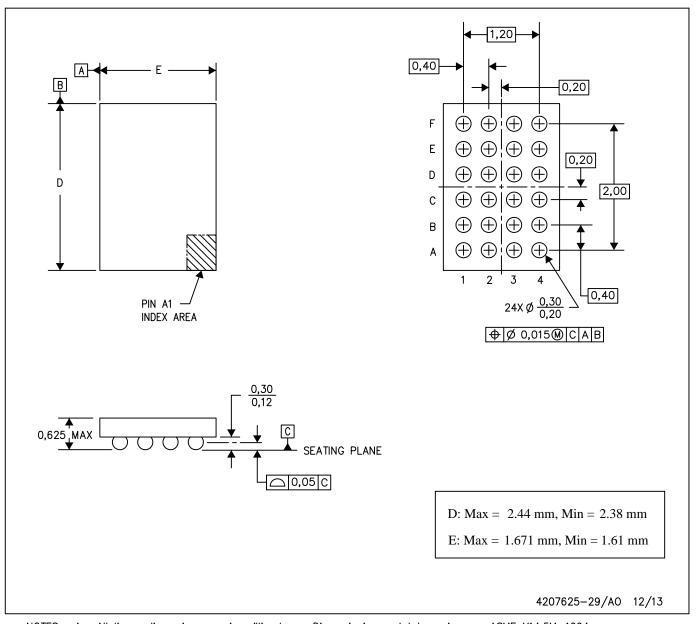

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)   |  |  |

|-------------|------------|-------------------|--|--|

| LM36272     | DSBGA (24) | 2.44 mm × 1.67 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

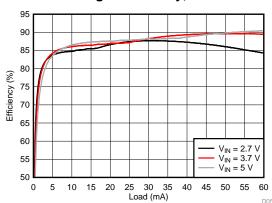

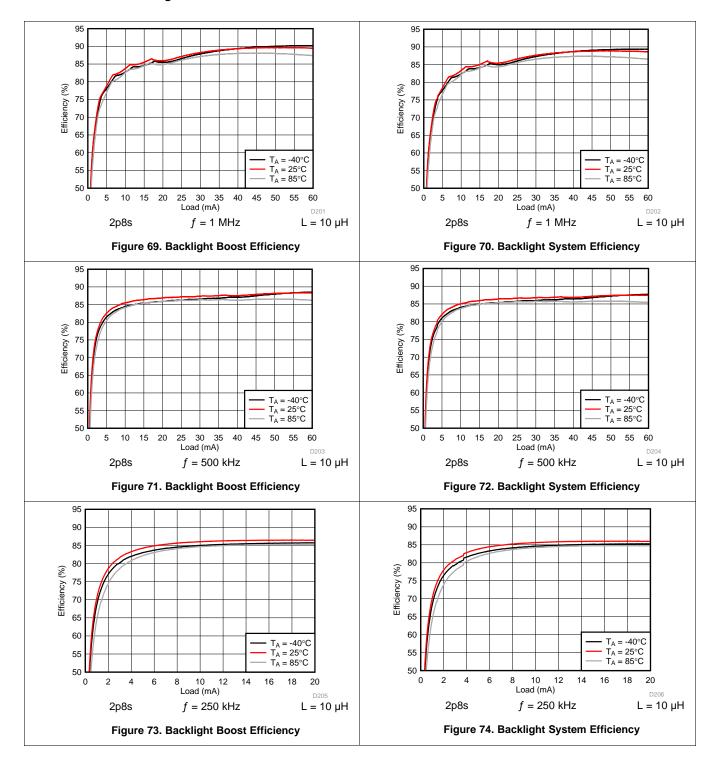

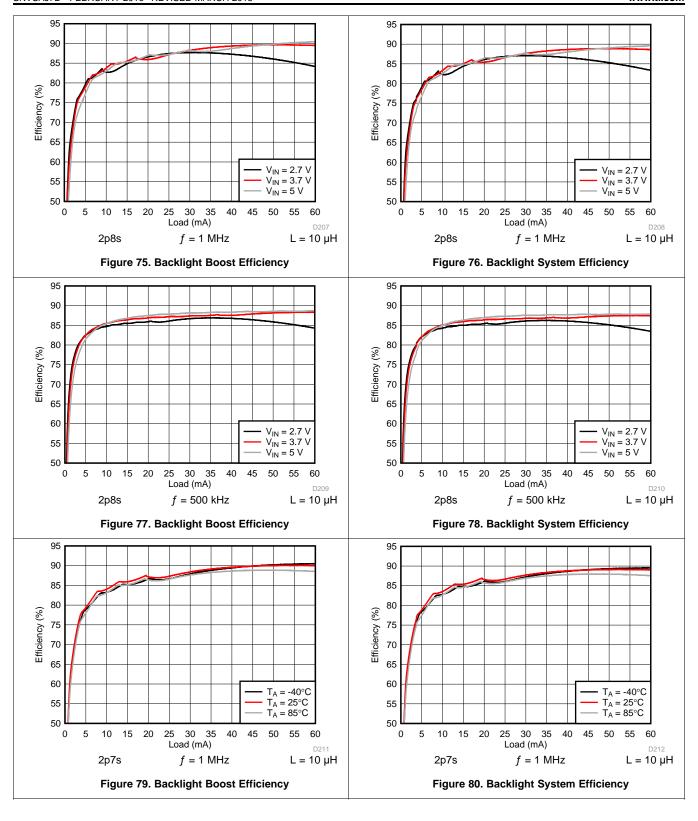

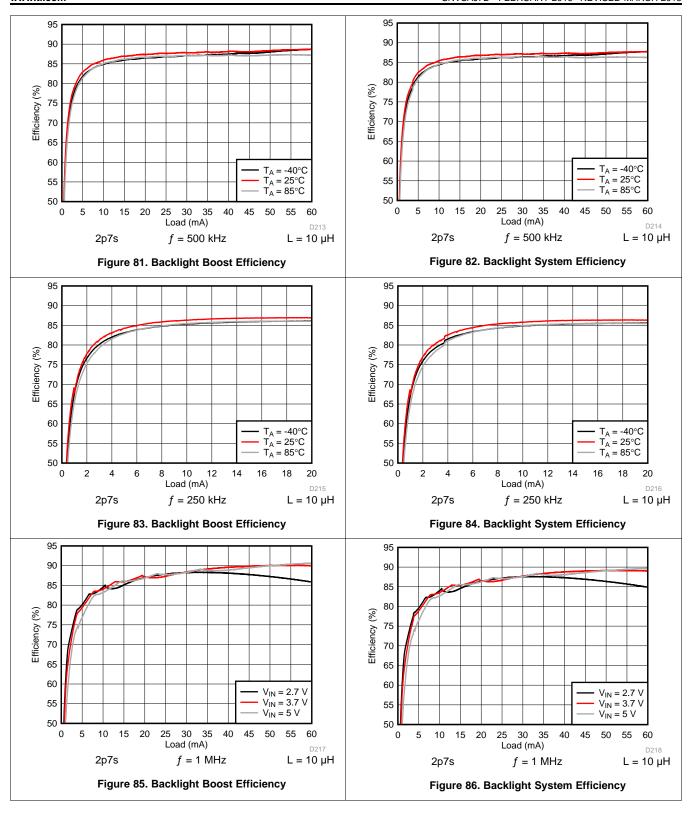

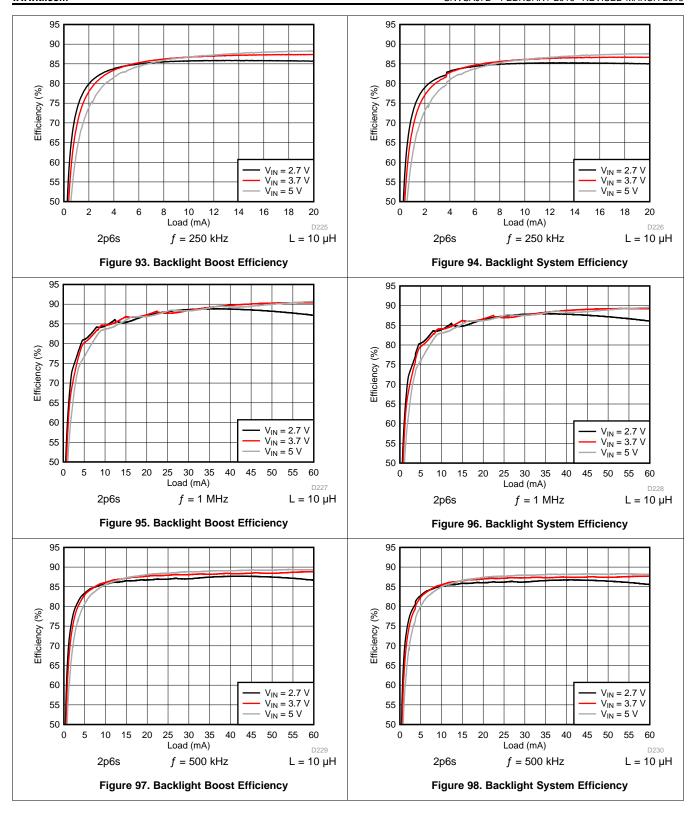

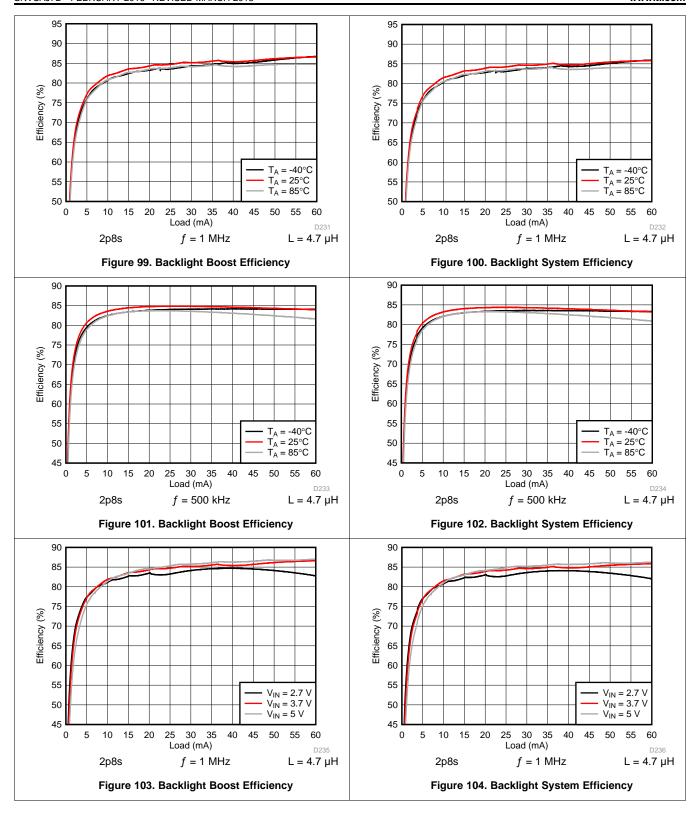

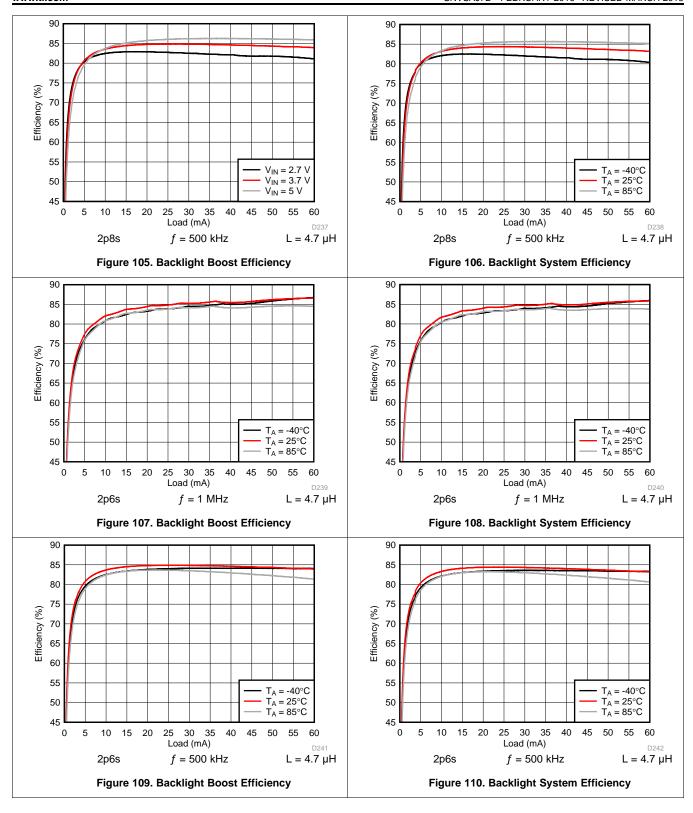

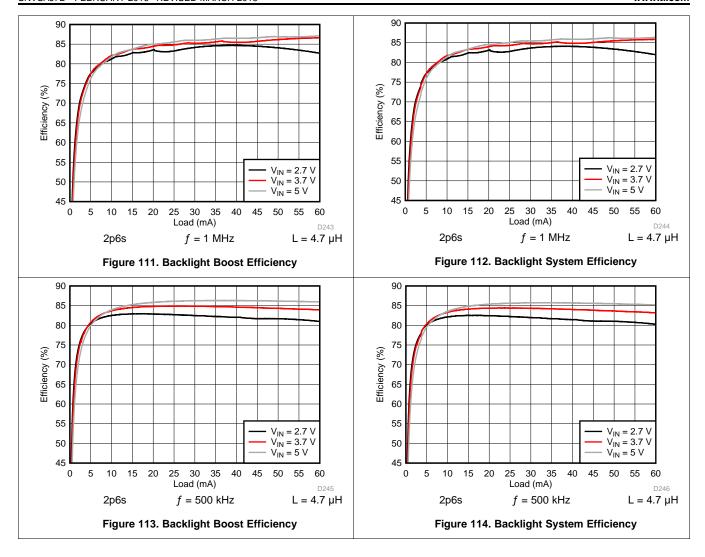

#### Backlight Efficiency, 2P8S

| Table of Content | ts |

|------------------|----|

|------------------|----|

| 1 | Features 1                                           | 7.5 Programming                                         |

|---|------------------------------------------------------|---------------------------------------------------------|

| 2 | Applications 1                                       | 7.6 Register Maps                                       |

| 3 | Description 1                                        | 8 Application and Implementation 47                     |

| 4 | Revision History                                     | 8.1 Application Information47                           |

| 5 | Pin Configuration and Functions                      | 8.2 Typical Application                                 |

| 6 | Specifications                                       | 9 Power Supply Recommendations 63                       |

| ٠ | 6.1 Absolute Maximum Ratings 5                       | 10 Layout 63                                            |

|   | 6.2 ESD Ratings                                      | 10.1 Layout Guidelines63                                |

|   | 6.3 Recommended Operating Conditions                 | 10.2 Layout Example64                                   |

|   | 6.4 Thermal Information                              | 11 Device and Documentation Support 65                  |

|   | 6.5 Electrical Characteristics                       | 11.1 Device Support                                     |

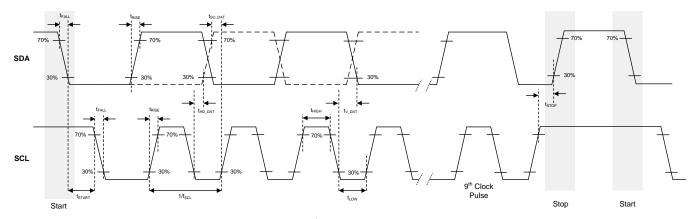

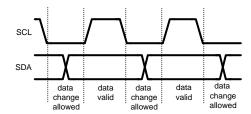

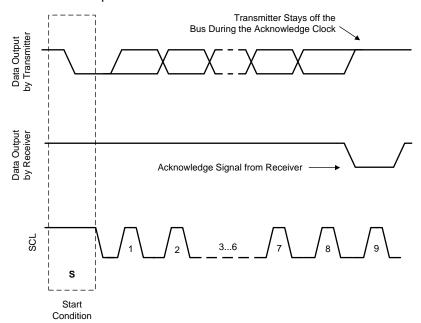

|   | 6.6 I <sup>2</sup> C Timing Requirements (Fast Mode) | 11.2 Documentation Support 65                           |

|   | 6.7 Typical Characteristics                          | 11.3 Receiving Notification of Documentation Updates 65 |

| 7 | Detailed Description 15                              | 11.4 Community Resources65                              |

| • | 7.1 Overview                                         | 11.5 Trademarks                                         |

|   | 7.2 Functional Block Diagram                         | 11.6 Electrostatic Discharge Caution                    |

|   | 7.3 Features Description                             | 11.7 Glossary 65                                        |

|   | 7.4 Device Functional Modes                          | 12 Mechanical, Packaging, and Orderable Information66   |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision C (June 2017) to Revision D                                             | Page                                    |

|-----------------------------------------------------------------------------------------------|-----------------------------------------|

| Added added silicon rev A1 to revision register.                                              |                                         |

| Changes from Revision B (March 2017) to Revision C                                            | Page                                    |

| Changed First public release of full data sheet to WEB                                        | 1                                       |

| Changes from Revision A (January 2017) to Revision B                                          | Page                                    |

| <ul> <li>Changed row(s) in Abs Max table: BL_SW from 30 V to 35 V, BL_OUT and curr</li> </ul> | ent sink inputs (LEDX) remain at 30 V 5 |

| Changes from Original (February 2016) to Revision A                                           | Page                                    |

| Changed "Orderable Device" suffix on POA from "YFRR" to "YFFR"                                |                                         |

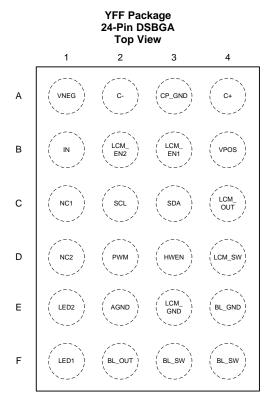

# 5 Pin Configuration and Functions

## **Pin Functions**

|        | PIN     | TVDE | DESCRIPTION                                                                                                     |

|--------|---------|------|-----------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME    | TYPE | DESCRIPTION                                                                                                     |

| A1     | VNEG    | 0    | Inverting charge pump output. Bypass VNEG with a 10-µF ceramic capacitor to CP_GND.                             |

| A2     | C-      | 0    | Inverting charge-pump flying capacitor negative connection                                                      |

| A3     | CP_GND  | _    | Charge pump GND. Connect the CNEG capacitor negative terminal to this pin.                                      |

| A4     | C+      | 0    | Inverting charge-pump flying capacitor positive connection                                                      |

| B1     | IN      | I    | Input voltage connection. Bypass IN with a 10-µF ceramic capacitor to GND.                                      |

| B2     | LCM_EN2 | I    | Enable for LCD bias negative output; 300-k $\Omega$ internal pulldown resistor between LCM_EN2 and GND.         |

| В3     | LCM_EN1 | I    | Enable for LCD bias positive output; 300-k $\Omega$ internal pulldown resistor between LCM_EN1 and GND.         |

| B4     | VPOS    | 0    | Positive LCD bias output. Bypass VPOS with a 10-µF ceramic capacitor to GND.                                    |

| C1     | NC2     | _    | No connect; leave this pin disconnected                                                                         |

| C2     | SCL     | I    | Serial clock connection for I <sup>2</sup> C-compatible interface                                               |

| C3     | SDA     | I/O  | Serial clock connection for I <sup>2</sup> C-compatible interface                                               |

| C4     | LCM_OUT | 0    | LCD bias boost output voltage. Bypass LCM_OUT with a 10-µF ceramic capacitor to LCM_GND.                        |

| D1     | NC1     | _    | No connect; leave this pin disconnected                                                                         |

| D2     | PWM     | I    | PWM input for duty cycle current control; 300-k $\Omega$ internal pulldown resistor between PWM and GND.        |

| D3     | HWEN    | 1    | Active high chip enable; 300-kΩ internal pulldown resistor between HWEN and GND.                                |

| D4     | LCM_SW  | 0    | LCD bias boost inductor connection                                                                              |

| E1     | LED2    | I    | Current sink 2 input. Connect the cathode of LED string 2 to this pin. Leave this pin disconnected if not used. |

# Pin Functions (continued)

|        | PIN     | TVDE | DESCRIPTION                                                                                                            |

|--------|---------|------|------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME    | TYPE | DESCRIPTION                                                                                                            |

| E2     | AGND    | _    | Analog ground connection. Connect AGND directly to GND on the PCB.                                                     |

| E3     | LCM_GND | _    | LCD bias boost GND connection. Connect LCM_GND to the negative terminal of the LCD bias output capacitor.              |

| E4     | BL_GND  | _    | Backlight boost output capacitor GND connection                                                                        |

| F1     | LED1    | 1    | Current sink 1 input. Connect the cathode of LED string 1 to this pin. Leave this pin disconnected if not used.        |

| F2     | BL_OUT  | 0    | Backlight boost output voltage sense connection. Connect to the positive terminal of backlight boost output capacitor. |

| F3     | BL_SW   | 0    | Backlight boost inductor connection                                                                                    |

| F4     | BL_SW   | 0    | Backlight boost inductor connection                                                                                    |

Submit Documentation Feedback

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                      | MIN        | MAX     | UNIT |

|------------------------------------------------------|------------|---------|------|

| Voltage on IN, HWEN, LCM_EN1, LCM_EN2, SCL, SDA, PWM | -0.3       | 6       | V    |

| Voltage on LCM_SW, LCM_OUT, VPOS, C+                 | -0.3       | 9       | V    |

| Voltage on VNEG, C-                                  | <b>-7</b>  | 0.3     | V    |

| Voltage on BL_SW                                     | -0.3       | 35      | V    |

| Voltage on BL_OUT, LED1, LED2                        | -0.3       | 30      | V    |

| Continuous power dissipation                         | Internally | limited |      |

| Maximum junction temperature, T <sub>J(MAX)</sub>    |            | 150     | °C   |

| Storage temperature, T <sub>stg</sub>                | -45        | 150     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                                            |                                                                   |                                                                     | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                               | V     |      |

|                                            | discharge                                                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)(1) (2)

|                                                              | MIN | MAX | UNIT |

|--------------------------------------------------------------|-----|-----|------|

| Input voltage, V <sub>IN</sub>                               | 2.7 | 5   | ٧    |

| Operating ambient temperature, T <sub>A</sub> <sup>(3)</sup> | -40 | 85  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the AGND pin.

## 6.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                | DSBGA (YFF) | UNIT |

|--------------------|----------------------------------------------|-------------|------|

|                    |                                              | (24 PINS)   |      |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 63.1        | °C/W |

| $R_{\theta JC}$    | Junction-to-case (top) thermal resistance    | 0.4         | °C/W |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 11.6        | °C/W |

| $\Psi_{\text{JT}}$ | Junction-to-top characterization parameter   | 1.6         | °C/W |

| $\Psi_{JB}$        | Junction-to-board characterization parameter | 11.6        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> All voltages are with respect to the potential at the AGND pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (R<sub>0JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>0JA</sub> × P<sub>D-MAX</sub>).

## 6.5 Electrical Characteristics

Unless otherwise specified, typical limits apply at 25°C, minimum and maximum limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$ ), and  $V_{IN} = 3.6 \text{ V}$ .

|                      | PARAMETER                                        | TEST CONI                                                                                           | DITIONS                                                                                                 | MIN  | TYP   | MAX      | UNIT |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-------|----------|------|

| CURRENT CO           | ONSUMPTION                                       | -                                                                                                   | <u>'</u>                                                                                                |      |       | <u>'</u> |      |

| I <sub>SD</sub>      | Shutdown current                                 | HWEN = 0                                                                                            |                                                                                                         |      | 0.2   | 2.8      | μΑ   |

| IQ                   | Quiescent current, device not switching          | HWEN = V <sub>IN</sub> , LCM b                                                                      | HWEN = V <sub>IN</sub> , LCM boost disabled                                                             |      | 1     | 7        | μΑ   |

| I <sub>LCM_EN</sub>  | Bias power no load supply current                | backlight boost disab                                                                               | VPOS, VNEG enabled with no load, backlight boost disabled, typical application circuit (not ATE tested) |      | 0.5   | 10       | μΑ   |

| BACKLIGHT I          | LED CURRENT SINKS (LED1, LED2,                   | LED3, LED4)                                                                                         |                                                                                                         |      |       |          |      |

| I <sub>LED_MAX</sub> | Maximum output current (per string)              | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, line exponential mode                                                | ear or                                                                                                  |      | 30    |          | mA   |

| I <sub>LED</sub>     | LED current accuracy <sup>(1)</sup>              | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, 60 mA, linear or expone                                              |                                                                                                         | -3%  |       | 3%       |      |

| I <sub>MATCH</sub>   | I <sub>LED</sub> current matching <sup>(2)</sup> | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, 60 mA, linear or expone                                              |                                                                                                         | -2%  | 0.2%  | 2%       |      |

| I <sub>LED_MIN</sub> | Minimum LED current (per string)                 | Linear or exponential                                                                               | mode                                                                                                    |      | 60    |          | μΑ   |

|                      | LED current step size (code to                   | Exponential mode (3)                                                                                |                                                                                                         |      | 0.3%  |          |      |

| I <sub>STEP</sub>    | code)                                            | Linear mode                                                                                         |                                                                                                         |      | 14.63 |          | μΑ   |

| BACKLIGHT I          | вооѕт                                            |                                                                                                     | ·                                                                                                       |      |       |          |      |

|                      |                                                  | ON threshold, 2.7 V<br>≤ V <sub>IN</sub> ≤ 5 V                                                      | 011 to 111                                                                                              | 28.5 | 29    | 29.5     |      |

| O)/D throobold       | 1                                                |                                                                                                     | 010                                                                                                     | 24.5 | 25    | 25.5     | V    |

| OVP threshold        |                                                  |                                                                                                     | 001                                                                                                     | 20.5 | 21    | 21.5     |      |

|                      |                                                  |                                                                                                     | 000                                                                                                     | 16.3 | 17    | 17.7     |      |

| OVP hysteresi        | s                                                | OFF threshold                                                                                       |                                                                                                         |      | 0.5   |          | V    |

| Efficiency           | Boost efficiency                                 | $V_{IN} = 3.6 \text{ V}, I_{BLED} = 5$<br>$(P_{OUT}/P_{IN}), \text{ Typical A}$<br>(not ATE tested) | mA/string,<br>pplication Circuit                                                                        |      | 90%   |          |      |

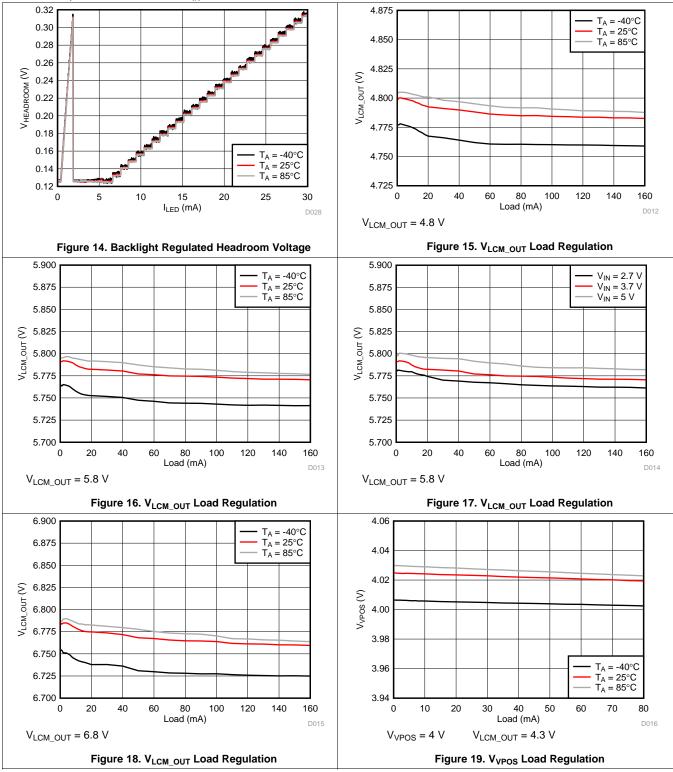

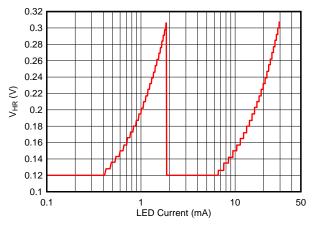

| V                    | Regulated current-sink headroom                  | $I_{LED} = 30 \text{ mA}$                                                                           |                                                                                                         |      | 310   |          | mV   |

| $V_{HR}$             | voltage (boost feedback voltage)                 | $I_{LED} = 5 \text{ mA}$                                                                            |                                                                                                         |      | 120   |          | mV   |

| $V_{HR\_MIN}$        | Current-sink minimum headroom voltage            | I <sub>LED</sub> = 95% of nomina                                                                    | al, I <sub>LED</sub> = 5 mA                                                                             |      | 30    | 50       | mV   |

| R <sub>DSON</sub>    | NMOS switch on resistance                        | $I_{SW} = 250 \text{ mA}$                                                                           |                                                                                                         |      | 0.2   |          | Ω    |

|                      |                                                  |                                                                                                     | 00                                                                                                      | 792  | 900   | 1008     | mA   |

|                      | NIMOS quitab gurrant limit                       | 271/21/251/                                                                                         | 01                                                                                                      | 1056 | 1200  | 1344     | mA   |

| I <sub>CL</sub>      | NMOS switch current limit                        | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}$                                          | 10                                                                                                      | 1320 | 1500  | 1680     | mA   |

|                      |                                                  |                                                                                                     | 11                                                                                                      | 1584 | 1800  | 2016     | mA   |

| for our              | Switching frequency                              | 271/21/251                                                                                          | 500-kHz mode                                                                                            | 450  | 500   | 550      | kHz  |

| f <sub>BL_SW</sub>   | Switching frequency                              | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}$                                          | 1-MHz mode                                                                                              | 900  | 1000  | 1100     | NITΔ |

| D <sub>MAX</sub>     | Maximum duty cycle                               | $V_{IN} = 2.7 \text{ V}, f_{LED\_SW}$                                                               | = 1 MHz                                                                                                 | 93%  | 94%   |          |      |

| DEVICE PRO           | TECTION                                          |                                                                                                     |                                                                                                         |      |       |          |      |

| TSD                  | Thermal shutdown                                 | Not ATE tested                                                                                      |                                                                                                         |      | 140   |          | °C   |

<sup>(1)</sup> Output current accuracy is the difference between the actual value of the output current and programmed value of this current.

LED current matching is the maximum difference between any string current and the average string current, divided by the average string current. This is calculated as (I<sub>LEDX</sub> – I<sub>LED\_AVE</sub>) / I<sub>LED\_AVE</sub> × 100.

(3) LED current step size from code to code in exponential mode is typically 0.304%, given as (1 – (I<sub>LED(CODE+1</sub>) / I<sub>LED(CODE)</sub>).

## **Electrical Characteristics (continued)**

Unless otherwise specified, typical limits apply at 25°C, minimum and maximum limits apply over the full operating ambient temperature range ( $-40^{\circ}$ C  $\leq T_A \leq 85^{\circ}$ C), and  $V_{IN} = 3.6 \text{ V}$ .

|                                         | PARAMETER                                                                                | TEST CONDITIONS                                                                                                                                | MIN         | TYP  | MAX  | UNIT   |

|-----------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|--------|

| DISPLAY BIAS (                          | LCM BOOST)                                                                               |                                                                                                                                                |             |      |      |        |

| V <sub>OVP_LCM</sub>                    | LCM bias boost overvoltage protection                                                    | On threshold, 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                                                                    |             | 7.8  |      | V      |

| $f_{LCM\_SW}$                           | Switching frequency (4)                                                                  | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V} \text{ (continuous conduction mode)}$                                                  |             | 2500 |      | kHz    |

|                                         | LCM boost output voltage range                                                           |                                                                                                                                                | 4           |      | 7.15 | V      |

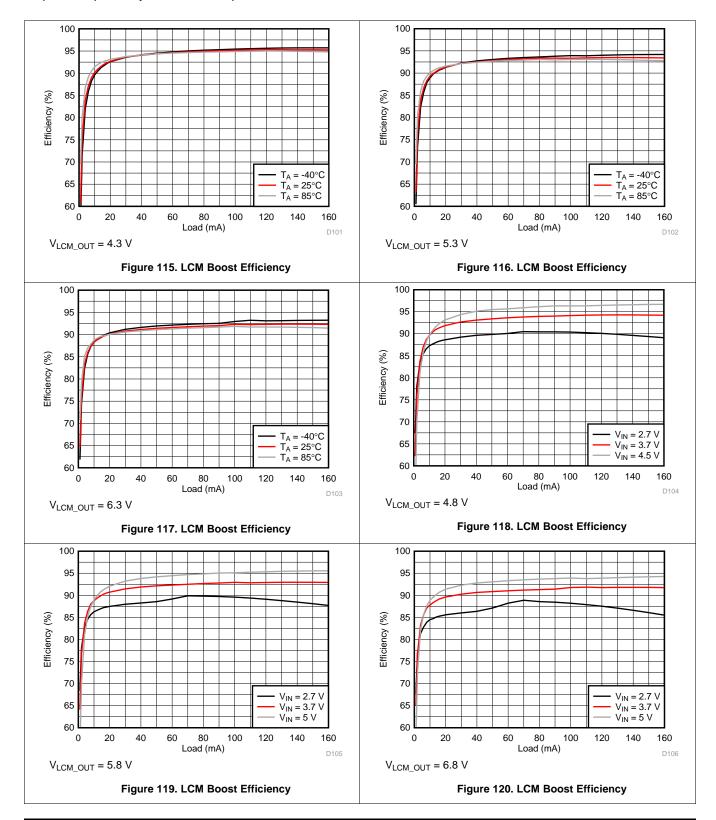

| V <sub>LCM_OUT</sub>                    | Efficiency                                                                               | V <sub>IN</sub> = 3.6 V, V <sub>LCM_OUT</sub> = 5.9 V, 6 mA<br>< I <sub>LCM_OUT</sub> < 160mA, Typical<br>Application Circuit (not ATE tested) |             | 92%  |      |        |

|                                         | Output voltage step size                                                                 |                                                                                                                                                |             | 50   |      | mV     |

| I <sub>LCM_BOOST_CL</sub>               | Valley current limit                                                                     |                                                                                                                                                |             | 1000 |      | mA     |

| D                                       | High-side MOSFET on resistance                                                           | $V_{IN} = V_{GS} = 3.6 \text{ V}$                                                                                                              |             | 170  |      | mΩ     |

| R <sub>DSON_LCM</sub>                   | Low-side MOSFET on Resistance                                                            | $V_{IN} = V_{GS} = 3.6 \text{ V}$                                                                                                              |             | 290  |      | 1115.2 |

| V <sub>LCM_OUT_</sub><br>RIPPLE         | Peak-to-peak ripple voltage (4)                                                          | $ \begin{array}{l} I_{LOAD\_LCM\_BOOST} = 5 \text{ mA and } 50 \text{ mA}, \\ C_{BST} = 20 \ \mu\text{F} \end{array} $                         |             | 50   |      | mVpp   |

| V <sub>LCM_OUT_LINE_</sub><br>TRANSIENT | LCM_OUT line transient response (4)                                                      | $V_{IN}$ + 500 mVp-p AC square wave, Tr = 100 mV/ $\mu$ s, 200 Hz, 12.5% DS at 5 mA, $I_{LOAD}$ = 5 mA, $C_{IN}$ = 10 $\mu$ F                  | -50         | ±25  | 50   | mV     |

| V <sub>LCM_OUT_LOAD_</sub><br>TRANSIENT | LCM_OUT load transient response (4)                                                      | 0 mA to 150 mA, $t_{RISE/FALL}$ = 100 mA/ $\mu$ s, $C_{IN}$ = 10 $\mu$ F                                                                       | -150        |      | 150  | mV     |

| t <sub>LCM_OUT_ST</sub>                 | Start-up time (LCM_OUT),<br>V <sub>LCM_OUT</sub> = 10% to 90% <sup>(4)</sup>             | C <sub>LCM_OUT</sub> = 20 μF                                                                                                                   |             |      | 1000 | μs     |

| DISPLAY BIAS F                          | POSITIVE OUTPUT (VPOS)                                                                   |                                                                                                                                                |             |      |      |        |

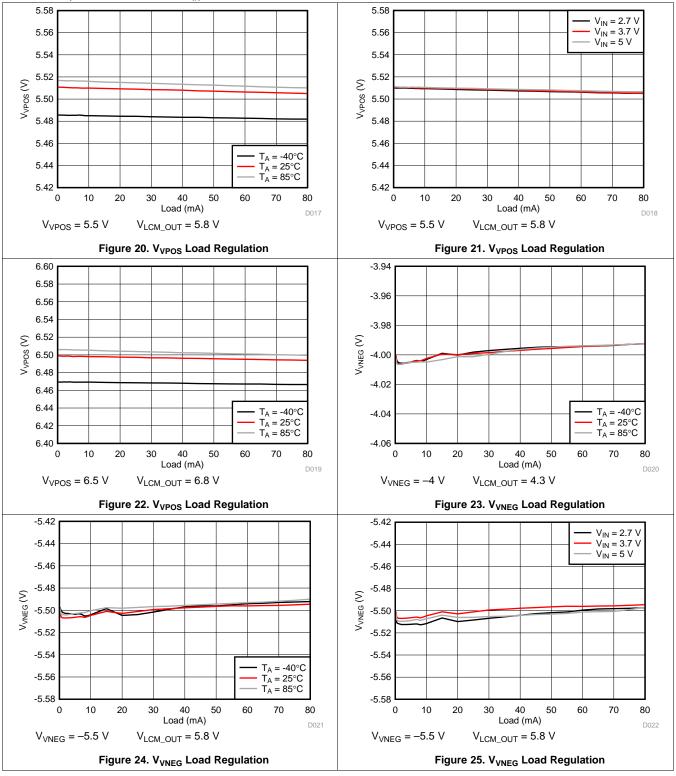

|                                         | Programmable output voltage range                                                        |                                                                                                                                                | 4           |      | 6.5  | V      |

| $V_{VPOS}$                              | Output voltage step size                                                                 |                                                                                                                                                |             | 50   |      | mV     |

|                                         | Output voltage accuracy                                                                  | Output voltage = 5.4 V                                                                                                                         | -1.5%       |      | 1.5% |        |

| I <sub>VPOS_MAX</sub>                   | Maximum output current                                                                   |                                                                                                                                                | 80          |      |      | mA     |

| I <sub>VPOS_CL</sub>                    | Output current limit                                                                     |                                                                                                                                                |             | 180  |      | mA     |

| I <sub>RUSH_PK_VPOS</sub>               | Peak start-up inrush current <sup>(4)</sup>                                              | $V_{LCM\_OUT}$ = 6.3 V, $V_{POS}$ = 5.8 V, $C_{VPOS}$ = 10 $\mu F$ (nominal)                                                                   |             |      | 250  | mA     |

| V <sub>VPOS</sub> _<br>LINE_TRANSIENT   | LDO_VPOS line transient response <sup>(4)</sup>                                          | $V_{IN}$ + 500 mVp-p AC square wave, Tr = 100 mV/ $\mu$ s, 200 Hz at 25 mA, $C_{IN}$ = 10 $\mu$ F (nominal)                                    | <b>–</b> 50 |      | 50   | mV     |

| V <sub>VPOS_LOAD_TRA</sub>              | LDO_VPOS load transient response (4)                                                     | Load current step 0 mA to 50 mA, C <sub>VPOS</sub> = 10 µF (nominal)                                                                           | -50         |      | 50   | mV     |

| V <sub>VPOS_DC_REG</sub>                | DC load regulation (4)                                                                   | 0 mA ≤ I <sub>LOAD_VPOS</sub> ≤ I <sub>LOAD_VPOS_MAX</sub>                                                                                     |             |      | 20   | mV     |

| V <sub>DO_VPOS</sub>                    | VPOS dropout voltage <sup>(5)</sup>                                                      | I <sub>LOAD_VPOS</sub> = I <sub>LOAD_VPOS_MAX</sub><br>V <sub>VPOS</sub> = 5.7 V                                                               |             |      | 160  | mV     |

| PSSR <sub>VPOS</sub>                    | Power supply rejection ratio (LDO_VPOS) (4)                                              | f = 10 Hz to 500 kHz at I <sub>MAX</sub> /2<br>V <sub>LCM_OUT</sub> - V <sub>VPOS</sub> ≥ 300 mV                                               | 25          |      |      | dB     |

| t <sub>ST_VPOS</sub>                    | Start-up time (LDO_VPOS) <sup>(6)</sup><br>V <sub>VPOS</sub> = 10% to 90% <sup>(4)</sup> | C <sub>VPOS</sub> = 10 μF v                                                                                                                    |             | 800  |      | μs     |

| R <sub>PD_VPOS</sub>                    | Output pulldown resistor (VPOS)                                                          | VPOS pulldown in shutdown                                                                                                                      | 30          | 80   | 270  | Ω      |

| Pulldown<br>resistance on<br>LCM_EN1    |                                                                                          | Not ATE tested                                                                                                                                 |             | 300  |      | kΩ     |

Product Folder Links: LM36272

Limits set by characterization and/or simulation only.  $V_{\text{IN\_VPOS}} - V_{\text{VPOS}}$  when  $V_{\text{VPOS}}$  has dropped 100 mV below target. Typical value only for information. (5)

## **Electrical Characteristics (continued)**

Unless otherwise specified, typical limits apply at 25°C, minimum and maximum limits apply over the full operating ambient temperature range (-40°C  $\leq T_A \leq 85$ °C), and  $V_{IN} = 3.6$  V.

| DISPLAY BIAS NEGATIVE OUTPUT (VNEG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       | PARAMETER                                                  | TEST CONDITIONS                                                                               | MIN   | TYP | MAX             | UNIT      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|-----|-----------------|-----------|--|

| Varied Short   NeG output short circuit protection   Varied to CP_GND, VNEG rises to % I draiget   I draight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DISPLAY BIAS N                        |                                                            |                                                                                               |       |     |                 |           |  |

| Neg > -5 mA   Neg > -5 mA   Neg > -5 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | ,                                                          |                                                                                               |       | 84% |                 |           |  |

| Value   Va                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | Efficiency <sup>(6)</sup>                                  |                                                                                               |       | 92% |                 |           |  |

| Output accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $V_{VNEG}$                            |                                                            |                                                                                               | -6.5  |     | -4              | V         |  |

| LOAD_VNEG_MAX   Maximum output current   VLCM_OUT = 5.9 V, VNEG = −5.4 V   80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | Output voltage step size                                   |                                                                                               |       | 50  |                 | mV        |  |

| V_VNEG_CL   Output current limit   01   355     Q2   240     Q3   324     Q2   240     Q3   240     Q3   240     Q3   240     Q4   240     Q5   240     Q6   240     Q6   240     Q7   240     Q8   240     Q9   240     Q9   240     Q9   240     Q9   240     Q1   240     Q2   240     Q3   240     Q4   240     Q4   240     Q5   240     Q6   240     Q6   240     Q7   240     Q8   240     Q8   240     Q9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | Output accuracy                                            | Output voltage = -5.4 V                                                                       | -1.5% |     | 1.5%            |           |  |

| Q1   350   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240   240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I <sub>LOAD_VNEG_MAX</sub>            | Maximum output current                                     | $V_{LCM\_OUT} = 5.9 \text{ V}, V_{NEG} = -5.4 \text{ V}$                                      | 80    |     |                 | mA        |  |

| RDSON_VNEG   CP FET ON resistance   Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>VNEG_CL</sub>                  | Output current limit                                       |                                                                                               |       | 135 |                 | mA        |  |

| V <sub>VNEG_RIPPLE</sub>   Peak-to-peak ripple voltage <sup>(4)</sup>   N <sub>EG</sub> = -5 mA and -50 mA, C <sub>VNEG</sub> = 10 μF (nominal)   60     V <sub>VNEG_LINE_TRAN</sub>   V <sub>VNEG_IINE_TRAN</sub>   V <sub>NEG_IINE_TRAN</sub>   V <sub>NEG_IINE_TRAN}   V<sub>NEG_IINE_TRAN}   V<sub>NEG_II</sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub></sub>                                                                                                        |                                       |                                                            | Q1                                                                                            |       | 350 |                 |           |  |

| V_NNEG_RIPPLE         Peak-to-peak ripple voltage (4)         I <sub>NEG</sub> = -5 mA and -50 mA, C <sub>VNEG</sub> = 10 μF (nominal)         60           V_NNEG_LINE_TRAN SIENT         VNEG line transient response (4)         V <sub>N</sub> + 500 mV-p - AC square wave, 100 mV-p - AC square wave, 100 mV-p ± 200 Hz, 12.5% duty at 5 mA         −50         ±25         50           V_NNEG_LOAD_TRA NSIENT         V <sub>VNEG</sub> load transient response (4)         V <sub>VNEG</sub> = 10 μF (nominal)         100           V <sub>VNEG</sub> to 50% (4)         V <sub>VNEG</sub> start-up time, V <sub>VNEG</sub> = 10% to 90% (4)         V <sub>VNEG</sub> = -6.5 V, C <sub>VNEG</sub> = 10 μF (nominal)         1           R <sub>VNEG</sub> Output pullup resistor (VNEG to CP_GND) (4)         VNEG pullup in shutdown         6         20           Pulldown resistance on LCM_EN2         Not ATE tested         300         300           PWM INPUT         PWM input frequency (6)         2.7 V ≤ V <sub>IN</sub> ≤ 5 V         50         50000           4-MHz sample rate         183.3         4-MHz sample rate         1100           4-MHz sample rate         1100         1-MHz sample rate         1400           4-MHz sample rate         1100         1-MHz sample rate         1100           4-MHz sample rate         1100         1-MHz sample rate         1100           4-MHz sample rate         1100         1-MHz sample rate         1100           4-MHz sample rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R <sub>DSON_VNEG</sub>                | CP FET ON resistance                                       | Q2                                                                                            |       | 240 |                 | $m\Omega$ |  |

| VNNEG_RIPPLE         Peak-to-peak hipple voltagers         C <sub>VNEG</sub> = 10 μF (nominal)         60           VVNEG_LINE_TRAN SIENT         VNEG line transient response(4)         V <sub>N</sub> + 500 mVp-p AC square wave, 100 mVp-p AC square wave, 12.5% duty at 5 mA         0 to −50 mA step, fkigs_FALL = 1 μs, CVHEG = 10 μF (nominal)         100           VVNEG_LOAD_TRAN SIENT         V <sub>VNEG</sub> start-up time, V <sub>VNEG</sub> = 10% to 90% (4)         V <sub>VNEG</sub> = -6.5 V, C <sub>VNEG</sub> = 10 μF (nominal)         100           feu_vneg         Output pullup resistor (VNEG to CP_GND) (4)         VNEG pullup in shutdown         6         20           Pulldown resistance on LCM_EN2         Not ATE tested         300         300           PWM INPUT         PWM input frequency (6)         2.7 V ≤ V <sub>IN</sub> ≤ 5 V         50         50000           PWM_INPUT         PWM input frequency (6)         2.7 V ≤ V <sub>IN</sub> ≤ 5 V         50         50000           4-MIN_ON         Minimum pulse ON time (4)         24-MHz sample rate         1100         1-MHz sample rate         1100           4-MIN_OFF         Minimum pulse OFF timet (4)         24-MHz sample rate         183.3         4-MHz sample rate         1100           4-MIN_OFF         Turnon delay from PWM = 0 to PWM = 50% duty cycle         4-MHz sample rate         1100         1-MHz sample rate         1100           4-MRES         PWM input glitch rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |                                                            | Q3                                                                                            |       | 240 |                 |           |  |

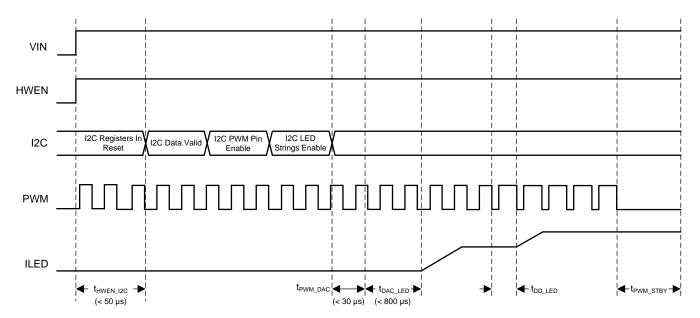

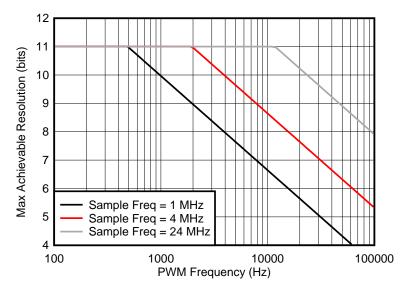

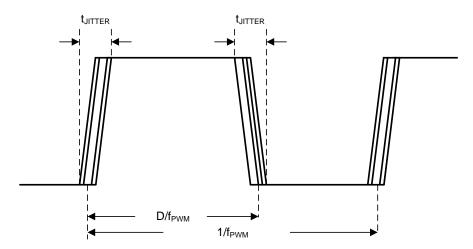

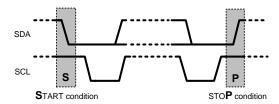

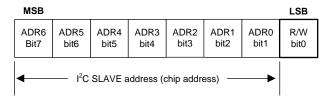

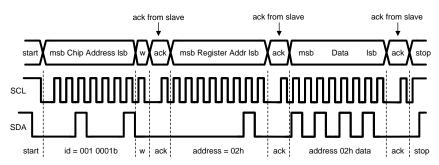

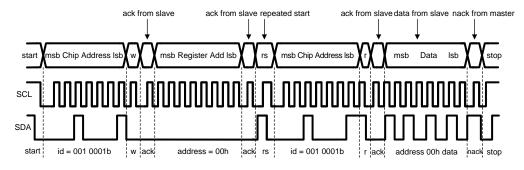

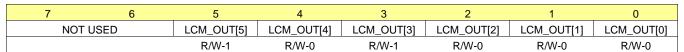

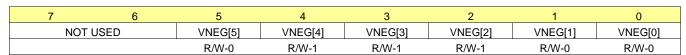

| VNREG_LINE_TRAN   VNEG line transient response (4)   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 200 Hz, 12.5% duty at 5 mA   100 mV/μs 2.7 V ≤ V <sub>IN</sub> ≤ 5 V   1.2 V <sub>IN</sub> 2.7 V ≤ V <sub>IN</sub> ≤ 5 V   1.2 V <sub>IN</sub> 2.7 V ≤ V <sub>IN</sub> ≤ 5 V   1.2 V <sub>IN</sub> 2.7 V ≤ V <sub>IN</sub> 2.7 V ≤ V <sub>IN</sub> 2.5 V   1.2 V <sub>IN</sub> 2.7 V ≤ V <sub>IN</sub> 2.7 V ≤ V <sub>IN</sub> 2.5 V   1.2 V <sub>IN</sub> 2.7 V ≤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $V_{VNEG\_RIPPLE}$                    | Peak-to-peak ripple voltage (4)                            |                                                                                               |       |     | 60              | mVpp      |  |