# TMS470R1x Multi-Buffered Analog-to-Digital Converter (MibADC) Reference Guide

Literature Number: SPNU206B September 2005

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and application s using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different form or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Automotive

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications Amplifiers amplifier.ti.com Audio

Amplifiers amplifier.ti.com

Data Converters dataconverter.ti.com

DSP dsp.ti.com

Interface interface.ti.com

Logic logic.ti.com

Power Mgmt power.ti.com

Microcontrollers microcontroller.ti.com

Broadband www.ti.com/broadband Digital Control www.ti.com/digitalcontrol Military www.ti.com/military Optical Networking www.ti.com/opticalnetwork Security www.ti.com/security Telephony www.ti.com/telephony Video & Imaging www.ti.com/video Wireless www.ti.com/wireless

www.ti.com/audio

www.ti.com/automotive

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

# **REVISION HISTORY**

| REVISION | DATE  | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 9/05  | Table 1: Added ADIN to formula in Results Row, changed 1023 to 1024. Figure 6: Removed the extra "10-bit 2us analog-to-dig" from the block diagram. Page 10: Changed 1023 to 1024 in Eq. 1. Added statement "where " after equation. Figure 11: Added "ADC Core Timing" diagram. Page 28: Changed completely the self-test mode and calibration mode descriptions. Table 9: Changed second column heading. Section 11.4: Rewrote introductory paragraphs to ADEISR register. Section 11.23: Section 11.24, changed register names. Section 11.5, Section 11.6, and Section 11.7: Changed "MibADC" to "ADC" in first paragraph. Section 13: Changed the Analog Input model. |

| А        | 3/04  | Updates: Section 11.12: Updated Bit 4 bit definition. Section 11.12: Added note concerning interrupt handling procedure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *        | 12/02 | Initial version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Contents**

| 1 | Overv  | iew        |                                                                     | 2    |

|---|--------|------------|---------------------------------------------------------------------|------|

|   | 1.1    | Definition | ons                                                                 | 3    |

|   | 1.2    | Feature    | S                                                                   | 3    |

| 2 | Funct  |            | scription                                                           |      |

|   | 2.1    | Detailed   | d MibADC Diagrams                                                   | 7    |

|   | 2.2    | Function   | nal Blocks                                                          | . 10 |

|   |        | 2.2.1      | Input Multiplexer                                                   | . 10 |

|   |        | 2.2.2      | Analog-to-Digital Converter Core                                    | . 10 |

|   |        | 2.2.3      | Conversion Group Selection Registers                                | . 11 |

|   |        | 2.2.4      | Event Edge Detector                                                 | . 12 |

|   |        | 2.2.5      | Event Source Selection                                              | . 13 |

|   |        | 2.2.6      | Self-Test and Calibration Functions                                 | . 14 |

|   |        | 2.2.7      | Offset Error Correction                                             | . 14 |

|   |        | 2.2.8      | Sequencer, Control, and Status Block                                | . 15 |

|   |        | 2.2.9      | Compatibility Mode Prescaler and ADC Timing                         | . 15 |

|   |        | 2.2.10     | MibADC Enhancements to Prescaler and ADC Timing                     | . 16 |

| 3 | Gener  | al Opera   | ation of the MibADC                                                 | . 17 |

| 4 | Progra | ammer C    | Options                                                             | . 18 |

|   | 4.1    | Compat     | tibility Mode                                                       | . 18 |

|   | 4.2    | Buffere    | d Mode                                                              | . 20 |

|   |        | 4.2.1      | Buffer Control Registers                                            |      |

|   |        | 4.2.2      | Interrupt Threshold Registers                                       | . 20 |

|   | 4.3    | Sample     | Time Registers                                                      | . 20 |

|   | 4.4    | Event T    | rigger Enhancements                                                 | . 21 |

|   | 4.5    |            | d Mode Control Registers                                            |      |

|   |        | 4.5.1      | Buffered Mode FIFOs                                                 |      |

|   |        | 4.5.2      | FIFO Channel Identifier                                             | . 24 |

|   |        | 4.5.3      | FIFO 8-Bit Mode                                                     |      |

| 5 | Modes  |            | ration                                                              |      |

|   | 5.1    | Convers    | sion Mode                                                           |      |

|   |        | 5.1.1      | Changing an Input Channel Select Register During a Conversion       |      |

|   |        | 5.1.2      | Changing Input Channel Selections During an Event Conversion        |      |

|   |        | 5.1.3      | Changing Input Channel Selections During a Group 1 or 2 Conversion  | . 27 |

|   | 5.2    |            | st Mode                                                             |      |

|   |        | 5.2.1      | Use of Self-Test Mode to Determine Open/Short on ADC Input Channels | . 30 |

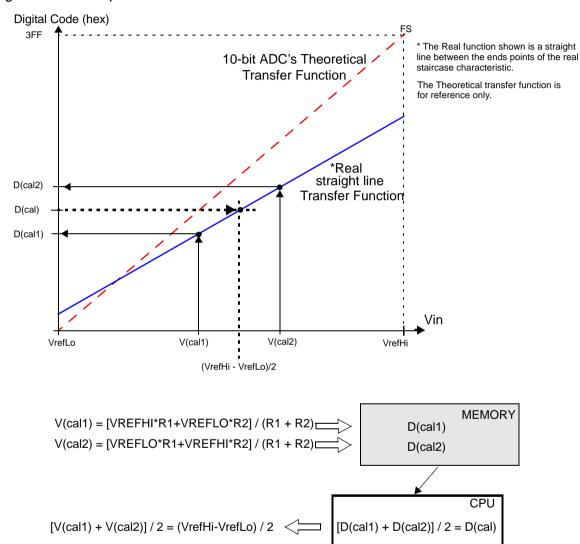

|    | 5.3     | Calibration Mode                                                      | 30  |

|----|---------|-----------------------------------------------------------------------|-----|

|    |         | 5.3.1 Calibration Conversion                                          | 31  |

|    |         | 5.3.2 Calibration and Offset Error Correction Sequences               | 32  |

|    |         | 5.3.3 Mid-Point Calibration                                           | 33  |

|    | 5.4     | Power-Down Mode                                                       | 35  |

| 6  | Conve   | ersion Priority and the Freeze-Enable Bit                             | 36  |

|    | 6.1     | Group Priority                                                        |     |

|    |         | 6.1.1 Simple Priority                                                 |     |

|    |         | 6.1.2 Explicit Conversion Requests and Continuous Conversion Requests |     |

|    |         | 6.1.3 Alternating Conversion of Continuous Groups                     |     |

|    |         | 6.1.4 Example Priority With Freeze                                    |     |

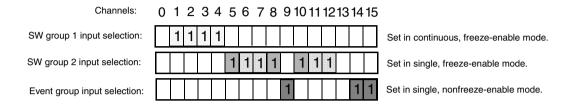

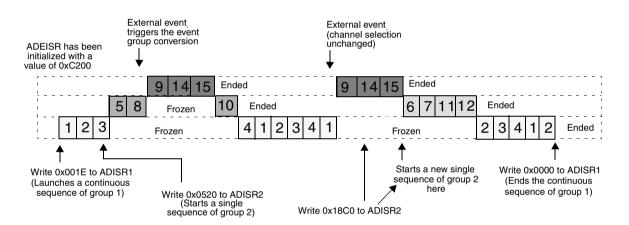

|    | 6.2     | Illustration: Multigroup Conversion Sequence Using Freeze Bits        | 38  |

| 7  | MibAE   | DC FIFO Configuration                                                 |     |

|    | 7.1     | FIFO State Machine                                                    |     |

| 8  | Interru | upt Generation                                                        |     |

|    | 8.1     | Interrupt Generation in Compatibility Mode                            | 43  |

|    | 8.2     | Interrupt Generation in Buffered Mode                                 |     |

|    |         | 8.2.1 Interrupt Threshold Registers                                   | 44  |

| 9  | DMA F   | Request Generation                                                    | 45  |

| 10 | Contro  | ol Registers Summary                                                  | 46  |

| 11 | Detail  | ed Description of Control Registers                                   |     |

|    | 11.1    | AD Control Register 1 (ADCR1)                                         |     |

|    | 11.2    | AD Control Register 2 (ADCR2)                                         | 56  |

|    | 11.3    | AD Status Register (ADSR)                                             |     |

|    | 11.4    | AD Event Group Input Channel Select Register (ADEISR)                 |     |

|    | 11.5    | AD Group 1 Input Channel Select Register (ADISR1)                     |     |

|    | 11.6    | AD Group 2 Input Channel Select Register (ADISR2)                     |     |

|    | 11.7    | Calibration and Offset Error Correction Register (ADCALR)             |     |

|    | 11.8    | Digital Result Registers (ADDR15–ADDR0)                               |     |

|    | 11.9    | Emulation Digital Result Registers (ADEMDR15-ADEMDR0)                 |     |

|    |         | Data Input Register (ADINR)                                           |     |

|    |         | Pin Control Register (ADPCR)                                          |     |

|    |         | AD Event FIFO Buffer (ADBUFE)                                         |     |

|    |         | AD EMU Event FIFO Buffer (ADEMBUFE)                                   |     |

|    |         | AD Group 1 FIFO Buffer (ADBUF1)                                       |     |

|    |         | AD EMU Group 1 FIFO Buffer (ADEMBUF1)                                 |     |

|    |         | AD Group 2 FIFO Buffer (ADBUF2)                                       |     |

|    |         | AD EMU Group 2 FIFO Buffer (ADEMBUF2)                                 |     |

|    |         | AD Buffer Control Register 1 (ADBCR1)                                 |     |

|    |         | AD Buffer Control Register 2 (ADBCR2)                                 |     |

|    |         | AD Buffer Control Register 3 (ADBCR3)                                 |     |

|    | 11.21   | AD Buffer Status Register (ADBUFST)                                   | 9/  |

|    |         | AD Event Group Threshold Counter Register (ADTHREV)                   |     |

|    |         | AD Group 3 Threshold Counter (G3THREV)                                |     |

|    |         | AD Group 2 Threshold Counter (G2THREV)                                |     |

|    | 11.∠5   | AD SAMPLE TIME EVENT REGISTER (ADSAMPLEV)                             | 103 |

|    | 11.26 | AD Sample Time Group 1 Register (ADSAMP1) | 104 |

|----|-------|-------------------------------------------|-----|

|    | 11.27 | AD Sample Time Group 2 Register (ADSAMP2) | 105 |

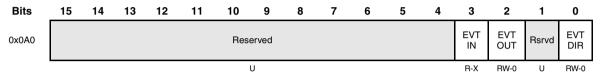

|    | 11.28 | AD Event Source Register (ADEVTSRC)       | 106 |

| 12 | MibAD | OC Timing                                 | 108 |

|    | 12.1  | Sample/Hold Time                          | 108 |

|    | 12.2  | Total Conversion Time                     | 109 |

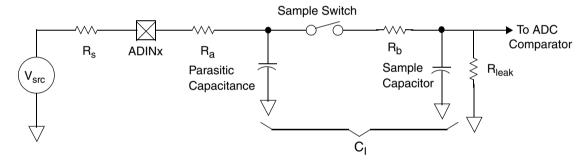

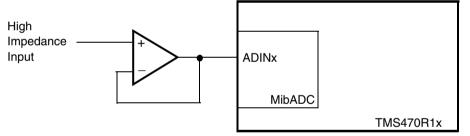

| 13 | Analo | a Input Modelina                          | 111 |

# **Figures**

| 1  | MibADC Block Diagram                                                        | 6    |

|----|-----------------------------------------------------------------------------|------|

| 2  | MibADC Compatibility Mode Functional Block Diagram                          | 8    |

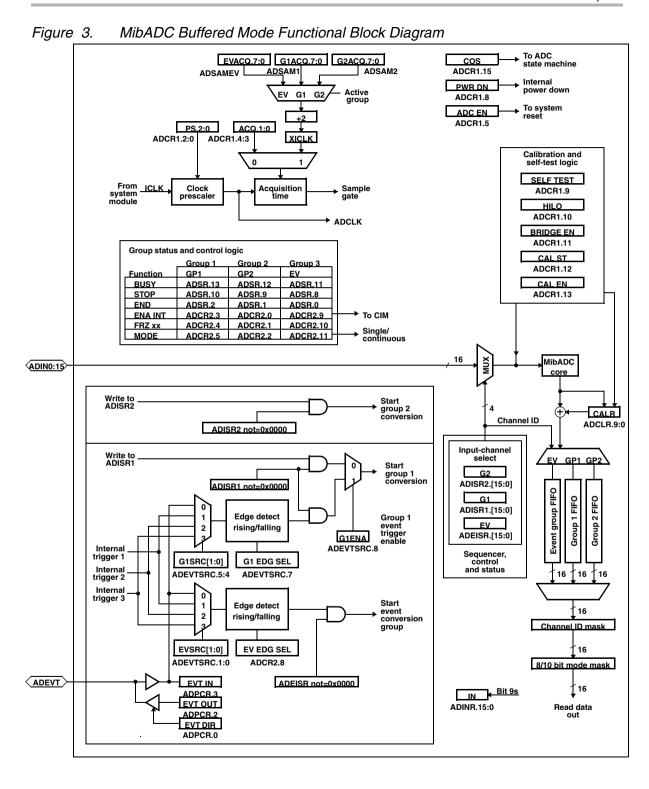

| 3  | MibADC Buffered Mode Functional Block Diagram                               | 9    |

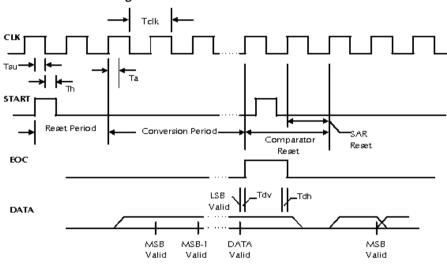

| 4  | ADC Core Timing                                                             | . 11 |

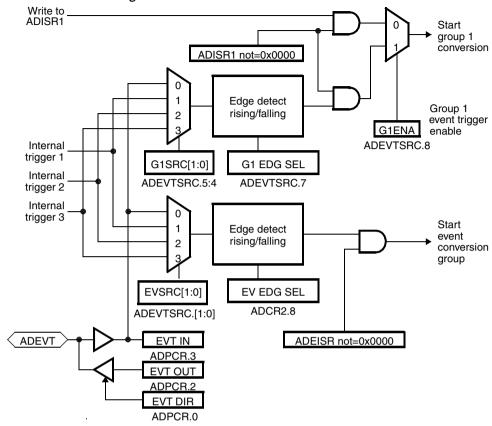

| 5  | ADEVT Pin Block Diagram                                                     | . 14 |

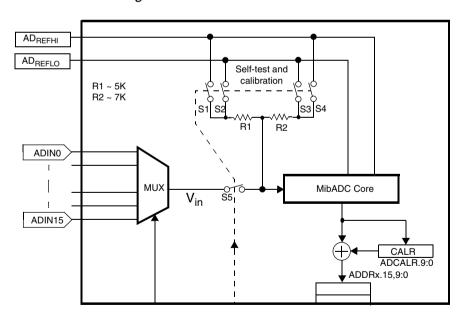

| 6  | Self-Test and Calibration Logic                                             | . 28 |

| 7  | Timing for Self-Test Mode                                                   | . 29 |

| 8  | Mid-point value calculation                                                 | . 34 |

| 9  | Example of Conversion Sequence Using the Three Groups                       | . 38 |

| 10 | FIFO Implementation                                                         | . 40 |

| 11 | FIFO State Machine: State Diagram                                           | . 42 |

| 12 | MibADC Control Registers in Compatibility Mode                              |      |

| 13 | MibADC Control Registers in Buffered Mode                                   | . 48 |

| 14 | MibADC Control Registers Available in Both Compatibility and Buffered Modes |      |

| 15 | AD Control Register 1 (ADCR1)                                               | . 51 |

| 16 | AD Control Register 2 (ADCR2)                                               |      |

| 17 | AD Status Register (ADSR)                                                   |      |

| 18 | AD Event Group Input Channel Select Register (ADEISR)                       | . 66 |

| 19 | AD Group 1 Input Channel Select Register (ADISR1)                           |      |

| 20 | AD Group 2 Input Channel Select Register (ADISR2)                           | . 70 |

| 21 | Calibration and Offset Error Correction Register (ADCALR)                   | . 72 |

| 22 | Digital Result Registers (ADDR15–ADDR0)                                     |      |

| 23 | Emulation Digital Result Registers (ADEMDR15-ADEMDR0)                       |      |

| 24 | Data Input Register (ADINR)                                                 |      |

| 25 | Pin Control Register (ADPCR)                                                | . 78 |

| 26 | AD Event FIFO Buffer (ADBUFE)                                               | . 80 |

| 27 | AD EMU Event FIFO Buffer (ADEMBUFE)                                         |      |

| 28 | AD Group 1 FIFO Buffer (ADBUF1)                                             |      |

| 29 | AD EMU Group 1 FIFO Buffer (ADEMBUF1)                                       |      |

| 30 | AD Group 2 FIFO Buffer (ADBUF2)                                             | . 88 |

| 31 | AD EMU Group 2 FIFO Buffer (ADEMBUF2)               | . 90 |

|----|-----------------------------------------------------|------|

| 32 | AD Buffer Control Register 1 (ADBCR1)               | . 92 |

| 33 | AD Buffer Control Register 2 (ADBCR2)               | . 93 |

| 34 | AD Buffer Status Register (ADBUFST)                 | . 97 |

| 35 | AD Event Group Threshold Counter Register (ADTHREV) | 100  |

| 36 | AD Group 1 Threshold Counter Register (G1THREV)     | 101  |

| 37 | AD Group 2 Threshold Counter Register (G2THREV)     | 102  |

| 38 | AD Sample Time Event Register (ADSAMPEV)            | 103  |

| 39 | AD Sample Time Group 1 Register (ADSAMP1)           | 104  |

| 40 | AD Sample Time Group 2 Register (ADSAMP2)           | 105  |

| 41 | AD Event Source Register (ADEVTSRC)                 | 106  |

| 42 | Input Source and MibADC Model                       | 111  |

| 43 | Driving MibADC Input Channel with Low Impedance     | 112  |

# **Tables**

| 1  | MibADC Module Overview                                                       |

|----|------------------------------------------------------------------------------|

| 2  | Compatibility Mode MibADC Control Registers                                  |

| 3  | Buffered Mode MibADC Control Registers                                       |

| 4  | Self-Test Reference Voltages(1)                                              |

| 5  | Determination of ADC Input Channel Condition                                 |

| 6  | Calibration Reference Voltages†31                                            |

| 7  | AD Control Register 1 (ADCR1) Field Descriptions                             |

| 8  | Reference Voltages Bit Encoding                                              |

| 9  | Acquisition Prescale Value Encoding                                          |

| 10 | Clock Prescale Bits55                                                        |

| 11 | AD Control Register 2 (ADCR2) Field Descriptions                             |

| 12 | AD Status Register (ADSR) Field Descriptions                                 |

| 13 | AD Event Group Input Channel Select Register (ADEISR) Field Descriptions67   |

| 14 | AD Group 1 Input Channel Select Register (ADISR1) Field Descriptions 69      |

| 15 | AD Group 2 Input Channel Select Register (ADISR2) Field Descriptions         |

| 16 | Calibration and Offset Error Correction Register (ADCALR) Field Descriptions |

| 17 | Digital Result Registers (ADDR15–ADDR0) Field Descriptions                   |

| 18 | Emulation Digital Result Registers (ADEMDR15-ADEMDR0) Field Descriptions     |

| 19 | Data Input Register (ADINR) Field Descriptions77                             |

| 20 | Pin Control Register (ADPCR) Field Descriptions                              |

| 21 | AD Event FIFO Buffer (ADBUFE) Field Descriptions                             |

| 22 | AD EMU Event FIFO Buffer (ADEMBUFE) Field Descriptions                       |

| 23 | AD Group 1 FIFO Buffer (ADBUF1) Field Descriptions                           |

| 24 | AD EMU Group 1 FIFO Buffer (ADEMBUF1) Field Descriptions                     |

| 25 | AD Group 2 FIFO Buffer (ADBUF2) Field Descriptions                           |

| 26 | AD EMU Group 2 FIFO Buffer (ADEMBUF2) Field Descriptions                     |

| 27 | AD Buffer Control Register 1 (ADBCR1) Field Descriptions92                   |

| 28 | AD Buffer Control Register 2 (ADBCR2) Field Descriptions93                   |

| 29 | AD Buffer Control Register 3 (ADBCR3) Field Descriptions94                   |

| 30 | AD Buffer Control Register 3 (ADBCR3) Field Descriptions97                   |

| 31 | AD Event Group Threshold Counter Register (ADTHREV) Field Descriptions | 100 |

|----|------------------------------------------------------------------------|-----|

| 32 | AD Group 1 Threshold Counter Register (G1THREV) Field Descriptions     | 101 |

| 33 | AD Group 2 Threshold Counter Register (G2THREV) Field Descriptions     | 102 |

| 34 | AD Sample Time Event Register (ADSAMPEV) Field Descriptions            | 103 |

| 35 | AD Sample Time Group 1 Register (ADSAMP1) Field Descriptions           | 104 |

| 36 | AD Sample Time Group 2 Register (ADSAMP2) Field Descriptions           | 105 |

| 37 | AD Event Source Register (ADEVTSRC) Field Descriptions                 | 106 |

# Multi-Buffered Analog To Digital Converter (MibADC)

This reference guide discusses the features, operation, specifications, and initialization of the TMS470R1VX 16-channel, multibuffered, 10-bit analog-to-digital converter (MibADC). The analog converter uses 10-bit sampling, successive approximation register-based architecture. The upper four bits are converted using a switched capacitor charge redistribution technique; the lower six bits are derived from a voltage-scaled reference (resistor string between  ${\rm AD}_{\rm REFHI}$  and  ${\rm AD}_{\rm REFLO}$ ). The buffered MibADC functions in compatibility mode or in buffered mode.

| Topi | Topic Page                                    |     |

|------|-----------------------------------------------|-----|

| 1    | Overview                                      | 2   |

| 2    | Functional Description                        |     |

| 3    | General Operation of the MibADC               | .17 |

| 4    | Programmer Options                            | .18 |

| 5    | Modes of Operation                            | .25 |

| 6    | Conversion Priority and the Freeze-Enable Bit | .36 |

| 7    | MibADC FIFO Configuration                     | .40 |

| 8    | Interrupt Generation                          | .43 |

| 9    | DMA Request Generation                        | .45 |

| 10   | Control Registers Summary                     | .46 |

| 11   | Detailed Description of Control Registers     | .51 |

| 12   | MibADC Timing                                 | 108 |

| 13   | Analog Input Modeling                         | 111 |

# 1 Overview

This section provides an overview of the MibADC module. Table 1 contains a brief description of the MibADC, lists its significant pins, describes the priority scheme and interrupts, how conversions are triggered, and the expected results of the conversion.

Table 1. MibADC Module Overview

| Description            | The analog-to-digital converter accepts an analog signal and converts it to a 10-bit digital value. Typical uses include converting a sensor voltage to a digital value for digital manipulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pins                   | V <sub>CCAD</sub> : Analog-to-digital converter power V <sub>SSAD</sub> : Analog-to-digital converter ground AD <sub>REFHI</sub> : Analog-to-digital converter high reference. Any signal with a voltage higher than AD <sub>REFHI</sub> is recorded as 0x3FF. AD <sub>REFHI</sub> ≤V <sub>CCAD</sub> . AD <sub>REFLO</sub> : Analog-to-digital converter low reference. Any signal with a voltage lower than AD <sub>REFLO</sub> is recorded as 0x00. AD <sub>REFLO</sub> ≥V <sub>SSAD</sub> . ADIN[15:0]: Analog-to-digital converter input channels. (A device can have up to 16 input channels.) ADEVT: Analog-to-digital event trigger. Signals on this line can trigger a group conversion. Internal Event Triggers: In addition to the ADEVT pin, the MibADC includes three additional event triggers from internal sources, for example, internal timers. |

| Priority               | Within a group, the lowest channel has priority over higher channels. The group priority is event group (highest), group 1, and group 2 (lowest); this group priority takes effect when groups are started simultaneously. When a second group is triggered while another group is being converted, the group being converted finishes conversion and then the second group begins its conversion; if the first group is freeze enabled, the second group interrupts the conversion of the first group.                                                                                                                                                                                                                                                                                                                                                           |

| Programmer's<br>Models | Compatibility Mode: Programmer's model is compatible with the TMS470R1X ADC module. Conversion results are stored in digital result registers.  Buffered Mode: Digital result registers are replaced with three FIFO buffers, one for each conversion group. Buffers can be serviced by interrupts or by DMA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operating<br>Modes     | Conversion Mode: Normal active mode for converting analog input pins Calibration Mode: Active mode for calibrating out the midpoint offset error of the MibADC. Self-test Mode: Active mode for detection of faults on the analog input pins. Power-down Mode: Inactive mode for low power consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Interrupts             | Interrupt request of each group can be individually enabled. Buffered mode provides an interrupt threshold counter for FIFO buffer of each group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DMA Capability         | Three DMA channels. The MibADC can be serviced by DMA in buffered mode only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Table 1. MibADC Module Overview (Continued)

For the event group, the external trigger on the ADEVT pin triggers the conversion (after ADEISR is initialized). Optionally, events can be triggered from an internal timer.

For groups 1 and 2, writing to the ADISR1 or ADISR2 (other than 0x00) initiates the group conversion.

Group 1 can also be event triggered.

| Results | Input Voltage on the ADINx Pin                                            | Value in the Digital Result Register (DRR)                                            |

|---------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|         | Input voltage between maximum recommended voltage and AD <sub>REFHI</sub> | 0x3FF                                                                                 |

|         | Input voltage for $AD_{REFHI} > ADIN \ge AD_{REFLO}$ .                    | $\approx \frac{1024 \times (Input\_Voltage - AD_{REFLO})}{(AD_{REFHI} - AD_{REFLO})}$ |

|         | Input voltage between AD <sub>REFLO</sub> and minimum recommended voltage | 0x00                                                                                  |

#### 1.1 Definitions

The following define some of the important terminology used in this document.

- ☐ Sample and hold—Internal capacitor array that averages the signal over the acquisition time.

- ☐ AD clock period:

$$t_{c(ADCLK)} = t_{c(ICLK)}*PS.2:0$$

#### 1.2 Features

The MibADC module converts analog voltages to 10-bit digital values; the module includes internal sample-and-hold circuitry capable of sampling one of the sixteen analog inputs at a time. A sequencer controls the order and the timing of conversions, with input channels organized in three conversion groups. Each input channel may be assigned to one or more of the conversion groups.

The conversion groups may be configured for either in single or continuous conversion modes. Each of the conversion groups may be triggered by software, and two of the three conversion groups may be event triggered. The

event is selectable for each group from one of four sources; three internal sources (from timer modules on the same device) and one MibADC controlled pin (ADEVT).

The result of conversions are stored in either in individual digital result registers (compatibility mode) or in three FIFOs (buffered mode) where each FIFO holds the results from one of the conversion groups.

The module supports interrupts in a flexible manner as described in section 8, *Interrupt Generation*. In addition, the module supports DMA accesses in buffered mode.

The main features of the MibADC include:

- □ 10-bit resolution

- □ AD<sub>REFHI</sub> and AD<sub>REFLO</sub> pins (high and low reference voltages)

- ☐ Total Sample/Hold/Convert time: 1.75 μs Typical Minimum (see datasheet)

- ☐ Two programmer's models (select one or the other)

- Unbuffered (compatibility):

- The programmer's model matches the TMS470R1x ADC module.

- One digital result register is available for each of the 16 MibADC channels.

- Results are stored in two-port RAM (some RAM unused).

- Data is organized by channel number.

#### ■ Buffered:

- The programmer's model is MibADC with three FIFO buffers.

- One FIFO buffer per conversion group is available (event, group 1, group 2).

- The size of FIFO buffers is adjustable because allocation of channels to conversion groups is completely programmable.

- The FIFO is serviced either by interrupt or by DMA.

- A programmable interrupt threshold counter is available for each FIFO.

- An option is available to store channel ID with data in FIFO mode for enhanced robustness.

- An option is available to read from FIFO as either 8-bit or 10-bit value. Saves shift operations for software using only the eight MSBs of the conversion result.

| ш | There are sequential multichannel conversions (up to 16 channels in ascending order).                                                                                                                                   |  |  |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   | Single or continuous conversion modes are available.                                                                                                                                                                    |  |  |  |

|   | One or two software-controlled conversions are available: up to 16 channels converted on a software request.                                                                                                            |  |  |  |

|   | One or two event-initiated conversions are available: up to 16 channels converted on an external event or internal timer event.                                                                                         |  |  |  |

|   | The MibADC is interrupt driven, DMA driven (buffered mode only), or polled operation (end-of-conversion sequence).                                                                                                      |  |  |  |

|   | A prrogrammable MibADC clock prescaler (ADCLK) to optimize conversion rate is available.                                                                                                                                |  |  |  |

|   | Each conversion group has a programmable acquisition time:                                                                                                                                                              |  |  |  |

|   | ■ If SEN (ADSAMPEV.15 is 0, then for compatibility with ADC, the MibADC sample time is determined by ACQ.1:0 (ADCR1.4:3)                                                                                                |  |  |  |

|   | ■ If SEN (ADSAMPEV.15) is set to 1, then the sample time for each group is programmable and controlled by EVACQ.7:0 (ADSAMPEV.7:0) for the event group, G1ACQ.7:0 for group 1, and G2ACQ.7:0 (ADSAMP2.7:0) for group 2. |  |  |  |

|   | The MibADC has an embedded self-test.                                                                                                                                                                                   |  |  |  |

|   | The MibADC has embedded calibration logic.                                                                                                                                                                              |  |  |  |

|   | Power-down mode can be used.                                                                                                                                                                                            |  |  |  |

|   | The external event pin (ADEVT) is programmable as general-purpose I/O.                                                                                                                                                  |  |  |  |

|   | Three device-specific internal timer events are available.                                                                                                                                                              |  |  |  |

|   |                                                                                                                                                                                                                         |  |  |  |

# 2 Functional Description

This section presents a general discussion of the components and operation of the TMS470 10-bit MibADC. Figure 1 illustrates the components of the MibADC module.

MibADC Block Diagram Figure 1. **A**DREFHI A<sub>DREFLO</sub> Self-test and calibration S1 S2 S3 **S4** R1 R2 ADIN0 nput MUX 10-bit 2 μs analog-to-digi-16-to-1 10 FIFO empty 10 ADIN15 Channel identifier Sequencer, control, DMA ADEVT GIO control 16 digital results registry or 3 FIFOs (buffer mode) request and status ΕV (buffer G1 mode) Event logic Prescaler and timing event group and 16 group 1 Interrupt threshold Conversion group Channel ID mask select register 8/10 bit mode mask  $V_{CCAD}$ Interrupt 16  $V_{SSAD}$ threshold counters Group 1 DMA request **Event DMA request** Group 1 INT reg. Group 2 INT req Event INT req. Internal 1 Internal 3 Internal Expansion bus

From internal sources (HET, EVM, timers)

# 2.1 Detailed MibADC Diagrams

The expanded MibADC diagram in Figure 2 shows compatibility mode in more detail; Figure 3 shows buffered mode in more detail. Inside the group status and control logic block is a matrix of function versus group register bits. As an example, the STOP bit of group 2 is in the ADSR register, bit 9.

To state machine G1ACQ.7: G2ACQ.7: cos ADSAM2 ADSAM1 ADSAMEV ADCR1.15 Inter-power down PWR Active E۷ G1 ADCR1.8 group To sys-reset ADC ADCR1.5 ACQ.1:0 PS.2:0 ADCR1.2: ADCR1.4: Calibration and self-test log-SELF TEST From system module ADCR1.9 ICLK Clock Acquisi-Sample prescaltime HILO ADCR1.1 ADCLK BRIDGE EN ADCR1.1 Group status and control CAL Group Group Group ADCR1.12 GP1 GP2 ΕV Func ADSR.11 CAL BUS ADSR.13 ADSR.12 STO ADSR.10 AD-AD-ADCR1.13 ADSR.1 END AD-AD-FΝΔ ADCR2.3 ADCR2.0 ADCR2.9 To CIM ADCR2.4 ADCR2.1 ADCR2.1 FRZxx Sin-MOD ADCR2.5 ADCR2.2 ADCR2.1 continuous Ϋ́ 16 Mi-ADIN0:15 core Write ADISR CAL group conver-ADCALR.9:0 ADISR2 ADDR Input-channel ADDR Write ADISR MDR ADDR Start MDR G2 ADDR group conversion MDR ADISR2.[15:0] ADDR ADISR1 MDR ADDR G1 EMDR ADDR ADISR1.[15:0] MDR ADDR Edge detect Group 1 MDR F۷ ADDR 2 rising/falling event trigger ADEISR.[15:0] MDR ADDR G1FN EMDR ADDR1 Inter-trigger ADEVTSRC.8 MDR Sequencer, ADDR1 G1SRC[1:0] G1 EDG con-and sta-MDR1 ADDR1 Inter-ADEVTSRC.5: ADEVTSRC. MDR1 ADDR1 MDR1 ADDR1 Inter-ADDR15 MDR1 trigger Edge detect Start ADEMDR1 event conversion rising/falling ADFMDR1 2 ADEMDRx.15,9:0 16 EV EDG SEL EVSRC[1:0] ADEVTSRC.1: ADCR2.8 16 Channel ID mask ADEV EVT IN ADEISR not=0x0000 16 ADPCR.3 8/10 bit mode mask FVT ADPCR.2 IN Bit 9s 1 16 **FVT DIR** ADPCR.0 Read ADINR.15:0

Figure 2. MibADC Compatibility Mode Functional Block Diagram

#### 2.2 Functional Blocks

This section contains a functional description of each block in the MibADC (see Figure 1 and Figure 3).

# 2.2.1 Input Multiplexer

The input multiplexer (MUX) connects the selected input channels (pins ADIN[15:0]) to the input  $V_{in}$  of the analog converter core (Figure 1). The selected input channel is determined by the conversion group that has priority. The channels chosen for conversion are programmed into one or more of the three conversion group selection registers: group 1 input-select register (ADISR1), group 2 input-select register (ADISR2), or the event group input-select register (ADEISR).

### 2.2.2 Analog-to-Digital Converter Core

The MibADC core has a separate power bus ( $V_{CCAD}$  and  $V_{SSAD}$ ) for its analog circuitry. This power bus enhances MibADC performance by reducing digital switching noise present on the digital power lines ( $V_{CC}$  and  $V_{SS}$ ), which can couple into the MibADC analog stage.

The converter core uses a 10-bit sampling, successive approximation type architecture. The analog conversion range is determined by the reference voltages:  $\mathsf{AD}_\mathsf{REFHI}$  (high reference voltage) and  $\mathsf{AD}_\mathsf{REFLO}$  (low reference voltage). These voltages are, respectively, the maximum and the minimum voltages that can be converted. Both  $\mathsf{AD}_\mathsf{REFHI}$  and  $\mathsf{AD}_\mathsf{REFLO}$  must be chosen not to exceed the analog power supplies (VCCAD and VSSAD).

Analog input voltages greater than  $AD_{REFHI}$  are converted to 0x3FF; input voltages less than  $AD_{REFLO}$  are converted to 0x000. Voltages between  $AD_{REFHI}$  and  $AD_{REFLO}$  produce a conversion result that is proportional to the difference of [ $AD_{REFHI}$  –  $AD_{REFLO}$ ]. The digital result of the conversion process is approximated by Equation 9:

$$DigitalResult = \frac{1024xInputVoltage - ADREFLO}{(ADREFHI - ADREFLO)}$$

(EQ 1)

where  $AD_{REFHI} > ADIN \ge AD_{REFLO}$ . If  $ADIN \ge AD_{REFHI}$ , the conversion result will be 0x3FF.

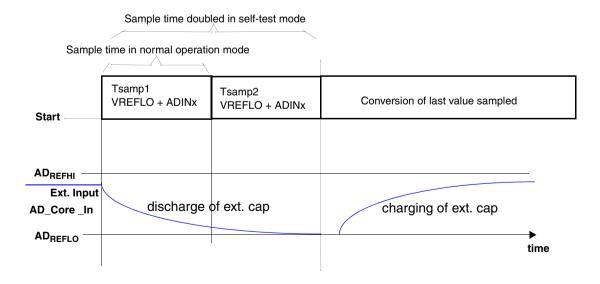

The MibADC acquisition period starts when either ADISR1 or ADISR2 is written with non-zero data, or when an event trigger initiates an event-triggered group. The acquisition bits should be programmed to

guarantee that the sample-and-hold circuitry has time to adequately sample the input voltage (see section 12.1, *Sample/Hold Time*). During this acquisition time, the converter stage is maintained in its reset state. The input signal is sampled directly onto the switched capacitor array, which provides an inherent sample-and-hold function.

When the acquisition time has elapsed, the converter reset is released, which allows the conversion of the sampled voltage to start. The ADC core is synchronized with the internal ADC clock (ADCLK). See section 12.2, *Total Conversion Time*. The digital result is determined one bit at a time, starting with the most significant bit (MSB). When all channels within a group have been converted, the group end (xx END) flag is set, and the digital result is then available in the corresponding digital result register.

Figure 4. ADC Core Timing

# 2.2.3 Conversion Group Selection Registers

The MibADC module can preset three groups of channels to be converted (always from lowest selected channel to highest). The input-select register 1 (ADISR1), input-select register 2 (ADISR2), and the event input-select register (ADEISR) define the channels associated with a conversion group. Any channel can be selected in any group. The same channel can be selected in more than one group.

#### **Note: Channels in Conversion Groups**

The logic circuitry does not prevent selecting the same channel in more than one group. A channel is converted for each group conversion in which it is selected. It is also possible to select all channels or no channels within a group.

The channels are fully controlled by software. Any write from the CPU to group 1 (ADISR1) or group 2 (ADISR2) with a value other than 0x0000 configures and starts the conversion of that group. ☐ Group 1 (ADISR1) can be either software-triggered or event-triggered. If group 1 is selected for event trigger, then conversion of this group begins when the event trigger occurs, not when ADISR1 is written as described above. When it is configured by software, the third group (EVT) is triggered by an external event at the ADEVT pin or from an internal timer. For each group, the control register ADCR2 defines the following attributes: □ Conversion mode: single or continuous (See Section 5.1, Conversion Mode.) □ Conversion arbitration level (finishes or freezes the current conversion sequence when another group conversion starts) (See Section 6, Conversion Priority and the Freeze-Enable Bit.) ☐ Interrupts to the CPU (See Section 8, *Interrupt Generation*.)

#### **Note: Continuous Conversion for Multiple Groups**

The software-controlled group 1 (G1), group 2 (G2), and the event-triggered group cannot operate together in continuous conversion mode. When this situation occurs, group 2 is automatically reset to single conversion mode, and the G2 MODE bit (ADCR2.2) is cleared to reflect the actual conversion mode of group 2.

# 2.2.4 Event Edge Detector

The ADEVT pin is intended to start an event group conversion from an external trigger signal; however, if the ADEVT pin is not used to launch an event-controlled conversion, it can be used as a digital input/output function through the ADPCR register. If the application needs to use the ADEVT pin as a general-purpose I/O, then it should be noted that any edge on the

ADEVT pin, even when created by software using the ADEVT pin as digital I/O, can trigger the event group.

If the application is not designed to trigger the event group when software toggles the ADEVT pin, the two options are:

- ☐ Program the ADEISR register to 0x0000 to disable the event group.

- ☐ Program the event group for one of the other event sources in the ADEVTSRC register.

When the ADEISR register is not 0x0000 and the event that is selected by EVSRC.1:0 (ADEVTSRC.1:0) occurs, all channels selected in the event group register (ADEISR) are sequentially converted (from lowest to highest). The edge that starts a conversion can be selected as a low-to-high or a high-to-low transition; this selection is configured through the event edge select bit, EV EDG SEL (ADCR2.8).

When group 1 is selected for event trigger by G1ENA (ADEVTSRC.8), conversion is similar to that of the event group described above. The event source for group 1 is selected by G1SRC.1:0 (ADEVTSRC.5:4) and the edge polarity for this event is selected by G1EDGESEL (ADEVTSRC.7).

# **Tip: Software Trigger for Event Group**

The ADEVT pin, configured as an output by setting EVT DIR (ADPCR.0) to 1, can be used to initiate a conversion of the event group by toggling the EVT OUT bit (ADPCR.2) to create the appropriate edge at the ADEVT pin. See Figure 5.

On reset, the pin is initialized as input (EVT DIR = 0), and the ADEISR register is 0x0000.

#### 2.2.5 Event Source Selection

A new feature of the TMS470R1VX buffered MibADC is that the event group and group 1 can be programmed to trigger a conversion based upon one of these internal event sources in addition to an edge on the ADEVT pin. Typically, these internal sources originate from timers on the device. (For more detailed information, see section 11.28, *AD Event Source Register (ADEVTSRC)*.)

Figure 5. ADEVT Pin Block Diagram

#### 2.2.6 Self-Test and Calibration Functions

The MibADC includes specific hardware for detecting an ADC pin failure and supporting the application program during the calibration phase. This function is initiated when self-test mode or calibration operations are enabled through the ADCR1 control register. See section 5.2, *Self-Test Mode* for additional information.

#### 2.2.7 Offset Error Correction

The offset error correction block adjusts the digital result output from the ADC core before storing the data in the digital result register frame. See section 5.3, *Calibration Mode*, for additional information.

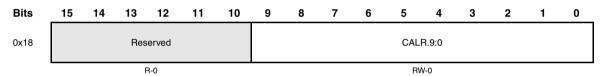

A dedicated 10-bit read/write register ADCALR (calibration and correction register) collects the calibration data and stores the offset error correction value generated by user software. During calibration operations, the CPU reads the ADCALR register to acquire the calibration data and compute an

offset error correction value. At the end of calibration operations, the CPU writes the computed offset error correction value to the ADCALR register.

The ADCALR register and an adder provide an offset cancellation mechanism. This automatic correction is enabled in noncalibration mode only. The digital result output from the ADC core is added to the contents of the ADCALR register before it is stored in the digital result register frame in compatibility mode, or before it is stored in the FIFO in buffered mode.

#### Note: Store Error Correction Value in Correct Form.

Always store the calculated offset error correction value in ADCALR in 2s complement form.

#### 2.2.8 Sequencer, Control, and Status Block

The sequencer, control, and status block coordinates the operations of the MibADC, including the input multiplexer, the converter, and the result registers. In addition, the logic of the sequencer sets the status register flags when the conversion is ongoing (G1 BUSY, G2 BUSY, or EV BUSY), stopped (G1 STOP, G2 STOP, or EV STOP), or finished (G1 END, G2 END, or EV END).

The logic controls handshaking within the three conversion groups and handles CPU read/write operations, interrupts, halts, resets, and addressing within the module. The logic in this block also supports self-test mode and calibration operations. This logic block generates the internal ADC clock that controls ADC timing.

In buffered mode, this block is responsible for buffer management, overflow detection, and generation of DMA requests.

# 2.2.9 Compatibility Mode Prescaler and ADC Timing

The MibADC applies a prescaler value, PS.2:0 (ADCR1.2:0) to ICLK to derive an ADC clock (ADCLK) period,  $t_{c(ADCLK)}$ . The total time required for acquisition and conversion is a function of ICLK, the prescaler value, and the acquisition period selections.

An acquisition prescaler selection, ACQ.1:0 (ADCR1.4:3) is provided so the MibADC acquisition time can be increased for sources with greater than 10-ohm source impedance. After the acquisition time, changing the analog input does not affect the conversion result.

See section 12.1, Sample/Hold Time, and section 12.2, Total Conversion Time.

#### **Note: ADCLK Period Parameters**

The electrical specifications and timing requirements for the analog core on TMS470R1Vx devices are different than those on TMS470R1x devices because of the different process used. Always check the electrical specifications in your device's data sheet to verify that your application meets the MibADC specifications.

#### 2.2.10 MibADC Enhancements to Prescaler and ADC Timing

The MibADC provides the option to program the sample time for each conversion group: ADSAMPEV, ADSAMPG1, and ADSAMPG2. For compatibility with ADC, the MibADC defaults to use ACQ.1:0 (ADCR1.4:3) to determine the sample time for all three groups. To make the MibADC use the new register to control sample time, the SEN bit (ADSAMPEV.15) must be set. When this bit is set, ACQ.1:0 (ADCR1.4:3) is ignored and the extension registers ADSAMPEV, ADSAMPG1, and ADSAMPG2 control the sample time.

# 3 General Operation of the MibADC

The MibADC is relatively autonomous after it is correctly initialized (see Figure 1). The internal clock frequency and acquisition time must be set, the channels to be converted must be stored in at least one group select register, and as an option, the interrupt control bits can be programmed. The conversion can then be triggered by hardware or software, and the data from each converted channel can be read by the CPU after the interrupt signals an end-of-conversion. In addition to this simple operation, the hardware provides for more complex operations:

| Real-time failure detection                           |

|-------------------------------------------------------|

| Calibration through sequences implemented in software |

| Self-offset error correction                          |

The two operational modes (single or continuous conversion) associated with three groups of channel selection enable conversion of multiple combinations of sets of channels without CPU accesses. This feature reduces the amount of software overhead required.

The TMS470R1Vx peripheral clock, ICLK, is divided down by a programmable prescaler to produce ADCLK. The prescaler value controls the total conversion time.

The self-offset error corrected digital data values are stored in either the 16bit digital results register or in three FIFOs, depending on whether the device is in compatibility mode or buffered mode.

# 4 Programmer Options

Two programming options are available for the MibADC module. You can select compatibility mode or buffered mode of operation.

# 4.1 Compatibility Mode

In compatibility mode, the MibADC programmer's model is exactly the same as the TMS470R1X ADC module. All control registers below offset 0xA0 maintain their present definition. The MibADC control registers appear to the programmer as listed in Table 2.

## Note: MibADC / ADC Compatibility

Although the TMS470R1VX MibADC and TMS470R1X ADC modules share the same programmer's model and are software compatible when the MibADC is in the default compatibility mode, the electrical specifications and timing requirements of the analog core on TMS470R1Vx devices are different because of process differences. Before migrating from the TMS470R1x ADC to the TMS470R1Vx MibADC, always verify by consulting the TMS470R1Vx device datasheet that the MibADC electrical specifications and timing requirements of the TMS470R1Vx MibADC are met by your application.

# Note: MibADC / Compatibility Mode II

A common question that arises is whether compatibility mode features are disabled in buffered mode, or whether buffered mode features are available in compatibility mode. In general, unless otherwise specified, it is left to the software to not use compatibility mode features in buffered mode and viceversa (rather than a hardware lock-out). For example, it is possible to enable interrupts after the end of a conversion group in buffered mode (using ADCR2). However, this is not the intended use—in buffered mode, interrupts are intended to be generated by the interrupt threshold registers (ADTHREV, ADTHRG1, ADTHRG2) and the interrupt enables in the buffer control register (ADBCR3). Again, it is left to the programmer to enable interrupts that are consistent with the mode in which the MibADC is being used.

Table 2. Compatibility Mode MibADC Control Registers

| Address        | Mnemonic             | Name                                               | Description                                                                             |

|----------------|----------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|

| 0x00           | ADCR1                | Control register 1                                 | Contains control bits for initiating and controlling calibration and conversions        |

| 0x04           | ADCR2                | Control register 2                                 | Contains control bits for initiating and controlling modes and events                   |

| 0x08           | ADSR                 | Status register                                    | Contains flags showing the status of conversion activities                              |

| 0x0C           | ADEISR               | Event group input-<br>channel select register      | Selects channels to be converted by the event group                                     |

| 0x10           | ADISR1               | Group 1 input-channel select register              | Selects channels to be converted by group 1                                             |

| 0x14           | ADISR2               | Group 2 input-channel select register              | Selects channels to be converted by group 2                                             |

| 0x18           | ADCALR               | Calibration and offset error correction register   | Holds calibration data from ADC core                                                    |

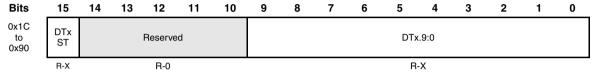

| 0x1C -<br>0x98 | ADDR15-<br>ADDR0     | Digital results registers<br>(15 through 0)        | Contains status flag and digital result of associated channel                           |

| 0x20 ~<br>0x98 | ADEMDR15-<br>ADEMDR0 | Emulation digital results registers (15 through 0) | Mirrors values in ADDR0-15 registers but is not cleared by a read                       |

| 0x9C           | ADINR                | Data input register                                | Contains bit 9 of the digital results registers, ADDR[15:0], of each of the 16 channels |

| 0xA0           | ADCPCR               | Pin control register                               | Contains digital value of current level on ADEVT pin and pin control bits               |

| 0xB0           | ADSAMPEV             | Sample Control Register Event                      | Event group sample time                                                                 |

| 0xB4           | ADSAMP1              | Sample Control Register 1                          | Group 1 sample time                                                                     |

| 0xB8           | ADSAMP2              | Sample Control Register 2                          | Group 2 sample time                                                                     |

| 0xBC           | ADBCR1               | Buffer Control Register 1                          | Buffer enable/disable, allocation                                                       |

| 0xC0           | ADBCR2               | Buffer Control Register 2                          | Buffer end pointer/size control                                                         |

| 0xC4           | ADBCR3               | Buffer Control Register 3                          | Buffer DMA and interrupt enable bits                                                    |

| 0xC8           | ADBST                | Buffer Status Register                             | Buffer empty, overrun, and interrupt flags                                              |

| 0xCC           | ADTHREV              | Event Group Interrupt Threshold                    | Sets fill level of event group FIFO before interrupt generated                          |

| 0xD0           | ADTHRG1              | Group 1 Interrupt Threshold                        | Sets fill level of group 1 FIFO before interrupt generated                              |

|                |                      |                                                    |                                                                                         |

Table 2. Compatibility Mode MibADC Control Registers (Continued)

| Address | Mnemonic | Name                        | Description                                                                                                                |

|---------|----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 0xD4    | ADTHRG2  | Group 2 Interrupt Threshold | Sets fill level of group 2 FIFO before interrupt generated                                                                 |

| 0xD8    | ADEVTSRC | Event Source Register       | Selects extended event trigger sources for ADEVT group and group 1, and enables group 1 to act as an event triggered group |

#### 4.2 Buffered Mode

You can also select the buffered mode of operation in which conversion results are stored in FIFOs instead of the results registers. Table 3 lists the buffered mode control registers.

#### 4.2.1 Buffer Control Registers

The three buffer control registers control the operation of the device in buffered mode. They provide the following control bits:

- ☐ Control bit that switches between compatibility and buffered modes

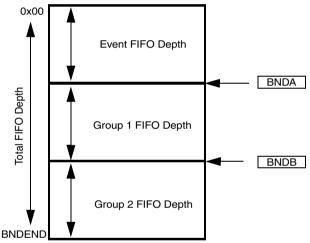

- ☐ Boundary registers that determine the allocation of the total available FIFO memory between the three MibADC conversion groups

- Interrupt bits

- DMA control and status bits

## 4.2.2 Interrupt Threshold Registers

For each of the three FIFOs, the interrupt threshold (i.e., the number of sample/conversion results stored in the FIFO before an interrupt to the CPU is generated) is programmable. This feature may significantly reduce the CPU load caused by MibADC interrupts by reducing the interrupt rate.

# 4.3 Sample Time Registers

The programmer's model includes a separate sample time register for each MibADC conversion group. When enabled, these registers override the global sample time programmed into control register 1 (ADCR1.4-3). In compatibility mode, these registers can also be enabled to take advantage of the updated sampling time without changing the storage scheme for conversion result.

- ☐ If SEN (ADSAMPEV.15) is 0, then for compatibility with ADC, the MibADC sample window (SW) is determined by ACQ.1:0 (ADCR1.4:3).

- ☐ If SEN (ADSAMPEV.15) is set to 1, then the sample window (SW) for each group is programmable and controlled by EVACQ.7:0 (ADSAMPEV.7:0) for the event group, G1ACQ.7:0 for group 1, and G2ACQ.7:0 (ADSAMP2.7:0) for group 2.

# 4.4 Event Trigger Enhancements

A new feature of the MibADC is that group 1 and the event group have the option to be event triggered, which produces a maximum of two event-triggered groups. A multiplexer allows the event source for both group 1 and the event group to be independently selected from either internal timers or the ADEVT pin.

Programming group 1 for event-triggered mode does not change its priority with respect to other groups when multiple groups are ready to be converted. It simply changes the behavior of group 1 so that group 1 is not ready to be converted immediately after ADISR1 is written; rather, it is ready for conversion only after the event which is programmed to trigger group 1 occurs.

The arbitration among groups (including behavior with freeze enable set) remains the same when group 1 is programmed for event-triggered mode and an event is pending. This behavior is fairly complex, and is described in more detail in Section 5.

# 4.5 Buffered Mode Control Registers

Table 3 lists the buffered mode control registers.

Table 3. Buffered Mode MibADC Control Registers

| Address | Mnemonic | Name                                          | Description                                                                      |

|---------|----------|-----------------------------------------------|----------------------------------------------------------------------------------|

| 0x00    | ADCR1    | Control register 1                            | Contains control bits for initiating and controlling calibration and conversions |

| 0x04    | ADCR2    | Control register 2                            | Contains control bits for initiating and controlling modes and events            |

| 0x08    | ADSR     | Status register                               | Contains flags showing the status of conversion activities                       |

| 0x0C    | ADEISR   | Event group input-<br>channel select register | Controls start of conversion of selected channels based on ADEVT event           |

Table 3. Buffered Mode MibADC Control Registers (Continued)

| Address     | Mnemonic | Name                                                  | Description                                                                                                                |

|-------------|----------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 0x10        | ADISR1   | Group 1 input-channel select register                 | Controls start of conversion of selected group 1 channels                                                                  |

| 0x14        | ADISR2   | Group 2 input-channel select register                 | Controls start of conversion of selected group 2 channels                                                                  |

| 0x18        | ADCALR   | Calibration and offset error cor-<br>rection register | Receives calibrated data from ADC core                                                                                     |

| 0x20 - 0x3F | ADBUFE   | Event group buffer                                    | FIFO 1 read location, event group                                                                                          |

| 0x90        | ADEMBUFE | Event Group Emu Buffer                                | FIFO 1 read location, event group - *No Side Effect to Read                                                                |

| 0x40-0x5F   | ADBUF1   | Group 1 Buffer                                        | FIFO 2 read location, group 1                                                                                              |

| 0x94        | ADEMBUF1 | Group 1 Emu Buffer                                    | FIFO 2 read location, group 1 - *No Side Effect to Read                                                                    |

| 0x60-0x7F   | ADBUF2   | Group 2 Buffer                                        | FIFO 3 read location, group 1                                                                                              |

| 0x98        | ADEMBUF2 | Group 2 Emu Buffer                                    | FIFO 3 read location, group 1 - *No Side Effect to Read                                                                    |

| 0x9C        | ADINR    | Data Input Register                                   | Contains last converted value on the ADVENT pins                                                                           |

| 0xA0        | ADCPC    | Pin Control Register                                  | Controls ADEVT pin                                                                                                         |

| 0xB0        | ADSAMPEV | Sample Control Register Event                         | Event group sample time                                                                                                    |

| 0xB4        | ADSAMP1  | Sample Control Register 1                             | Group 1 sample time                                                                                                        |

| 0xB8        | ADSAMP2  | Sample Control Register 2                             | Group 2 sample time                                                                                                        |

| 0xBC        | ADBCR1   | Buffer Control Register 1                             | Buffer enable/disable, allocation                                                                                          |

| 0xC0        | ADBCR2   | Buffer Control Register 2                             | Buffer end pointer/size control                                                                                            |

| 0xC4        | ADBCR3   | Buffer Control Register 3                             | Buffer DMA and interrupt enable bits                                                                                       |

| 0xC8        | ADBST    | Buffer Status Register                                | Buffer empty, overrun, and interrupt flags                                                                                 |

| 0xCC        | ADTHREV  | Event Group Interrupt Threshold                       | Sets fill level of event group FIFO before interrupt generated                                                             |

| 0xD0        | ADTHRG1  | Group Interrupt 1 Threshold                           | Sets fill level of group 1 FIFO before interrupt generated                                                                 |

| 0xD4        | ADTHRG2  | Group 2 Interrupt Threshold                           | Sets fill level of group 2 FIFO before interrupt generated                                                                 |

| 0xD8        | ADEVTSRC | Event Source Register                                 | Selects extended event trigger sources for ADEVT group and group 1, and enables group 1 to act as an event-triggered group |

#### 4.5.1 Buffered Mode FIFOs

In buffered mode, the 16 digital result registers and their corresponding 16 emulation registers are replaced with 3 FIFOs and an emulation version of each.

Each buffer is readable from more than one register address (aliased) to allow effective use of the CPU capability to load multiple instructions to empty the buffer. For example, a read to any address between offset 0x20 and 0x3F pulls one conversion result from the event group buffer.

Also, for debug purposes, each buffer has an emulation address that returns the next conversion result from the buffer without removing the result from the buffer itself. For example, reading from offset 0x90 returns the next result in the event group buffer, but does not actually remove that result from the buffer or change the amount of data held in the buffer.

Only the MibADC module itself writes to the FIFOs. Data is written to the specific FIFO for a particular conversion group when a conversion from that group is complete.

Data can be read out of a FIFO either by the CPU or the DMA controller. The MibADC cannot distinguish between the two.

Reading from an empty FIFO results in a data value with bit 15 (EMPTY) set. This bit can be checked to verify that the conversion data is indeed valid.

Each FIFO may be read (either by the CPU or DMA) at the same time a new conversion result is stored in it by the MibADC. This feature is supported in hardware for simplicity and no additional wait states are incurred in this situation.

The MibADC works with the DMA in request mode generating one DMA request for each piece of data moved into a FIFO. Therefore, when a FIFO is serviced by the DMA controller, an empty buffer read should not occur during normal operation. However, the EMPTY flag can be checked as a precaution.

If the CPU is used to read from a FIFO, the load multiple (LDM) instruction enables the loading of multiple registers from memory with back-to-back read operations. The EMPTY flag saves the CPU from polling the DMA controller between each data read to determine if there is more data in the FIFO.

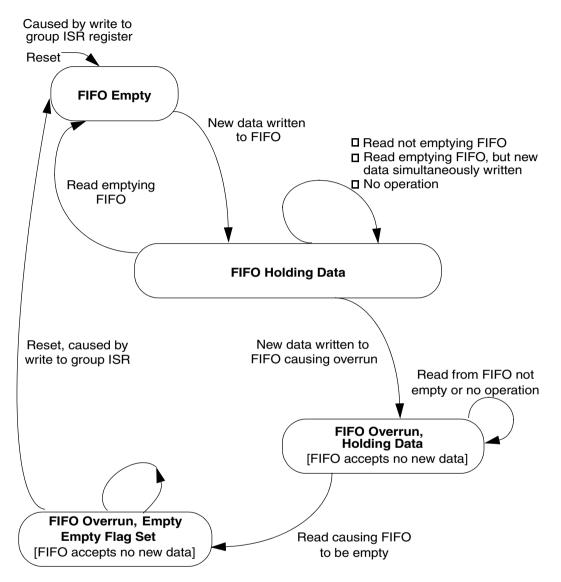

Finally, a FIFO overrun occurs when a FIFO is full and the MibADC attempts to write data into the FIFO while no data is being read from the FIFO. If this occurs, the FIFO blocks the write (does not allow an overrun to occur) and goes into an overrun state. In the overrun state, no new data can be written to the FIFO (new conversions are lost), but the data already in the FIFO can

be read either by the CPU or DMA. An interrupt request is generated, and the CPU must re-initialize the conversion group and its FIFO.

#### 4.5.2 FIFO Channel Identifier

Optionally, as each channel is converted and its digital result is stored in the FIFO, the channel number can be stored along with the digital result in bit positions [13:10]. This is useful for verifying that the data read from a FIFO is the conversion result of the expected channel.

This mode is optional and must be enabled by setting the CHID bit in the ADBUFCR2 register.

#### 4.5.3 FIFO 8-Bit Mode

Some applications can use only the eight most significant bits (MSBs) of the A/D result. To make using the MibADC in this way more efficient, the MibADC can automatically shift the conversion result right by two bits as the result is read out of a FIFO. This shift eliminates the need for the application program to shift each piece of data and results in faster execution.

The FIFO 8-bit mode is optional, and must be enabled by setting the G18BIT, G28BIT, and EV8BIT control bits in the ADBUFCR2 register. It is selectable on a per-FIFO basis. This option is functional only in FIFO mode.

# 5 Modes of Operation

This section provides a general discussion of the four operating modes of the TMS470 MibADC.

- □ Conversion mode: The normal active mode for converting the selected external input voltage according to the configuration set in ADCR2 and according to the timing selected by PS.2:0 and ACQ.1:0 in ADCR1.4:0 or, alternatively, ADSAMPEV.7:0, ADSAMPG1.7:0, and ADSAMPG2.7:0. See Section 5.1, Conversion Mode for more details.

- □ **Self-test mode**: An active mode that inserts a failure-detection step before the normal conversion flow is entered. Self-test mode is enabled by writing a 1 to the SELF TST bit (ADCR1.9). See section 5.2, *Self-Test Mode*, for more details.

- □ Calibration mode: A special active mode that allows an internal reference voltage to be connected to the ADC core input. While the calibration is selected, the input channel multiplexer is disabled and only the reference is available at the converter input. The calibration mode is enabled by writing a 1 to the CAL EN bit (ADCR1.13). See section 5.3, Calibration Mode, for more details.

- □ Power-down mode: Inactive mode in which the ADC internal clock is stopped, leaving the module in a static state. After power-down mode is released, time  $t_{d(PU-ADV)}$  (see the device-specific data sheet for specific timing) is required for the MibADC to stabilize. See section 5.4, *Power-Down Mode*, for more details.

#### 5.1 Conversion Mode

The MibADC offers two modes of conversion: continuous conversion mode and single conversion mode. Both conversion modes are selectable for each conversion group.

#### **Note: Continuous Conversion for Multiple Groups**

The three groups (G1, G2, and EVT) cannot operate together in continuous mode. When this situation occurs, group 2 is automatically reset to single conversion mode, and the G2 MODE (ADCR2.2) bit is cleared to reflect the actual conversion mode of group 2.

There are two conversion modes:

#### □ Single conversion mode

In single conversion mode, the MibADC converts all selected channels in a group sequentially one time through and then stops.

The entire conversion sequence, from the acceptance of a group conversion request to the end of the last conversion, is flagged for each group by the corresponding BUSY bit (ADSR.13:11). After single conversion mode is started, the BUSY bit is read as 1 until the conversion of the last selected channel is complete.

#### □ Continuous conversion mode