TI Designs: TIDEP-0093

# Electronic Point of Sale (EPOS) Payment Terminal Reference Design

## Description

The TIDEP-0093 design provides faster time to market with a processor that helps customers meet PCI-PTS and EMV requirements. Electronic point of sale (EPOS) payment terminals require features such as authenticated boot, tamper detection, DDR encryption and more. This AM438x processor enables developers to design systems that meet Payment Card Industry (PCI) certification. The AM438x processors provides scalability with various processors speeds and compatible software to satisfy low- to high-end applications, along with ample connectivity including key peripherals required for payment terminals such as smart card and magnetic card reader.

#### Resources

TIDEP-0093 Design Folder

AM438x Product Folder

TPS65218 Product Folder

TCA5013 Product Folder

ASK Our E2E Experts

#### **Features**

- TI Sitara<sup>™</sup> AM438x Processor With Integrated Features Help Customers Design Point-of-Sale Applications

- ARM® Cortex®-A9-based Processor With 300-MHz, 600-MHz, and 1-GHz Speeds as Well as 3D Graphics and PRU Options

- Processor Software Development Kit (SDK) for Linux® Development

- Smart Card and Magnetic Card Reader Along With Other Peripherals Such as Touchscreen Display, Keypad, USB, Ethernet, and More

- Includes TI TPS65218 Power Management IC and TCA5013 Smart Card PHY Devices

## **Applications**

- · Vending, Payment, and Change Machines

- · Handheld and Stationary EFT Terminals

- EPOS, ECR, and Cash Drawer

- Fuel Dispensers

- EPOS Printers

- ATMs

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

System Description www.ti.com

# 1 System Description

Based on the AM438x EVM, the TIDEP-0093 design is a kickstarter for customers wanting to design a module or system for EPOS. The TIDEP-0093 design uses the Sitara AM438x, TPS65218x, and TCA5013 devices.

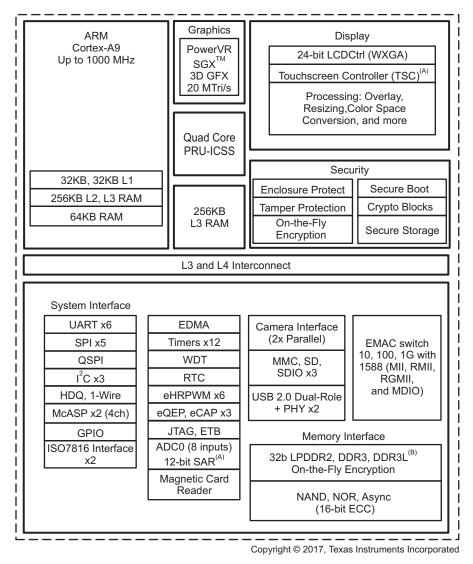

The TI AM438x high-performance processors are based on the ARM Cortex-A9 core. The processors are enhanced with payment card peripherals and logical and physical security to help customers meet PCI requirements. The devices support high-level operating systems (HLOS). Linux is available free of charge from TI. The devices offer an upgrade to systems that are based on lower-performance ARM cores, provide updated peripherals (including memory options such as QSPI-NOR and LPDDR2), and support the security features typically required for PCI-PTS. AM438x integrates key peripherals often required in payment terminals: smart card reader and magnetic card reader. Figure 1 shows the Sitara AM438x.

Figure 1. Sitara AM438x

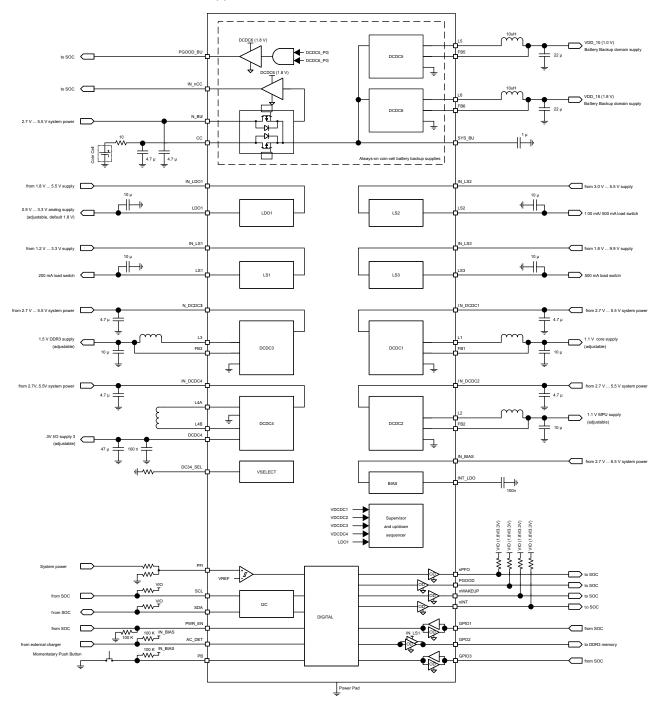

The TPS65218x is a power management solution for AM438x with special rails to power AM438x's tamper module. The TPS65218x provides three step-down converters, three load switches, three general-purpose IOs, two battery backup supplies, one buck-boost converter, and one low-dropout (LDO) regulator. The system can be supplied by a single-cell Li-lon battery or regulated 5-V supply. A coin-cell battery can be added to supply the two always-on backup supplies. Figure 2 shows the TPS65218x.

Figure 2. TPS65218x

www.ti.com System Description

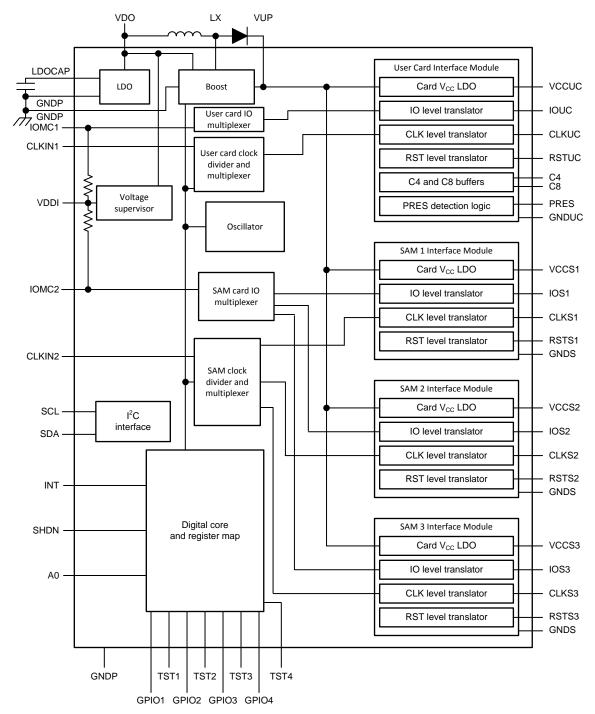

The TCA5013 is designed to seamlessly work with AM438x. The TCA5013 is a smart card interface IC that is targeted for use in point of sale (POS) terminals. The device enables POS terminals to interface with EMV4.3, ISO7816-3, and ISO7816-10 compliant cards. The device supports up to three secure access module (SAM) cards in addition to one user card. Figure 3 shows the TCA5013.

Figure 3. TCA5013

System Overview www.ti.com

# 2 System Overview

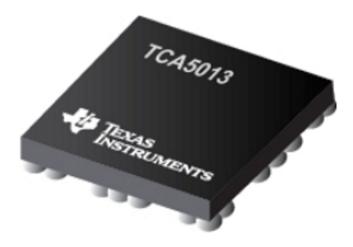

# 2.1 Block Diagram

Copyright © 2017, Texas Instruments Incorporated

Figure 4. EPOS EVM System Block Diagram

www.ti.com System Overview

## 2.2 Highlighted Products

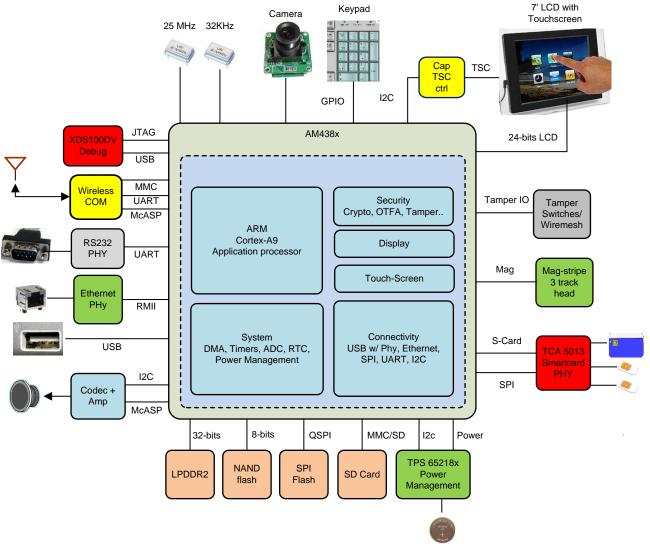

#### 2.2.1 AM438x

The TI AM438x high-performance processors are based on the ARM Cortex-A9 core. The processors are enhanced with payment card peripherals and logical and physical security to help customers meet payment card industry (PCI) requirements.

The devices support HLOS. Linux is available free of charge from TI. The devices offer an upgrade to systems that are based on lower-performance ARM cores, provide updated peripherals (including memory options such as QSPI-NOR and LPDDR2), and support the security features discussed in this design guide.

Figure 5. AM438x Functional Block Diagram

The processor subsystem is based on the ARM Cortex-A9 core, and the PowerVR SGX™ graphics accelerator subsystem provides 3D graphics acceleration to support display and advanced user interfaces.

System Overview www.ti.com

The programmable real-time unit subsystem and industrial communication subsystem (PRU-ICSS) is separate from the ARM core and allows independent operation and clocking for greater efficiency and flexibility. The programmable nature of the PRU-ICSS, along with the system's access to pins, events, and all system-on-chip (SoC) resources, provides flexibility in implementing fast real-time responses, specialized data handling operations, custom peripheral interfaces, and in offloading tasks from the other processor cores of the SoC.

High-performance interconnects provide high-bandwidth data transfers for multiple initiators to the internal and external memory controllers and to on-chip peripherals. The device also offers a comprehensive clock-management scheme. The on-chip analog-to-digital converter (ADC0) can couple with the display subsystem to provide an integrated touch-screen solution. There is also an EMV-compliant ISO7816 interface (smart card) interface and magnetic card controller (ADC1).

The real-time clock (RTC) provides a clock reference on a separate power domain. The clock reference enables a battery-backed clock reference.

The camera interface offers configuration for a single- or dual-camera parallel port.

The physical protection subsystem adds enclosure protection to the secure features offered by the AM438x processors, which include cryptography acceleration and secure boot. Enclosure protection helps customers design products that detect when the casing is opened and protect sensitive parts of the circuit with a wire mesh. Tamper protection monitors voltage, temperature, and crystal frequency so system designers can detect external attacks.

In addition, the partial ARM TrustZone® technology allows system designers to configure memory for secure storage and protect against software attacks.

www.ti.com System Overview

## 2.2.2 TPS65218x

The TPS65218x provides three step-down converters, three load switches, three general-purpose IOs, two battery backup supplies, one buck-boost converter, and one LDO. The system can be supplied by a single cell Li-Ion battery or regulated 5-V supply. A coin-cell battery can be added to supply the two always-on backup supplies. The device is characterized across a –40°C to 105°C temperature range, which makes it suitable for various industrial applications.

Figure 6. TPS65218x Functional Block Diagram

System Overview www.ti.com

The I<sup>2</sup>C interface provides comprehensive features for using the TPS65218x. All rails, load-switches, and GPIOs can be enabled or disabled. Voltage thresholds for the undervoltage lockout (UVLO) and supervisor can be customized. Power-up and power-down sequences can also be programmed through I<sup>2</sup>C. Interrupts for overtemperature, overcurrent, and undervoltage can be monitored as well.

The integrated voltage supervisor monitors DC-DC 1 through 4 and LDO1. The supervisor has two settings; the standard settings only monitor for undervoltage while the strict settings implement tight tolerances on both undervoltage and overvoltage. A power good signal is provided to report the regulation state of the five rails.

The three hysteretic step-down converters can each supply up to 1.8 A of current. The default output voltages for each converter can be adjusted through the I<sup>2</sup>C interface. DC-DC 1 and 2 feature dynamic voltage scaling with adjustable slew rate. The step-down converters operate in a low power mode at light load and can be forced into PWM operation for noise sensitive applications.

The battery backup supplies consist of two low-power step-down converters optimized for very light loads and are monitored with a separate power good signal. The converters can be configured to operate as always-on supplies with the addition of a coin-cell battery. The state of the battery can be monitored over I<sup>2</sup>C.

www.ti.com System Overview

## 2.2.3 TCA5013

The TCA5013 is a smart card interface IC that is targeted for use in POS terminals. The device enables POS terminals to interface with EMV4.3, ISO7816-3, and ISO7816-10 compliant cards. The device supports up to three SAM cards in addition to one user card.

Figure 7. TCA5013 Functional Block Diagram

System Overview www.ti.com

The TCA5013 operates from a single supply and generates all the card voltages. The device is controlled by a standard I<sup>2</sup>C interface and is capable of card activation and deactivation per EMV4.3 and ISO7816-3 standards. In addition the device also supports ISO7816-10 synchronous cards. The TCA5013 has a 4-byte FIFO that stores the answer to reset (ATR) sequence in ISO7816-10 type one cards. Synchronous cards (ISO7816-10 type one and type two) can be set up for automatic activation or manual activation. The device has multiple power saving modes and also supports power saving in the smart card itself by *clock stop* or lowering clock frequency to lowest allowable levels per the ISO7816-3 standards.

The TCA5013 has IEC 61000-4-2, 8-kV, contact discharge on all pins that interface with smart cards, which enables the system to be resistant to ESD in the field without the requirement for external ESD devices. The device is available in a 5-mm×5-mm BGA package. All IO pins are securely surrounded by other pins in the pinout of the device, which prevents the secure pins from being probed during device operation.

# 3 Hardware, Software, Testing Requirements, and Test Results

## 3.1 Required Hardware and Software

#### 3.1.1 Hardware

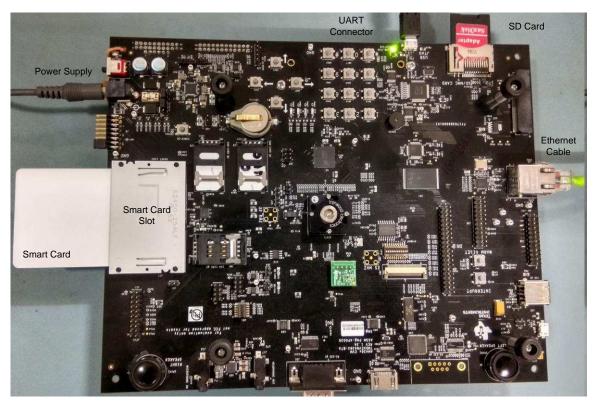

The AM438x EPOS evaluation module (EVM) is a standalone test, development, and EVM system that enables developers to write software and develop hardware around an AM438x processor subsystem. The EPOS EVM also hosts TPS65218 and TCA5013 devices.

See the AM438x EPOS EVM Hardware's User's Guide[2] for getting started instructions and details on hardware architecture of EPOS EVM.

The following hardware is required to get the smart card demonstration application:

- AM438x EPOS EVM

- SD card (the TI processor SDK EPOS image requires at least 8GB of space)

- Power supply (5 V, 3 A) for the AM438x-based board

- Programmed SMART card

**NOTE:** The smart card demonstration application uses an ACOS3 demo card. This smart card is programmed with ACOS3 demo card Flash scripts.

## 3.1.2 Software

The AM438x EPOS SDK is a restricted-access software package that requires business approval and a special NDA with TI before access is provided from the TI secure delivery portal (mySecure Software). See Section 5 on how to request access.

Once access is given, the AM438x EPOS SDK package contains a software user's guide and additional documentation for setting up and running the demonstration test applications.

With the required hardware, perform the following steps to replicate the software portion of the demonstration.

For the purposes of this design guide, it is assumed that a Linux host machine is being used. Program the SD card with the Linux processor SDK image using the following steps:

- 1. Download the SDK installer ti-processor-sdk-am438x-epos-evm-xx.xx.xx.xx-Linux-x86-Install.bin from TI mySecure site (where "xx.xx.xx.xx" is the version number of the latest Linux Processor SDK EPOS).

- 2. Create the SD card with default images using the SDK Create SD Card Script or see the user's guide.

- 3. Boot the Linux kernel and file system using the created SD card.

# 3.2 Testing and Results

## 3.2.1 Test Setup

This section provides details of test setup with the required hardware and software to be able to run the TI EPOS software application.

Figure 8. AM438x EVM Setup

## 3.2.2 Test Results

This section provides the test cases details and results for the TI smart card software application.

Figure 9. AM438x Default Matrix GUI

# Test Case One: EPOS Smart Card Demo Application Launcher

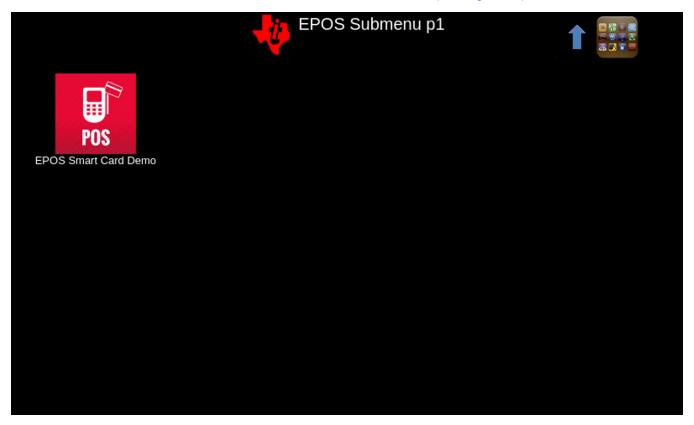

1. On Matrix GUI, select the EPOS icon to launch the submenu (see Figure 10).

Figure 10. EPOS Submenu to Launch EPOS Smart Card Demo

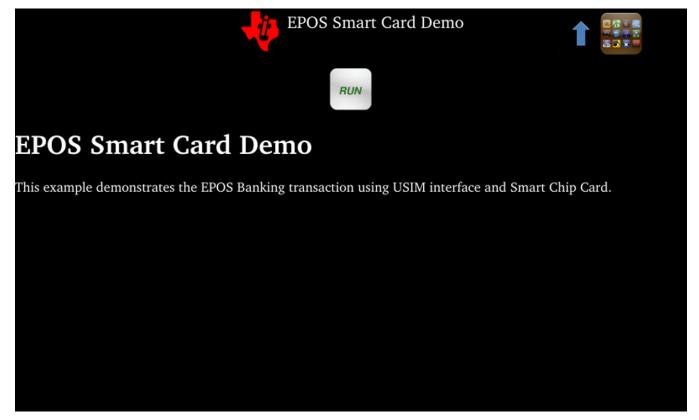

2. Select the EPOS Smart Card Demo App RUN utility (see Figure 11).

Figure 11. EPOS Smart Card Demo Home Screen

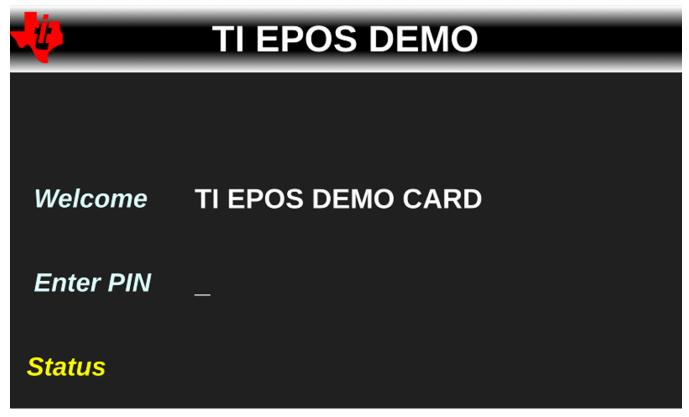

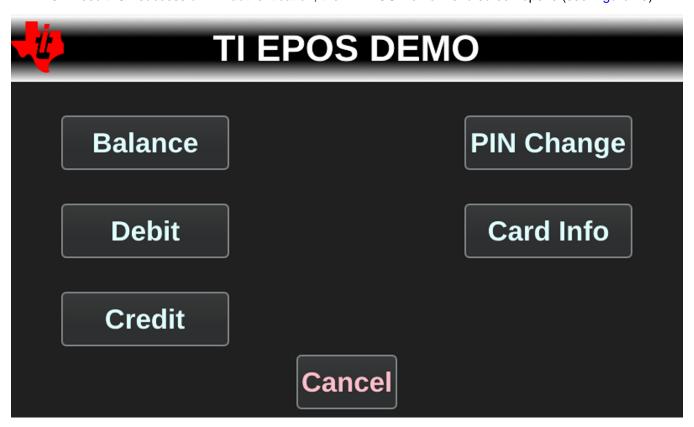

3. Result: TI EPOS Demo screen should launch (see Figure 12).

Figure 12. EPOS Smart Card Demo Launch Successful

## Test Case Two: Smart Card Detection

- 1. Insert preprogrammed smart card into the card slot.

- 2. Result: On successful card presence detection, the program redirects to the *authentication screen* in Figure 13.

Figure 13. Authentication Screen

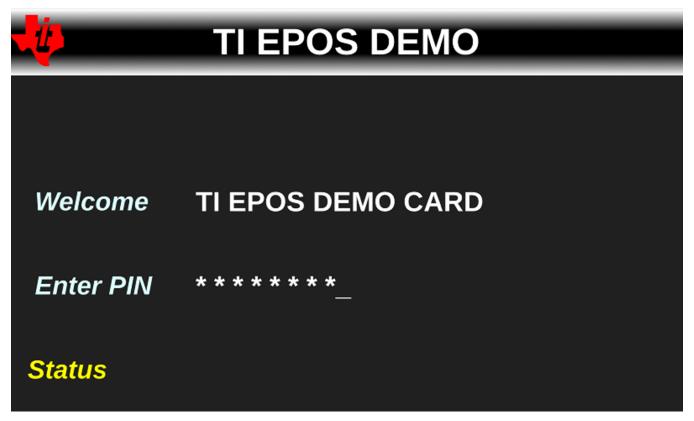

## Test Case Three: Smart Card Authentication With PIN Validation

- 1. Enter the default PIN as 12345678.

- 2. Press the \* key to enter.

**NOTE:** Press the # key to cancel or re-enter the PIN.

Figure 14. PIN Authentication Login

3. Result: On successful PIN authentication, the TI EPOS Demo menu screen opens (see Figure 15).

Figure 15. PIN Authentication Successful

**NOTE:** An invalid PIN or pressing *Cancel* returns the user to the card detection screen.

## Test Case Four: Smart Card Information

- 1. Select the Card Info icon for card information.

- 2. Select *OK* to return to the main menu.

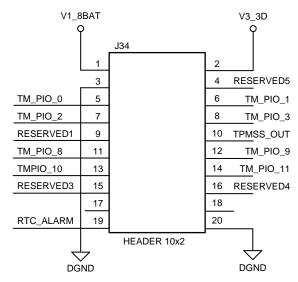

## 3.2.2.1 Wire Mesh Tamper

A wire mesh is a loop between two PIOs—one acting as a TX and the other RX. When the RX stops receiving the TX signal, it generates a tamper event.

**Table 1. Wire Mesh Pin Configuration**

| SIGNAL NAME | HEADER   | PIN | SIGNAL NAME | HEADER | PIN |

|-------------|----------|-----|-------------|--------|-----|

| TM_PIO_0    | -<br>J34 | 5   | TM_PIO_8    | J34    | 11  |

| TM_PIO_1    |          | 6   | TM_PIO_9    |        | 12  |

| TM_PIO_2    |          | 7   | TM_PIO_10   |        | 13  |

| TM_PIO_3    |          | 8   | TM_PIO_11   |        | 14  |

Figure 16. Wire Mesh Header

## **Board Connections**

- Use J34 and J88 headers to test the wire mesh.

- Make connection should be made according to the pin connections mentioned in Figure 16.

**Table 2. Wire Mesh Pin Configuration**

| PIO   | PIN CONFIGURATION |

|-------|-------------------|

| PIO_0 | Pin 5 and 11      |

| PIO_1 | Pin 6 and 12      |

| PIO_2 | Pin 7 and 13      |

| PIO_3 | Pin 8 and 14      |

## **PIO Combinations**

The combinations of the PIOs that can be connected as wire meshes are fixed. The PIOs can be paired as PIO\_0 to PIO\_8, PIO\_1 to PIO\_9, and so on to configure wire meshes. First configure the PIOs based on the wire meshes required. The remaining PIOs can be used for open close switches.

For wire mesh configurations, PIO\_0 through PIO\_5 must be configured as TX and PIO\_8 through PIO\_13 must be configured as RX.

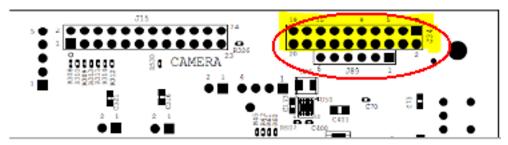

Figure 17. Wire Mesh Connections for Four PIOs

## **Hardware Requirements for Testing**

· Female-to-female pin connector

Figure 18. Pin Connector for Wire Mesh

## **How to Test Wire Mesh**

Currently the wire mesh is tested using U-Boot by halting it during boot-up. The following are instructions and screenshots for testing wire mesh:

1. Halt U-Boot during boot-up by pressing Enter.

```

tpmss_pio 4 0 0 1 10 1 0 1

Set PIO configuration

PIO QSM0 configured

PIO QSM1 configured

PIO QSM1 configured

PIO QSM2 configured

PIO QSM2 configured

PIO QSM3 enabled

PIO QSM3 enabled

PIO monitoring enabled and Pulse Generator is OK

=> ■

```

## CTRL-A Z for help | 115200 8N1 | NOR | Minicom 2.7 | VT102 | Offline | ttyUSB0

## Figure 19. Configuring Four PIOs on U-Boot Prompt

Command information:

- <n meshes>—number of wire mesh: 4

- <n switches>—number of enclosure switches: 0

**NOTE:** The combinations of the PIOs that can be connected as wire meshes are fixed. The PIOs can be paired as PIO\_0 to PIO\_8, PIO\_1 to PIO\_9, and so on. Go on shorting loops starting from pair 0 to the number of pairs selected in this example.

- <irq>—enable IRQ on tamper [reset = 0]: 0

- <bbdmem>—clear BBD memory on tamper [reset=0]: 1

- <thrctr>—Event counter threshold for FREQ QSM [reset = 4]: 10

- <distimer>—disable timer mode [reset = 0]: 1

- <tmrctr>—Timer counter value for FREQ QSM [reset = 0]: 0

- qsm enable>—Enables FREQ QSM (1 = State Machine enabled, 0 = State Machine disabled): 1

- 2. Apply the command "tpmss\_prolog" to unlock the core, bbd RAM, and some initialization.

- 3. Initialize the number of PIOs required.

NOTE: For demonstration purposes, four PIOs are used to test.

4. Dump the error log without breaking any loops (and without opening any PIOs).

JOY®PUNECPU297:~

tpmss\_dump\_log

BBD Tamper Log is Empty

⇒

CTRL-A Z for help | 115200 8N1 | NOR | Minicom 2.7 | VT102 | Offline | ttyUSB0

Figure 20. TPMSS Log Before Breaking Loop

5. Dump the error after breaking any loops.

```

joy@PUNECPU297: ~

11 En 🖾 40)) 5:50 PM 😃

tpmss dump log

debug: log entry 0 address = 44e91fe0, data = 139 4010000

BBD Tamper Log Entry 1 (44e91fe0)

SecureTimeStamp = 313 (139)

System state when trigger occured = 0 (Core Active)

State of Trigger Outputs:

PIO QSMs

CPU Tamper

JTAG Trigger

Temp QSM1 Trigger = 0

Freq QSM0 Trigger = 0

PI0[7:0]

PI[7:0]

Temp. Sensor Low = 0

Temp. Sensor High = 0

XOSC Low Fail

XOSC High Fail

```

CTRL-A Z for help | 115200 8N1 | NOR | Minicom 2.7 | VT102 | Offline | ttyUSB0

Figure 21. TPMSS Log After Breaking Loop

NOTE: In this example, the loop breaks by removing the PIO\_2 connector (pin 7 or 13).

Command: tpmss\_dump\_log

The output value is the bit position, which provides the PIO number.

If the following combinations are removed:

- PIO\_0 (pin 5 and 11): Error output for PIO [7:0] = 1

- PIO\_1 (pin 6 and 12): Error output for PIO [7:0] = 2

- PIO\_2 (pin 7 and 13): Error output for PIO [7:0] = 4

- PIO\_3 (pin 8 and 14): Error output for PIO [7:0] = 8

**NOTE:** In this example, the value is 4, which is the PIO\_2 connector.

=>

www.ti.com Design Files

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDEP-0093.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDEP-0093.

## 4.3 PCB Layout Recommendations

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDEP-0093.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDEP-0093.

## 4.5 Gerber Files

To download the Gerber files, see the design files at TIDEP-0093.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDEP-0093.

## 5 Software Files

The AM438x EPOS SDK is a restricted-access software package that requires business approval and special NDA with TI before access is provided through the TI secure delivery portal (mySecure Software). Contact a local TI representative for details. Request access using the following link: <a href="https://www.ti.com/licreg/docs/swlicexportcontrol.tsp?form\_id=250333&prod\_no=AM438X\_RESTRICTED\_SW&ref\_url=sitara">https://www.ti.com/licreg/docs/swlicexportcontrol.tsp?form\_id=250333&prod\_no=AM438X\_RESTRICTED\_SW&ref\_url=sitara</a>

The AM438x EPOS SDK package contains a software user's guide and additional documentation for setting up and running the demo test applications.

## 6 Related Documentation

- 1. TI E2E Community, Texas Instruments Security Private E2E

- 2. Texas Instruments, AM438x EPOS EVM Hardware's User's Guide, User's Guide (SPRUIF8)

#### 6.1 Trademarks

Sitara is a trademark of Texas Instruments, Inc..

ARM, Cortex, TrustZone are registered trademarks of ARM Limited.

PowerVR SGX is a trademark of Imagination Technologies Limited.

Linux is a registered trademark of The Linux Foundation.

All other trademarks are the property of their respective owners.

## 7 Terminology

**EPOS**— Electronic point of sale

**PCI-PTS**— Payment card industry pin transaction security

About the Authors www.ti.com

## 8 About the Authors

**AMRIT MUNDRA** is a part of the system team in the Catalog Processors BU. He has been with TI for more than 14 years and has worked on multiple IPs and SoCs. He is the security architect for Keystone3 and security lead for Catalog BU. Amrit also is System lead for EPOS EE initiative in BU. Amrit earned his master of science in electrical engineering (MSEE) from SMU, Dallas, TX.

**CARLOS BETANCOURT** is a product marketing engineer at Texas Instruments, where he is responsible for marketing Sitara processors. Carlos earned his bachelor and master of science in electrical engineering degrees from the University of Texas at El Paso in 1997 and 1999, respectively.

**JAMES DOUBLESIN** is a member of the hardware applications team in the Catalog Processors Business Unit. He has worked at TI for more than 24 years and has been involved with many different ARM-based embedded processors in the Sitara product line. James earned his BS in electrical engineering from Southern Methodist University and MS in electrical engineering from University of Texas at Arlington.

**YOGESH SIRASWAR** is a software project lead for Processor SDK EPOS in the Catalog Processors Business Unit. He has worked at TI for more than 15 years and delivered various software on many different DSP and ARM-based embedded processors. Yogesh has earned his BS in electronic & communication engineering from Maulana Azad National Institute of Technology, Bhopal.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated