# ADS981x 18-Bit, 2-MSPS/Ch, Dual, Simultaneous-Sampling ADC With Integrated **Analog Front-End**

### 1 Features

- 8-channel, 18-bit ADC with analog front-end:

- Dual, simultaneous sampling: 4 × 1 channels

- Constant 1MΩ input impedance front-end

- Programmable analog input ranges:

- ±12V, ±10V, ±7V, ±5V, ±3.5V, and ±2.5V

- Single-ended and differential inputs

- ±12V common-mode voltage range

- Input overvoltage protection: Up to ±18V

- User-selectable analog input bandwidth:

- 21kHz and 400kHz

- Integrated low-drift precision references

- ADC reference: 4.096V

- 2.5V reference output for external circuits

- Excellent AC and DC performance at fullthroughput:

- DNL: ±0.5LSB, INL: ±0.8LSB SNR: 92dB, THD: -113dB

- Power supply:

- Analog and digital: 5V and 1.8V Digital interface: 1.2V to 1.8V Temperature range: -40°C to +125°C

# 2 Applications

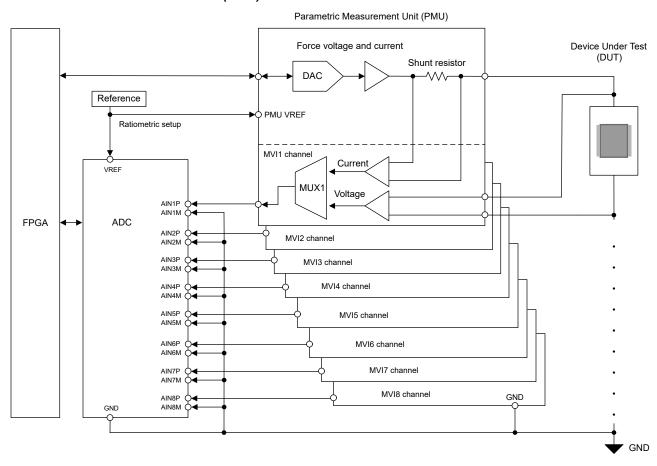

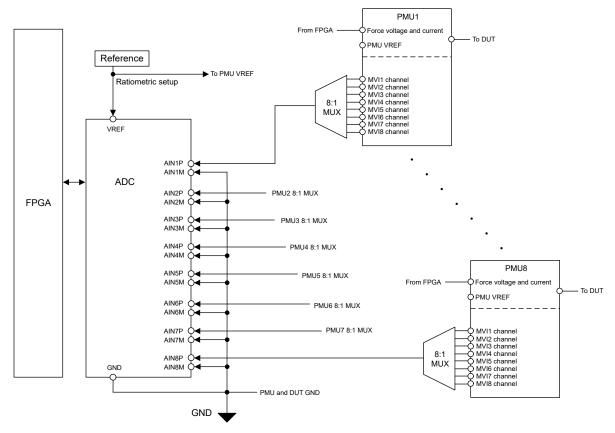

- Parametric measurement units (PMU)

- Battery cell formation and test equipment

- Data acquisition (DAQ)

### 3 Description

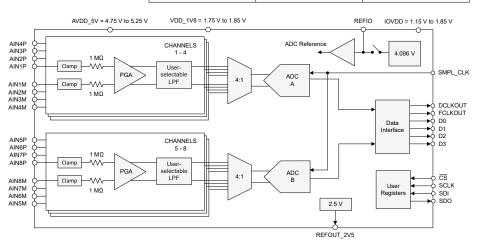

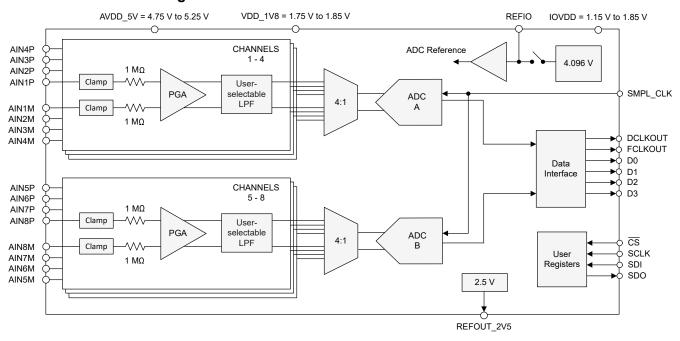

The ADS981x is an 8-channel data acquisition (DAQ) system based on a dual, simultaneous-sampling, 18bit successive approximation register (SAR) analogto-digital converter (ADC). The ADS981x features a complete analog front-end for each channel with an input clamp protection circuit,  $1M\Omega$  input impedance, and a programmable gain amplifier (PGA) with user-selectable bandwidth options. The high input impedance allows direct connection with sensors and transformers, thus eliminating the need for external driver circuits. The ADS981x can be configured to accept unipolar or bipolar inputs with up to a ±12V common-mode voltage.

The device also features a 4.096V reference for the ADC and a 2.5V reference output for use with external circuits. A digital interface supporting 1.2V to 1.8V operation enables the ADS981x to be used without external voltage level translators.

Package Information

|             | •                      |                             |

|-------------|------------------------|-----------------------------|

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

| ADS981x     | RSH (VQFN, 56)         | 7mm × 7mm                   |

- For more information, see the Mechanical, Packaging, and Orderable Information.

- The package size (length × width) is a nominal value and includes pins, where applicable.

#### **Device Information**

|   | PART NUMBER | SPEED         | TOTAL POWER |

|---|-------------|---------------|-------------|

|   | ADS9817     | 2MSPS/channel | 232mW       |

| ı | ADS9815     | 1MSPS/channel | 165mW       |

**Device Block Diagram**

# **Table of Contents**

| 1 Features1                           | 6.5 Programming34                                     |

|---------------------------------------|-------------------------------------------------------|

| 2 Applications1                       | 7 Register Map3                                       |

| 3 Description1                        | 7.1 Register Bank 0                                   |

| 4 Pin Configuration and Functions3    | 7.2 Register Bank 1                                   |

| 5 Specifications5                     | 7.3 Register Bank 256                                 |

| 5.1 Absolute Maximum Ratings5         | 8 Application and Implementation5                     |

| 5.2 ESD Ratings5                      | 8.1 Application Information58                         |

| 5.3 Recommended Operating Conditions6 | 8.2 Typical Application58                             |

| 5.4 Thermal Information6              | 8.3 Power Supply Recommendations62                    |

| 5.5 Electrical Characteristics7       | 8.4 Layout62                                          |

| 5.6 Timing Requirements10             | 9 Device and Documentation Support64                  |

| 5.7 Switching Characteristics11       | 9.1 Receiving Notification of Documentation Updates64 |

| 5.8 Timing Diagrams11                 | 9.2 Support Resources64                               |

| 5.9 Typical Characteristics14         | 9.3 Trademarks64                                      |

| 6 Detailed Description21              | 9.4 Electrostatic Discharge Caution64                 |

| 6.1 Overview21                        | 9.5 Glossary64                                        |

| 6.2 Functional Block Diagram21        | 10 Revision History64                                 |

| 6.3 Feature Description22             | 11 Mechanical, Packaging, and Orderable               |

| 6.4 Device Functional Modes31         | Information65                                         |

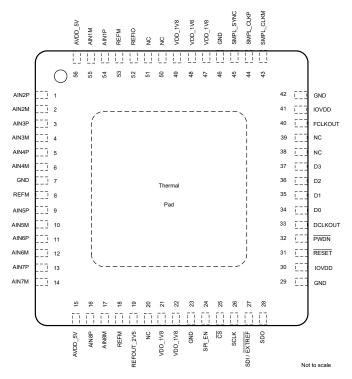

# **4 Pin Configuration and Functions**

Figure 4-1. RSH Package, 56-Pin VQFN (Top View)

**Table 4-1. Pin Functions**

| PIN                                                 | N                                       | TYPE(1) | DESCRIPTION                                                                                                             |  |  |  |

|-----------------------------------------------------|-----------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                | NO.                                     | 1 TPE(" | DESCRIPTION                                                                                                             |  |  |  |

| AIN1M                                               | 55                                      | Al      | Analog input channel 1, negative input.                                                                                 |  |  |  |

| AIN1P                                               | 54                                      | Al      | Analog input channel 1, positive input.                                                                                 |  |  |  |

| AIN2M                                               | 2                                       | Al      | Analog input channel 2, negative input.                                                                                 |  |  |  |

| AIN2P                                               | 1                                       | Al      | Analog input channel 2, positive input.                                                                                 |  |  |  |

| AIN3M                                               | 4                                       | Al      | Analog input channel 3, negative input.                                                                                 |  |  |  |

| AIN3P                                               | 3                                       | Al      | Analog input channel 3, positive input.                                                                                 |  |  |  |

| AIN4M                                               | Analog input channel 4, negative input. |         |                                                                                                                         |  |  |  |

| AIN4P 5 Al Analog input channel 4, positive input.  |                                         |         |                                                                                                                         |  |  |  |

| AIN5M 10 AI Analog input channel 5, negative input. |                                         |         |                                                                                                                         |  |  |  |

| AIN5P                                               | 9                                       | Al      | Analog input channel 5, positive input.                                                                                 |  |  |  |

| AIN6M                                               | 12                                      | Al      | Analog input channel 6, negative input.                                                                                 |  |  |  |

| AIN6P                                               | 11                                      | Al      | Analog input channel 6, positive input.                                                                                 |  |  |  |

| AIN7M                                               | 14                                      | Al      | Analog input channel 7, negative input.                                                                                 |  |  |  |

| AIN7P                                               | 13                                      | Al      | Analog input channel 7, positive input.                                                                                 |  |  |  |

| AIN8M                                               | 17                                      | Al      | Analog input channel 8, negative input.                                                                                 |  |  |  |

| AIN8P                                               | 16                                      | Al      | Analog input channel 8, positive input.                                                                                 |  |  |  |

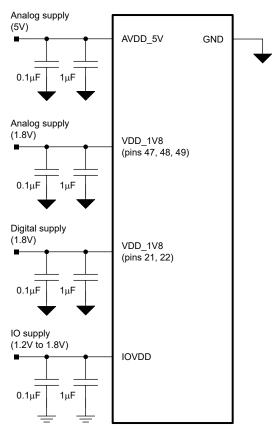

| AVDD_5V                                             | 15, 56                                  | Р       | 5V analog supply. Connect 1μF and 0.1μF decoupling capacitors to GND.                                                   |  |  |  |

| CS                                                  | 25                                      | DI      | Chip-select input for SPI interface configuration; active low. This pin has an internal 100kΩ pullup resistor to IOVDD. |  |  |  |

| D0                                                  | 34                                      | DO      | Serial output data lane 0.                                                                                              |  |  |  |

| D1                                                  | 35                                      | DO      | Serial data output lane 1.                                                                                              |  |  |  |

### **Table 4-1. Pin Functions (continued)**

| PII                                | N                                                                                                                                                                                                                                                                                         |                     | Table 4-1. Fill Fullctions (Continued)                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                               | NO.                                                                                                                                                                                                                                                                                       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

| D2                                 | 36                                                                                                                                                                                                                                                                                        | DO                  | Serial data output lane 2.                                                                                                                                                                                                                                                                                                                                                                                   |

| D3                                 | 37                                                                                                                                                                                                                                                                                        | DO                  | Serial data output lane 3.                                                                                                                                                                                                                                                                                                                                                                                   |

| DCLKOUT                            | 33                                                                                                                                                                                                                                                                                        | DO                  | Clock output for data interface.                                                                                                                                                                                                                                                                                                                                                                             |

| FCLKOUT                            | 40                                                                                                                                                                                                                                                                                        | DO                  | Frame synchronization output for data interface.                                                                                                                                                                                                                                                                                                                                                             |

| GND                                | 7, 23, 29, 42,<br>46                                                                                                                                                                                                                                                                      | Р                   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                      |

| IOVDD                              | 30, 41                                                                                                                                                                                                                                                                                    | Р                   | Digital I/O supply for data interface. Connect 1µF and 0.1µF decoupling capacitor to GND.                                                                                                                                                                                                                                                                                                                    |

| NC                                 | 20, 38, 39, 50,<br>51                                                                                                                                                                                                                                                                     | _                   | Not connected. No external connection.                                                                                                                                                                                                                                                                                                                                                                       |

| PWDN                               | 32                                                                                                                                                                                                                                                                                        | DI                  | Power-down control; active low. $\overline{PWDN}$ has an internal 100k $\Omega$ pullup resistor to the digital interface supply.                                                                                                                                                                                                                                                                             |

| REFIO                              | REFIO acts as an internal reference output when the internal reference is enabled. REFIO functions as an input pin for the external reference when the internal reference is disabled. Connect a 10μF decoupling capacitor to the REFM pins.  Reference ground potential. Connect to GND. |                     |                                                                                                                                                                                                                                                                                                                                                                                                              |

| REFM 8, 18, 53 Al Reference ground |                                                                                                                                                                                                                                                                                           |                     | Reference ground potential. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                  |

| REFOUT_2V5                         | 19                                                                                                                                                                                                                                                                                        | AO                  | 2.5V reference output. Connect a decoupling 10µF capacitor to the REFM pins.                                                                                                                                                                                                                                                                                                                                 |

| RESET                              | 31                                                                                                                                                                                                                                                                                        | DI                  | Reset input for the device; active low. $\overline{\text{RESET}}$ has an internal 100k $\Omega$ pullup resistor to the digital interface supply.                                                                                                                                                                                                                                                             |

| SCLK                               | 26                                                                                                                                                                                                                                                                                        | DI                  | Serial clock input for the configuration interface. SCLK has an internal $100k\Omega$ pulldown resistor to the digital interface ground.                                                                                                                                                                                                                                                                     |

| SDI                                | 27                                                                                                                                                                                                                                                                                        | DI                  | SDI is a multifunction logic input; pin function is determined by the SPI_EN pin. SDI has an internal $100k\Omega$ pulldown resistor to GND.<br>SPI_EN = 0b: SDI is the logic input to select between the internal or external reference. Connect SDI to GND for the external reference. Connect SDI to IOVDD for the internal reference.<br>SPI_EN = 1b: Serial data input for the configuration interface. |

| SDO                                | 28                                                                                                                                                                                                                                                                                        | DO                  | Serial data output for the configuration interface.                                                                                                                                                                                                                                                                                                                                                          |

| SMPL_CLKP                          | 44                                                                                                                                                                                                                                                                                        | DI                  | Single-ended ADC sampling clock input. SMPL_CLKP is the positive input for the differential sampling clock input to the ADC.                                                                                                                                                                                                                                                                                 |

| SMPL_CLKM                          | 43                                                                                                                                                                                                                                                                                        | DI                  | Connect SMPL_CLKM to GND for a single-ended ADC sampling clock input. SMPL_CLKM is the negative input for the differential sampling clock input to the ADC.                                                                                                                                                                                                                                                  |

| SMPL_SYNC                          | 45                                                                                                                                                                                                                                                                                        | DI                  | Synchronization input. See the <i>Sample Synchronization</i> section on how to use the SMPL_SYNC pin.                                                                                                                                                                                                                                                                                                        |

| SPI_EN                             | 24                                                                                                                                                                                                                                                                                        | DI                  | Logic input to enable the SPI interface configuration ( $\overline{CS}$ , SCLK, SDI, and SDO). SPI_EN has an internal 100k $\Omega$ pullup resistor to the digital interface supply.                                                                                                                                                                                                                         |

| VDD_1V8                            | 21, 22, 47, 48,<br>49                                                                                                                                                                                                                                                                     | Р                   | 1.8V power-supply. Connect 1μF and 0.1μF decoupling capacitors to GND.                                                                                                                                                                                                                                                                                                                                       |

| Thermal pad                        | _                                                                                                                                                                                                                                                                                         | Р                   | Exposed thermal pad; connect to GND.                                                                                                                                                                                                                                                                                                                                                                         |

<sup>(1)</sup> I = input, O = output, I/O = input or output, G = ground, and P = power.

# 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                            | MIN        | MAX           | UNIT |

|------------------------------------------------------------|------------|---------------|------|

| AVDD_5V to GND                                             | -0.3       | 6             | V    |

| VDD_1V8 to GND                                             | -0.3       | 2.1           | V    |

| IOVDD to GND                                               | -0.3       | 2.1           | V    |

| AINxP and AINxM to GND                                     | -18        | 18            | V    |

| REFIO to REFM                                              | REFM - 0.3 | AVDD_5V + 0.3 | V    |

| REFM to GND                                                | GND - 0.3  | GND + 0.3     | V    |

| Digital inputs to GND                                      | GND - 0.3  | 2.1           | V    |

| Input current to any pin except supply pins <sup>(2)</sup> | -10        | 10            | mA   |

| Junction temperature, T <sub>J</sub>                       | -40        | 150           | °C   |

| Storage temperature, T <sub>stg</sub>                      | -60        | 150           | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Pin current must be limited to 10 mA or less.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                               | TEST CONDITIONS       | MIN   | TYP   | MAX   | UNIT |

|------------------|-----------------------------------------|-----------------------|-------|-------|-------|------|

| POWER SU         | PPLY                                    | ·                     |       |       | '     |      |

| AVDD_5V          | Analog power supply                     | AVDD_5V to GND, 5 V   | 4.75  | 5     | 5.25  | V    |

| VDD_1V8          | Analog power supply                     | VDD_1V8 to GND, 1.8 V | 1.75  | 1.8   | 1.85  | V    |

| IOVDD            | Digital interface power supply          | IOVDD to GND          | 1.15  | 1.8   | 1.85  | V    |

| REFERENC         | E VOLTAGE                               |                       |       |       | '     |      |

| V <sub>REF</sub> | Reference voltage to the ADC            | External reference    | 4.092 | 4.096 | 4.100 | V    |

| ANALOG IN        | IPUTS                                   |                       |       |       | '     |      |

|                  | E.W. and investment of                  | RANGE_CHx = 0010b     | -2.5  |       | 2.5   | -    |

|                  |                                         | RANGE_CHx = 0001b     | -3.5  |       | 3.5   |      |

| \ /              |                                         | RANGE_CHx = 0000b     | -5    |       | 5     |      |

| $V_{FSR}$        | Full-scale input range                  | RANGE_CHx = 0011b     | -7    |       | 7     |      |

|                  |                                         | RANGE_CHx = 0100b     | -10   |       | 10    |      |

|                  |                                         | RANGE_CHx = 0101b     | -12   |       | 12    |      |

| AINxP            | Operating input voltage, positive input |                       | -17   |       | 17    | V    |

| AINxM            | Operating input voltage, negative input |                       | -17   |       | 17    | V    |

| TEMPERAT         | URE RANGE                               |                       |       |       | '     |      |

| T <sub>A</sub>   | Ambient temperature                     |                       | -40   | 25    | 125   | °C   |

### **5.4 Thermal Information**

|                       |                                              | ADS981x    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSH (VQFN) | UNIT |

|                       |                                              | 56 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 23.2       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.5       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.1        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 6.0        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.9        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

### 5.5 Electrical Characteristics

at AVDD\_5V = 4.75 V to 5.25 V, VDD\_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V, V<sub>REF</sub> = 4.096 V (internal or external), wide-common-mode disabled for analog input ranges  $\pm 2.5$ V,  $\pm 3.5$ V, and  $\pm 5$ V, wide-common-mode enabled for analog input ranges  $\pm 7$ V,  $\pm 10$ V, and  $\pm 12$ V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to  $\pm 125$ °C; typical values at  $T_A = 25$ °C

|                       | PARAMETER                                     | TEST CONDITIONS                                                              | MIN   | TYP   | MAX  | UNIT   |

|-----------------------|-----------------------------------------------|------------------------------------------------------------------------------|-------|-------|------|--------|

| ANALOG                | INPUTS                                        |                                                                              |       |       |      |        |

| R <sub>IN</sub>       | Input impedance                               | All input ranges                                                             | 0.85  | 1     | 1.15 | МΩ     |

|                       | Input impedance thermal drift                 | All input ranges                                                             |       | 10    | 25   | ppm/°C |

|                       | Input capacitance                             |                                                                              |       | 10    |      | pF     |

| ANALOG                | INPUT FILTER                                  |                                                                              |       |       | '    |        |

|                       |                                               | All input ranges, low-bandwidth filter                                       |       | 21    |      |        |

| 3W <sub>(-3 dB)</sub> |                                               | RANGE = ±2.5V, wide-bandwidth filter                                         |       | 182   |      |        |

|                       |                                               | RANGE = ±3.5V, wide-bandwidth filter                                         |       | 240   |      |        |

| BW <sub>(-3 dB)</sub> | Analog input LPF bandwidth  –3 dB             | RANGE = ±5V, wide-bandwidth filter                                           |       | 320   |      | kHz    |

|                       | -0 db                                         | RANGE = ±7V, wide-bandwidth filter                                           |       | 400   |      |        |

|                       |                                               | RANGE = ±10V, wide-bandwidth filter                                          |       | 385   |      |        |

|                       |                                               | RANGE = ±12V, wide-bandwidth filter                                          |       | 375   |      |        |

| DC PERF               | ORMANCE                                       |                                                                              |       |       | '    |        |

|                       | Resolution                                    | No missing codes                                                             | 18    |       |      | Bits   |

| DNL                   | Differential nonlinearity <sup>(3)</sup>      | All ranges, wide-CM enabled and disabled                                     | -0.99 | ±0.5  | 0.99 | LSB    |

| INL                   | Integral nonlinearity                         | All ranges, wide-CM enabled and disabled,<br>T <sub>A</sub> = 0°C to 70°C    | -4    | ±0.8  | 4    | LSB    |

| IINL                  |                                               | All ranges, wide-CM enabled and disabled,<br>T <sub>A</sub> = -40°C to 125°C | -4.5  | ±0.8  | 4.5  | LSB    |

|                       |                                               | RANGE = ±2.5V                                                                | -175  | ±90   | 175  |        |

|                       |                                               | RANGE = ±2.5V, wide-CM enabled                                               |       | ±120  |      |        |

|                       |                                               | RANGE = ±3.5V                                                                | -100  | ±60   | 100  |        |

|                       |                                               | RANGE = ±3.5V, wide-CM enabled                                               |       | ±80   |      |        |

|                       | Offset error <sup>(2) (5)</sup>               | RANGE = ±5V                                                                  | -50   | ±10   | 50   | LSB    |

|                       |                                               | RANGE = ±5V, wide-CM enabled                                                 |       | ±60   |      |        |

|                       |                                               | RANGE = ±7V                                                                  | -100  | ±35   | 100  |        |

|                       |                                               | RANGE = ±10V                                                                 | -50   | ±10   | 50   |        |

|                       |                                               | RANGE = ±12V                                                                 | -75   | ±15   | 75   |        |

|                       | Offset error thermal drift <sup>(2)</sup> (4) | All ranges, wide-CM enabled and disabled                                     |       | 0.5   | 1.5  | ppm/°C |

|                       |                                               | RANGE = ±2.5V, ±3.5V, and ±5V                                                | -0.05 | ±0.02 | 0.05 |        |

|                       | Gain error <sup>(2) (5)</sup>                 | RANGE = ±2.5V, ±3.5V, and ±5V, wide-CM enabled                               |       | ±0.04 |      | %FSR   |

|                       |                                               | RANGE = ±7V, ±10V, ±12V                                                      | -0.05 | ±0.02 | 0.05 |        |

|                       | Gain error thermal drift <sup>(2)</sup> (4)   | Wide-CM enabled and disabled, all ranges                                     |       | 0.7   | 3    | ppm/°C |

## 5.5 Electrical Characteristics (continued)

at AVDD\_5V = 4.75 V to 5.25 V, VDD\_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V, V<sub>REF</sub> = 4.096 V (internal or external), wide-common-mode disabled for analog input ranges  $\pm 2.5$ V,  $\pm 3.5$ V, and  $\pm 5$ V, wide-common-mode enabled for analog input ranges  $\pm 7$ V,  $\pm 10$ V, and  $\pm 12$ V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to  $\pm 125$ °C; typical values at  $T_A = 25$ °C

|                      | PARAMETER                                            | TEST CONDITIONS                                           | MIN   | TYP   | MAX | UNIT   |

|----------------------|------------------------------------------------------|-----------------------------------------------------------|-------|-------|-----|--------|

|                      |                                                      | RANGE = ±2.5V, f <sub>IN</sub> = 2kHz                     | 86.7  | 89.5  |     |        |

|                      |                                                      | RANGE = ±3.5V, f <sub>IN</sub> = 2kHz                     | 87.8  | 90.5  |     |        |

|                      | Signal-to-noise ratio,                               | RANGE = ±5V, f <sub>IN</sub> = 2kHz                       | 88.5  | 91.4  |     |        |

|                      | low-noise filter                                     | RANGE = ±7V, f <sub>IN</sub> = 2kHz                       | 89.3  | 91.3  |     |        |

| SINAD -              |                                                      | RANGE = ±10V, f <sub>IN</sub> = 2kHz                      | 89.9  | 91.8  |     |        |

|                      |                                                      | RANGE = ±12V, f <sub>IN</sub> = 2kHz                      | 90    | 92    |     | 4050   |

|                      |                                                      | RANGE = ±2.5V, f <sub>IN</sub> = 2kHz                     | 79    | 82.5  |     | dBFS   |

|                      |                                                      | RANGE = ±3.5V, f <sub>IN</sub> = 2kHz                     | 80    | 83.5  |     |        |

|                      | Signal-to-noise ratio,<br>wide-bandwidth filter      | RANGE = ±5V, f <sub>IN</sub> = 2kHz                       | 80.5  | 84.5  |     |        |

|                      |                                                      | RANGE = ±7V, f <sub>IN</sub> = 2kHz                       | 81.5  | 83.5  |     |        |

|                      |                                                      | RANGE = ±10V, f <sub>IN</sub> = 2kHz                      | 83    | 85    |     |        |

|                      |                                                      | RANGE = ±12V, f <sub>IN</sub> = 2kHz                      | 83.5  | 85.5  |     |        |

|                      | Signal-to-noise + distortion ratio, low-noise filter | RANGE = ±2.5V, f <sub>IN</sub> = 2kHz                     | 85.7  | 88.9  |     | - dB   |

|                      |                                                      | RANGE = ±3.5V, f <sub>IN</sub> = 2kHz                     | 86.7  | 89.9  |     |        |

|                      |                                                      | RANGE = ±5V, f <sub>IN</sub> = 2kHz                       | 87.3  | 90.7  |     |        |

|                      |                                                      | RANGE = ±7V, f <sub>IN</sub> = 2kHz                       | 88.0  | 90.6  |     |        |

|                      |                                                      | RANGE = ±10V, f <sub>IN</sub> = 2kHz                      | 88.5  | 91.1  |     |        |

|                      |                                                      | RANGE = ±12V, f <sub>IN</sub> = 2kHz                      | 88.6  | 91.3  |     |        |

| SINAD                |                                                      | RANGE = ±2.5V, f <sub>IN</sub> = 2kHz                     | 78.6  | 82.2  |     |        |

|                      |                                                      | RANGE = ±3.5V, f <sub>IN</sub> = 2kHz                     | 79.5  | 83.2  |     |        |

|                      | Signal-to-noise + distortion ratio,                  | RANGE = ±5V, f <sub>IN</sub> = 2kHz                       | 80.0  | 84.2  |     |        |

|                      | wide-bandwidth filter                                | RANGE = ±7V, f <sub>IN</sub> = 2kHz                       | 80.9  | 83.2  |     |        |

|                      |                                                      | RANGE = ±10V, f <sub>IN</sub> = 2kHz                      | 82.3  | 84.7  |     |        |

|                      |                                                      | RANGE = ±12V, f <sub>IN</sub> = 2kHz                      | 82.8  | 85.1  |     |        |

| TUD                  | T-A-III                                              | All ranges, low-noise filter, f <sub>IN</sub> = 2kHz      | ,     | -113  |     | ē      |

| IHD                  | Total harmonic distortion                            | All ranges, wide-bandwidth filter, f <sub>IN</sub> = 2kHz |       | -113  |     | dB     |

| SFDR                 | Spurious-free dynamic range                          | All ranges, f <sub>IN</sub> = 2kHz                        |       | 113   |     | dB     |

|                      | CMRR                                                 | at dc                                                     |       | -70   |     | dB     |

|                      | Isolation crosstalk                                  | at dc                                                     |       | -100  |     | dB     |

| NTERNA               | AL REFERENCE                                         |                                                           | ,     |       |     |        |

| / <sub>REF</sub> (1) | Voltage on REFIO pin (configured as output)          | 1μF capacitor on REFIO pin, T <sub>A</sub> = 25°C         | 4.092 | 4.096 | 4.1 | ٧      |

|                      | Reference temperature drift <sup>(4)</sup>           |                                                           |       | 10    | 25  | ppm/°C |

## 5.5 Electrical Characteristics (continued)

at AVDD\_5V = 4.75 V to 5.25 V, VDD\_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V, V<sub>REF</sub> = 4.096 V (internal or external), wide-common-mode disabled for analog input ranges  $\pm 2.5$ V,  $\pm 3.5$ V, and  $\pm 5$ V, wide-common-mode enabled for analog input ranges  $\pm 7$ V,  $\pm 10$ V, and  $\pm 12$ V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to  $\pm 125$ °C; typical values at  $T_A = 25$ °C

|                      | PARAMETER                           | TEST CONDITIONS                        | MIN       | TYP | MAX       | UNIT |

|----------------------|-------------------------------------|----------------------------------------|-----------|-----|-----------|------|

| DIGITAL              | INPUTS                              |                                        |           |     |           |      |

| V <sub>IL</sub>      | Input low logic level               |                                        | -0.3      |     | 0.3 IOVDD | V    |

| V <sub>IH</sub>      | Input high logic level              |                                        | 0.7 IOVDD |     | IOVDD     | V    |

|                      | Input current                       |                                        |           | 0.1 |           | μA   |

|                      | Input capacitance                   |                                        |           | 6   |           | pF   |

| LVDS SA              | MPLING CLOCK INPUT                  |                                        |           |     | ,         |      |

| .,                   | I link to a line was to a like an   | AC coupled                             | 100       |     |           | \/   |

| $V_{TH}$             | High-level input voltage            | DC coupled                             | 300       |     |           | mV   |

|                      | I I I I I I                         | AC coupled                             |           |     | -100      | \/   |

| $V_{TL}$             | Low-level input voltage             | DC coupled                             |           |     | -300      | mV   |

| V <sub>ICM</sub>     | Input common-mode voltage           |                                        | 0.3       | 1.2 | 1.4       | V    |

| DIGITAL              | OUTPUTS                             |                                        |           |     |           |      |

| V <sub>OL</sub>      | Output low logic level              | I <sub>OL</sub> = 500μA sink           | 0         |     | 0.2 IOVDD | V    |

| V <sub>OH</sub>      | Output high logic level             | I <sub>OH</sub> = 500μA source         | 0.8 IOVDD |     | IOVDD     | V    |

| POWER                | SUPPLY - ADS9817                    |                                        |           |     | <u> </u>  |      |

|                      | Total power dissipation             | Maximum throughput                     |           | 232 | 304       | mW   |

|                      | 0                                   | Maximum throughput, internal reference |           | 26  | 32        | ^    |

| I <sub>AVDD_5V</sub> | Supply current from AVDD_5V         | Power-down                             |           | 0.2 | 2         | mA   |

|                      | 0                                   | Maximum throughput, internal reference |           | 50  | 70        | ^    |

| I <sub>VDD_1V8</sub> | Supply current from VDD_1V8         | Power-down                             |           | 0.2 | 8         | mA   |

|                      | 0                                   | Maximum throughput                     |           | 7   | 10        | ^    |

| I <sub>IOVDD</sub>   | Supply current from IOVDD           | Power-down                             |           | 0.1 | 3         | mA   |

| POWER                | SUPPLY - ADS9815                    |                                        |           |     |           |      |

|                      | Total power dissipation             | Maximum throughput                     |           | 165 | 215       | mW   |

|                      | 0                                   | Maximum throughput, internal reference |           |     |           |      |

| I <sub>AVDD_5V</sub> | Supply current from AVDD_5V         | Power-down                             |           | 0.2 | 2         | mA   |

|                      | Committee and the second AVID 11/10 | Maximum throughput, internal reference |           | 35  | 43        | Λ    |

| I <sub>VDD_1V8</sub> | Supply current from VDD_1V8         | Power-down                             |           | 0.2 | 8         | mA   |

|                      | 0                                   | Maximum throughput                     |           | 4   | 7         | ^    |

| I <sub>IOVDD</sub>   | Supply current from IOVDD           | Power-down                             |           | 0.1 | 3         | mA   |

<sup>(1)</sup> Does not include the variation in voltage resulting from solder shift effects.

<sup>(2)</sup> These specifications include full temperature range variation but not the error contribution from internal reference. Measured with single-ended inputs as described in Wide Common-Mode Configuration for Single-Ended Inputs

<sup>(3)</sup> Wide-CM refers to wide-common-mode voltage at the analog inputs. See section on Section 6.3.1.3 for more details.

<sup>(4)</sup> Thermal drift is the difference between maximum and minimum error measured over the temperature range, divided by the temperature range.

<sup>(5)</sup> Minimum and maximum specifications are applicable for low-bandwidth filter setting.

# 5.6 Timing Requirements

at AVDD\_5V = 4.75 V to 5.25 V, VDD\_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to +125°C; typical values at  $T_A = 25$ °C

|                          |                                                            |         | MIN                        | MAX                        | UNIT             |

|--------------------------|------------------------------------------------------------|---------|----------------------------|----------------------------|------------------|

| CONVERSION               | CYCLE                                                      |         |                            |                            |                  |

| f <sub>SMPL_CLK</sub>    | Sampling frequency                                         | ADS9817 | 3.9                        | 8.1                        | MHz              |

| f <sub>SMPL_CLK</sub>    | Sampling frequency                                         | ADS9815 | 3.9                        | 4.1                        | MHz              |

| t <sub>SMPL_CLK</sub>    | Sampling time interval                                     |         | 1 / f <sub>SMPL_CLK</sub>  |                            | ns               |

| t <sub>PL_SMPL_CLK</sub> | SMPL_CLK low time                                          |         | 0.45 t <sub>SMPL_CLK</sub> | 0.55 t <sub>SMPL_CLK</sub> | ns               |

| t <sub>PH_SMPL_CLK</sub> | SMPL_CLK high time                                         |         | 0.45 t <sub>SMPL_CLK</sub> | 0.55 t <sub>SMPL_CLK</sub> | ns               |

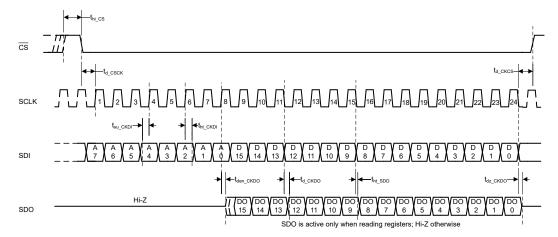

| SPI INTERFACE            | TIMINGS (CONFIGURATION INTERFACE)                          |         |                            |                            |                  |

| f <sub>SCLK</sub>        | Maximum SCLK frequency                                     |         |                            | 20                         | MHz              |

| t <sub>PH_CK</sub>       | SCLK high time                                             |         | 0.48                       | 0.52                       | t <sub>CLK</sub> |

| t <sub>PL_CK</sub>       | SCLK low time                                              |         | 0.48                       | 0.52                       | t <sub>CLK</sub> |

| t <sub>hi_CS</sub>       | Pulse duration: CS high                                    |         | 220                        |                            | ns               |

| t <sub>d_CSCK</sub>      | Delay time: CS falling to the first SCLK capture edge      |         | 20                         |                            | ns               |

| t <sub>su_CKDI</sub>     | Setup time: SDI data valid to the SCLK rising edge         |         | 10                         |                            | ns               |

| t <sub>ht_CKDI</sub>     | Hold time: SCLK rising edge to data valid on SDI           |         | 5                          |                            | ns               |

| t <sub>D_CKCS</sub>      | Delay time: last SCLK falling to CS rising                 | 5       |                            | ns                         |                  |

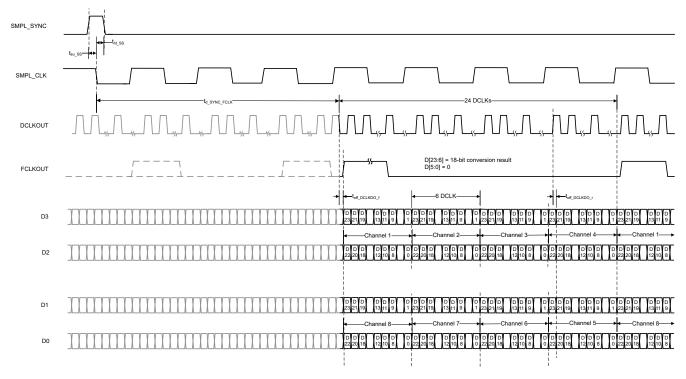

| CMOS DATA IN             | TERFACE                                                    |         |                            |                            |                  |

| t <sub>su_SS</sub>       | Setup time: SMPL_SYNC rising edge to SMPL_CLK falling edge |         | 10                         |                            | ns               |

| t <sub>ht_SS</sub>       | Hold time: SMPL_CLK falling edge to SMPL_SYNC high         | 10      |                            | ns                         |                  |

|                          |                                                            |         |                            |                            |                  |

# 5.7 Switching Characteristics

at AVDD\_5V = 4.75 V to 5.25 V, VDD\_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to +125°C; typical values at  $T_A = 25$ °C

|                           | PARAMETER                                                                               | TEST CONDITIONS | MIN                         | MAX                         | UNIT                 |  |

|---------------------------|-----------------------------------------------------------------------------------------|-----------------|-----------------------------|-----------------------------|----------------------|--|

| RESET                     |                                                                                         |                 |                             |                             |                      |  |

| t <sub>PU</sub>           | Power-up time for device                                                                |                 |                             | 25                          | ms                   |  |

| SPI INTERFA               | CE TIMINGS (CONFIGURATION INTERFACE                                                     | ≡)              |                             |                             |                      |  |

| t <sub>den_CKDO</sub>     | Delay time: 8 <sup>th</sup> SCLK rising edge to data enable                             |                 |                             | 22                          | ns                   |  |

| t <sub>dz_CKDO</sub>      | Delay time: 24 <sup>th</sup> SCLK rising edge to SDO going Hi-Z                         |                 |                             | 50                          | ns                   |  |

| t <sub>d_CKDO</sub>       | Delay time: SCLK falling edge to corresponding data valid on SDO                        |                 |                             | 16                          | ns                   |  |

| t <sub>ht_CKDO</sub>      | Delay time: SCLK falling edge to previous data valid on SDO                             |                 | 2                           |                             | ns                   |  |

| CMOS DATA                 | INTERFACE                                                                               |                 |                             |                             |                      |  |

| +                         | Data clock output                                                                       | DDR mode        | 10                          |                             |                      |  |

| t <sub>DCLK</sub>         | Data clock output                                                                       | SDR mode        | 20                          |                             | ns                   |  |

|                           | Clock duty cycle                                                                        |                 | 45                          | 55                          | %                    |  |

| t <sub>off_DCLKDO_r</sub> | Time offset: DCLK rising to corresponding data valid                                    | DDR mode        | t <sub>DCLK</sub> / 4 – 1.5 | t <sub>DCLK</sub> / 4 + 1.5 | ns                   |  |

| t <sub>off_DCLKDO_f</sub> | Time offset: DCLK falling to corresponding data valid                                   | DDR mode        | t <sub>DCLK</sub> / 4 – 1.5 | t <sub>DCLK</sub> / 4 + 1.5 | ns                   |  |

| t <sub>d_DCLKDO</sub>     | Time delay: DCLK rising to corresponding data valid                                     | SDR mode        | <b>–1</b>                   | 1                           | ns                   |  |

| t <sub>d_SYNC_FCLK</sub>  | Time delay: SMPL_CLK falling edge with SYNC signal to corresponding FCLKOUT rising edge |                 | 3                           | 4                           | t <sub>SMPL_CL</sub> |  |

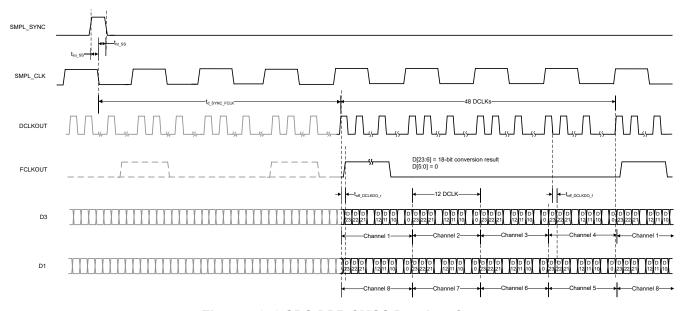

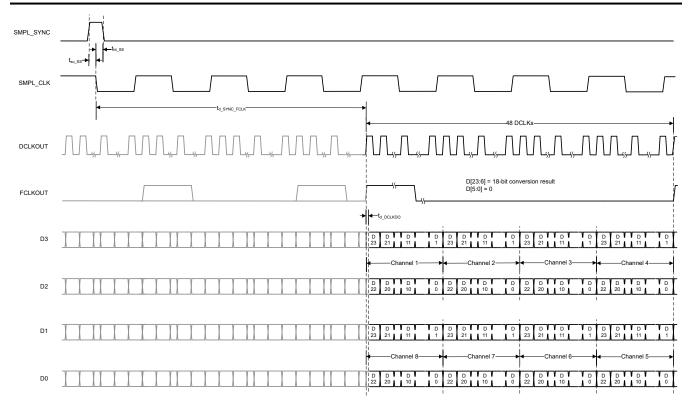

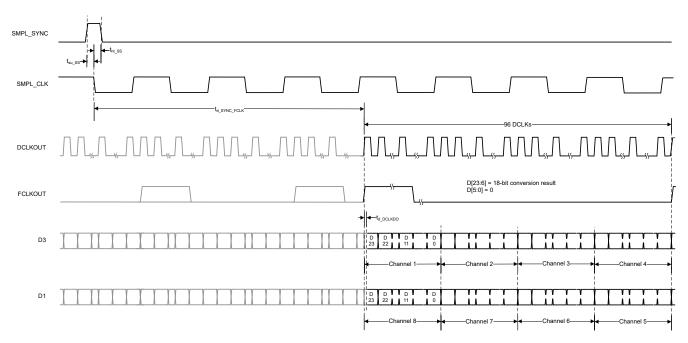

### 5.8 Timing Diagrams

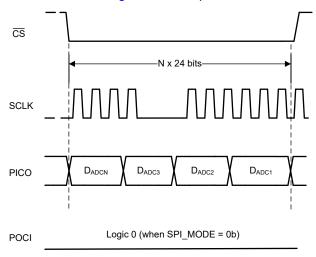

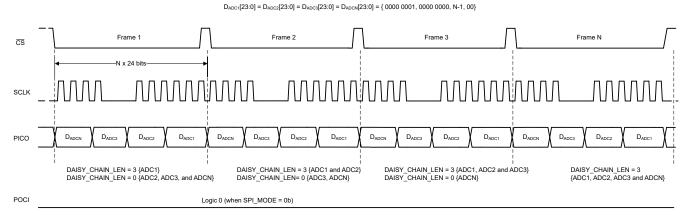

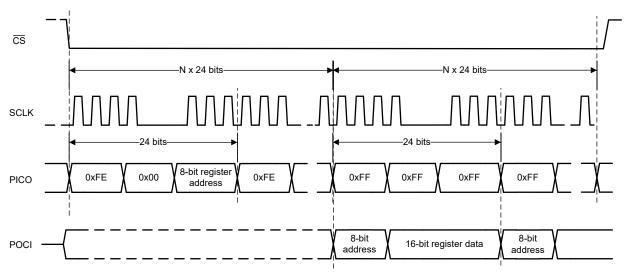

Figure 5-1. SPI Configuration Interface

Figure 5-2. 4-SDO DDR CMOS Data Interface

Figure 5-3. 2-SDO DDR CMOS Data Interface

Figure 5-4. 4-SDO SDR CMOS Data Interface

Figure 5-5. 2-SDO SDR CMOS Data Interface

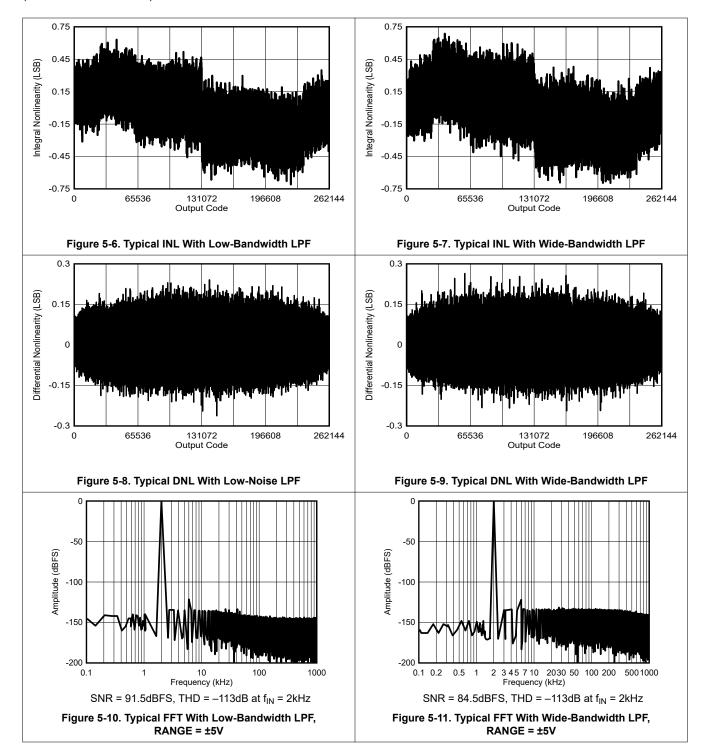

### 5.9 Typical Characteristics

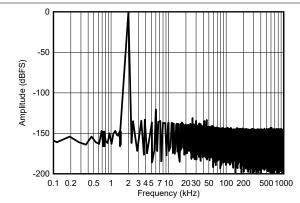

SNR = 92.1dBFS, THD = -113dB at  $f_{IN}$  = 2kHz

Figure 5-12. Typical FFT With Low-Bandwidth LPF, RANGE = ±10V

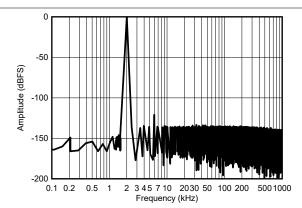

SNR = 85.5dBFS, THD = -113dB at  $f_{IN}$  = 2kHz

Figure 5-13. Typical FFT With Wide-Bandwidth LPF, RANGE = ±10V

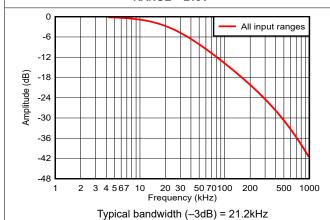

Figure 5-14. Low-Bandwidth LPF Frequency Response Across Input Ranges

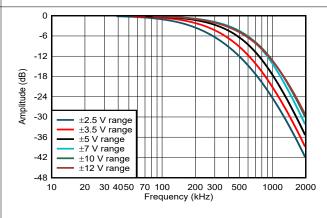

Figure 5-15. Wide-Bandwidth LPF Frequency Response Across Input Ranges

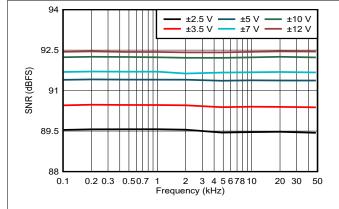

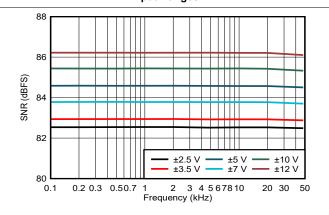

Figure 5-16. SNR vs Input Signal Frequency Across Input Ranges With Low-Bandwidth LPF

Figure 5-17. SNR vs Input Signal Frequency Across Input Ranges With Wide-Bandwidth LPF

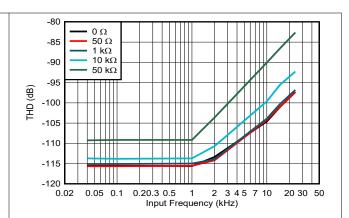

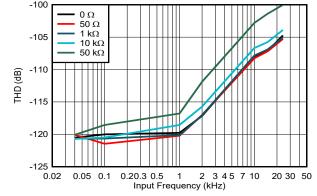

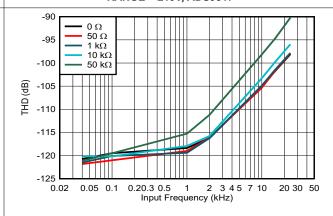

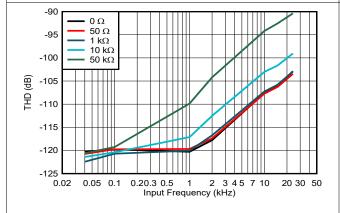

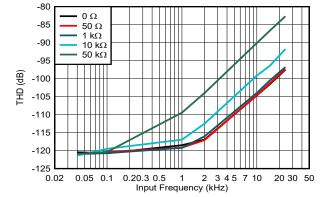

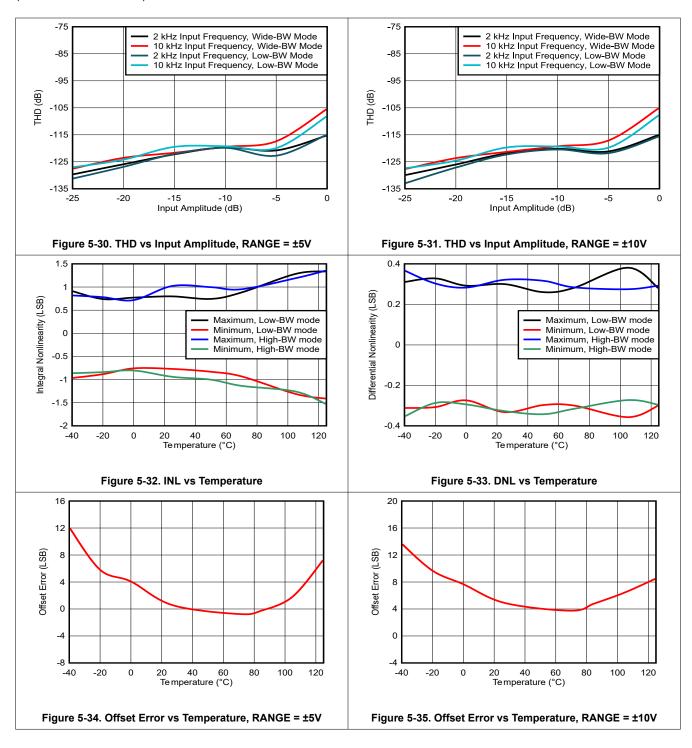

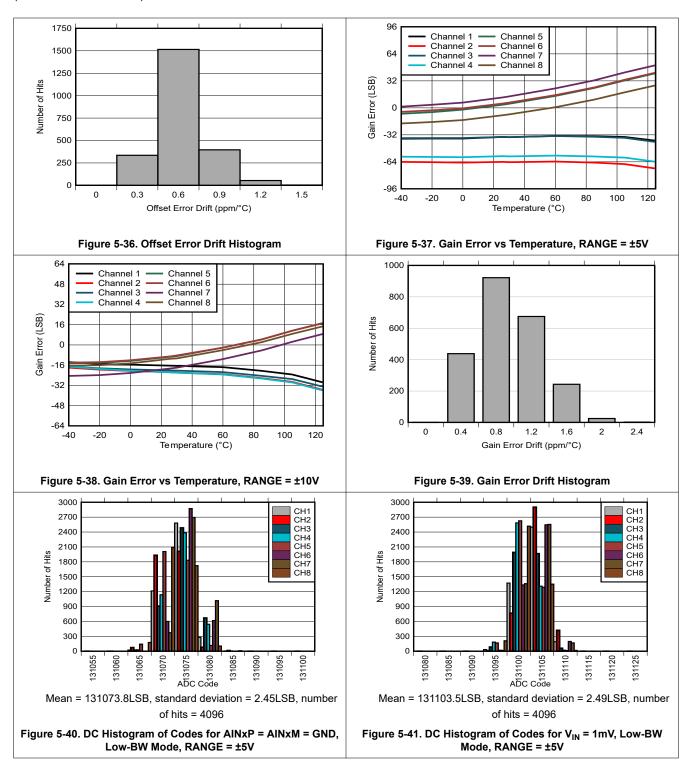

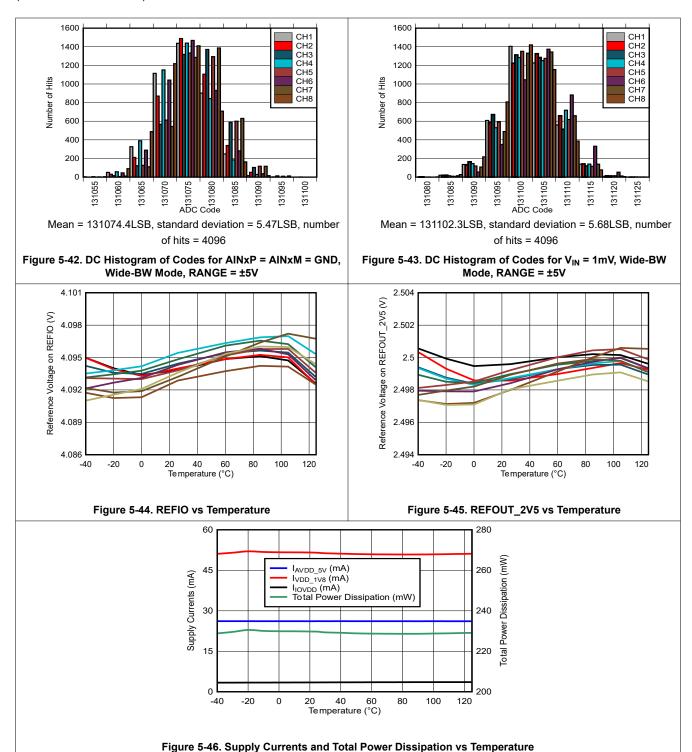

at  $T_A$  = 25°C, AVDD\_5V = 5V, VDD\_1V8 = 1.8V, internal  $V_{REF}$  = 4.096V, ±5V analog input range, and maximum throughput (unless otherwise noted)

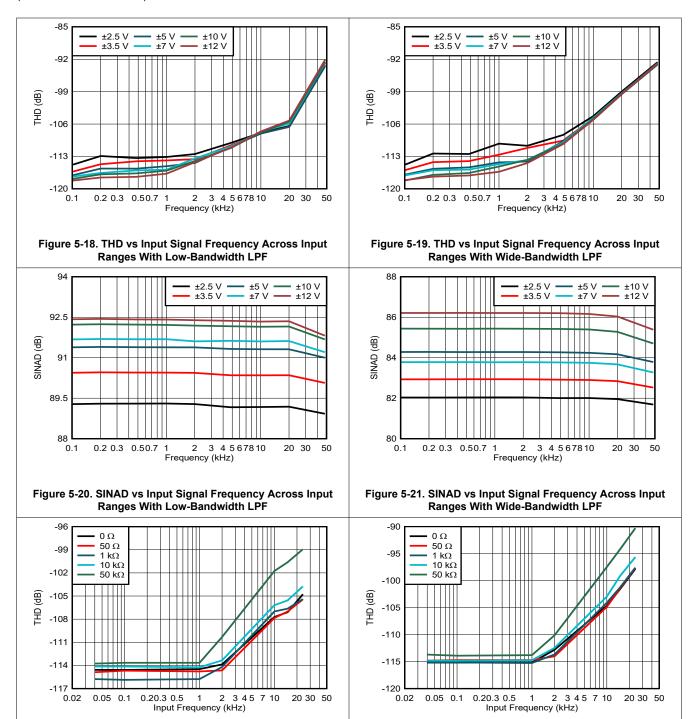

Figure 5-22. THD vs Input Frequency, Low-BW Mode,

RANGE = ±5V, ADS9817

Figure 5-23. THD vs Input Frequency, High-BW Mode,

RANGE = ±5V, ADS9817

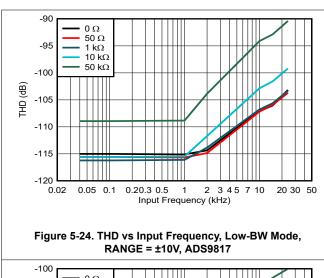

Figure 5-25. THD vs Input Frequency, High-BW Mode, RANGE = ±10V, ADS9817

Figure 5-26. THD vs Input Frequency, Low-BW Mode, RANGE = ±5V, ADS9815

Figure 5-27. THD vs Input Frequency, High-BW Mode, RANGE = ±5V, ADS9815

Figure 5-28. THD vs Input Frequency, Low-BW Mode, RANGE = ±10V, ADS9815

Figure 5-29. THD vs Input Frequency, High-BW Mode, RANGE = ±10V, ADS9815

# 6 Detailed Description

#### 6.1 Overview

The ADS981x is an 18-bit data acquisition (DAQ) system with eight-channel analog inputs that can be configured as either single-ended or differential. Each analog input channel consists of an input clamp protection circuit, and a programmable gain amplifier (PGA) with user-selectable bandwidth options. The input signals are digitized using an 18-bit analog-to-digital converter (ADC), based on the successive approximation register (SAR) architecture. This overall system can achieve a maximum throughput of 2 MSPS/channel for all channels. The device features a 4.096V internal reference with a fast-settling buffer.

The device operates from 5V and 1.8V analog supplies and can accommodate true bipolar input signals. The input clamp protection circuitry can tolerate voltages up to  $\pm 18V$ . The device offers a constant  $1M\Omega$  resistive input impedance irrespective of the sampling frequency or the selected input range. The ADS981x offers a simplified end solution without requiring external high-voltage bipolar supplies and complicated driver circuits.

### 6.2 Functional Block Diagram

### **6.3 Feature Description**

#### 6.3.1 Analog Inputs

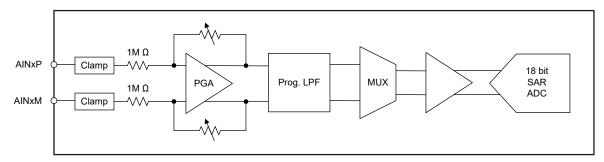

The ADS981x incorporates dual, simultaneous-sampling, 18-bit successive approximation register (SAR) analog-to-digital converters (ADCs). Each ADC is connected to four analog input channels through a multiplexer. The device has a total of eight analog input pairs. The ADC digitizes the voltage difference between the analog input pairs AINxP – AINxM. Figure 6-1 shows the simplified circuit schematic for each analog input channel, including the input clamp protection circuit, PGA, low-pass filter, multiplexer, high-speed ADC driver, and a precision 18-bit SAR ADC.

Figure 6-1. Front-End Circuit Schematic for the Selected Analog Input Channel

### 6.3.1.1 Input Clamp Protection Circuit

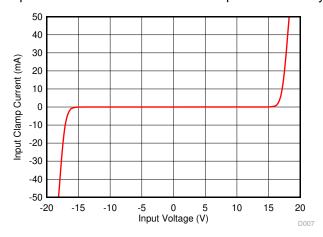

The ADS981x features an internal clamp protection circuit on each of the eight analog input channels, see Figure 6-1. The input clamp protection circuit allows each analog input to swing up to a maximum voltage of ±18V. Beyond an input voltage of ±18V, the input clamp circuit turns on and still operates from the single 5V supply. Figure 6-2 shows a typical current versus voltage characteristic curve for the input clamp.

For input voltages above the clamp threshold, make sure that the input current never exceeds ±10mA. A resistor placed in series with the analog inputs is an effective way to limit the input current. In addition to limiting the input current, the series resistor can also provide an antialiasing, low-pass filter (LPF) when coupled with a capacitor. Matching the external source impedance on the AINxP and AINxM pins cancels any additional offset error.

Figure 6-2. Input Protection Clamp Profile, Input Clamp Current vs Source Voltage

### 6.3.1.2 Programmable Gain Amplifier (PGA)

The ADS981x features a PGA at every analog input channel. The PGA supports single-ended and differential inputs with a bipolar signal swing. Table 6-1 lists the supported analog input ranges. The analog input range can be configured independently for each channel by using the RANGE\_CHx register fields in address 0xC2 and address 0xC3.

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

Table 6-1. Analog Input Ranges

| <u> </u>            |                                                                                                                                                                                                                      |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SINGLE-ENDED INPUTS | RANGE_CHx CONFIGURATION                                                                                                                                                                                              |  |  |  |

| ±12V                | 5                                                                                                                                                                                                                    |  |  |  |

| ±10V                | 4                                                                                                                                                                                                                    |  |  |  |

| ±7V                 | 3                                                                                                                                                                                                                    |  |  |  |

| ±5V                 | 0                                                                                                                                                                                                                    |  |  |  |

| ±3.5V               | 1                                                                                                                                                                                                                    |  |  |  |

| ±2.5V               | 2                                                                                                                                                                                                                    |  |  |  |

|                     | \$\frac{\pmathrm{\text{single-ended inputs}}{\pmathrm{\pmathrm{\text{t}}12V}} \\ \pmathrm{\pmathrm{\pmathrm{\pmathrm{t}}}27V} \\ \pmathrm{\pmathrm{\pmathrm{\pmathrm{t}}25V}} \\ \pmathrm{\pmathrm{\pmathrm{t}}3.5V} |  |  |  |

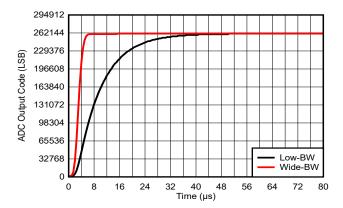

Each analog input channel features an antialiasing, low-pass filter (LPF) at the output of the PGA. Table 6-2 lists the various programmable LPF options available in the ADS981x corresponding to the analog input range. Figure 5-14 and Figure 5-15 illustrate the frequency responses for low-bandwidth and wide-bandwidth LPF configurations. The analog input bandwidth for the eight analog input channels can be can be selected using the ANA\_BW[7:0] bits in address 0xC0 of register bank 1.

Table 6-2. Low-Pass Filter Corner Frequency

| LPF             | ANALOG INPUT RANGE | CORNER FREQUENCY (-3dB) |

|-----------------|--------------------|-------------------------|

| Low-bandwidth   | All input ranges   | 21kHz                   |

|                 | ±12V               | 375kHz                  |

|                 | ±10V               | 385kHz                  |

| Wide-bandwidth  | ±7V                | 400kHz                  |

| Wide-paridwidth | ±5V                | 320kHz                  |

|                 | ±3.5V              | 240kHz                  |

|                 | ±2.5V              | 182kHz                  |

#### 6.3.1.3 Wide-Common-Mode Voltage Rejection Circuit

The ADS981x features a common-mode (CM) rejection circuit at the analog inputs that supports CM voltages up to  $\pm 12$ V. The CM voltage for differential inputs is given by Equation 1. On power-up or after reset, the common-mode voltage range for the analog input channels is  $\pm 12$ V (CM\_CTRL\_EN = 0b). Voltage at the analog inputs, in all cases, must be within the *Absolute Maximum Ratings*.

Common mode voltage =

$$\frac{\text{(Voltage on AINP)} + \text{(Voltage on AINM)}}{2}$$

(1)

As described in Table 6-3, the CM voltage rejection circuit can be optimized for various CM voltages for differential inputs.

Table 6-3. Wide Common-Mode Configuration for Differential Inputs

| garanon ioi zinian inpate |            |               |                                      |               |                      |  |

|---------------------------|------------|---------------|--------------------------------------|---------------|----------------------|--|

| COMMON-MODE<br>(CM) RANGE | CM_CTRL_EN |               | ADC A<br>(ANALOG INPUT CHANNELS 1–4) |               | C B<br>CHANNELS 5–8) |  |

| (CW) RANGE                |            | CM_EN_CH[4:1] | CM_RNG_CH[4:1]                       | CM_EN_CH[8:5] | CM_RNG_CH[8:5]       |  |

| CM ≤ ±1V                  |            | 0             | Don't care                           | 0             | Don't care           |  |

| CM ≤ ±RANGE / 2           | 1          |               | 0                                    | 1             | 0                    |  |

| CM ≤ ±6V                  | , I        | 1             | 1                                    |               | 1                    |  |

| CM ≤ ±12V                 |            |               | 2                                    |               | 2                    |  |

The CM voltage rejection circuit must be configured depending on the analog input range of the PGA when using single-ended inputs as well. Table 6-4 lists the recommended configuration for single-ended inputs for various analog input voltage ranges.

Table 6-4. Wide Common-Mode Configuration for Single-Ended Inputs

| PGA ANALOG<br>INPUT RANGE | CM_CTRL_EN | ADC A (ANALOG INPUT CHANNELS |                | ADC B (ANALOG INPUT CHANNELS 5–8) |                |

|---------------------------|------------|------------------------------|----------------|-----------------------------------|----------------|

| INFOTRANGE                |            | CM_EN_CH[4:1]                | CM_RNG_CH[4:1] | CM_EN_CH[8:5]                     | CM_RNG_CH[8:5] |

| ±2.5V, ±3.5V, and ±5V     | 1          | 0                            | Don't care     | 0                                 | Don't care     |

| ±7V, ±10V, and ±12V       |            | 1                            | 0              | 1                                 | 0              |

#### 6.3.1.4 Gain Error Calibration

The ADS981x features calibration logic to minimize gain error from the analog inputs. Enable gain error calibration for minimum gain error. Gain error calibration can be enabled by configuring the GE\_CAL\_EN1 (address = 0xD), GE\_CAL\_EN2, GE\_CAL\_EN3 (address = 0x33), and GE\_CAL\_EN4 (address = 0x34).

If gain error calibration is not enabled as shown in Table 6-5, the full-scale analog input ranges are increased by a factor of 1.024.

Table 6-5. Analog Input Ranges vs Gain-Error Calibration

| RANGE_CHx CONFIGURATION | ANALOG INPUT RANGE WITH CALIBRATION | ANALOG INPUT RANGE WITHOUT CALIBRATION |

|-------------------------|-------------------------------------|----------------------------------------|

| 5                       | ±12V                                | ±12.288V                               |

| 4                       | ±10V                                | ±10.24V                                |

| 3                       | ±7V                                 | ±7.168V                                |

| 0                       | ±5V                                 | ±5.12V                                 |

| 1                       | ±3.5V                               | ±3.584V                                |

| 2                       | ±2.5V                               | ±2.56V                                 |

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

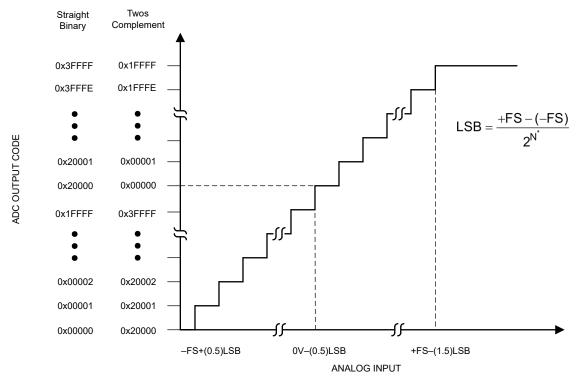

#### 6.3.2 ADC Transfer Function

The ADS981x outputs 18 bits of conversion data in either straight-binary or binary two's-complement formats. The format for the output codes is the same across all analog channels. The format for the output codes can be selected using the DATA\_FORMAT field in address 0xD in register bank 1. Figure 6-3 and Table 6-6 show the transfer characteristics for the ADS981x. The LSB size depends on the analog input range selected, gain-error calibration, and system gain error calibration as shown in Equation 2.

$$LSB = \frac{Analog input range}{2^{18}} \times \left(1 + G \times 0.024\right)$$

(2)

where:

• G is 0 when gain-error calibration is enabled, otherwise G is1; see the Gain Error Calibration section

Figure 6-3. Transfer Characteristics

Table 6-6. ADC Full-Scale Range and LSB Size

| RANGE | +FS  | MIDSCALE | -FS   | LSB     |

|-------|------|----------|-------|---------|

| ±2.5V | 2.5V | 0V       | –2.5V | 19.07µV |

| ±3.5V | 3.5V | 0V       | -3.5V | 26.70µV |

| ±5V   | 5V   | 0V       | -5V   | 38.15µV |

| ±7V   | 7V   | 0V       | -7V   | 53.41µV |

| ±10V  | 10V  | 0V       | -10V  | 76.29µV |

| ±12V  | 12V  | 0V       | –12V  | 91.55µV |

### 6.3.3 ADC Sampling Clock Input

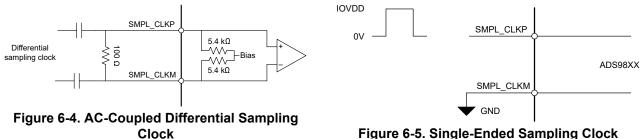

Use a low-jitter external clock with a high slew rate to maximize SNR performance. The ADS981x can be operated with a differential or a single-ended clock input. Clock amplitude impacts the ADC aperture jitter and consequently the SNR. For maximum SNR performance, provide a clock signal with fast slew rates that maximizes swing between IOVDD and GND levels.

The sampling clock must be a free-running continuous clock. The ADC generates a valid output data, data clock, and frame clock after a free-running sampling clock is applied. The ADC is powered down and output data, data clock, and frame clock are invalid when the sampling clock is stopped.

Figure 6-4 shows a diagram of the differential sampling clock input. For this configuration, connect the differential sampling clock input to the SMPL\_CLKP and SMPL\_CLKM pins. Figure 6-5 shows a diagram of the singleended sampling clock input. In this configuration, connect the single-ended sampling clock to SMPL CLKP and connect SMPL\_CLKM to ground.

Figure 6-5. Single-Ended Sampling Clock

#### 6.3.4 Reference

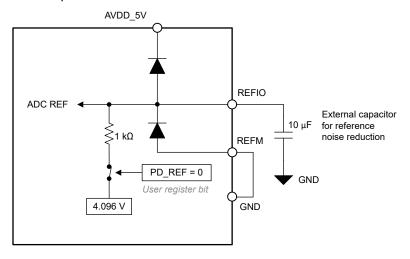

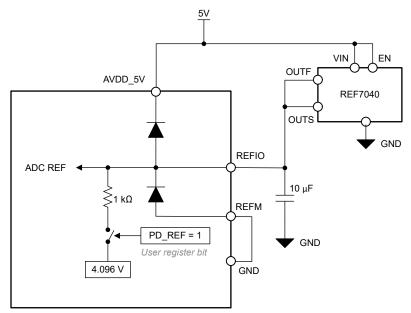

The ADS981x has a precision, low-drift voltage reference internal to the device. For best performance, filter the internal reference noise by connecting a 10µF ceramic bypass capacitor to the REFIO pin. An external reference can also be connected at the REFIO pin and the internal reference voltage can be disabled by writing to PD REF = 1b in address 0xC1 of register bank 1.

### 6.3.4.1 Internal Reference Voltage

The ADS981x features an internal reference voltage with a nominal output voltage of 4.096V. On power-up, the internal reference is enabled by default. As shown in Figure 6-6, place a minimum 10µF decoupling capacitor between the REFIO and REFM pins.

Figure 6-6. Internal Reference Voltage

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

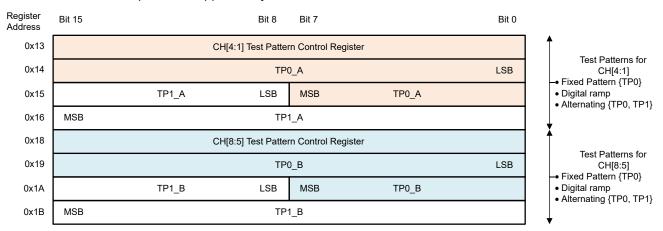

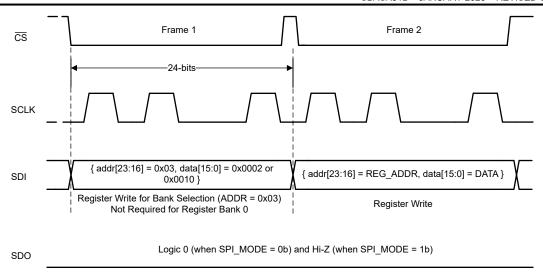

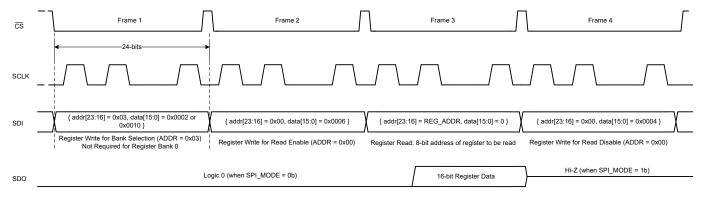

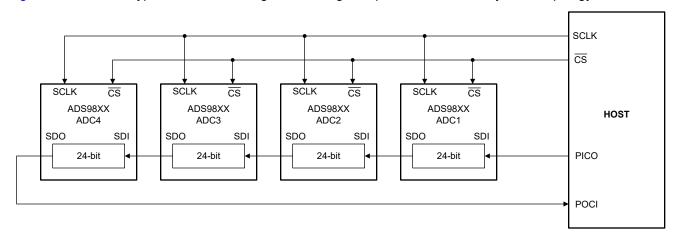

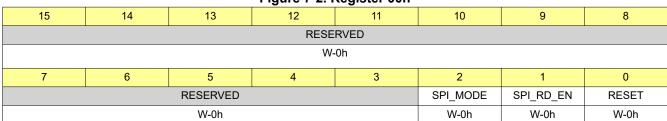

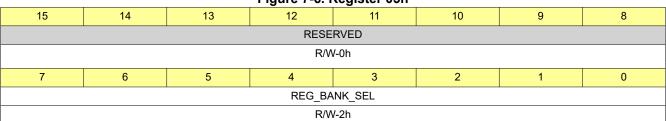

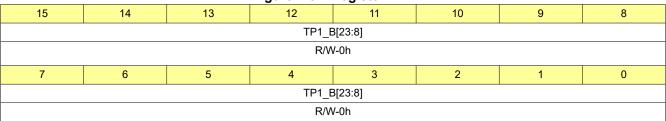

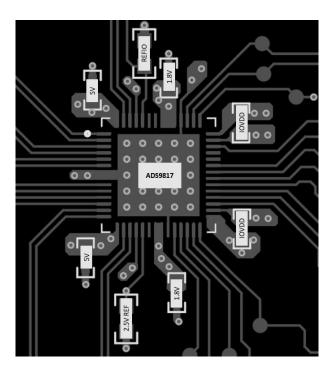

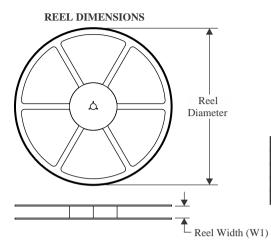

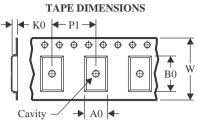

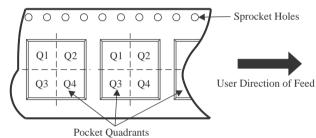

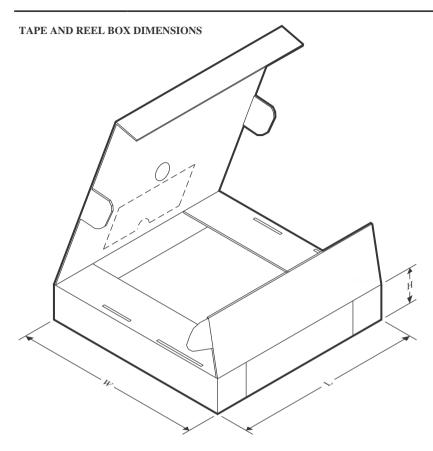

#### 6.3.4.2 External Reference Voltage