# Two-String LED Driver with I<sup>2</sup>C OTP ROM Current Trim

Check for Samples: TPS92660

#### **FEATURES**

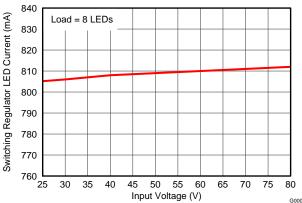

- Input Voltage: Up to 80 V

- Two-Output LED Current Controller

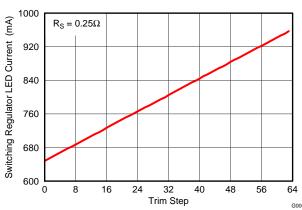

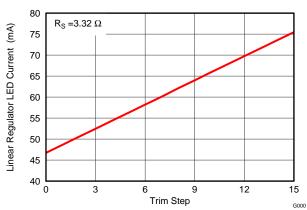

- LED Currents Trimmed Through One-Time Programmable (OTP) ROM with I<sup>2</sup>C Interface

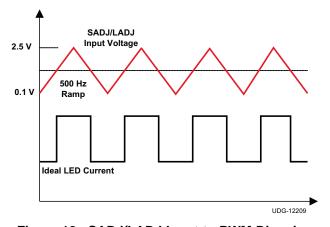

- Adjustable SADJ and LADJ Pins for PWM Dimming of Each LED String

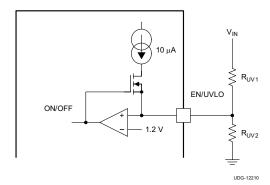

- Input Undervoltage Lockout and Output Overvoltage Protection

- Enable On/Off

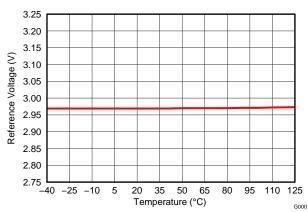

- Accurate 3.0-V Reference Voltage

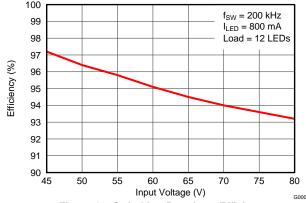

- > 95% Efficiency

- Thermal Shutdown Protection

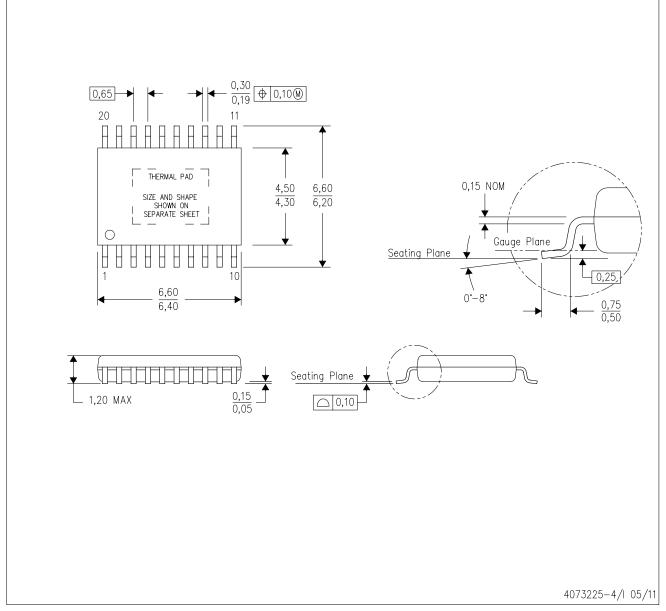

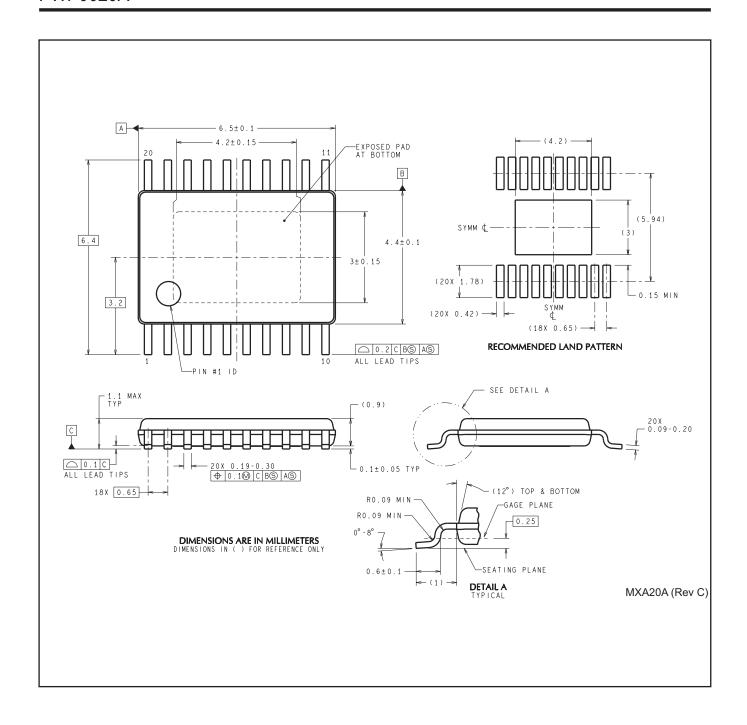

- 20-pin TSSOP Exposed Pad Package

#### **APPLICATIONS**

- Professional Lighting

- Industrial and Commercial Lighting

- General Illumination

#### DESCRIPTION

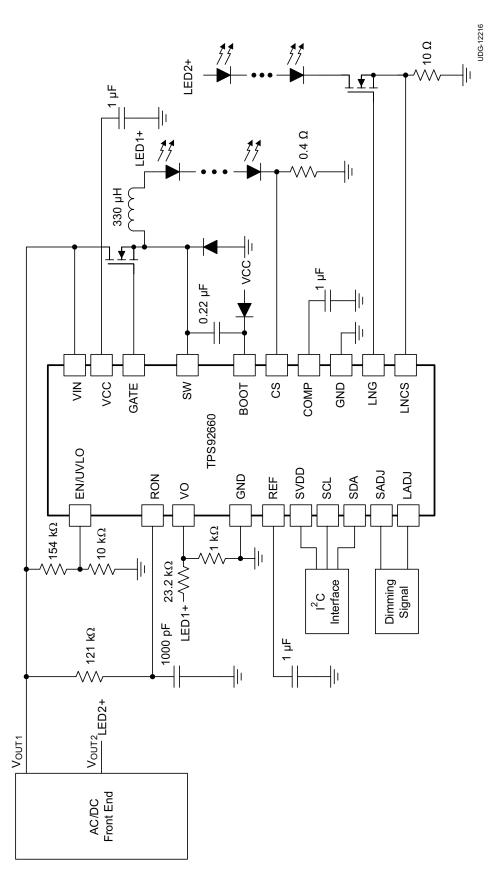

The TPS92660 is a two-output LED driver with one time programmable (OTP) ROM and I<sup>2</sup>C interface for LED current trim. The current trim provides a way for LED fixture manufacturers to produce LED lighting fixtures at a consistent lumen output without binning LEDs.

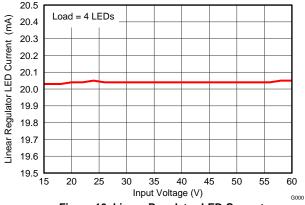

One output of the device is a non-synchronous buck controller which is used to regulate current of higher power white LEDs. The other output of the device is a linear regulator controller which is used to regulate current of lower power red LEDs. The TPS92660 is used for applications of controlled CCT (correlated color temperature) LED lights by mixing white LEDs with red LEDs.

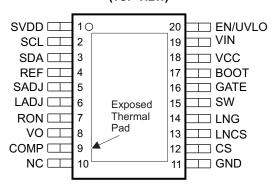

This device is available in a 20-pin, TSSOP exposed pad package.

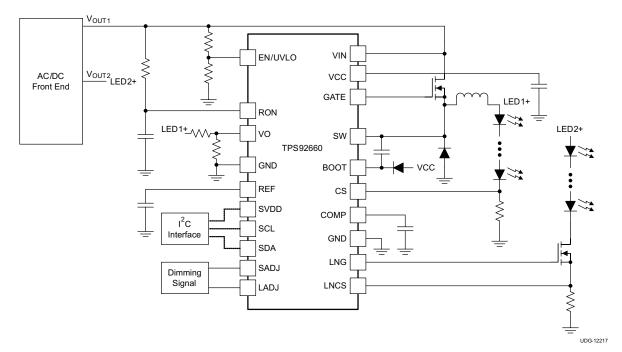

#### TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

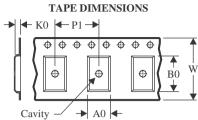

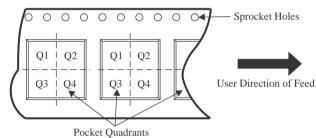

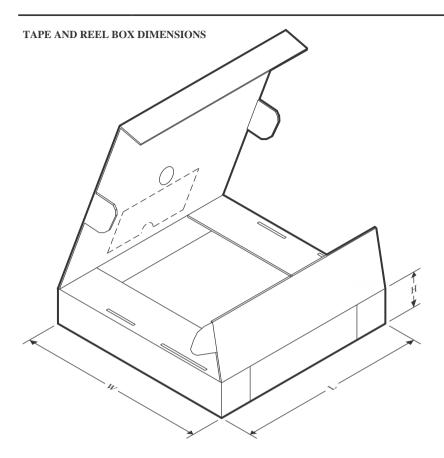

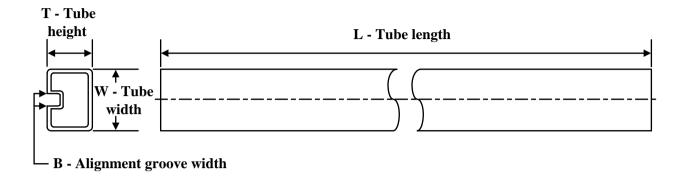

## ORDERING INFORMATION(1) (2)

| TJ             | PACKAGE            | ORDERABLE<br>DEVICE NUMBER | PINS | OUTPUT SUPPLY | MINIMUM ORDER QUANTITY |

|----------------|--------------------|----------------------------|------|---------------|------------------------|

| -40°C to 125°C | TCCOD avenaged and | TPS92660PWP                | 20   | Tube          | 73                     |

|                | TSSOP exposed pad  | TPS92660PWPR               | 20   | Tape and Reel | 2500                   |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the TI website at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                    |                                                                                                                                             | VALU | VALUE |      |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|

|                                    |                                                                                                                                             | MIN  | MAX   | UNIT |

| Supply voltage                     | VCC                                                                                                                                         | -0.3 | 14    |      |

| (2)                                | VIN, UVLO/EN                                                                                                                                | -0.3 | 80    |      |

|                                    | BOOT to SW                                                                                                                                  | -0.3 | 14    |      |

|                                    | SADJ, LADJ, RON, VO, COMP, CS, LNCS                                                                                                         | -0.3 | 6     | V    |

| Input voltage range <sup>(2)</sup> | SW                                                                                                                                          | -2.0 | 80    |      |

|                                    | воот                                                                                                                                        | -0.3 | 90    |      |

|                                    | SVDD, SCL, SDA                                                                                                                              | -0.3 | 5.5   |      |

| Electronic Co. Posteron            | Human body model (HBM) QSS 009-105 (JESD22-A114A)                                                                                           |      | 2000  | V    |

| Electrostatic discharge            | BOOT -0.3  SVDD, SCL, SDA -0.3  Human body model (HBM) QSS 009-105 (JESD22-A114A)  Charged device model (CDM) QSS 009-147 (JESD22-C101B.01) | 750  |       |      |

| Junction temperature rai           | nge, T <sub>J</sub> <sup>(3)</sup>                                                                                                          |      | 165   | °C   |

| Storage temperature ran            | ige, T <sub>stg</sub>                                                                                                                       | -55  | 150   |      |

| Lead temperature range             | , soldering, 10 s                                                                                                                           |      | 260   |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted.

<sup>(3)</sup> Maximum junction temperature is internally limited

#### THERMAL INFORMATION

|                  |                                                           | TPS92660                |       |

|------------------|-----------------------------------------------------------|-------------------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                             | TSSOP exposed pad (PWP) | UNITS |

|                  |                                                           | 20 PINS                 |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (2)                | 36.9                    |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)             | 22.7                    |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance <sup>(4)</sup>       | 18.6                    | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup> | 0.6                     | C/VV  |

| ΨЈВ              | Junction-to-board characterization parameter (6)          | 18.4                    |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (7)          | 1.9                     |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                      |                                                           | MIN | MAX | UNIT |

|----------------------|-----------------------------------------------------------|-----|-----|------|

| $V_{VIN}$            | Input Voltage                                             | 8.6 | 80  | V    |

| V <sub>SVDD</sub>    | I <sup>2</sup> C VDD                                      | 2.7 | 5.5 | V    |

| $V_{VO}$             | Output voltage sense for control and protection           | 0   | 2.5 | V    |

| V <sub>UVLO/EN</sub> | Enable/Under Voltage lock-out                             | 0   | 5.5 | V    |

| $V_{SADJ}$           | Switching regulator analog or PWM LED current adjust      | 0   | 5.5 | V    |

| $V_{LADJ}$           | Linear regulator analog or PWM LED current adjust         | 0   | 5.5 | V    |

| $V_{RON}$            | Resistor and capacitor sets switching frequency of device | 0   | 5.5 | V    |

| TJ                   | Operating junction temperature                            | -40 | 125 | °C   |

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified  $V_{IN} = 48 \text{ V}, -40^{\circ}\text{C} < T_{A} = T_{J} < 125^{\circ}\text{C}$  .

|                        | PARAMETER                                            | CONDITIONS                 | MIN                     | TYP        | MAX                   | UNITS |

|------------------------|------------------------------------------------------|----------------------------|-------------------------|------------|-----------------------|-------|

| V <sub>CC</sub> REGUL  | ATOR (VCC)                                           |                            |                         |            |                       |       |

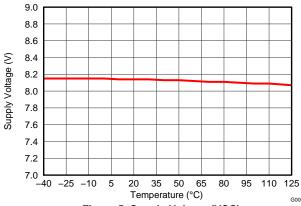

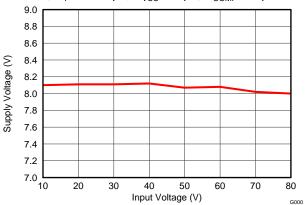

| V <sub>CC</sub>        | V <sub>CC</sub> Voltage                              |                            | 7.75                    | 8.2        | 8.55                  | V     |

| l <sub>vcc</sub>       | V <sub>CC</sub> current limit                        | $V_{CC} = 0$               | 14                      | 20         | 27                    | mA    |

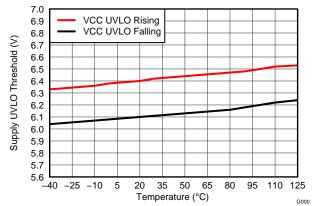

| .,                     | Rising threshold                                     |                            |                         | 6.4        |                       | V     |

| √ccuvLo                | Falling threshold                                    |                            |                         | 6.1        |                       | V     |

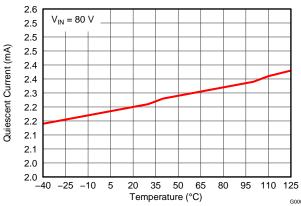

| Q                      | Quiescent current                                    | V <sub>IN</sub> = 80 V     |                         | 2.2        |                       | mΑ    |

| JVLO/DEVI              | CE ENABLE (EN/UV)                                    | •                          |                         |            | ·                     |       |

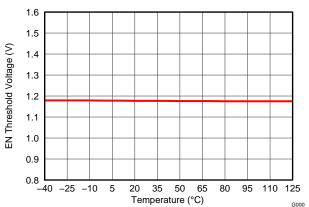

| V <sub>EN</sub>        | Device enable voltage threshold                      | V <sub>EN</sub> increasing | 1.14                    | 1.2        | 1.26                  | V     |

| / <sub>EN_HYS</sub>    | Enable input hysteresis                              |                            |                         | 20         |                       | mV    |

| EN                     | Enable source current                                | V <sub>EN</sub> = 0        |                         | 10         |                       | μΑ    |

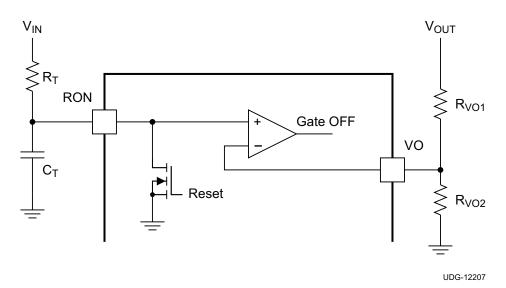

| ON/OFF TIM             | IER/OVER VOLTAGE PROTECTION                          | (RON, VO)                  |                         |            | ·-                    |       |

| R <sub>PD_RON</sub>    | RON pull-down resistance                             |                            |                         | 60         | 83                    | Ω     |

| Vov                    | VO pin overvoltage threshold                         |                            | 2.4                     | 2.5        | 2.6                   | V     |

| / <sub>OV_HYS</sub>    | VO pin overvoltage hysteresis                        |                            |                         | 0.1        |                       | V     |

| ON_DLY                 | RON pin to GATE delay                                |                            |                         | 58         |                       | ns    |

| OFF(min)               | Minimum off-time                                     | V <sub>CS</sub> = 0 V      | 200                     | 255        | 340                   | ns    |

| ON(min)                | Minimum on-time                                      |                            | 80                      | 120        | 180                   | ns    |

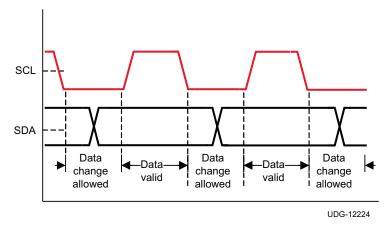

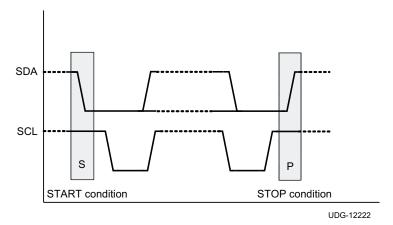

| <sup>2</sup> C LOGIC I | NTERFACE (SCL, SDA) (2.7V ≤ V <sub>SVD</sub>         | <sub>DD</sub> ≤ 5.5V)      | •                       |            | '                     |       |

| / <sub>IL</sub>        | Low-level input voltage                              |                            |                         | 0.2        | 2 × V <sub>SVDD</sub> | V     |

| / <sub>IH</sub>        | High-level input voltage                             |                            | 0.8 × V <sub>SVDD</sub> |            |                       | V     |

| L                      | Logic input current                                  |                            | -1                      | 0          | 1                     | μΑ    |

| SCL                    | SCL input frequency                                  |                            |                         | 100        | 200                   | kHz   |

| / <sub>OL</sub>        | Low-level output voltage                             | I <sub>SDA</sub> = 3 mA    |                         | 0.2        | 0.38                  | V     |

| L                      | Output leakage current                               | V <sub>SDA</sub> = 5 V     |                         |            | 1                     | μA    |

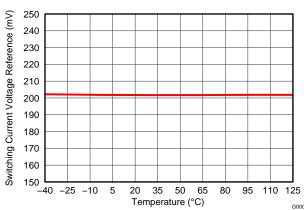

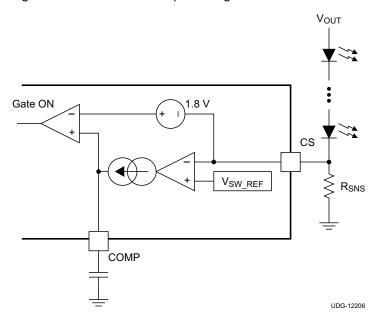

| SWITCHER               | LED CURRENT SENSE (CS, COMP)                         |                            | <u> </u>                |            | "                     |       |

| V <sub>SW_REF</sub>    | Switcher LED current reference voltage               | Non-programmed             | 196                     | 202        | 209                   | mV    |

| ∆ V <sub>SW_REF</sub>  | Switcher LED current reference voltage adjust range  |                            |                         | ±40<br>-40 |                       | mV    |

| cs                     | CS bias current                                      |                            |                         |            | 1                     | μΑ    |

| <b>Э</b> м             | CS amplifier transconductance                        |                            |                         | 600        |                       | μA/V  |

| CS_COMP                | CS to COMP offset voltage                            |                            |                         | 1.8        |                       | V     |

|                        | COMP source current                                  |                            |                         | 75         |                       | μΑ    |

| COMP                   | COMP sink current                                    |                            |                         | 75         |                       | μΑ    |

| IIGH SIDE              | SWITCH CURRENT LIMIT (VIN, SW)                       |                            |                         |            | ,                     |       |

| V <sub>SW_LIM</sub>    | High side switch current limit (referenced from VIN) |                            | 232                     | 275        | 329                   | mV    |

| LIM_OFF                | Current limit OFF time                               |                            |                         | 280        |                       | μS    |

| LEB                    | Switch current sense leading edge blank time         |                            |                         | 200        |                       | nS    |

## **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise specified  $V_{IN} = 48 \text{ V}, -40^{\circ}\text{C} < T_{\Delta} = T_{I} < 125^{\circ}\text{C}$

|                       | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CONDITIONS     | MIN  | TYP        | MAX  | UNITS |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------------|------|-------|

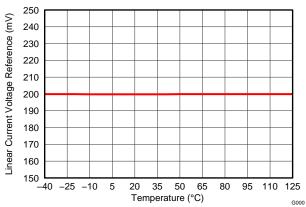

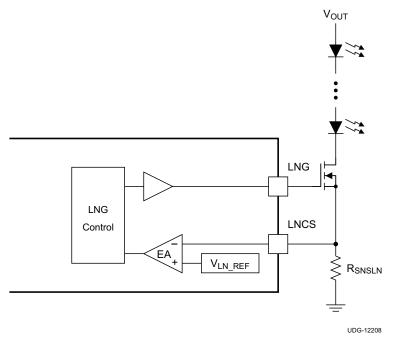

| LINEAR LEI            | D CURRENT SENSE (LNCS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |      |            |      |       |

| V <sub>LN_REF</sub>   | Linear LED current reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Non-programmed | 190  | 200        | 209  | mV    |

| $\Delta V_{LN\_REF}$  | LinearLED current reference voltage adjust range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |      | +44<br>-50 |      | mV    |

| I <sub>LNCS</sub>     | LNCS Input bias current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |      |            | 1    | μΑ    |

|                       | GATE DRIVER (GATE, BOOT, SW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | 1    |            |      | -     |

| R <sub>SRC GATE</sub> | Gate sourcing resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GATE = High    |      | 2          |      | Ω     |

| R <sub>SNK_GATE</sub> | Gate sinking resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GATE = Low     |      | 2          |      | Ω     |

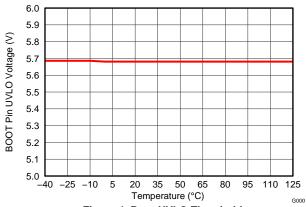

| V <sub>BOOT</sub>     | BOOT UVLO threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BOOT-SW rising | 4.2  | 5.6        | 7.0  | V     |

| V <sub>BOOT_HYS</sub> | BOOT UVLO threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |      | 750        |      | mV    |

| I <sub>SW PD</sub>    | SW node pull down current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |      | 60         |      | mA    |

| LINEAR GA             | TE DRIVER (LNG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |      |            | ,    |       |

| V <sub>LNG_MAX</sub>  | LNG Maximum output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |      | 6.3        |      | V     |

| V <sub>LNG_MIN</sub>  | LNG Minimum output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |      | 1.4        |      | V     |

| I <sub>LNG_MAX</sub>  | LNG Maximum output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |      |            | 5.5  | mA    |

|                       | WM DIMMING (SADJ, LADJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | 1    |            | ,    |       |

| f <sub>DIM</sub>      | Internal PWM dimming frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |      | 500        |      | Hz    |

|                       | CAD I triangle valte as few analysis in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | High           |      | 2.5        |      | V     |

| V <sub>tri</sub>      | SADJ triangle voltage for analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Low            |      | 0.1        |      | V     |

|                       | LAD I in the second sec | High           |      | 2.5        |      |       |

|                       | LADJ triangle voltage for analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Low            |      | 0.1        |      | V     |

|                       | SADJ Pulse detect timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |      | 10         |      |       |

| t <sub>TIMER</sub>    | LADJ Pulse detect timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |      | 10         |      | ms    |

| 1/                    | SADJ PWM input threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |      | 2.7        |      |       |

| $V_{ADJ}$             | LADJ PWM input threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |      | 2.7        |      | V     |

| M                     | SADJ PWM input hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |      | 500        |      | m)/   |

| V <sub>ADJ_HYS</sub>  | LADJ PWM input hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |      | 500        |      | mV    |

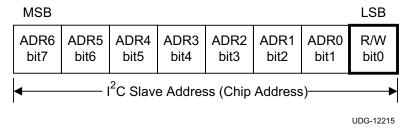

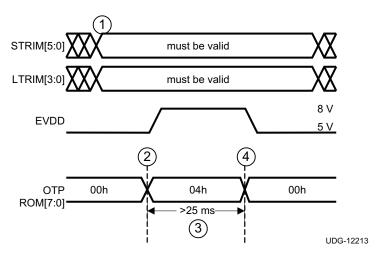

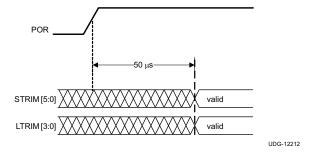

|                       | SADJ Pull up current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |      | 5          |      |       |