Order

Now

TPS92692, TPS92692-Q1

SLVSDD9-MARCH 2017

# TPS92692, TPS92692-Q1 High Accuracy LED Controller With **Spread Spectrum Frequency Modulation**

#### Features 1

- Wide Input Voltage: 4.5 V to 65 V

- Better than ± 4% LED Current Accuracy over -40°C to 150°C Junction Temperature Range

- Spread Spectrum Frequency Modulation for Improved EMI

- Comprehensive Fault Protection Circuitry with Current Monitor output and Open Drain Fault Flag Indicator

- Internal Analog Voltage to PWM Duty Cycle Generator for stand-alone Dimming Operation

- Compatible with Direct PWM Input with over • 1000:1 Dimming Range

- Analog LED Current Adjust Input (IADJ) with over ٠ 15:1 Contrast Ratio

- Integrated P-Channel Driver to enable Series FET Dimming and LED Protection

- TPS92692-Q1: Automotive Q100 Grade 1 ٠ Qualified

# 2 Applications

- TPS92692-Q1: Automotive Exterior Lighting Applications

- Driver Monitoring Systems (DMS)

- LED General Lighting Applications

- Exit Signs and Emergency Lighting

# 3 Description

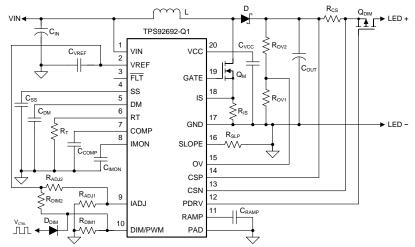

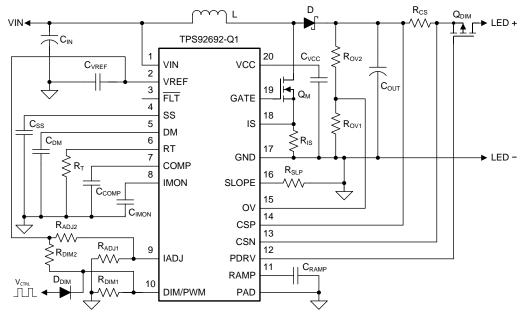

The TPS92692 and TPS92692-Q1 are high accuracy peak current mode based controllers designed to support step-up/down LED driver topologies. The device incorporates a rail-to-rail current amplifier to measure LED current and spread spectrum frequency modulation technique for improved EMI performance.

performance LED controller This hiah can independently modulate LED current using either analog or PWM dimming techniques. Linear analog dimming response with over 15:1 range is obtained by varying the voltage across the high impedance analog adjust (IADJ) input. PWM dimming of LED current is achieved by directly modulating the DIM/PWM input pin with the desired duty cycle or by enabling the internal PWM generator circuit. The PWM generator translates the DC voltage at DIM/PWM pin to corresponding duty cycle by comparing it to the internal triangle wave generator. The optional PDRV gate driver output can be used to drive an external P-Channel series MOSFET.

The TPS92692 and TPS92692-Q1 devices support continuous LED status check through the current monitor (IMON) output. The devices also include an open drain fault indicator output to indicate LED overcurrent, output overvoltage and output undervoltage conditions.

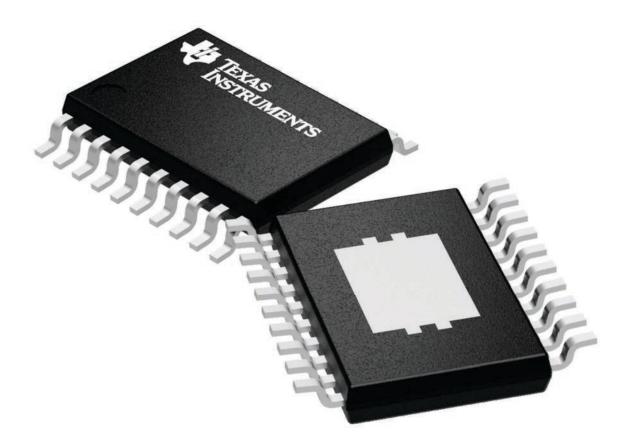

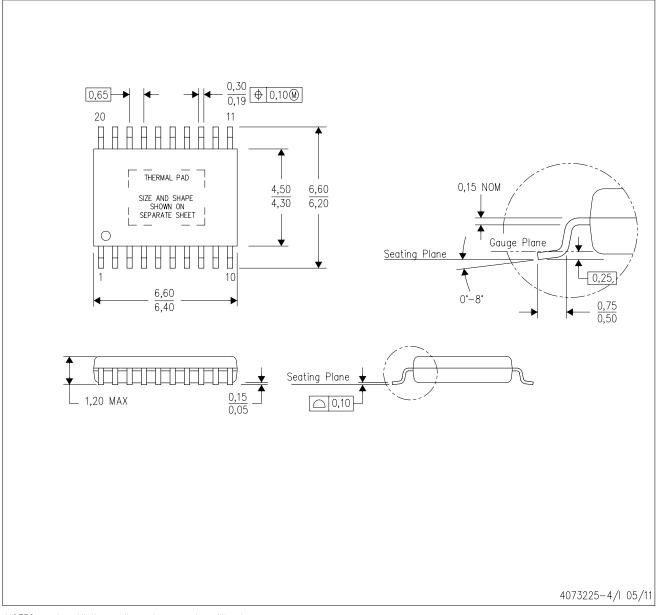

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |  |  |  |

|-------------|-------------|-------------------|--|--|--|

| TPS92692-Q1 | HTSSOP (20) | 5 10 mm v 6 60 mm |  |  |  |

| TPS92692    | H1330F (20) | 5.10 mm × 6.60 mm |  |  |  |

| TPS92692    |             |                   |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# **Typical Boost LED Driver**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Тур  | ical Boost LED Driver1             |

| 5 | Rev  | ision History 2                    |

| 6 | Pin  | Configuration and Functions 3      |

| 7 | Spe  | cifications4                       |

|   | 7.1  | Absolute Maximum Ratings 4         |

|   | 7.2  | ESD Ratings 5                      |

|   | 7.3  | Recommended Operating Conditions 5 |

|   | 7.4  | Thermal Information 5              |

|   | 7.5  | Electrical Characteristics         |

|   | 7.6  | Typical Characteristics 9          |

| 8 | Deta | ailed Description 13               |

|   | 8.1  | Overview 13                        |

|   | 8.2  | Functional Block Diagram 14        |

|   |      |                                    |

|    | 8.3  | Feature Description               | 15 |

|----|------|-----------------------------------|----|

|    | 8.4  | Device Functional Modes           | 22 |

| 9  | Арр  | lication and Implementation       | 25 |

|    | 9.1  | Application Information           | 25 |

|    | 9.2  | Typical Applications              | 34 |

| 10 | Pov  | ver Supply Recommendations        | 46 |

| 11 | Lay  | out                               | 47 |

|    | 11.1 | Layout Guidelines                 | 47 |

|    | 11.2 | Layout Example                    | 48 |

| 12 | Dev  | ice and Documentation Support     | 49 |

|    | 12.1 | Related Links                     | 49 |

|    | 12.2 | Community Resources               | 49 |

|    | 12.3 | Trademarks                        | 49 |

|    | 12.4 | Electrostatic Discharge Caution   | 49 |

|    | 12.5 | Glossary                          | 49 |

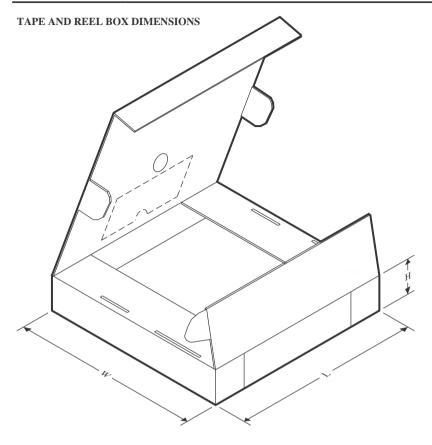

| 13 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           | 49 |

|    |      |                                   |    |

# 5 Revision History

| DATE       | REVISION | NOTES            |

|------------|----------|------------------|

| March 2017 | *        | Initial release. |

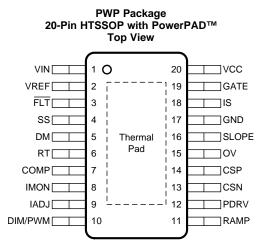

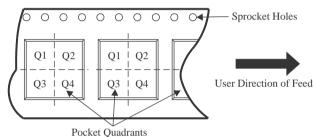

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN     | PIN I/O DESCRIPTION |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------|---------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO.                 | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| COMP    | 7                   | I/O | Transconductance error amplifier output. Connect compensation network to achieve desired closed-loop response.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| CSN     | 13                  | I   | Current sense amplifier negative input (–). Connect directly to the negative node of LED current sense resistor, ${\sf R}_{CS}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| CSP     | 14                  | Ι   | Current sense amplifier positive input (+). Connect directly to the positive node of LED current sense resistor, $R_{CS}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DIM/PWM | 10                  | I   | External analog to PWM dimming command or direct PWM dimming input. The external analog dimming command between 1 V and 3 V is compared to the internal PWM generator triangle waveform to set LED current duty cycle between 0% and 100%. With PWM generator disabled, a direct PWM dimming command can be applied to control the LED current duty cycle and frequency. The analog or PWM command is used to generate an internal PWM signal that controls the GATE and PDRV outputs. Setting the internal PWM signal to logic level low, turns off switching, idles the oscillator, disconnects the COMP pin, and sets PDRV to $V_{CSP}$ . Connect to VREF when not used for PWM dimming. |  |

| DM      | 5                   | I/O | Triangle wave spread spectrum modulation frequency, $f_m$ , programming pin. Connect a capac GND to set the spread spectrum modulating frequency. Connect directly to GND to disable sp spectrum modulation of switching frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

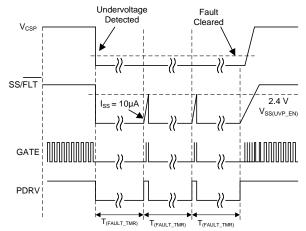

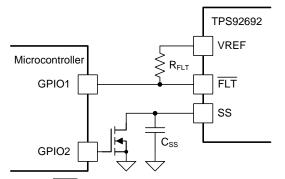

| FLT     | 3                   | ο   | Open-drain fault indicator. Connect to VREF with a resistor to create active low fault signal output.<br>Internal LED short circuit protection and auto-restart timer can enabled by directly connecting the<br>pin to SS input.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| GATE    | 19                  | 0   | N-channel MOSFET gate driver output. Connect to gate of external main switching N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| GND     | 17                  | _   | Analog and Power ground connection pin. Connect to circuit ground to complete return path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| IADJ    | 9                   | I   | LED current reference input. Connect this pin to VCC with a 100-k $\Omega$ series resistor to set the internal reference voltage to 2.42 V and the current sense threshold, V <sub>(CSP-CSN)</sub> to 170.7 mV. The pin can be modulated by an external voltage source from 140 mV to 2.25 V to implement analog dimming.                                                                                                                                                                                                                                                                                                                                                                   |  |

| IMON    | 8                   | 0   | LED current report pin. The LED current sensed by CSP/CSN input is reported as $V_{IMON} = 14 \times I_{LED} \times R_{CS}$ . Bypass with a 1-nF ceramic capacitor connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| IS      | 18                  | I   | Switch current sense input. Connect to the switch sense resistor, $R_{IS}$ to set the switch current limit threshold based on the internal 250 mV reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| OV      | 15                  | I   | Output voltage input. Connect a resistor divider from output voltage to GND to set output overvoltage and under-voltage protection thresholds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PDRV    | 12                  | 0   | Series dimming P-channel FET gate driver output. Connect to gate of external P-channel MOSFET to implement series FET PWM dimming and fault disconnect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

TEXAS INSTRUMENTS

www.ti.com

# Pin Functions (continued)

| PIN         | I   | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                      |  |

|-------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO. | 1/0   | DESCRIPTION                                                                                                                                                                                                                                                                                                      |  |

| RAMP        | 11  | I/O   | Programming input for internal PWM generator. Connect a capacitor to GND to set the triangle wave frequency for PWM generator circuit. Connect a 249-k $\Omega$ resistor to GND to disable the PWM generator and to set a fixed reference for direct external PWM dimming input. Do not allow this pin to float. |  |

| RT          | 6   | I/O   | Oscillator frequency programming pin. Connect a resistor to GND to set the switching frequency. The internal oscillator can be synchronized by coupling an external clock pulse through a series capacitor with a value of 100 nF.                                                                               |  |

| SLOPE       | 16  | I/O   | Slope compensation input. Connect a resistor to GND to set the desired slope compensation rabased on inductor value, input and output voltages.                                                                                                                                                                  |  |

| SS          | 4   | I/O   | Soft-start programming pin. Connect a capacitor to GND to extend the start-up time. Switching can be disabled by shorting this pin to GND.                                                                                                                                                                       |  |

| VCC         | 20  | —     | VCC (7.5 V) bias supply pin. Locally decouple to GND using a ceramic capacitor (with a value between 2.2- $\mu$ F and 4.7- $\mu$ F). Locate close to the controller.                                                                                                                                             |  |

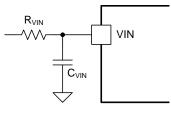

| VIN         | 1   | _     | Input supply for the internal regulators. Bypass with a low-pass filter using a series $10-\Omega$ resistor and $10- nF$ capacitor connected to GND. Locate the capacitor close to the controller.                                                                                                               |  |

| VREF        | 2   | _     | VREF (5 V) bias supply pin. Locally decouple to GND using a ceramic capacitor (with a value between 2.2- $\mu$ F and 4.7- $\mu$ F) located close to the controller.                                                                                                                                              |  |

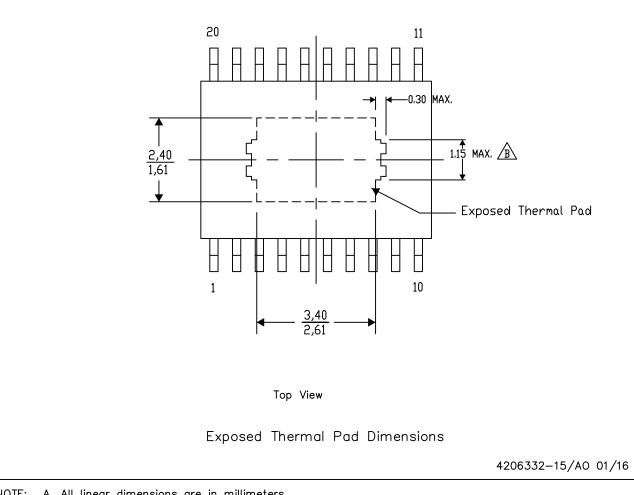

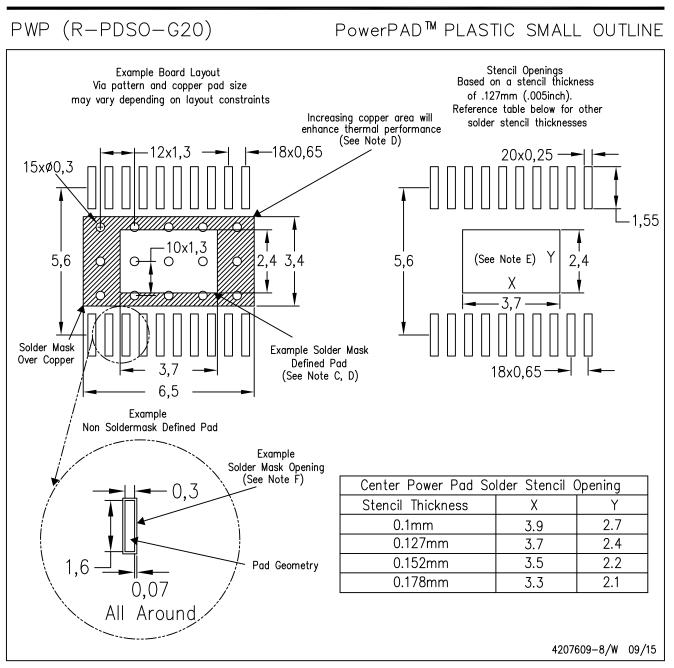

| Thermal Pad |     | _     | The GND pin must be connected to the exposed thermal pad for proper operation. This PowerPAD must be connected to PCB ground plane using multiple vias for good thermal performance.                                                                                                                             |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) $^{(1)(2)}$

|                                       |                                     | MIN                                                                                                                                                                                                                                                                                                             | MAX                                                                                                             | UNIT |

|---------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|

|                                       | VIN, CSP, CSN                       | -0.3                                                                                                                                                                                                                                                                                                            | 65                                                                                                              | V    |

|                                       | DIM/PWM                             | -0.3                                                                                                                                                                                                                                                                                                            | 14                                                                                                              | V    |

| Input voltage                         | IS, RT, FLT                         | -0.3                                                                                                                                                                                                                                                                                                            | 8.8                                                                                                             | V    |

|                                       | OV, SS, RAMP, DM, SLOPE, VREF, IADJ | -0.3                                                                                                                                                                                                                                                                                                            | 5.5                                                                                                             | V    |

|                                       | CSP to CSN <sup>(3)</sup>           | -0.3                                                                                                                                                                                                                                                                                                            | 0.3                                                                                                             | V    |

|                                       | VCC, GATE                           | -0.3                                                                                                                                                                                                                                                                                                            | 8.8                                                                                                             | V    |

| utput voltage <sup>(4)</sup>          | PDRV                                | V <sub>CSP</sub> – 8.8                                                                                                                                                                                                                                                                                          | V <sub>CSP</sub>                                                                                                | V    |

|                                       | COMP                                | -0.3                                                                                                                                                                                                                                                                                                            | 5.0                                                                                                             | V    |

|                                       | IMON                                | —                                                                                                                                                                                                                                                                                                               | 100                                                                                                             | μA   |

| Source current                        | GATE (pulsed < 20 ns)               | —                                                                                                                                                                                                                                                                                                               | 500                                                                                                             | mA   |

|                                       | PDRV (pulsed < 10 µs)               | —                                                                                                                                                                                                                                                                                                               | 65           14           8.8           5.5           0.3           8.8           8           5.0           100 | mA   |

| Cials aurorat                         | GATE (pulsed < 20 ns)               | CSP, CSN         -0.3           /PWM         -0.3           RT, FLT         -0.3           SS, RAMP, DM, SLOPE, VREF, IADJ         -0.3           P to CSN <sup>(3)</sup> -0.3           C, GATE         -0.3           RV $V_{CSP}$ - 8.8           MP         -0.3           N            TE (pulsed < 20 ns) | 500                                                                                                             | mA   |

| Sink current                          | PDRV (pulsed < 10 µs)               | —                                                                                                                                                                                                                                                                                                               | 50                                                                                                              | mA   |

| Operating junction temperature, $T_J$ |                                     | -40                                                                                                                                                                                                                                                                                                             | 150                                                                                                             | °C   |

| Storage temperature, T <sub>stg</sub> |                                     |                                                                                                                                                                                                                                                                                                                 | 165                                                                                                             | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND unless otherwise noted

(3) Continuous sustaining voltage

(4) All output pins are not specifie

(4) All output pins are not specified to have an external voltage applied.

# 7.2 ESD Ratings

|                                               |                                              |                                                 |                                                                                         | VALUE | UNIT |

|-----------------------------------------------|----------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|

| TPS926                                        | 92-Q1 IN PWP (H                              | TSSOP) PACKAGE                                  |                                                                                         |       |      |

|                                               |                                              | Human-body model (HBM), per AEC Q100-002, all   | pins <sup>(1)</sup>                                                                     | ±2000 |      |

| V <sub>(ESD)</sub> Electrostatic<br>discharge | Charged device model (CDM) per AEC 0100 011  | All pins except 1, 10, 11, and 20               | ±500                                                                                    | V     |      |

|                                               | Charged-device model (CDM), per AEC Q100-011 |                                                 | Pins 1, 10, 11, and 20                                                                  | ±750  |      |

| TPS926                                        | 92 IN PWP (HTSS                              | OP) PACKAGE                                     |                                                                                         |       |      |

| V                                             | Electrostatic                                | Human-body model (HBM), per ANSI/ESDA/JEDEC     | C JS-001, all pins <sup>(2)</sup>                                                       | ±2000 | V    |

| V <sub>(ESD)</sub> discharge                  |                                              | Charged-device model (CDM), per JEDEC specifica | harged-device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(3)</sup> |       | v    |

AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification. (1)

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2) (3)

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                     |                                       | MIN  | NOM MAX      | UNIT |

|-------------------------------------|---------------------------------------|------|--------------|------|

| VIN                                 | Supply input voltage                  | 6.5  | 14 65        | V    |

| VIN, crank                          | Supply input, battery crank voltage   | 4.5  |              | V    |

| V <sub>CSP</sub> , V <sub>CSN</sub> | Current sense common mode             | 6.5  | 60           | V    |

| fsw                                 | Switching frequency                   | 80   | 800          | kHz  |

| f <sub>m</sub>                      | Spread spectrum modulation frequency  | 0.1  | 12           | kHz  |

| f <sub>RAMP</sub>                   | Internal PWM ramp generator frequency | 100  | 2000         | Hz   |

| V <sub>IADJ</sub>                   | Current reference voltage             | 0.14 | VIADJ(CLAMP) | V    |

| T <sub>A</sub>                      | Operating ambient temperature         | -40  | 125          | °C   |

# 7.4 Thermal Information

|                       |                                              | TPS92692     | TPS92692-Q1  |      |

|-----------------------|----------------------------------------------|--------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | PWP (HTSSOP) | UNIT |

|                       |                                              | 20 PINS      | 20 PINS      |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 40.8         | 40.8         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 26.1         | 26.1         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 22.2         | 22.2         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.8          | 0.8          | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 22.0         | 22.0         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.3          | 2.3          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

| I <sub>IN(SW)</sub>     | Input switching current                     | V <sub>CC</sub> = 7.5 V, C <sub>GATE</sub> = 1 nF |      | 5.1  | 6.6  | mA  |

|-------------------------|---------------------------------------------|---------------------------------------------------|------|------|------|-----|

| BIAS SUPP               | LY (VCC)                                    |                                                   |      |      |      |     |

| V <sub>CC(REG)</sub>    | Regulation voltage                          | No load                                           | 7.0  | 7.5  | 8.0  | V   |

|                         |                                             | VCC rising threshold, $V_{IN} = 8 V$              |      | 4.5  | 4.9  | V   |

| V <sub>CC(UVLO)</sub>   | Supply undervoltage protection              | VCC falling threshold, $V_{IN} = 8 V$             | 3.7  | 4.1  |      | V   |

|                         |                                             | Hysteresis                                        |      | 400  |      | mV  |

| I <sub>CC(LIMIT)</sub>  | Supply current limit                        | $V_{CC} = 0 V$                                    | 30   | 36   | 46   | mA  |

| V <sub>DO</sub>         | LDO dropout voltage                         | $I_{CC}$ = 20 mA, $V_{IN}$ = 5 V                  |      | 300  |      | mV  |

| REFERENC                | E VOLTAGE (VREF)                            |                                                   |      |      |      |     |

| VREF                    | Reference voltage                           | No load                                           | 4.77 | 4.96 | 5.15 | V   |

| I <sub>REF(LIMIT)</sub> | Current limit                               | $V_{REF} = 0 \ V$                                 | 30   | 36   | 46   | mA  |

| OSCILLATO               | DR (RT)                                     |                                                   |      |      |      |     |

| £                       | Switching froquency                         | $R_T = 40 \text{ k}\Omega$                        | 175  | 200  | 225  | kHz |

| $f_{\rm SW}$            | Switching frequency                         | $R_T = 20 \ k\Omega$                              | 341  | 390  | 439  | kHz |

| V <sub>RT</sub>         | RT output voltage                           |                                                   |      | 1    |      | V   |

| V                       | SYNC rising threshold                       | V <sub>RT</sub> rising                            |      | 2.5  | 3.1  | V   |

| V <sub>SYNC</sub>       | SYNC falling threshold                      | V <sub>RT</sub> falling                           | 1.8  | 2    |      | V   |

| t <sub>SYNC(MIN)</sub>  | Minimum SYNC clock pulse width              |                                                   |      | 100  |      | ns  |

| SPREAD SP               | PECTRUM FREQUENCY MODULATION                | I (DM)                                            |      |      |      |     |

|                         | Triangle wave generator sink current        |                                                   |      | 10   |      | μA  |

| I <sub>DM</sub>         | Triangle wave generator source current      |                                                   |      | 10   |      | μA  |

| N/                      | Triangle wave voltage peak (High)           |                                                   |      | 1.15 |      | V   |

| V <sub>DM(TR)</sub>     | Triangle wave voltage valley (Low)          |                                                   |      | 850  |      | mV  |

| V <sub>DM(EN)</sub>     | Spread spectrum modulation enable threshold |                                                   |      | 700  |      | mV  |

| V <sub>DM(CLAMP)</sub>  | Internal clamp voltage                      | $V_{PWM} = 0 V, R_{RAMP} = 200 k\Omega$           |      | 1.25 |      | V   |

| (                       |                                             |                                                   |      |      |      |     |

$I_{GATE} = -10 \text{ mA}$

$I_{GATE} = 10 \text{ mA}$

$V_{DIM/PWM} = 5 V, R_{RAMP} = 249 k\Omega$

$V_{DIM/PWM} = 0 V, R_{RAMP} = 249 k\Omega$

V<sub>IS</sub> pulsed from 0 V to 1 V

PARAMETER

Input stand-by current

TPS92692, TPS92692-Q1

SLVSDD9-MARCH 2017

**INPUT VOLTAGE (VIN)**

I<sub>IN(STBY)</sub>

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}, \text{ V}_{\text{IN}} = 14 \text{ V}, \text{ V}_{\text{IADJ}} = 2.1 \text{ V}, \text{ V}_{\text{RAMP}} = 500 \text{ mV}, \text{ V}_{\text{DIM/PWM}} = 3 \text{ V}, \text{ V}_{\text{OV}} = 500 \text{ mV}, \text{ C}_{\text{VCC}} = 1 \text{ } \mu\text{F}, \text{ C}_{\text{VREF}} = 1 \text{ } \mu\text{F}, \text{ C}_{\text{COMP}} = 2.2 \text{ } \text{nF}, \text{ R}_{\text{CS}} = 100 \text{ } \text{m}\Omega, \text{ R}_{\text{T}} = 20 \text{ } \text{k}\Omega, \text{ no load on GATE and PDRV (unless otherwise noted)}^{(1)}$

$V_{PWM} = 0 V$

**TEST CONDITIONS**

MIN

TYP

1.8

(1) All voltages are with respect to GND unless otherwise noted

Gate driver high side resistance

Gate driver low side resistance

Current limit threshold

Current limit fault time

Leading edge blanking time

IS to GATE propagation delay

5.4

4.3

250

700

118

35

78

230.6

665

88

11.2

10.5

270

735

158

Ω

Ω

mV

mV

ns

μs

ns

MAX

2.5

www.ti.com

UNIT

mΑ

GATE DRIVER (GATE)

**CURRENT SENSE (IS)**

R<sub>GH</sub>

$R_{GL}$

VIS(LIMIT)

t<sub>IS(BLANK)</sub>

t<sub>IS(FAULT)</sub>

t<sub>ILMT(DLY)</sub>

6

# **Electrical Characteristics (continued)**

$-40^{\circ}C \leq T_{J} \leq 150^{\circ}C, V_{IN} = 14 \text{ V}, V_{IADJ} = 2.1 \text{ V}, V_{RAMP} = 500 \text{ mV}, V_{DIM/PWM} = 3 \text{ V}, V_{OV} = 500 \text{ mV}, C_{VCC} = 1 \text{ }\mu\text{F}, C_{VREF} = 1 \text{ }\mu\text{F}, C_{COMP} = 2.2 \text{ }n\text{F}, R_{CS} = 100 \text{ }m\Omega, R_{T} = 20 \text{ }k\Omega, \text{ no load on GATE and PDRV (unless otherwise noted)}^{(1)}$

|                          | PARAMETER                                                              | TEST CONDITIONS                                               | MIN   | TYP   | MAX    | UNIT |

|--------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|-------|-------|--------|------|

| PWM COMP                 | ARATOR AND SLOPE COMPENSATIO                                           | DN (SLOPE)                                                    |       |       |        |      |

| D <sub>MAX</sub>         | Maximum duty cycle                                                     |                                                               |       | 90    |        | %    |

| V <sub>SLOPE</sub>       | Adaptive slope compensation                                            | $V_{CSP} = 24 V$                                              |       | 410   |        | mV   |

| V <sub>SLOPE(MIN)</sub>  | Minimum slope compensation output voltage                              | V <sub>CSP</sub> = 0 V                                        |       | 72    |        | mV   |

| V <sub>LV</sub>          | IS to COMP level shift voltage                                         | No slope compensation added                                   | 1.42  | 1.60  | 1.82   | V    |

| I <sub>LV</sub>          | IS level shift bias current                                            | No slope compensation added                                   |       | 17    |        | μA   |

| CURRENT S                | ENSE AMPLIFIER (CSP, CSN)                                              | •                                                             |       |       |        |      |

|                          |                                                                        | $V_{CSP} = 14 \text{ V}, V_{IADJ} = 3 \text{ V}$              | 163.4 | 170.7 | 177.6  | mV   |

| V <sub>(CSP-CSN)</sub>   | Current sense thresholds                                               | V <sub>CSP</sub> = 14 V, V <sub>IADJ</sub> = 1.4 V            | 95.83 | 100.5 | 103.85 | mV   |

| CS <sub>(BW)</sub>       | Current sense unity gain bandwidth                                     |                                                               |       | 500   |        | kHz  |

| G <sub>CS</sub>          | Current sense amplifier gain                                           | $G = V_{IADJ}/V_{(CSP-CSN)}$                                  |       | 14    |        |      |

| K <sub>(OCP)</sub>       | Ratio of over-current detection threshold to analog adjust voltage     | $K_{(OCP)} = V_{(OCP-THR)}/V_{IADJ}$                          | 1.46  | 1.5   | 1.61   |      |

| I <sub>CSP(BIAS)</sub>   | CSP bias current                                                       | V <sub>CSN</sub> = 14.1 V, V <sub>CSP</sub> = 14 V            |       | 107   |        | μA   |

| I <sub>CSN(BIAS)</sub>   | CSN bias current                                                       | V <sub>CSN</sub> = 14.1 V, V <sub>CSP</sub> = 14 V            |       | 110   |        | μA   |

|                          | CATOR (FLT)                                                            | · · · · · · · · · · · · · · · · · · ·                         |       |       |        |      |

| R <sub>(FLT)</sub>       | Open-drain pull down resistance                                        |                                                               |       | 241   |        | Ω    |

| t(FAULT_TMR)             | Fault timer                                                            |                                                               | 24    | 36    | 48     | ms   |

| CURRENT N                | IONITOR (IMON)                                                         |                                                               |       |       |        |      |

| I <sub>IMON(SRC)</sub>   | IMON source current                                                    | $V_{(CSP-CSN)} = 150 \text{ mV},$<br>$V_{IMON} = 0 \text{ V}$ |       |       | 144    | μΑ   |

| VIMON(CLP)               | IMON output voltage clamp                                              |                                                               | 3.2   | 3.7   | 4.2    | V    |

| VIMON(OS)                | IMON buffer offset voltage                                             |                                                               | -7.2  | 0     | 8.5    | mV   |

|                          | DJUST (IADJ)                                                           | •                                                             |       |       |        |      |

| VIADJ(CLP)               | IADJ internal clamp voltage                                            | $I_{IADJ} = 1 \ \mu A$                                        | 2.29  | 2.40  | 2.55   | V    |

| IIADJ(BIAS)              | IADJ input bias current                                                | V <sub>IADJ</sub> < 2.2 V                                     |       | 10.5  |        | nA   |

| R <sub>IADJ(LMT)</sub>   | IADJ current limiting series resistor                                  | V <sub>IADJ</sub> > 2.6 V                                     |       | 12    |        | kΩ   |

| ERROR AM                 | PLIFIER (COMP)                                                         | •                                                             |       |       |        |      |

| 9м                       | Transconductance                                                       |                                                               |       | 121   |        | μA/V |

| ICOMP(SRC)               | COMP current source capacity                                           | $V_{IADJ} = 1.4 \text{ V}, V_{(CSP-CSN)} = 0 \text{ V}$       |       | 130   |        | μA   |

| ICOMP(SINK)              | COMP current sink capacity                                             | $V_{IADJ} = 0 V, V_{(CSP-CSN)} = 0.1 V$                       |       | 130   |        | μA   |

| EA <sub>(BW)</sub>       | Error amplifier bandwidth                                              | Gain = -3 dB                                                  |       | 5     |        | MHz  |

| V <sub>COMP(RST)</sub>   | COMP pin reset voltage                                                 |                                                               |       | 100   |        | mV   |

| R <sub>COMP(DCH)</sub>   | COMP discharge FET resistance                                          |                                                               |       | 246   |        | Ω    |

| SOFT-STAR                | T (SS)                                                                 |                                                               |       |       |        |      |

| I <sub>SS</sub>          | Soft-start source current                                              |                                                               | 7     | 10    | 12.8   | μA   |

| V <sub>SS(UVP_EN)</sub>  | Soft-start voltage threshold to enable output under-voltage protection |                                                               |       | 2.4   |        | V    |

| V <sub>SS(RST)</sub>     | Soft-start pin reset voltage                                           |                                                               |       | 50    |        | mV   |

| R <sub>SS(DCH)</sub>     | SS discharge FET resistance                                            |                                                               |       | 240   |        | Ω    |

| 1 1                      | DLTAGE INPUT (OV)                                                      |                                                               |       |       |        |      |

| V <sub>OVP(THR)</sub>    | Overvoltage protection threshold                                       |                                                               | 1.195 | 1.228 | 1.262  | V    |

| V <sub>UVP(THR)</sub>    | Undervoltage protection threshold                                      |                                                               | 81.7  | 100   | 115.1  | mV   |

| t <sub>(UVP-BLANK)</sub> | Undervoltage protection blanking period                                |                                                               |       | 4     |        | μs   |

| I <sub>OVP(HYS)</sub>    | OVP hysteresis current                                                 |                                                               | 12    | 20    | 27.5   | μA   |

Copyright © 2017, Texas Instruments Incorporated

Submit Documentation Feedback 7

# **Electrical Characteristics (continued)**

$-40^{\circ}C \leq T_{J} \leq 150^{\circ}C, V_{IN} = 14 \text{ V}, V_{IADJ} = 2.1 \text{ V}, V_{RAMP} = 500 \text{ mV}, V_{DIM/PWM} = 3 \text{ V}, V_{OV} = 500 \text{ mV}, C_{VCC} = 1 \text{ }\mu\text{F}, C_{VREF} = 1 \text{ }\mu\text{F}, C_{COMP} = 2.2 \text{ }n\text{F}, R_{CS} = 100 \text{ }m\Omega, R_{T} = 20 \text{ }k\Omega, \text{ no load on GATE and PDRV (unless otherwise noted)}^{(1)}$

|                        | PARAMETER                                    | TEST CONDITIONS                       | MIN  | TYP | MAX   | UNIT |

|------------------------|----------------------------------------------|---------------------------------------|------|-----|-------|------|

| INTERNAL I             | PWM RAMP GENERATOR (RAMP)                    |                                       |      |     |       |      |

| I <sub>RAMP</sub>      | Ramp generator source current                |                                       | 7.75 | 10  | 12.73 | μA   |

|                        | Ramp generator sink current                  |                                       | 8.24 | 10  | 12.41 | μA   |

|                        | Ramp signal peak (high)                      |                                       |      | 3   |       | V    |

| V <sub>RAMP</sub>      | Ramp signal valley (low)                     |                                       |      | 1   |       | V    |

| PWM INPUT              | (DIM/PWM)                                    | •                                     | •    |     |       |      |

| V <sub>PWM(HIGH)</sub> | Schmitt trigger logic level (high threshold) | V <sub>RAMP</sub> = 2.0 V             |      | 2.0 | 2.2   | V    |

| V <sub>PWM(LOW)</sub>  | Schmitt trigger logic level (low threshold)  | V <sub>RAMP</sub> = 2.0 V             | 1.8  | 2.0 |       | V    |

| R <sub>PWM(PD)</sub>   | PWM pull-down resistance                     |                                       |      | 10  |       | MΩ   |

| t <sub>DLY(RISE)</sub> | PWM rising to PDRV delay                     | C <sub>PDRV</sub> = 1 nF              |      | 294 |       | ns   |

| t <sub>DLY(FALL)</sub> | PWM falling to PDRV delay                    | C <sub>PDRV</sub> = 1 nF              |      | 326 |       | ns   |

| SERIES P-C             | HANNEL PWM FET GATE DRIVE OUT                | PUT (PDRV)                            |      |     | ·     |      |

| V <sub>PDRV(OFF)</sub> | P-channel gate driver off-state voltage      | $V_{CSP} = 14 V$                      |      | 14  |       | V    |

| V <sub>PDRV(ON)</sub>  | P-channel gate driver on-state voltage       | $V_{CSP} = 14 V$                      |      | 7.4 |       | V    |

| IPDRV(SRC)             | PDRV sink current                            | Pulsed                                |      | 50  |       | mA   |

| R <sub>PDRV(L)</sub>   | PDRV driver pull up resistance               |                                       |      | 82  |       | Ω    |

| THERMAL S              | GHUTDOWN                                     | · · · · · · · · · · · · · · · · · · · |      |     |       |      |

| T <sub>SD</sub>        | Thermal shutdown temperature                 |                                       |      | 175 |       | °C   |

| T <sub>SD(HYS)</sub>   | Thermal shutdown hysteresis                  |                                       |      | 25  |       | °C   |

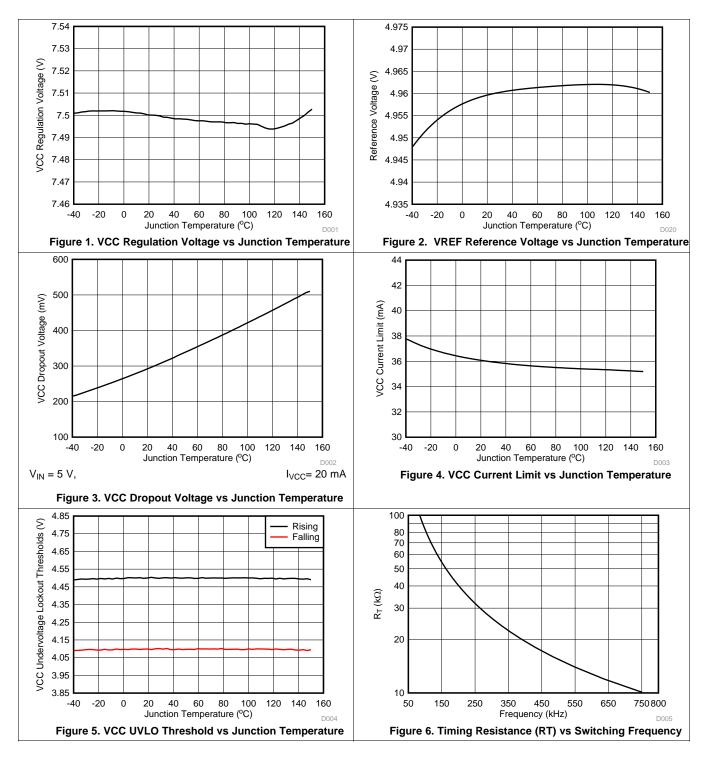

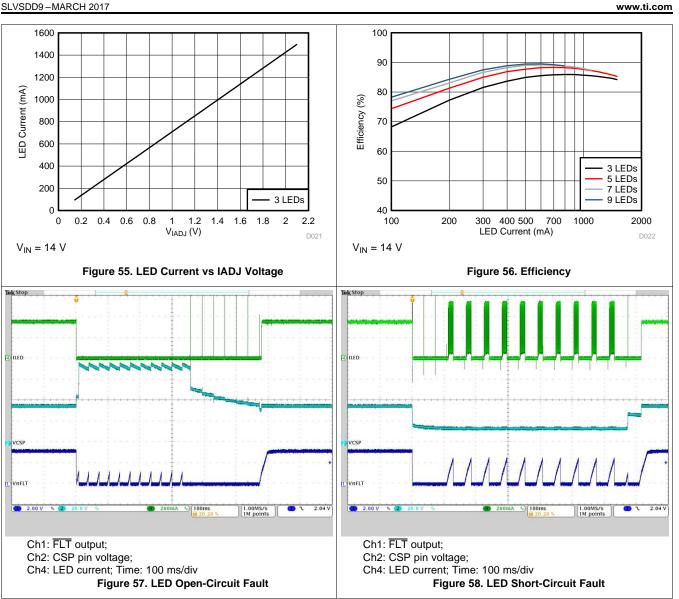

# 7.6 Typical Characteristics

$T_A = 25^{\circ}C, V_{IN} = 14 \text{ V}, V_{IADJ} = 2.2 \text{ V}, C_{VCC} = 1 \text{ }\mu\text{F}, C_{COMP} = 2.2 \text{ }n\text{F}, R_{CS} = 100 \text{ }m\Omega, R_T = 20 \text{ }k\Omega, V_{PWM} = 5 \text{ }V, \text{ no load on GATE and PDRV (unless otherwise noted)}$

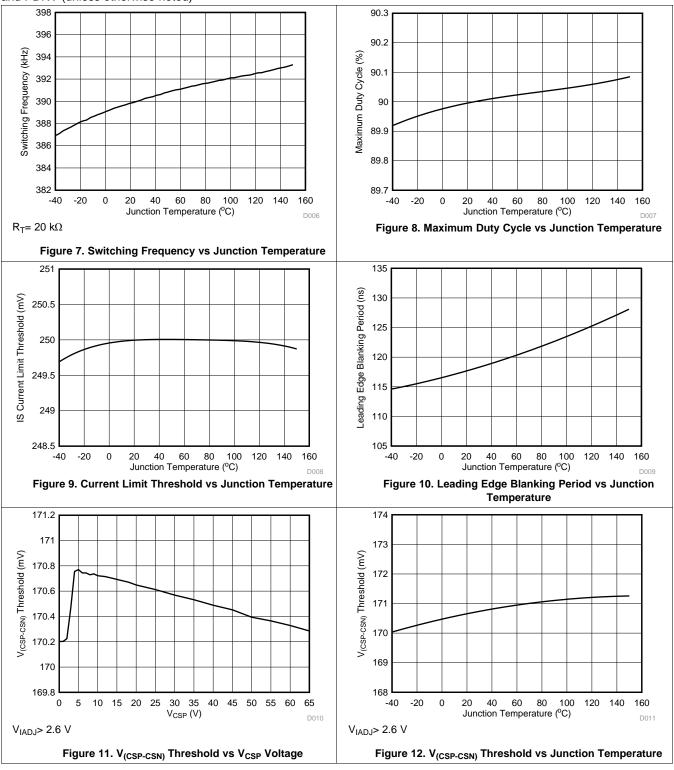

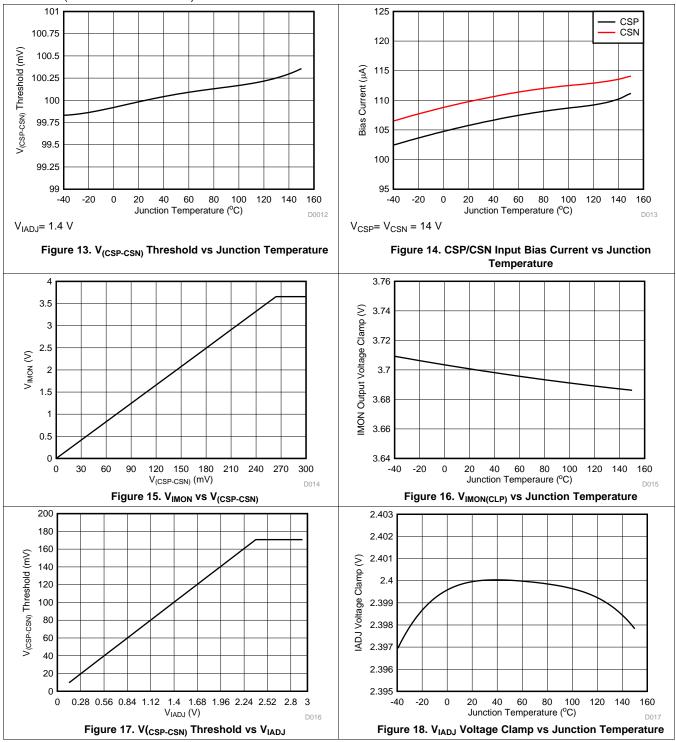

# **Typical Characteristics (continued)**

$T_A = 25^{\circ}$ C,  $V_{IN} = 14$  V,  $V_{IADJ} = 2.2$  V,  $C_{VCC} = 1$  µF,  $C_{COMP} = 2.2$  nF,  $R_{CS} = 100$  m $\Omega$ ,  $R_T = 20$  k $\Omega$ ,  $V_{PWM} = 5$  V, no load on GATE and PDRV (unless otherwise noted)

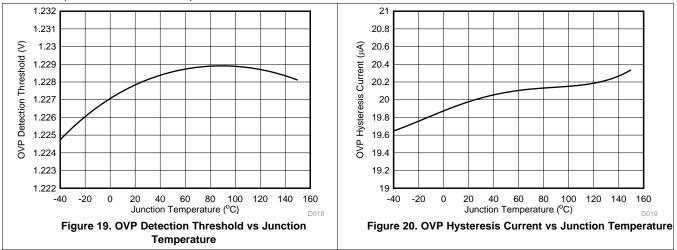

# **Typical Characteristics (continued)**

$T_A = 25^{\circ}C$ ,  $V_{IN} = 14$  V,  $V_{IADJ} = 2.2$  V,  $C_{VCC} = 1$   $\mu$ F,  $C_{COMP} = 2.2$  nF,  $R_{CS} = 100$  m $\Omega$ ,  $R_T = 20$  k $\Omega$ ,  $V_{PWM} = 5$  V, no load on GATE and PDRV (unless otherwise noted)

# **Typical Characteristics (continued)**

$T_A = 25^{\circ}C, V_{IN} = 14 \text{ V}, V_{IADJ} = 2.2 \text{ V}, C_{VCC} = 1 \text{ }\mu\text{F}, C_{COMP} = 2.2 \text{ }n\text{F}, R_{CS} = 100 \text{ }m\Omega, R_T = 20 \text{ }k\Omega, V_{PWM} = 5 \text{ V}, \text{ no load on GATE and PDRV (unless otherwise noted)}$

# 8 Detailed Description

# 8.1 Overview

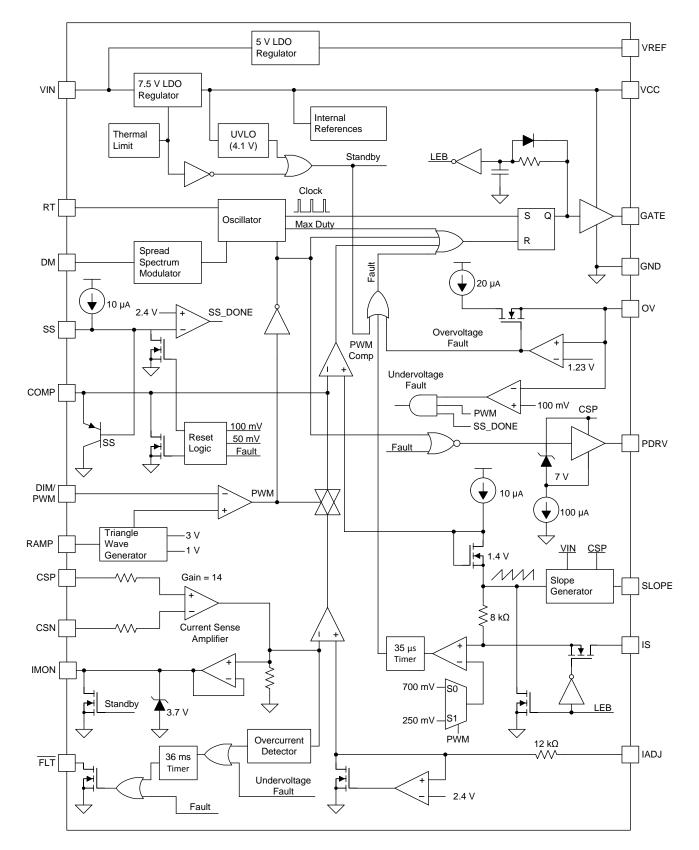

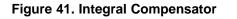

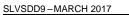

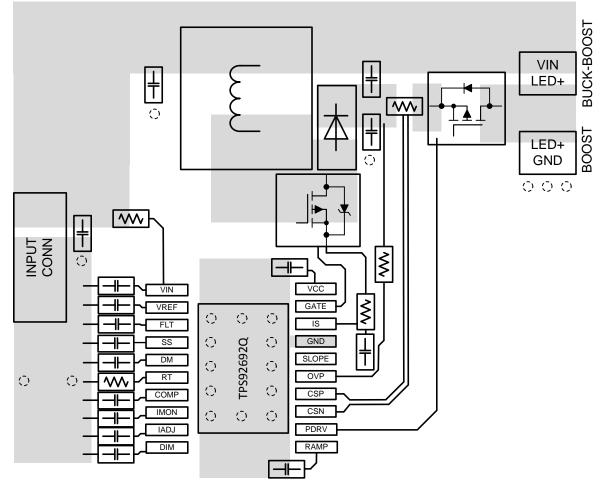

The TPS92692 and TPS92692-Q1 devices feature all of the functions necessary to implement a compact LED driver based on step-up or step-down power converter topologies. The devices implement a fixed-frequency, peak current mode control technique to achieve constant output current and fast transient response. The integrated low offset, rail-to-rail current sense amplifier provides the flexibility required to power a single string consisting of 1 to 20 series connected LEDs while maintaining better than 4% current accuracy over the operating temperature range. The LED current regulation threshold is set by the analog adjust input, IADJ and can be externally programmed to implement analog dimming with over 15:1 linear dimming range. The high impedance IADJ input simplifies LED current binning and thermal protection.

The TPS92692 and TPS92692-Q1 devices incorporate an internal PWM generator that can be programmed to implement pulse width modulation (PWM) dimming of LED current. The PWM duty cycle can be varied from 0% to 100% by modulating the analog voltage on DIM/PWM input from 1 V to 3 V. The PWM dimming frequency is externally programmable and is set by the capacitor connected to RAMP input. As an alternative, the TPS92692 and TPS92692-Q1 devices can also be configured to implement direct PWM dimming based on the duty cycle of external PWM signal by connecting a 249-k $\Omega$  resistor across RAMP pin and GND. The internal PWM signal controls the GATE and PDRV outputs which control the external n-channel switching FET and p-channel dimming FET connected in series with LED string, respectively.

The current monitor output, IMON, reports the instantaneous status of LED current measured by the rail-to-rail current sense amplifier. This feature indicates instantaneous current as a result of LED short circuit and cable harness failure, independent of LED driver topology. An open-drain fault indicator is also provided to report faults including cycle-by-cycle current limit, output overvoltage, and output undervoltage conditions. LED driver protection with auto-restart (hiccup) mode is enabled by connecting the fault pin (FLT) to the SS pin. Other protection features include VCC undervoltage protection and thermal shutdown. A remote signal can force the device in to shutdown by pulling down on the SS pin.

**TPS92692, TPS92692-Q1** SLVSDD9 – MARCH 2017

www.ti.com

# 8.2 Functional Block Diagram

# 8.3 Feature Description

# 8.3.1 Internal Regulator and Undervoltage Lockout (UVLO)

The device incorporates a 65-V input voltage rated linear regulators to generate the 7.5 V (typ)  $V_{CC}$  bias supply, the 5 V (typ)  $V_{REF}$  reference supply and other internal reference voltages. The device monitors the  $V_{CC}$  output to implement UVLO protection. Operation is enabled when  $V_{CC}$  exceeds the 4.5-V (typ) threshold and is disabled when  $V_{CC}$  drops below the 4.1-V (typ) threshold. The UVLO comparator provides 400 mV of hysteresis to avoid chatter during transitions. The UVLO thresholds are internally fixed and cannot be adjusted. An internal current limit circuit is implemented to protect the device during VCC pin short-circuit conditions. The  $V_{CC}$  supply powers the internal circuitry and the N-channel gate driver output, GATE. Place a bypass capacitor in the range of 2.2  $\mu$ F to 4.7  $\mu$ F across the  $V_{CC}$  output and GND to ensure proper operation. The regulator operates in dropout when input voltage  $V_{IN}$  falls below 7.5 V forcing  $V_{CC}$  to be lower than  $V_{IN}$  by 300 mV for a 20-mA supply current. The  $V_{CC}$  is a regulated output of the internal regulator and is not recommended to be driven from an external power supply.

The V<sub>REF</sub> supply is internally used to generate voltage thresholds for the RAMP generator circuit and to power some digital circuits. This supply can be used in conjunction with a resistor divider to set voltage levels for the IADJ pin and DIM/PWM pin to set LED current and PWM dimming duty cycle. It can also be used to bias external circuitry requiring a reference supply. The supply current is internally limited to protect the device from output overload and short-circuit conditions. Place a bypass capacitor in the range of 2.2  $\mu$ F to 4.7  $\mu$ F across the VREF output to GND to ensure proper operation.

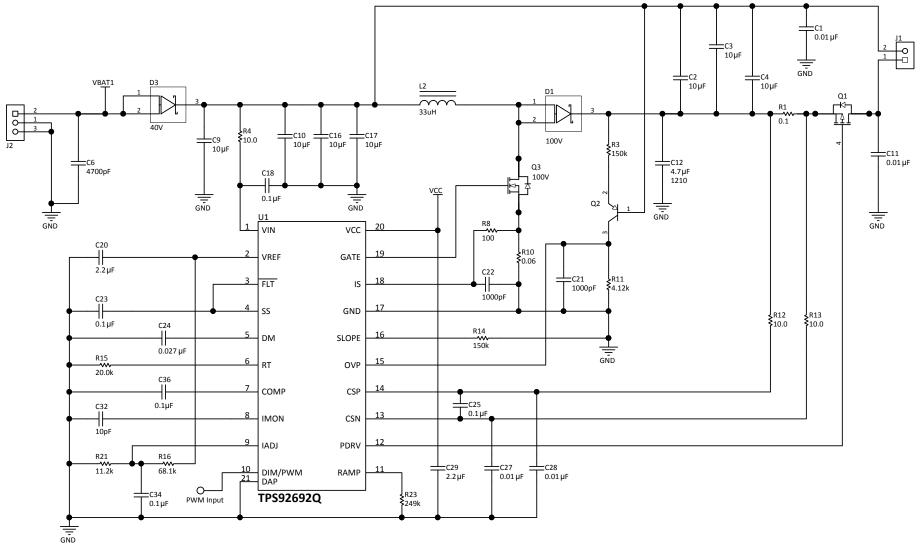

The TPS92692 and TPS92692-Q1 devices incorporate features that simplify compliance with the CISPR and automotive EMI requirements. The devices have optional spread spectrum frequency modulation circuit that can be externally configured to reduce peak and average conducted and radiated EMI. The internal programmable oscillator has a range of 80 kHz to 800 kHz and can be tuned based on the EMI requirements. The devices are available in HTSSOP-20 package with an exposed pad to aid in thermal dissipation.

# 8.3.2 Oscillator

The switching frequency is programmable by a single external resistor connected between the RT pin and GND. To set a desired frequency,  $f_{SW}$  (Hz), the resistor value can be calculated from Equation 1.

$$\mathsf{R}_{\mathsf{T}} = \frac{1.432 \times 10^{10}}{(\mathsf{f}_{\mathsf{SW}})^{1.047}} \ (\Omega)$$

(1)

Figure 6 shows a graph of switching frequency versus resistance, R<sub>T</sub>. TI recommends a switching frequency setting between 80 kHz and 700 kHz for optimal performance over input and output voltage operating range and for best efficiency. Operation at higher switching frequencies requires careful selection of N-channel MOSFET characteristics as well as detailed analysis of switching losses.

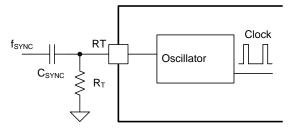

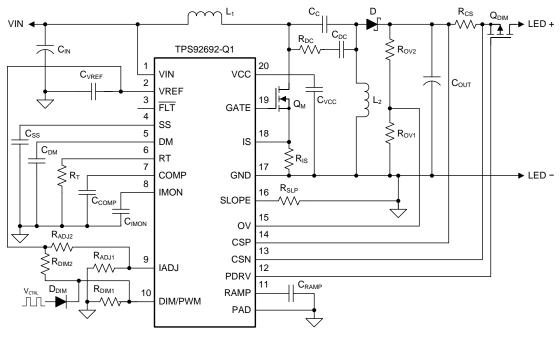

Figure 21. Oscillator Synchronization Through AC Coupling

The internal oscillator can be synchronized by AC coupling an external clock pulse to RT pin as shown in Figure 21. The positive going synchronization clock at the RT pin must exceed the RT sync threshold and the negative going synchronization clock at the RT pin must exceed the RT sync falling threshold to trip the internal synchronization pulse detector. TI recommends that the frequency of the external synchronization pulse is within  $\pm 20\%$  of the internal oscillator frequency programmed by the R<sub>T</sub> resistor. TI recommends a minimum coupling capacitor of 100 nF and a typical pulse width of 100 ns for proper synchronization. In the case where external synchronization clock is lost the internal oscillator takes control of the switching rate based on the R<sub>T</sub> resistor to maintain output current regulation. The R<sub>T</sub> resistor is always required whether the oscillator is free running or externally synchronized.

Copyright © 2017, Texas Instruments Incorporated

### Feature Description (continued)

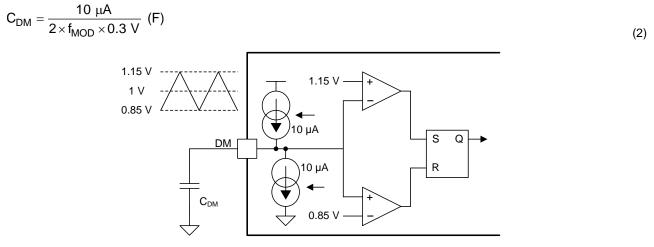

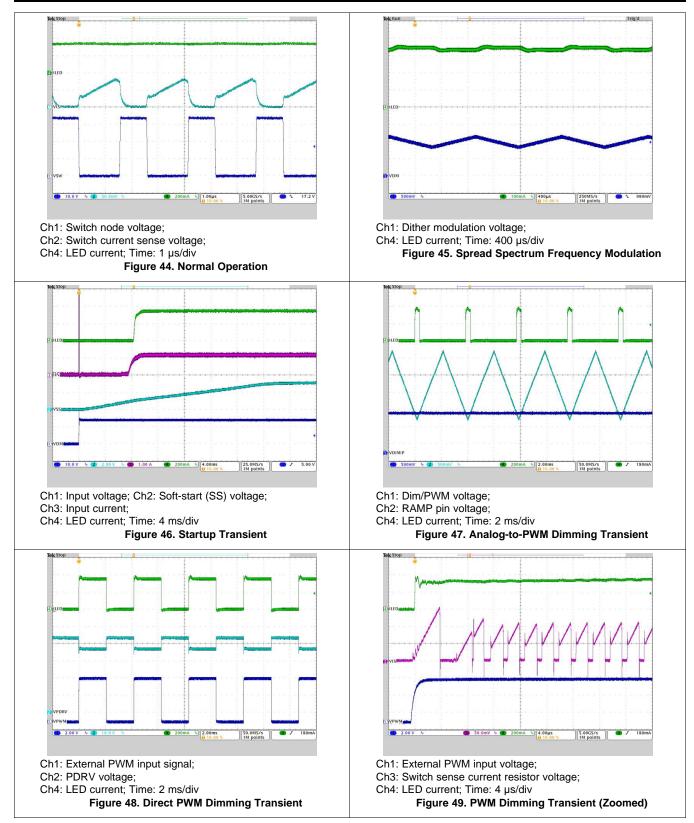

### 8.3.3 Spread Spectrum Frequency Modulation

The TPS92692 and TPS92692-Q1 devices provide a frequency dithering option that is enabled by connecting a capacitor from the DM pin to GND. A triangle waveform centered at 1 V is generated across the  $C_{DM}$  capacitor. The triangle waveform modulates the oscillator frequency by  $\pm$  15% of the nominal frequency set by an external timing resistor,  $R_T$ . The  $C_{DM}$  capacitance value sets the rate of the low frequency modulation. To achieve maximum attenuation in average EMI scan set modulation frequency ranging from 100 Hz to 1.2 kHz. The low modulating frequency has little impact on the quasi-peak EMI scan. Set the modulation frequency to 10 KHz or higher to achieve attenuation for quasi-peak EMI measurements. The modulation frequency higher than the receiver resolution bandwidth (RBW) of 9 kHz only impacts the quasi-peak EMI scan and has little impact on the average measurement. The device simplifies EMI compliance by providing the means to tune the modulation frequency based on measured EMI signature. Equation 2 calculates the  $C_{DM}$  capacitance required to set the modulation frequency,  $f_{MOD}$  (Hz).

Figure 22. Frequency Dither Operation

Connect the DM pin to GND to disable frequency dither circuit operation. Internal frequency dithering is not supported when the devices are synchronized based on an external clock signal.

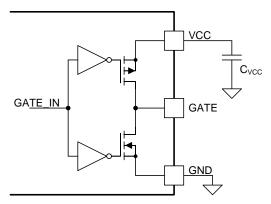

# 8.3.4 Gate Driver

The TPS92692 and TPS92692-Q1 devices contain a N-channel gate driver that switches the output  $V_{GATE}$  between  $V_{CC}$  and GND. A peak source and sink current of 500 mA allows controlled slew-rate of the MOSFET gate and drain node voltages, limiting the conducted and radiated EMI generated by switching.

Figure 23. Push-Pull N-Channel Gate Driver Circuit

# Feature Description (continued)

The gate driver supply current  $I_{CC(GATE)}$  depends on the total gate drive charge (Q<sub>G</sub>) of the MOSFET and the operating frequency of the converter,  $f_{SW}$ ,  $I_{CC(GATE)} = Q_G \times f_{SW}$ . Choose a MOSFET with a low gate charge specification to limit the junction temperature rise and switch transition losses.

It is important to consider the MOSFET threshold voltage when operating in the dropout region when the input voltage,  $V_{IN}$ , is below the  $V_{CC}$  regulation level. TI recommends a logic level device with a threshold voltage below 5 V when the device is required to operate at an input voltage less than 7 V.

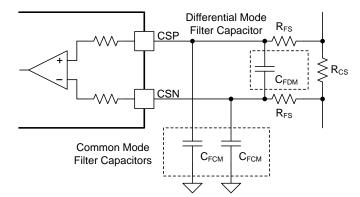

# 8.3.5 Rail-to-Rail Current Sense Amplifier

The internal rail-to-rail current sense amplifier measures the average LED current based on the differential voltage drop between the CSP and CSN inputs over a common mode range of 0 V to 65 V. The differential voltage,  $V_{(CSP-CSN)}$ , is amplified by a voltage-gain factor of 14 and is connected to the negative input of the transconductance error amplifier. Accurate LED current feedback is achieved by limiting the cumulative input offset voltage, (represented by the sum of the voltage-gain error, the intrinsic current sense offset voltage, and the transconductance error amplifier offset voltage) to less than 5 mV over the recommended common-mode voltage, and temperature range.

Figure 24. Current Sense Amplifier Input Filter Options

An optional common-mode or differential mode low-pass filter implementation, as shown in Figure 24, can be used to smooth out the effects of large output current ripple and switching current spikes caused by diode reverse recovery. TI recommends a filter resistance in the range of 10  $\Omega$  to 100  $\Omega$  to limit the additional offset caused by amplifier bias current mismatch to achieve the best accuracy and line regulation.

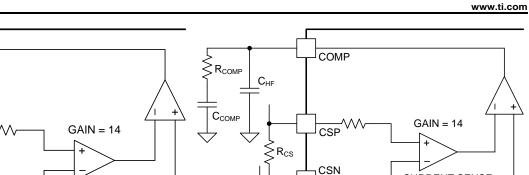

# 8.3.6 Transconductance Error Amplifier

The internal transconductance amplifier generates an error signal proportional to the difference between the LED current sense feedback voltage and the external IADJ input voltage. The output of the error amplifier is connected to an external compensation network to achieve closed-loop LED current regulation. In most LED driver applications a simple integral compensation circuit consisting of a capacitor connected from COMP output to GND provides a stable response over wide range of operating conditions. TI recommends a capacitor value between 10 nF and 100 nF as a good starting point. To achieve higher closed-loop bandwidth a proportional-integral compensator, consisting of a series resistor and a capacitor network connected across the COMP output and GND, is required. Based on the converter topology, tune the compensation network to achieve a minimum of 60° of phase margin and 10 dB of gain margin. The *Application and Implementation* section includes a summarized detailed design procedure.

# Feature Description (continued)

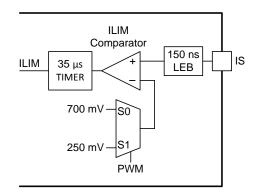

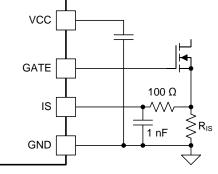

### 8.3.7 Switch Current Sense

The IS input pin monitors the main MOSFET current to implement peak current mode control. The GATE output duty cycle is derived by comparing the peak switch current, measured by the R<sub>IS</sub> resistor, to the internal COMP voltage threshold. An internal slope signal, V<sub>SL</sub>, generated by slope compensation circuit is added to the measured sense voltage, V<sub>IS</sub>, to prevent subharmonic oscillations for duty cycles greater than 50%. An internal blanking circuit prevents MOSFET switching current spike propagation and premature termination of duty cycle by internally shunting the IS input for 150 ns after the beginning of the new switching period. For additional noise suppression connect an external low-pass RC filter with resistor values ranging from 100  $\Omega$  to 500  $\Omega$  and a 1000 pF capacitor. The external RC filter ensures proper operation when operating in the dropout region (V<sub>IN</sub> less than 7 V).

Figure 25. Switch Current Limit Circuit

Cycle-by-cycle current limit is accomplished by a redundant internal comparator. The current limit threshold is set based on the status of internal PWM signal. The current limit threshold is set to 250 mV (typ) when PWM signal is high and to 700 mV (typ) when PWM signal is low. The transition between the two thresholds work in conjunction with slope compensation and the error amplifier circuit to allow for higher inductor current immediately after the PWM transition and to improve LED current transient response during PWM dimming. Refer to the *DIM/PWM Input* section for details on PWM Dimming operation.

The device immediately terminates the GATE and PDRV output when the IS input voltage,  $V_{IS}$ , exceeds the threshold value. Upon a current limit event, the SS and COMP pin are internally grounded to reset the state of the controller. The GATE output is enabled after the expiration of the 35-µs internal fault timer and a new start-up sequence is initiated through the SS pin. Equation 3 calculates the peak inductor current in the current limit.

$$I_{L(PK)} = \frac{250mV}{R_{IS}}$$

(A) (3)

# 8.3.8 Slope Compensation

Peak current mode based regulators are subject to sub-harmonic oscillations for duty cycle greater than 50%. To avoid this instability problem, the control scheme is modified by the addition of an artificial ramp to the sensed switch current waveform. The slope of the artificial ramp required is dependent on the input voltage,  $V_{IN}$ , output voltage,  $V_O$ , inductor, L, and switch current sense resistor,  $R_{IS}$ . The devices incorporate an adaptive slope compensation technique that modifies the slope of the artificial ramp generated based on the input voltage,  $V_{IN}$  and output voltage measured at CSP pin,  $V_{CSP}$ , thus greatly simplifying the design for common LED driver topologies, such as boost, buck-boost, and boost-to-battery. The magnitude of the internal ramp signal can be calculated as follows:

$$V_{SL} = 278 \times 10^{6} \times D \times \frac{\left(0.494 \times \left(V_{CSP} - V_{O}\right) + 1\right)}{f_{SW} \times R_{SLP}}$$

where

D is the converter duty cycle

(4)

### Feature Description (continued)

The resistor, R<sub>SLOPE</sub> provides the flexibility to set the slope of the internal artificial ramp based on the inductance value, L and the LED driver topology. The *Application and Implementation* section includes detailed calculations for the resistor, R<sub>SLOPE</sub>, based on the LED driver topology. The SLOPE pin cannot be left floating.

### 8.3.9 Analog Adjust Input

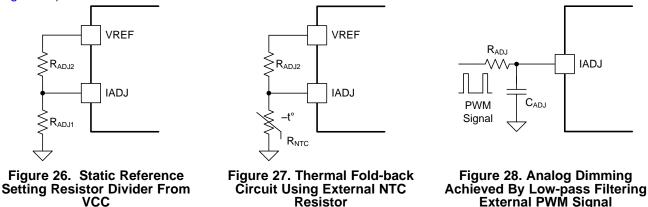

The voltage across the LED current sense resistor,  $V_{(CSP-CSN)}$ , is regulated to the analog adjust input voltage,  $V_{IADJ}$ , scaled by the current sense amplifier voltage gain of 14. The LED current can be linearly adjusted by varying the voltage on IADJ pin from 140 mV to 2.25 V using either a resistor divider from  $V_{REF}$  or a voltage source. The IADJ pin can be connected to  $V_{REF}$  through an external resistor to set LED current based on the 2.4-V internal reference voltage. This device offers different methods to set the IADJ voltage. Figure 27 shows how the IADJ input can be used in conjunction with a NTC resistor to implement thermal foldback protection. A PWM signal in conjunction with first- or second-order low-pass filter can be used to program the IADJ voltage as shown in Figure 28).

# 8.3.10 DIM/PWM Input

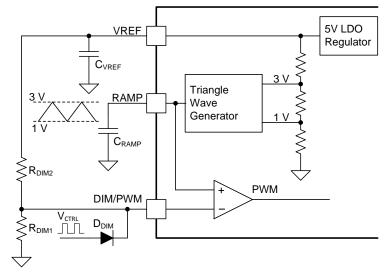

The TPS92692 and TPS92692-Q1 devices incorporate a PWM generator circuit to facilitate analog voltage to PWM duty cycle translation. The dimming frequency is set by connecting a capacitor from RAMP pin to GND. The dimming frequency, f<sub>DIM</sub>, can be calculated as follows:

$$f_{\text{DIM}} = \frac{10 \ \mu\text{A}}{2 \times 2 \ \text{V} \times \text{C}_{\text{DIM}}} \quad (\text{Hz})$$

(5)

The internal PWM signal can be varied from 0% to 100% by setting the DIM/PWM pin voltage between 1 V and 3 V. Equation 6 describes the relationship between DIM/PWM pin voltage,  $V_{DIM}$  and internal PWM duty cycle,  $D_{PWM(INT)}$ .

$$\mathsf{D}_{\mathsf{PWM}(\mathsf{INT})} = \frac{\mathsf{V}_{\mathsf{DIM}} - 1}{2} \tag{6}$$

For improved dimming accuracy, use the VREF pin and a resistor divider to set the DIM/PWM pin voltage,  $V_{DIM}$ , and the corresponding duty cycle. The device can be configured to step the duty cycle between 100% and the programmed value by diode connecting the external control signal,  $V_{CTRL}$ , to the DIM/PWM pin, as shown in Figure 29. The external control signal, of amplitude 3-V, is usually generated by the command module and is based on the light output required by the application.

# Feature Description (continued)

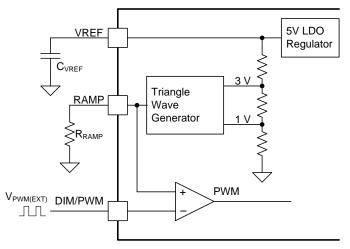

Figure 29. PWM Dimming Using Internal PWM Generator

The devices can be configured to be compatible with external PWM signal,  $V_{PWM(EXT)}$ , where the LED current is modulated based on the duty cycle,  $D_{PWM(EXT)}$ . To enable direct PWM, it is required to disable the internal triangle wave generator by connecting a 249-k $\Omega$  resistor from RAMP pin to GND. In this case, the internal comparator threshold is set to 2.49-V and the internal PWM duty cycle,  $D_{PWM(INT)}$ , is controlled by the external PWM command. The RAMP pin cannot be left floating.

Figure 30. Direct PWM Dimming

The internal PWM signal,  $V_{PWM}$  controls the GATE and PDRV outputs. Forcing  $V_{PWM}$  in a logic low state turns off switching, parks the oscillator, disconnects the COMP pin, and sets the PDRV output to  $V_{CSP}$  in order to maintain the charge on the compensation network and output capacitors. On the rising edge of the PWM voltage ( $V_{PWM}$ set to logic level high), the GATE and PDRV outputs are enabled to ramp the inductor current to the previous steady-state value. The COMP pin is connected and the error amplifier and oscillator are enabled only when the switch current sense voltage  $V_{IS}$  exceeds the COMP voltage,  $V_{COMP}$ , thus immediately forcing the converter into steady-state operation with minimum LED current overshoot. When dimming is not required, connect the DIM/PWM pin to the  $V_{CC}$  pin. An internal pull-down resistor sets the input to logic-low and disables the device when the pin is disconnected or left floating.

### **Feature Description (continued)**

# 8.3.11 Series P-Channel FET Dimming Gate Driver Output

The PDRV output is a function of the internal PWM signal and is capable of sinking and sourcing up to 50 mA of peak current to control a high-side series connected P-channel dimming FET. The PDRV switches between  $V_{CSP}$  and  $(V_{CSP}-7 V)$  based on the status of PWM signal to completely turn-off and turn-on the external P-channel dimming FET. The series dimming FET is required to achieve high contrast ratio as it ensures fast rise and fall times of the LED current in response to the PWM input. Without any dimming FET, the rise and fall times are limited by the inductor slew rate and the closed-loop bandwidth of the system. Leave the PDRV pin unconnected if not used.

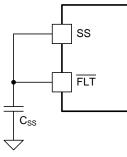

### 8.3.12 Soft-Start

The soft-start feature helps the regulator gradually reach the steady-state operating point, thus reducing startup stresses and surges. The devices clamp the COMP pin to the SS pin, separated by a diode, until LED current nears the regulation threshold. The internal 10- $\mu$ A soft-start current source gradually increases the voltage on an external soft-start capacitor C<sub>SS</sub> connected to the SS pin. This results in a gradual rise of the COMP voltage from GND.

The internal 10- $\mu$ A current source turns on when VCC exceeds the UVLO threshold. At the beginning of the softstart sequence, the SS pull-down switch is active and is released when the voltage V<sub>SS</sub> drops below 50 mV. The SS pin can also be pulled down by an external switch to stop switching. When the SS pin is externally driven to enable switching, the slew-rate on the COMP pin is controlled by the compensation capacitor. In this case, the startup duration and LED current transient is controlled by tunning the compensation network. It is essential to ensure that the softstart duration is longer than the time required to charge the output capacitor when selecting the soft-start capacitor, C<sub>SS</sub> and the compensation capacitor, C<sub>COMP</sub>.

# 8.3.13 Current Monitor Output

The IMON pin voltage represents the LED current measured by the rail-to-rail current sense amplifier across the external current shunt resistor. The linear relationship between the IMON voltage and LED current includes the amplifier gain-factor of 14 (see *Feature Description* section). The IMON output can be connected to an external microcontroller or comparator to facilitate LED open, short, or cable harness fault detection and mitigation. The IMON voltage is internally clamped to 3.7 V.

# 8.3.14 Output Overvoltage Protection

The TPS92692 and TPS92692-Q1 devices include a dedicated OV pin which can be used for either input or output overvoltage protection. This pin features a precision 1.228 V (typ) threshold with  $20-\mu$ A (typ) of hysteresis current. The overvoltage threshold limit is set by a resistor divider network from the input or output terminal to GND. When the OV pin voltage exceeds the reference threshold, the GATE pin is immediately pulled low, the PDRV output is disabled, and the SS and COMP capacitors are discharged. The GATE and PDRV outputs are enabled and a new startup sequence is initiated after the voltage drops below the hysteresis threshold set by the 20- $\mu$ A source current and the external resistor divider.

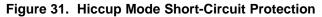

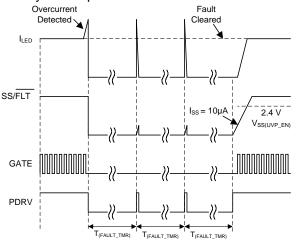

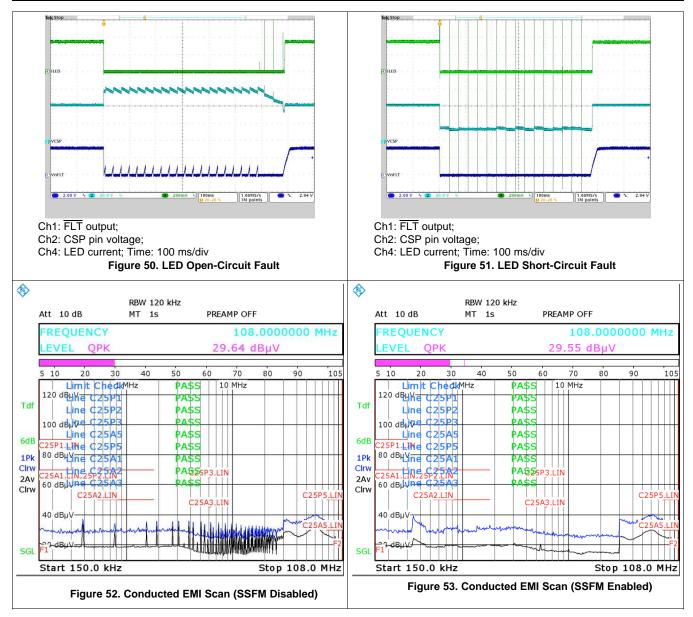

# 8.3.15 Output Short-circuit Protection

The device monitors the output of the current sense amplifier and the output voltage via OV pin to determine LED Short-circuit fault. The device signals an output overcurrent fault when the voltage across the current sense amplifier, ( $V_{(CSP-CSN)}$ ), exceeds the regulation set point based on the IADJ pin voltage,  $V_{IADJ}$ . The overcurrent fault threshold is calculated as follows:

$$V_{(CSP-CSN),OCP)} = 1.5 \times \frac{V_{IADJ}}{14}$$

(7)

The device also indicates a short-circuit condition when the voltage across the OV pin and GND falls below 100 mV. In this case, the output voltage,  $V_0$ , is below the undervoltage fault threshold determined based on the resistor divider connected to the OV pin.

$$V_{O(UV)} = 0.1 \times \frac{R_{OV1} + R_{OV2}}{R_{OV1}}$$

(8)

TPS92692, TPS92692-Q1

SLVSDD9-MARCH 2017

### **Feature Description (continued)**