**TUSB8020B**

SLLSEF6C -JULY 2014-REVISED JUNE 2017

# TUSB8020B Two-Port USB 3.0 Hub

#### **Features**

- Two-Port USB 3.0 Compliant Hub, USBIF TID#330000057

- USB 2.0 Hub Features

- Multi-Transaction Translator (MTT) Hub: Two **Transaction Translators**

- Four Asynchronous Endpoint Buffers Per **Transaction Translator**

- Supports Battery Charging

- CDP Mode (Upstream Port Connected)

- DCP Mode (Upstream Port Unconnected)

- DCP Mode Complies With Chinese Telecommunications Industry Standard YD/T 1591-2009

- Support D+/D- Divider Mode

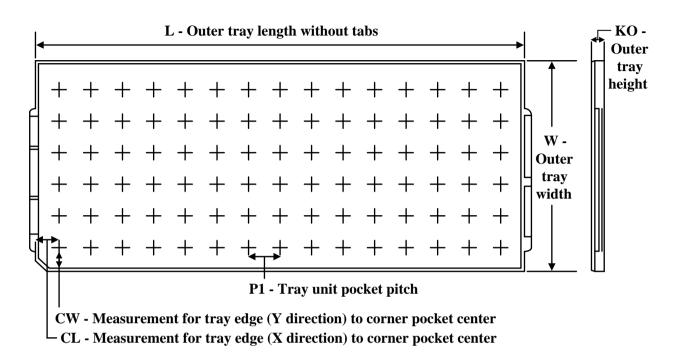

- Supports Operation as a USB 3.0 or USB 2.0 Compound Device

- Per Port or Ganged Power Switching and **Overcurrent Notification Inputs**

- OTP ROM, Serial EEPRO,M or I<sup>2</sup>C/SMBus Slave Interface for Custom Configurations:

- VID and PID

- Port Customizations

- Manufacturer and Product Strings (not by OTP ROM)

- Serial Number (not by OTP ROM)

- Application Feature Selection Using Terminal Selection or EEPROM/ or I<sup>2</sup>C/SMBus Slave Interface

- Provides 128-Bit Universally Unique Identifier

- Supports On-Board and In-System OTP/EEPROM Programming Through the USB 2.0 Upstream Port

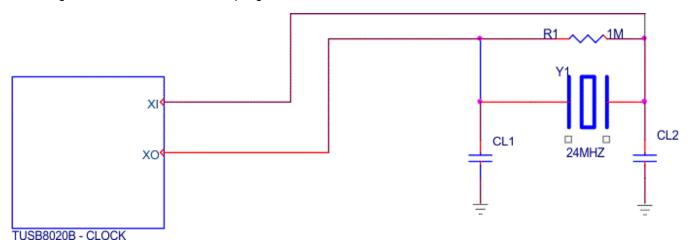

- Single Clock Input, 24-MHz Crystal or Oscillator

- No Special Driver Requirements: Works Seamlessly on any Operating System With USB Stack Support

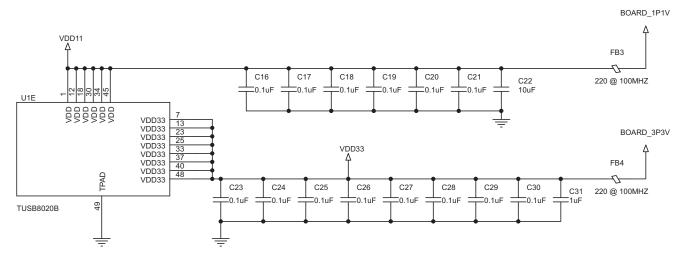

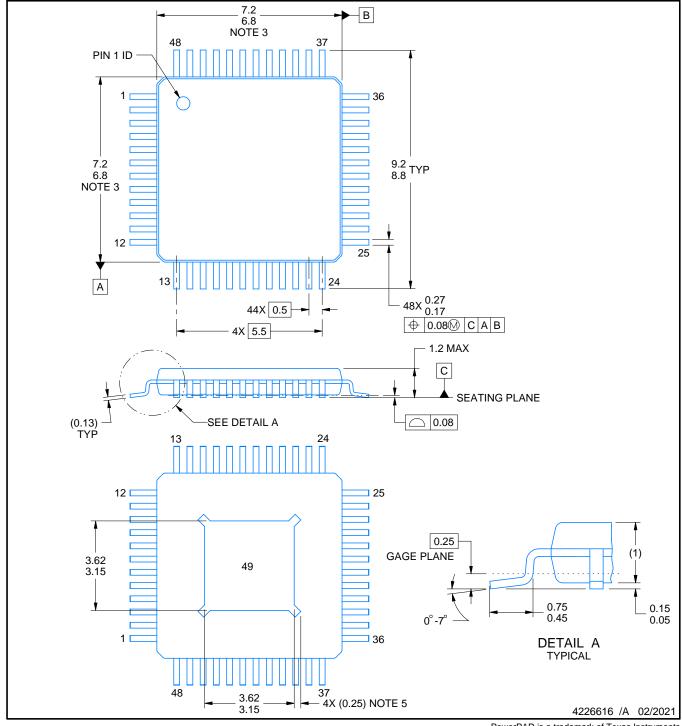

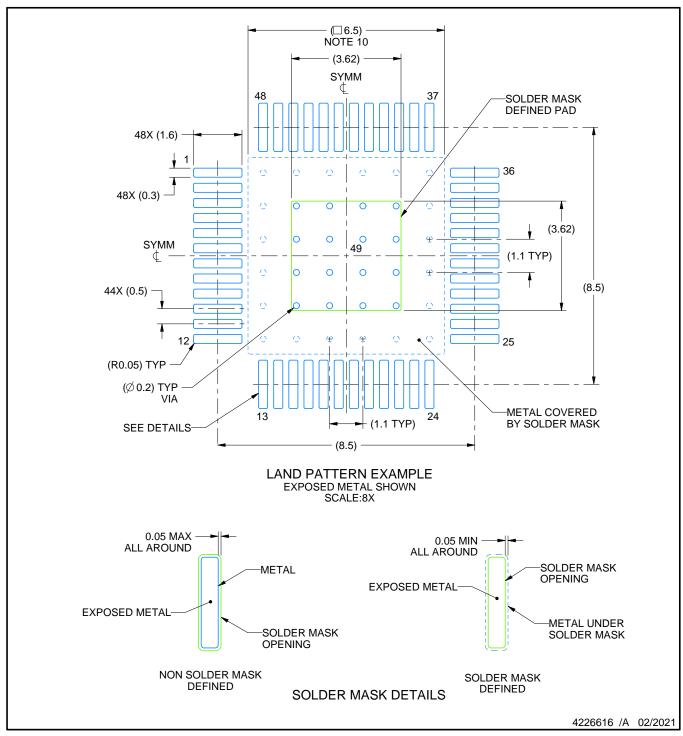

- 48-Pin HTQFP Package (PHP)

# Applications

- Computer Systems

- **Docking Stations**

- Monitors

- Set-Top Boxes

## 3 Description

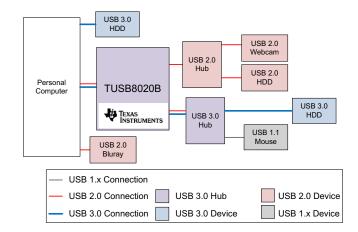

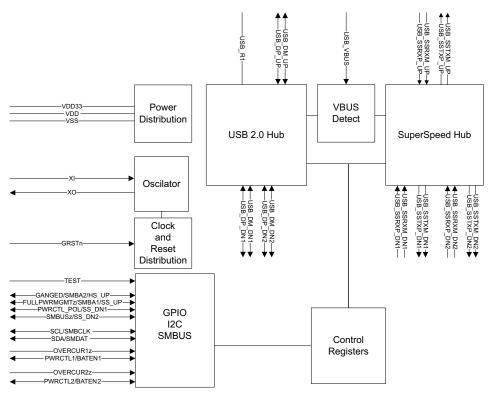

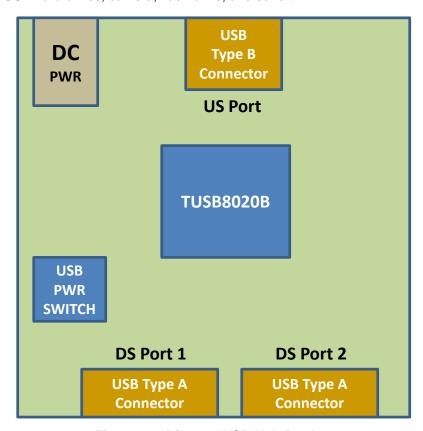

The TUSB8020B is a two-port USB 3.0 compliant hub. It provides simultaneous SuperSpeed USB and high-speed/full-speed connections on the upstream port and provides SuperSpeed USB, high-speed, fullspeed, or low-speed connections on the downstream ports. When the upstream port is connected to an electrical environment that only supports high-speed or full-speed/low-speed connections, SuperSpeed USB connectivity is disabled on the downstream ports. When the upstream port is connected to an electrical environment that only supports fullspeed/low-speed connections, SuperSpeed USB and high-speed connectivity are disabled downstream ports.

The TUSB8020B supports per port or ganged power switching and overcurrent protection.

An individually port power controlled hub switches power on or off to each downstream port as requested by the USB host. Also when an individually port power controlled hub senses an overcurrent event, only power to the affected downstream port will be switched off.

A ganged hub switches on power to all its downstream ports when power is required to be on for any port. The power to the downstream ports is not switched off unless all ports are in a state that allows power to be removed. Also when a ganged hub senses an overcurrent event, power to all downstream ports will be switched off.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TUSB8020B   | HTQFP (48) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Table of Contents

| 1 | Features 1                               |    | 8.4 Device Functional Modes                      | 12 |

|---|------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                           |    | 8.5 Register Maps                                | 13 |

| 3 | Description 1                            | 9  | Application and Implementation                   | 25 |

| 4 | Revision History2                        |    | 9.1 Application Information                      | 25 |

| 5 | Description (continued)2                 |    | 9.2 Typical Application                          | 25 |

| 6 | Pin Configuration and Functions          | 10 | Power Supply Recommendations                     | 30 |

| 7 | Specifications                           |    | 10.1 Power Supply                                | 30 |

| • | 7.1 Absolute Maximum Ratings             |    | 10.2 Downstream Port Power                       | 30 |

|   | 7.2 ESD Ratings                          |    | 10.3 Ground                                      | 30 |

|   | 7.3 Recommended Operating Conditions     | 11 | Layout                                           | 31 |

|   | 7.4 Thermal Information                  |    | 11.1 Layout Guidelines                           | 31 |

|   | 7.5 3.3-V I/O Electrical Characteristics |    | 11.2 Layout Example                              | 32 |

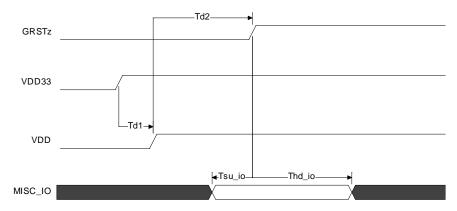

|   | 7.6 Power-Up Timing Requirements         | 12 | Device and Documentation Support                 | 34 |

|   | 7.7 Hub Input Supply Current             |    | 12.1 Community Resources                         | 34 |

| 8 | Detailed Description9                    |    | 12.2 Trademarks                                  | 34 |

| Ū | 8.1 Overview                             |    | 12.3 Electrostatic Discharge Caution             | 34 |

|   | 8.2 Functional Block Diagram             |    | 12.4 Glossary                                    | 34 |

|   | 8.3 Feature Description                  | 13 | Mechanical, Packaging, and Orderable Information | 34 |

# 4 Revision History

| Changes from Revision B (March 2017) to Revision C                    | Page |

|-----------------------------------------------------------------------|------|

| Added SMBUS Programming current to the Hub Input Supply Current table | 8    |

| Added Note to the SMBus Slave Operation section                       | 12   |

| Changes from Revision A (July 2014) to Revision B                     | Page |

| Replaced the Absolute Maximum Ratings table                           | 6    |

| Changes from Original (July 2004) to Revision A                       | Page |

| Changed device status to production data                              | 1    |

# 5 Description (continued)

The TUSB8020B downstream ports provide support for battery charging applications by providing battery charging connected downstream port (CDP) handshaking support. It also supports a dedicated charging port (DCP) mode when the upstream port is not connected. The DCP mode supports USB devices which support the USB Battery Charging and the Chinese Telecommunications Industry Standard YD/T 1591-2009. In addition, an automatic mode provides transparent support for BC devices and devices supporting Divider Mode charging solutions when the upstream port is unconnected.

The TUSB8020B provides terminal strap configuration for some features including battery charging support, and also provides customization though OTP ROM, I<sup>2</sup>C EEPROM or through an I<sup>2</sup>C/SMBus slave interface for PID, VID, and custom port and phy configurations. Custom string support is also available when using an I<sup>2</sup>C EEPROM or the I<sup>2</sup>C/SMBus slave interface.

The device is available in a 48-pin HTQFP package and is offered in a commercial version (TUSB8020B) for operation over the temperature range of 0°C to 70°C and in an industrial version (TUSB8020BI) for operation over the temperature range of –40°C to 85°C.

Submit Documentation Feedback

Copyright © 2014–2017, Texas Instruments Incorporated

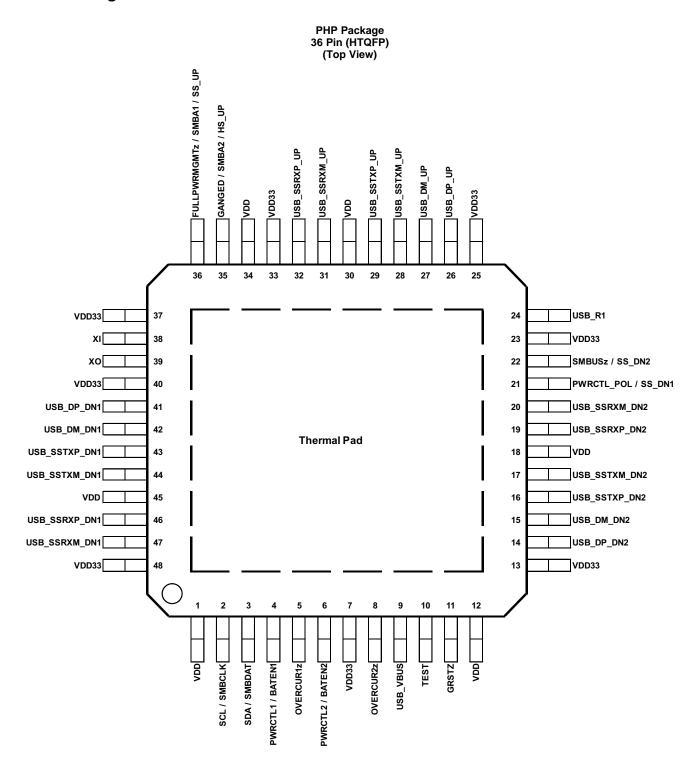

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN                 |       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | NO.   | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CLOCK AND RESET SIG | SNALS |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

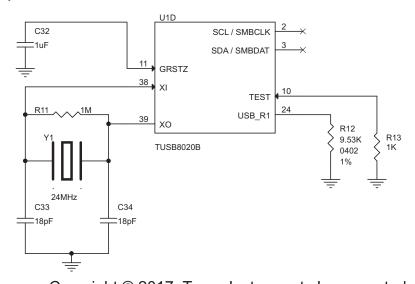

| GRSTz               | 11    | I<br>PU   | Global power reset. This reset brings all of the TUSB8020B internal registers to their default states. When GRSTz is asserted, the device is completely nonfunctional.                                                                                                                                                                                                                                                                                                                            |  |  |

| XI                  | 38    | I         | Crystal input. This terminal is the crystal input for the internal oscillator. The input may alternately be driven by the output of an external oscillator. When using a crystal a $1-M\Omega$ feedback resistor is required between XI and XO.                                                                                                                                                                                                                                                   |  |  |

| хо                  | 39    | 0         | Crystal output. This terminal is the crystal output for the internal oscillator. If XI is driven by an external oscillator this pin may be left unconnected. When using a crystal a 1- $M\Omega$ feedback resistor is required between XI and XO.                                                                                                                                                                                                                                                 |  |  |

| USB UPSTREAM SIGNA  | LS    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

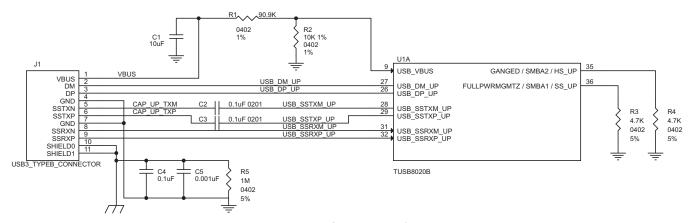

| USB_SSTXP_UP        | 29    | 0         | USB SuperSpeed transmitter differential pair (positive)                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| USB_SSTXM_UP        | 28    | 0         | USB SuperSpeed transmitter differential pair (negative)                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| USB_SSRXP_UP        | 32    | - 1       | USB SuperSpeed receiver differential pair (positive)                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| USB_SSRXM_UP        | 31    | - 1       | USB SuperSpeed receiver differential pair (negative)                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| USB_DP_UP           | 26    | I/O       | USB high-speed differential transceiver (positive)                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| USB_DM_UP           | 27    | I/O       | USB high-speed differential transceiver (negative)                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| USB_R1              | 24    | 1         | Precision resistor reference. A 9.53-kΩ ±1% resistor should be connected between USB_R1 and GND.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| USB_VBUS            | 9     | I         | USB upstream port power monitor. The VBUS detection requires a voltage divider. The signal USB_VBUS must be connected to VBUS through a 90.9-kΩ ±1% resistor, and to ground through a 10-kΩ ±1% resistor from the signal to ground.                                                                                                                                                                                                                                                               |  |  |

| USB DOWNSTREAM SIG  | GNALS |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

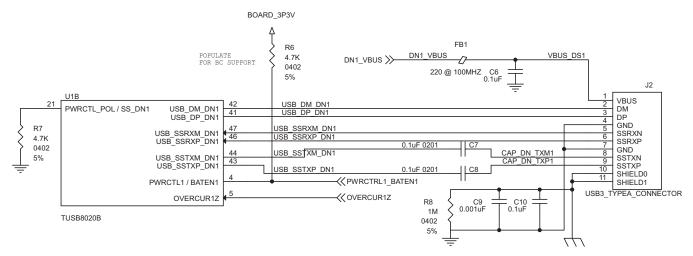

| USB_SSTXP_DN1       | 43    | 0         | USB SuperSpeed transmitter differential pair (positive) downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| USB_SSTXM_DN1       | 44    | 0         | USB SuperSpeed transmitter differential pair (negative) downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| USB_SSRXP_DN1       | 46    | 1         | USB SuperSpeed receiver differential pair (positive) downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| USB_SSRXM_DN1       | 47    | 1         | USB SuperSpeed receiver differential pair (negative) downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| USB_DP_DN1          | 41    | I/O       | USB high-speed differential transceiver (positive) downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| USB DM DN1          | 42    | I/O       | USB high-speed differential transceiver (negative) downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

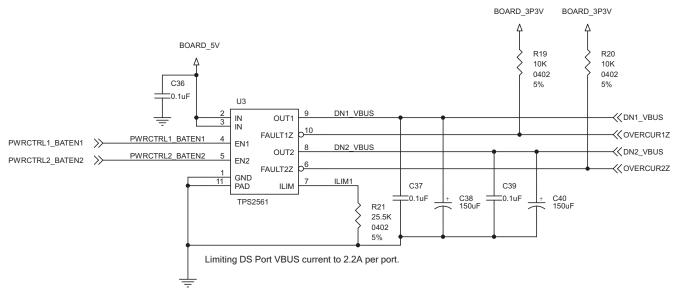

| PWRCTL1/BATEN1      | 4     | I/O<br>PD | USB port 1 power-on control for downstream power or battery charging enable. The terminal is used for control of the downstream power switch for Port 1.  In addition, the value of the terminal is sampled at the deassertion of reset to determine the value of the battery charging support for Port 1 as indicated in the Battery Charging Support register.  0 = Battery charging not supported 1 = Battery charging supported                                                               |  |  |

| OVERCUR1z           | 5     | I<br>PU   | USB DS port 1 overcurrent detection input. This terminal is used to connect the over current output of the downstream port power switch for port 1.  0 = An overcurrent event has occurred 1 = An overcurrent event has not occurred If power management is enabled, the external circuitry needed should be determined by the power switch. In ganged mode, either OVERCUR1z or OVERCUR2z can be used. In ganged mode, the overcurrent will be reported as a hub event instead of a port event.  |  |  |

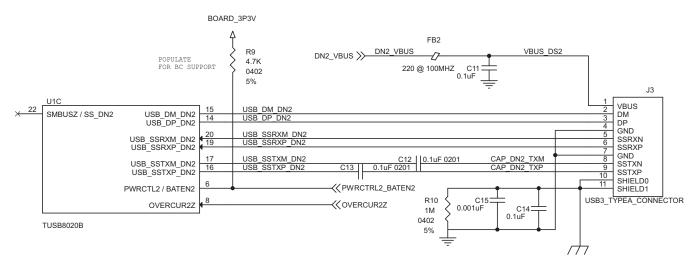

| USB_SSTXP_DN2       | 16    | 0         | USB SuperSpeed transmitter differential pair (positive) downstream port 2.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| USB_SSTXM_DN2       | 17    | 0         | USB SuperSpeed transmitter differential pair (negative) downstream port 2.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| USB_SSRXP_DN2       | 19    | 1         | USB SuperSpeed receiver differential pair (positive) downstream port 2.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| USB_SSRXM_DN2       | 20    | - 1       | USB SuperSpeed receiver differential pair (negative) downstream port 2.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| USB_DP_DN2          | 14    | I/O       | USB high-speed differential transceiver (positive) downstream port 2.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| USB_DM_DN2          | 15    | I/O       | USB high-speed differential transceiver (negative) downstream port 2.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| PWRCTL2/BATEN2      | 6     | I/O<br>PD | Power-on control /battery charging enable for downstream port 2. This terminal is used for control of the downstream power switch for port 2.  The value of the terminal is sampled at the deassertion of reset to determine the value of the battery charging support for port 2 as indicated in the Battery Charging Support register.  0 = Battery charging not supported 1 = Battery charging supported                                                                                       |  |  |

| OVERCUR2z           | 8     | I<br>PU   | Overcurrent detection for downstream port 2. This terminal is used to connect the over current output of the downstream port power switch for port 2.  0 = An overcurrent event has occurred 1 = An overcurrent event has not occurred  If power management is enabled, the external circuitry needed should be determined by the power switch. In ganged mode either OVERCUR1z or OVERCUR2z can be used. In ganged mode the overcurrent will be reported as a hub event instead of a port event. |  |  |

Submit Documentation Feedback

Copyright © 2014–2017, Texas Instruments Incorporated

# Pin Functions (continued)

| PIN                            |                                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                           | NO.                              | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| I <sup>2</sup> C/SMBUS SIGNALS |                                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                |                                  |           | I <sup>2</sup> C clock/SMBus clock. Function of terminal depends on the setting of the SMBUSz input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| l                              |                                  | I/O       | When SMBUSz = 1, this terminal acts as the serial clock interface for an $I^2C$ EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SCL/SMBCLK                     | 2                                | PD        | When SMBUSz = 0, this terminal acts as the serial clock interface for an SMBus host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| l                              |                                  |           | This pin must be pulled up to use the OTP ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                |                                  |           | Can be left unconnected if external interface not implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                |                                  |           | I <sup>2</sup> C data/SMBus data. Function of terminal depends on the setting of the SMBUSz input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                                |                                  | I/O       | When SMBUSz = 1, this terminal acts as the serial data interface for an $I^2C$ EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SDA/SMBDAT                     | 3                                | PD        | When SMBUSz = 0, this terminal acts as the serial data interface for an SMBus host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                |                                  |           | This pin must be pulled up to use the OTP ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                |                                  |           | Can be left unconnected if external interface not implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| TEST AND MISCELLANE            | OUS SIGNALS                      |           | DUDING THE RESIDENCE OF THE PROPERTY OF THE PR |  |  |  |

| İ                              |                                  |           | SMBUS mode / SuperSpeed USB Status for downstream port 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| İ                              |                                  | 1         | The value of the terminal is sampled at the deassertion of reset to enable I <sup>2</sup> C or SMBus mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| SMBUSz/SS_DN2                  | 22                               | PU        | 0 = SMBus mode selected 1 = I <sup>2</sup> C mode selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                |                                  |           | After reset, this signal indicates the SuperSpeed USB connection status of downstream port 2. A value of 1 indicates the connection is SuperSpeed USB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                |                                  |           | Power control polarity / SuperSpeed USB status for downstream port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                |                                  |           | The value of the terminal is sampled at the deassertion of reset to set the polarity of PWRCTL[2:1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PWRCTL_POL/SS_DN1              | 21                               | I/O<br>PD | 0 = PWRCTL polarity is active high. 1 = PWRCTL polarity is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                |                                  |           | After reset, this signal indicates the SuperSpeed USB connection status of downstream port 1. A value of 1 indicates the connection is SuperSpeed USB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                |                                  |           | Ganged operation enable/SMBus address bit 2/ high-speed status for upstream port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                |                                  |           | The value of the terminal is sampled at the deassertion of reset to set the power switch and over current detection mode as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

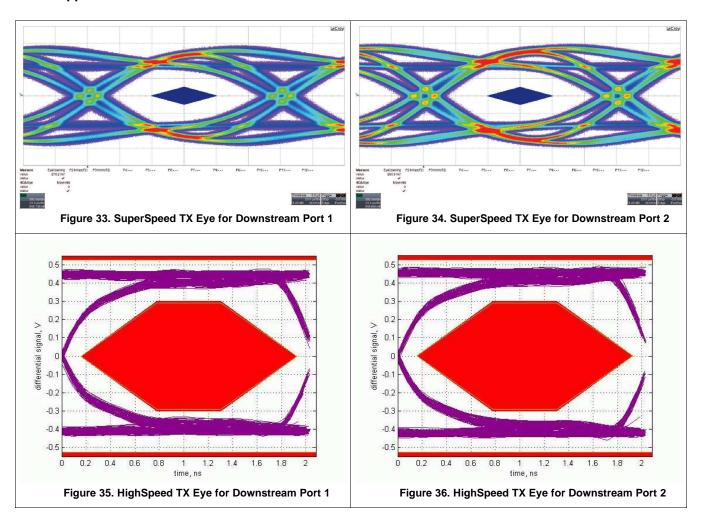

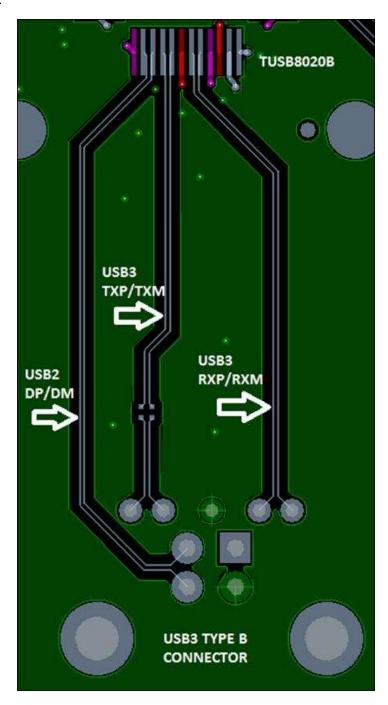

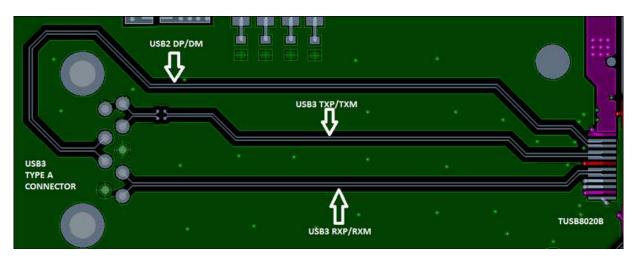

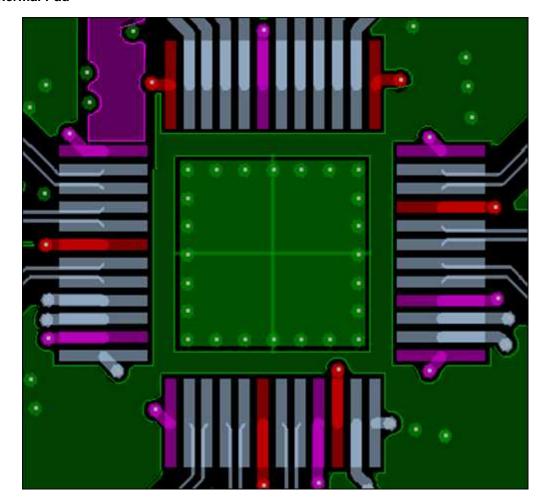

| GANGED/SMBA2/<br>HS_UP         | 35                               | I<br>PU   | <ul><li>0 = Individual power control supported when power switching is enabled.</li><li>1 = Power control gangs supported when power switching is enabled.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |