- Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of -55°C to 125°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product Change Notification

- Qualification Pedigree<sup>†</sup>

- High-Performance Floating-Point Digital Signal Processor (DSP) SM320C32-50EP (5 V)

- 40-ns Instruction Cycle Time

- 275 MOPS

- 50 MFLOPS

- 25 MIPS

SM320C32-60EP (5 V)

- 33-ns Instruction Cycle Time

- 330 MOPS

- 60 MFLOPS

- 30 MIPS

- 32-Bit High-Performance CPU

- 16-/32-Bit Integer and 32-/40-Bit Floating-Point Operations

- 32-Bit Instruction Word, 24-Bit Addresses

- Two 256 × 32-Bit Single-Cycle, Dual-Access On-Chip RAM Blocks

- Flexible Boot-Program Loader

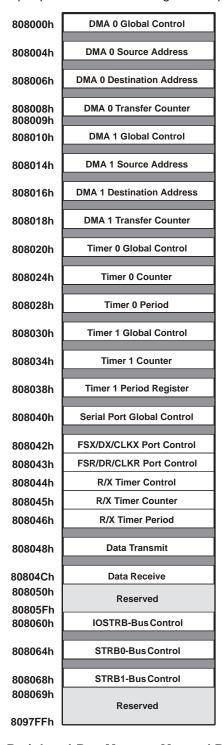

- On-Chip Memory-Mapped Peripherals:

- One Serial Port

- Two 32-Bit Timers

- Two-Channel Direct Memory Access (DMA) Coprocessor With Configurable Priorities

- Enhanced External Memory Interface That Supports 8-/16-/32-Bit-Wide External RAM for Data Access and Program Execution From 16-/32-Bit-Wide External RAM

- SMJ320C30 and SMJ320C31 Object Code Compatible

- Fabricated Using Enhanced Performance Implanted CMOS (EPIC™) Technology by Texas Instruments

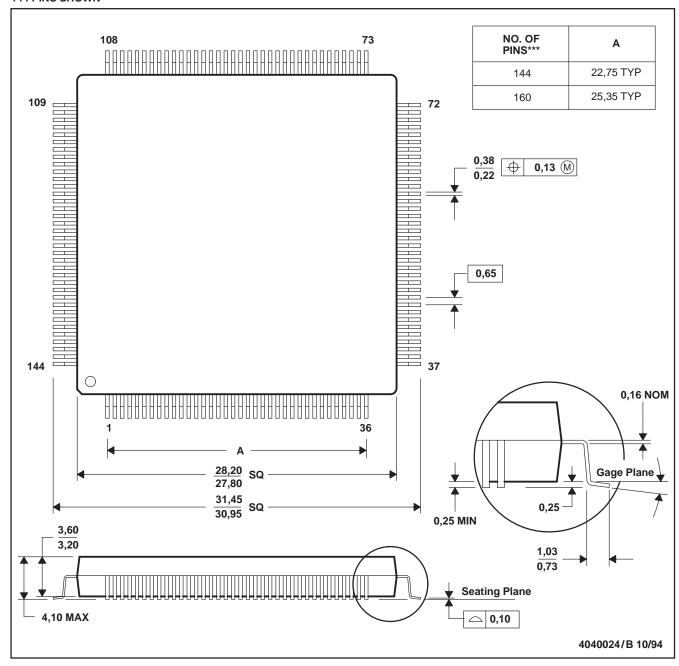

- 144-Pin Plastic Quad Flatpack (PCM Suffix) 5 V

- Eight Extended-Precision Registers

- Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Two Low-Power Modes

- Two- and Three-Operand Instructions

- Parallel Arithmetic Logic Unit (ALU) and Multiplier Execution in a Single Cycle

- Block-Repeat Capability

- Zero-Overhead Loops With Single-Cycle Branches

- Conditional Calls and Returns

- Interlocked Instructions for Multiprocessing Support

- One External Pin, PRGW, That Configures the External-Program-Memory Width to 16 or 32 Bits

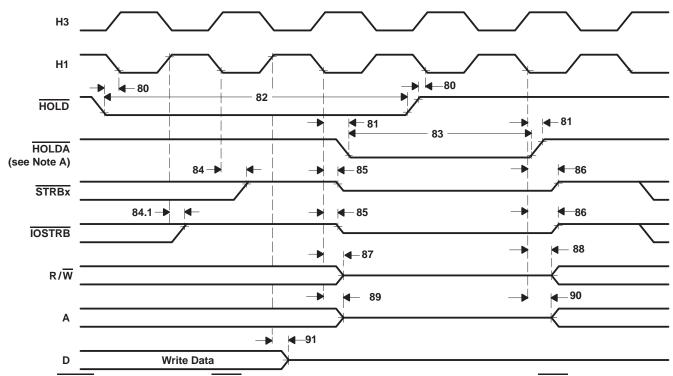

- Two Sets of Memory Strobes (STRB0 and STRB1) and One I/O Strobe (IOSTRB)

Allow Zero-Glue Logic Interface to Two Banks of Memory and One Bank of External Peripherals

- Separate Bus-Control Registers for Each Strobe-Control Wait-State Generation, External Memory Width, and Data Type Size

- STRB0 and STRB1 Memory Strobes Handle 8-, 16-, or 32-Bit External Data Accesses (Reads and Writes)

- Multiprocessor Support Through the HOLD and HOLDA Signals Is Valid for All Strobes

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

EPIC is a trademark of Texas Instruments Incorporated. All trademarks are the property of their respective owners

## SM320C32-EP DIGITAL SIGNAL PROCESSOR

SGUS038 - AUGUST 2002

## description

The SM320C32-EP is a member of the 320C3x generation of digital signal processors from Texas Instruments. The SM320C32-EP is an enhanced 32-bit floating-point processor manufactured in 0.7-µm triple-level-metal CMOS technology. The enhancements to the 320C3x architecture include a variable-width external-memory interface, faster instruction cycle time, power-down modes, two-channel DMA coprocessor with configurable priorities, flexible bootloader, relocatable interrupt-vector table, and edge- or level-triggered interrupts.

The internal busing and special digital signal processing instruction set of the SM320C32-EP have the speed and flexibility to execute up to 50 million floating-point operations per second (MFLOPS). The SM320C32-EP optimizes speed by implementing functions in hardware that other processors implement through software or microcode. This hardware-intensive approach provides performance previously unavailable on a single chip.

For additional information when designing for cold temperature operation, please see Texas Instruments application report 320C3x, 320C4x and 320MCM42x Power-up Sensitivity at Cold Temperature, literature number SGUA001.

#### part order information

| DEVICE           | TECHNOLOGY   | POWER<br>SUPPLY | OPERATING<br>FREQUENCY | PACKAGE TYPE                   | PROCESSING<br>LEVEL |

|------------------|--------------|-----------------|------------------------|--------------------------------|---------------------|

| SM320C32PCMM50EP | 0.65-μm CMOS | 5 V ± 5%        | 50 MHz                 | Plastic 144-lead quad flatpack | EP                  |

| SM320C32PCMM60EP | 0.65-μm CMOS | 5 V ± 5%        | 60 MHz                 | Plastic 144-lead quad flatpack | EP                  |

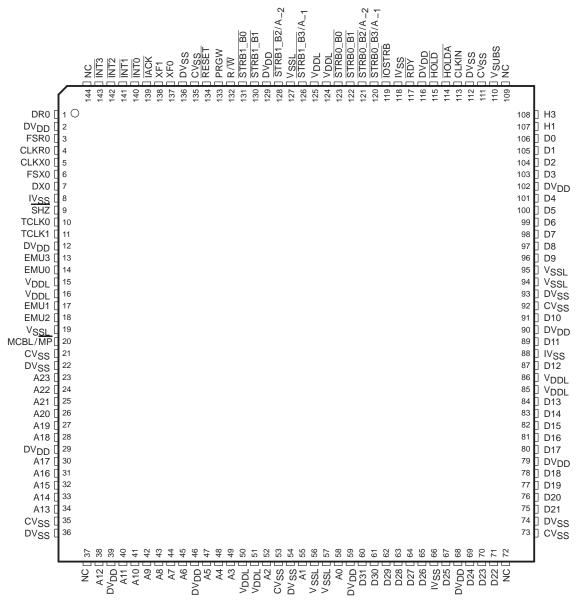

# PCM PACKAGE† (TOP VIEW)

† NC=No internal connection

## SM320C32-EP DIGITAL SIGNAL PROCESSOR

SGUS038 - AUGUST 2002

## **Pin Assignments**

|     | PIN              |

|-----|------------------|-----|------------------|-----|------------------|-----|------------------|-----|------------------|

| NO. | NAME             |

| 1   | DR0              | 30  | A17              | 59  | DV <sub>DD</sub> | 88  | IV <sub>SS</sub> | 117 | RDY              |

| 2   | DV <sub>DD</sub> | 31  | A16              | 60  | D31              | 89  | D11              | 118 | IV <sub>SS</sub> |

| 3   | FSR0             | 32  | A15              | 61  | D30              | 90  | $DV_DD$          | 119 | IOSTRB           |

| 4   | CLKR0            | 33  | A14              | 62  | D29              | 91  | D10              | 120 | STRB0_B3/A_1     |

| 5   | CLKX0            | 34  | A13              | 63  | D28              | 92  | CVSS             | 121 | STRB0_B2/A_2     |

| 6   | FSX0             | 35  | CVSS             | 64  | D27              | 93  | DVSS             | 122 | STRB0_B1         |

| 7   | DX0              | 36  | DV <sub>SS</sub> | 65  | D26              | 94  | VSSL             | 123 | STRB0_B0         |

| 8   | IV <sub>SS</sub> | 37  | NC               | 66  | IVSS             | 95  | VSSL             | 124 | $V_{DDL}$        |

| 9   | SHZ              | 38  | A12              | 67  | D25              | 96  | D9               | 125 | $V_{DDL}$        |

| 10  | TCLK0            | 39  | $DV_{DD}$        | 68  | $DV_{DD}$        | 97  | D8               | 126 | STRB1_B3/A_1     |

| 11  | TCLK1            | 40  | A11              | 69  | D24              | 98  | D7               | 127 | VSSL             |

| 12  | $DV_DD$          | 41  | A10              | 70  | D23              | 99  | D6               | 128 | STRB1_B2/A_2     |

| 13  | EMU3             | 42  | A9               | 71  | D22              | 100 | D5               | 129 | $DV_DD$          |

| 14  | EMU0             | 43  | A8               | 72  | NC               | 101 | D4               | 130 | STRB1_B1         |

| 15  | $V_{DDL}$        | 44  | A7               | 73  | CVSS             | 102 | $DV_DD$          | 131 | STRB1_B0         |

| 16  | $V_{DDL}$        | 45  | A6               | 74  | DVSS             | 103 | D3               | 132 | $R/\overline{W}$ |

| 17  | EMU1             | 46  | $DV_{DD}$        | 75  | D21              | 104 | D2               | 133 | PRGW             |

| 18  | EMU2             | 47  | A5               | 76  | D20              | 105 | D1               | 134 | RESET            |

| 19  | VSSL             | 48  | A4               | 77  | D19              | 106 | D0               | 135 | CV <sub>SS</sub> |

| 20  | MCBL/MP          | 49  | A3               | 78  | D18              | 107 | H1               | 136 | DV <sub>SS</sub> |

| 21  | CV <sub>SS</sub> | 50  | $V_{DDL}$        | 79  | $DV_DD$          | 108 | H3               | 137 | XF0              |

| 22  | DVSS             | 51  | $V_{DDL}$        | 80  | D17              | 109 | NC               | 138 | XF1              |

| 23  | A23              | 52  | A2               | 81  | D16              | 110 | VSUBS            | 139 | IACK             |

| 24  | A22              | 53  | CVSS             | 82  | D15              | 111 | CVSS             | 140 | INT0             |

| 25  | A21              | 54  | DVSS             | 83  | D14              | 112 | DVSS             | 141 | INT1             |

| 26  | A20              | 55  | A1               | 84  | D13              | 113 | CLKIN            | 142 | INT2             |

| 27  | A19              | 56  | $V_{SSL}$        | 85  | $V_{DDL}$        | 114 | HOLDA            | 143 | ĪNT3             |

| 28  | A18              | 57  | $V_{SSL}$        | 86  | $V_{DDL}$        | 115 | HOLD             | 144 | NC               |

| 29  | $DV_DD$          | 58  | A0               | 87  | D12              | 116 | $DV_DD$          |     |                  |

## pin functions

This section provides signal descriptions for the SM320C32-EP device. The following table lists each signal (grouped by function), the number of pins, operating modes, and a brief signal description.

#### **Pin Functions**

| PIN<br>NAME NO. |    | TYPE† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SI | NDITION NOTES NOTE | l<br>IS |

|-----------------|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                 |    | •     | EXTERNAL BUS INTERFACE (70 PINS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| D31-D0          | 32 | I/O/Z | 32-bit data port of the external bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R       |

| A23-A0          | 24 | O/Z   | 24-bit address port of the external bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R       |

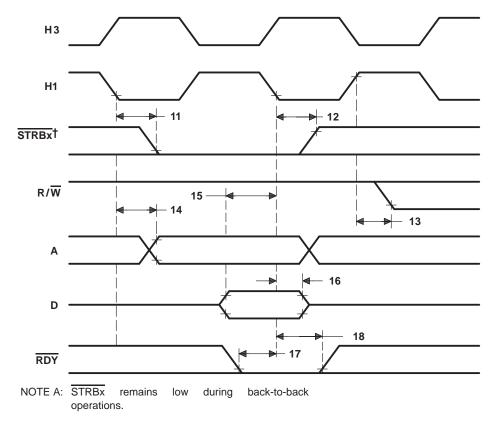

| R/W             | 1  | O/Z   | Read/write for external memory interface. $R/\overline{W}$ is high when a read is performed and low when a write is performed over the parallel interface.                                                                                                                                                                                                                                                                                                                                              | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R       |

| IOSTRB          | 1  | O/Z   | External peripheral I/O strobe for the external memory interface                                                                                                                                                                                                                                                                                                                                                                                                                                        | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB0_B3/A_1    | 1  | O/Z   | External memory-access strobe 0, byte enable 3 for 32-bit external memory interface and address pin for 8-bit and 16-bit external memory interface                                                                                                                                                                                                                                                                                                                                                      | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB0_B2/A_2    | 1  | O/Z   | External memory-access strobe 0, byte enable 2 for 32-bit external memory interface and address pin for 8-bit external memory interface                                                                                                                                                                                                                                                                                                                                                                 | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB0_B1        | 1  | O/Z   | External memory-access strobe 0, byte enable 1 for the external memory interface                                                                                                                                                                                                                                                                                                                                                                                                                        | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB0_B0        | 1  | O/Z   | External memory-access strobe 0, byte enable 0 for the external memory interface                                                                                                                                                                                                                                                                                                                                                                                                                        | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB1_B3/A_1    | 1  | O/Z   | External memory-access strobe 1, byte enable 3 for 32-bit external memory interface and address pin for 8-bit and 16-bit external memory interface                                                                                                                                                                                                                                                                                                                                                      | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB1_B2/A_2    | 1  | O/Z   | External memory-access strobe 1, byte enable 2 for 32-bit external memory interface and address pin for 8-bit external memory interface                                                                                                                                                                                                                                                                                                                                                                 | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB1_B1        | 1  | O/Z   | External memory-access strobe 1, byte enable 1 for the external memory interface                                                                                                                                                                                                                                                                                                                                                                                                                        | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| STRB1_B0        | 1  | O/Z   | External memory-access strobe 1, byte enable 0 for the external memory interface                                                                                                                                                                                                                                                                                                                                                                                                                        | S  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| RDY             | 1  | I     | Ready. RDY indicates that the external device is prepared for an external memory interface transaction to complete.                                                                                                                                                                                                                                                                                                                                                                                     |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| HOLD            | 1  | I     | Hold signal for external memory interface. When $\overline{\text{HOLD}}$ is a logic low, any ongoing transaction is completed. A23 – A0, D31 – D0, $\overline{\text{IOSTRB}}$ , $\overline{\text{STRB0}}$ Bx, $\overline{\text{STRB1}}$ Bx, and $\overline{\text{R}/\text{W}}$ are placed in the high-impedance state, and all transactions over the external memory interface are held until $\overline{\text{HOLD}}$ becomes a logic high or the NOHOLD bit of the STRB0 bus-control register is set. |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| HOLDA           | 1  | O/Z   | Hold acknowledge for external memory interface. HOLDA is generated in response to a logic low on HOLD. HOLDA indicates that A23 – A0, D31 – D0, IOSTRB, STRB0_Bx, STRB1_Bx, and R/W are in the high-impedance state and that all transactions over the memory are held. HOLDA is high in response to a logic high of HOLD or when the NOHOLD bit of the external bus-control register is set.                                                                                                           | S  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| PRGW            | 1  | ı     | Program memory width select. When PRGW is a logic low, program is fetched as a single 32-bit word. When PRGW is a logic high, two 16-bit program fetches are performed to fetch a single 32-bit instruction word. The status of PRGW at device reset affects the reset value of the STRB0 and STRB1 bus-control register.                                                                                                                                                                               |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

<sup>§</sup> Recommended decoupling capacitor is 0.1 μF.

<sup>†</sup> I = input, O = output, Z = high-impedance state ‡ S =  $\overline{SHZ}$  active, H =  $\overline{HOLD}$  active, R =  $\overline{RESET}$  active

## **Pin Functions (Continued)**

|                                      |                                                                                                                |       |                                                                                                                                                                                                                                                                                                                                                                                                                       | CONDITIONS              |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| PIN                                  |                                                                                                                | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                           | WHEN                    |  |  |  |  |

| NAME                                 | NO.                                                                                                            |       |                                                                                                                                                                                                                                                                                                                                                                                                                       | SIGNAL IS<br>IN HIGH Z‡ |  |  |  |  |

|                                      |                                                                                                                | •     | CONTROL SIGNALS (9 PINS)                                                                                                                                                                                                                                                                                                                                                                                              |                         |  |  |  |  |

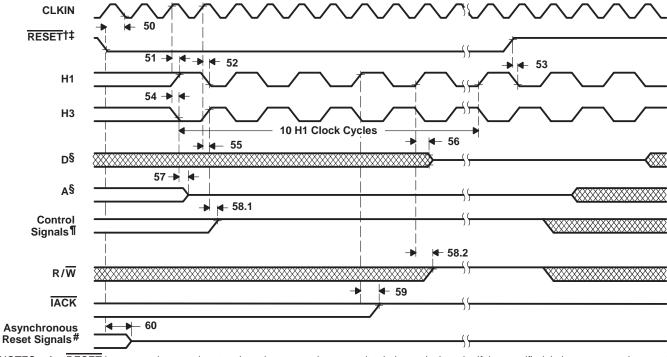

| RESET                                | 1                                                                                                              | ı     | Reset. When RESET is a logic low, the device is in the reset condition. When RESET becomes a logic high, execution begins from the location specified by the reset vector.                                                                                                                                                                                                                                            |                         |  |  |  |  |

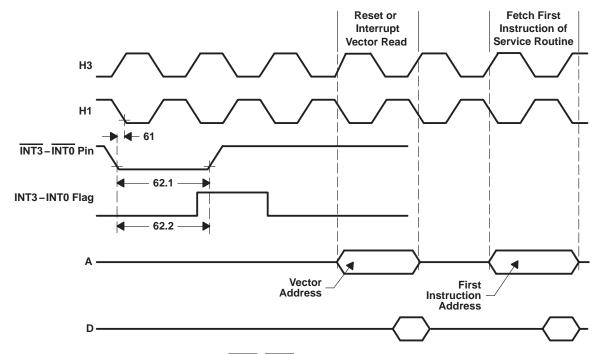

| INT3-INT0                            | 4                                                                                                              | I     | External interrupts                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| CONTROL SIGNALS (9 PINS) (CONTINUED) |                                                                                                                |       |                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

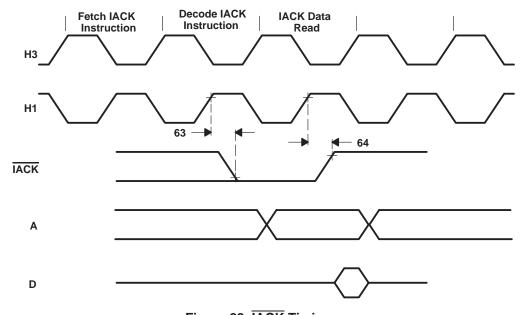

| ĪACK                                 | 1                                                                                                              | O/Z   | Interrupt acknowledge. IACK is set to a logic high by the IACK instruction. This signal can be used to indicate the beginning or end of an interrupt-service routine.                                                                                                                                                                                                                                                 | S                       |  |  |  |  |

| MCBL/MP                              | 1                                                                                                              | I     | Microcomputer bootloader/microprocessor mode                                                                                                                                                                                                                                                                                                                                                                          |                         |  |  |  |  |

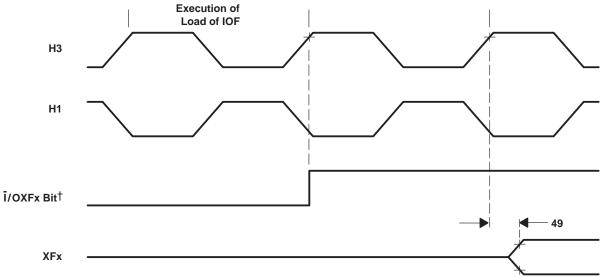

|                                      |                                                                                                                | I/O/Z | External flags. XF1 and XF0 are used as general-purpose I/Os or used to support interlocked-processor instructions.                                                                                                                                                                                                                                                                                                   | S R                     |  |  |  |  |

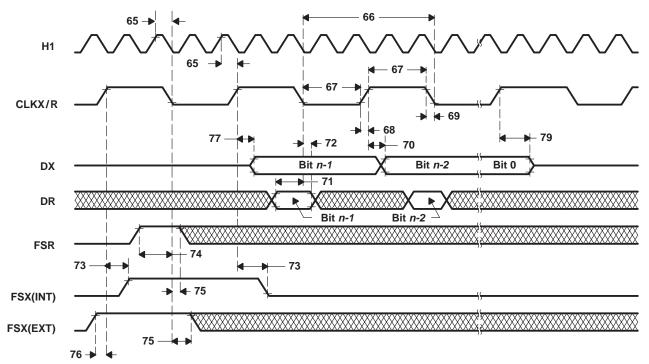

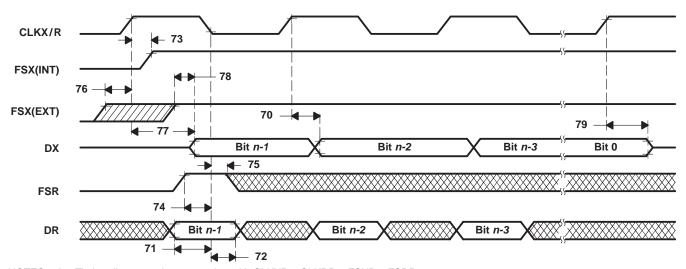

|                                      | •                                                                                                              |       | SERIAL PORT SIGNALS (6 PINS)                                                                                                                                                                                                                                                                                                                                                                                          |                         |  |  |  |  |

| CLKX0                                | 1                                                                                                              | I/O/Z | Serial port 0 transmit clock. CLKX0 is the serial shift clock for the serial port 0 transmitter.                                                                                                                                                                                                                                                                                                                      | S R                     |  |  |  |  |

| DX0                                  | 1 I/O/Z Data transmit output. Serial port 0 transmits serial data on DX0.                                      |       | S R                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| FSX0                                 | 1 I/O/Z Frame-synchronization pulse for transmit. The FSX0 pulse initiates the transmit-data process over DX0. |       | S R                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| CLKR0                                | 1                                                                                                              | I/O/Z | Serial port 0 receive clock. CLKR0 is the serial shift clock for the serial port 0 receiver.                                                                                                                                                                                                                                                                                                                          | S R                     |  |  |  |  |

| DR0                                  | 1                                                                                                              | I/O/Z | Data receive. Serial port 0 receives serial data on DR0.                                                                                                                                                                                                                                                                                                                                                              | S R                     |  |  |  |  |

| FSR0                                 | 1                                                                                                              | I/O/Z | Frame-synchronization pulse for receive. The FSR0 pulse initiates the receive-data process over DR0.                                                                                                                                                                                                                                                                                                                  | S R                     |  |  |  |  |

|                                      |                                                                                                                |       | TIMER SIGNALS (2 PINS)                                                                                                                                                                                                                                                                                                                                                                                                |                         |  |  |  |  |

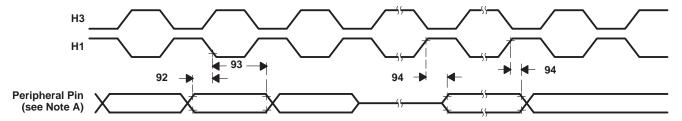

| TCLK0                                | 1                                                                                                              | I/O/Z | Timer clock 0. As an input, TCLK0 is used by timer 0 to count external pulses. As an output, TCLK0 outputs pulses generated by timer 0.                                                                                                                                                                                                                                                                               | S R                     |  |  |  |  |

| TCLK1                                | 1                                                                                                              | I/O/Z | Timer clock 1. As an input, TCLK1 is used by timer 1 to count external pulses. As an output, TCLK1 outputs pulses generated by timer 1.                                                                                                                                                                                                                                                                               | S R                     |  |  |  |  |

|                                      |                                                                                                                |       | CLOCK SIGNALS (3 PINS)                                                                                                                                                                                                                                                                                                                                                                                                |                         |  |  |  |  |

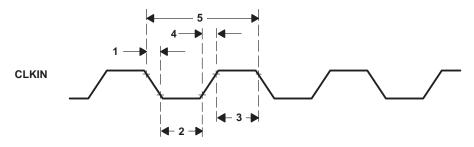

| CLKIN                                | 1                                                                                                              | - 1   | Input to the internal oscillator from an external clock source                                                                                                                                                                                                                                                                                                                                                        |                         |  |  |  |  |

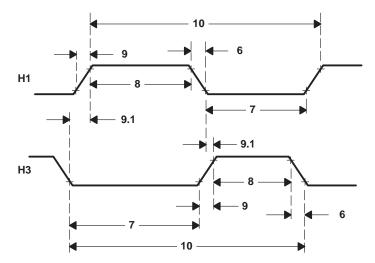

| H1                                   | 1                                                                                                              | O/Z   | External H1 clock. H1 has a period equal to twice CLKIN.                                                                                                                                                                                                                                                                                                                                                              | S                       |  |  |  |  |

| H3                                   | 1                                                                                                              | O/Z   | External H3 clock. H3 has a period equal to twice CLKIN.                                                                                                                                                                                                                                                                                                                                                              | S                       |  |  |  |  |

|                                      | _                                                                                                              |       | RESERVED (5 PINS)                                                                                                                                                                                                                                                                                                                                                                                                     |                         |  |  |  |  |

| EMU0-EMU2                            |                                                                                                                |       |                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

| EMU3                                 | 1                                                                                                              | O/Z   | Reserved for emulation                                                                                                                                                                                                                                                                                                                                                                                                | S                       |  |  |  |  |

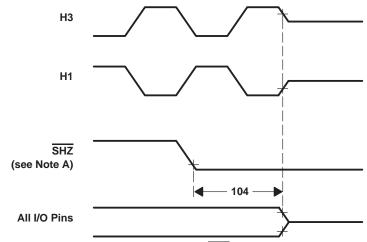

| SHZ 1 I                              |                                                                                                                | I     | Shutdown high impedance. When active, $\overline{SHZ}$ shuts down the C32 and places all 3-state I/O pins in the high-impedance state. $\overline{SHZ}$ is used for board-level testing to ensure that no dual drive conditions occur. <b>CAUTION:</b> A low on $\overline{SHZ}$ corrupts C32 memory and register contents. Reset the device with $\overline{SHZ}$ high to restore it to a known operating condition. |                         |  |  |  |  |

<sup>†</sup> I = input, O = output,  $\underline{Z}$  = high-impedance state ‡ S = SHZ active, H = HOLD active, R = RESET active § Recommended decoupling capacitor is 0.1  $\mu$ F.

## Pin Functions (Continued)

| PIN              | PIN TYPET DESCRIPTION |   | CONDITIONS<br>WHEN        |                         |

|------------------|-----------------------|---|---------------------------|-------------------------|

| NAME             | NO.                   |   |                           | SIGNAL IS<br>IN HIGH Z‡ |

|                  |                       | _ | POWER/GROUND              |                         |

| CVSS             | 7                     | I | Ground                    |                         |

| DV <sub>SS</sub> | 7                     | I | Ground                    |                         |

| IV <sub>SS</sub> | 4                     | I | Ground                    |                         |

| $DV_{DD}$        | 12                    | I | 5 V <sub>dc</sub> supply§ |                         |

| $V_{DDL}$        | 8                     | I | 5 V <sub>dc</sub> supply§ |                         |

| VSSL             | 6                     | I | Ground                    |                         |

| VSUBS            | 1                     | I | Substrate, tie to ground  |                         |

<sup>†</sup> I = input, O = output, Z = high-impedance state ‡ S = SHZ active, H = HOLD active, R = RESET active § Recommended decoupling capacitor is 0.1 μF.

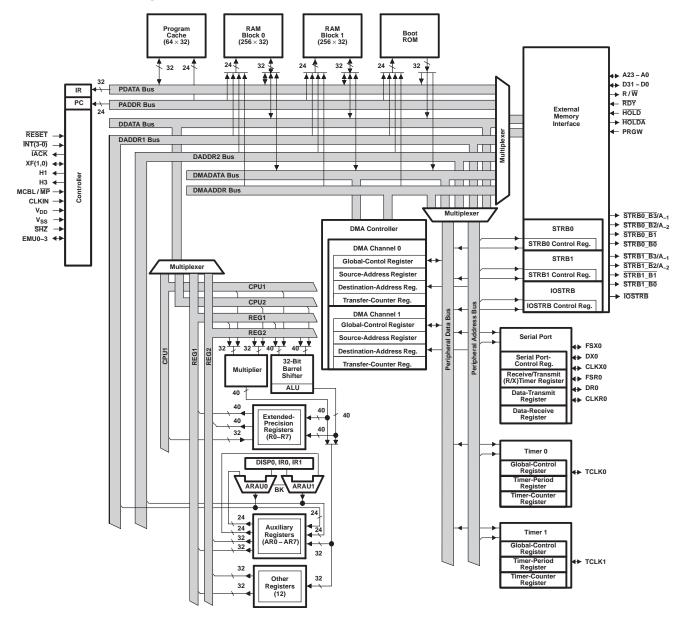

## functional block diagram

#### operation

Operation of the SM320C32-EP is identical to the 320C30 and 320C31 digital signal processors, with the exception of an enhanced external memory interface and the addition of two CPU power-management modes.

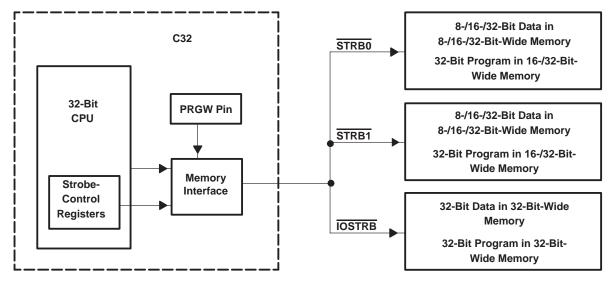

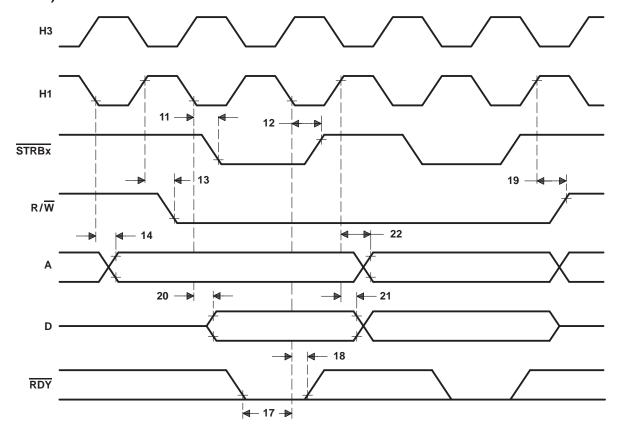

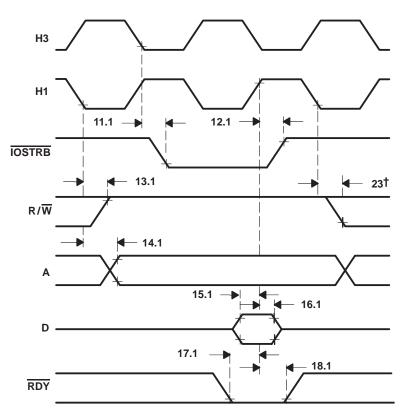

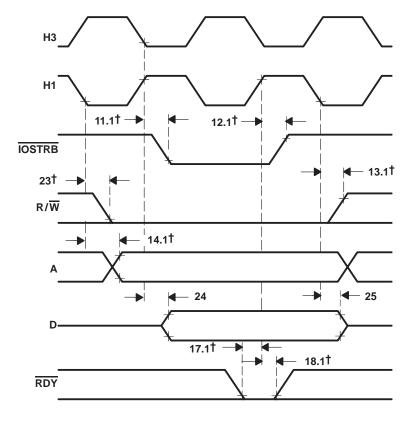

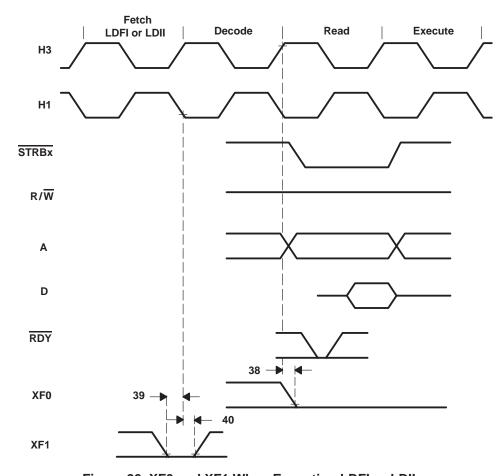

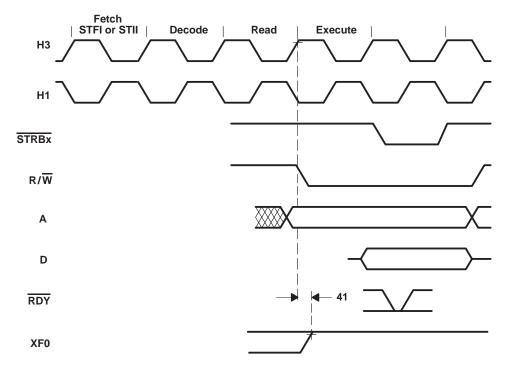

## external memory interface

The SM320C32-EP has a configurable external memory interface with a 24-bit address bus, a 32-bit data bus, and three independent multi-function strobes. The flexibility of this unique interface enables product designers to minimize external memory-chip count.

#### external memory interface (continued)

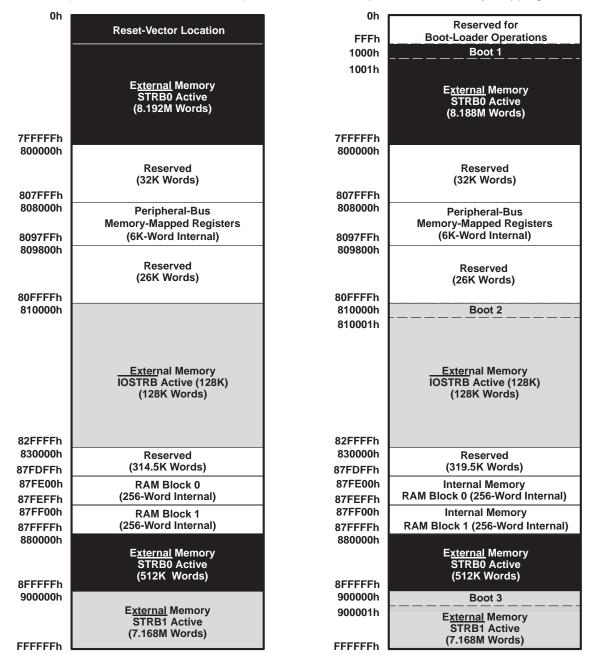

Up to three mutually exclusive memory areas—one program area and two data areas—can be implemented. Each memory area configuration is independent of the physical memory width and independent of the other memory areas configurations. See Figure 1.

Figure 1. C32 External Memory Interface

The SM320C32-EP external memory configuration is controlled by a combination of hardware configuration and memory-mapped control registers and can be reconfigured dynamically. The signals that control external memory configuration are the PRGW, STRB0, STRB1, and IOSTRB. The signals work as follows:

- The SM320C32-EP is a 32-bit microprocessor, that is, the CPU operates on 32-bit program words. The

external memory interface provides the capability of fetching instructions as either 32-bit words or two 16-bit

half words from consecutive addresses. Program memory width is 16 bits if the PRGW signal is high,

32 bits if the PRGW signal is low.

- STRB0 and STRB1 are sets of control signals, four signals each, that are mapped to specific ranges of

external memory addresses. When an address within one of these ranges is accessed by a read or write

instruction (CPU or DMA), the corresponding set of control signals is activated. Figure 8 illustrates the

SM320C32-EP memory map, showing the address ranges for which the strobe signals become active.

The behavior of the STRB0 and STRB1 control signals is determined by the contents of the STRB0 and STRB1 control registers.

The STRBO and STRB1 control registers each have a field that specifies the physical memory width (8, 16, or 32 bits) of the external memory address ranges they control. Another field specifies the data width (8, 16, or 32 bits) of the data contained in those addresses. The values in these fields are not required to match. For example, a 32-bit-wide physical memory space can be configured to segment each 32-bit word into four consecutive 8-bit locations, each having its own address.

Each control signal set has two pins (STRBx\_B2/A\_2 and STRBx\_B3/A\_1) that can act as either byte-enable (chip-select) pins or address pins, and two dedicated byte-enable (chip-select) pins (STRBx\_B0 and STRBx\_B1). The pin functions are determined by the physical memory width specified in the corresponding control register:

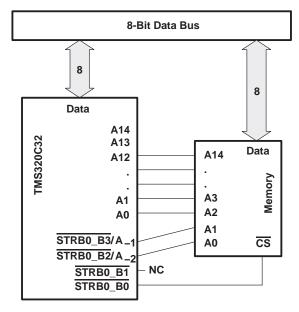

#### external memory interface (continued)

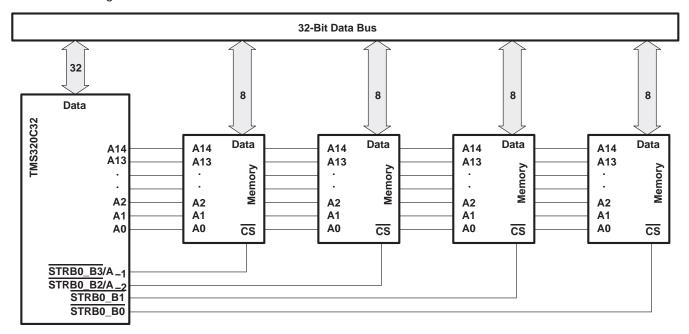

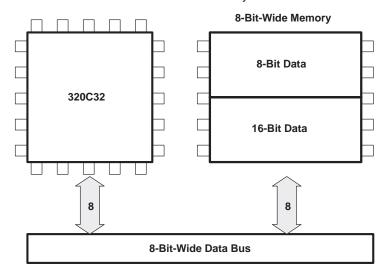

• For 8-bit-wide physical memory, the \$\overline{\subseteq} \overline{\subseteq} \overline{\s

Figure 2. C32 With 8-Bit-Wide External Memory

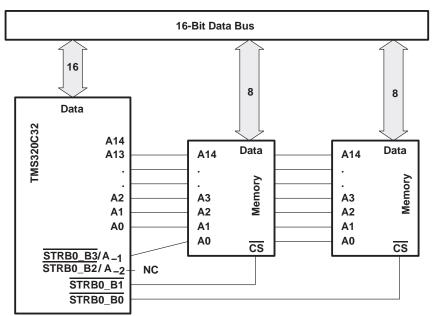

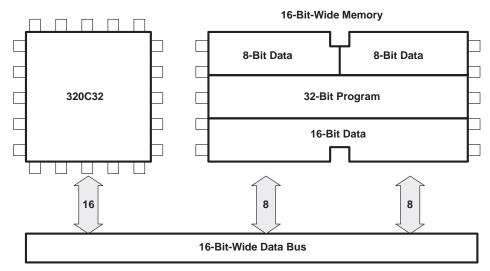

• For 16-bit-wide physical memory, the \$\overline{STRBx\_B3}/A\_1\$ pin functions as an address pin (least significant address bits). The \$\overline{STRBx\_B0}\$ and \$\overline{STRBx\_B1}\$ pins function as byte-enable (chip-select) pins. \$\overline{STRBx\_B2}/A\_2\$ is unused. See Figure 3.