# TPS1210-Q1 45V, Automotive Low Io, Back-to-Back MOSFET Smart High Side Driver With Short-Circuit Protection and Diagnostics

### 1 Features

- AEC-Q100 automotive qualified for automotive applications

- Device temperature grade 1: –40°C to +125°C ambient operating temperature range

- **Functional Safety-Capable**

- Documentation available to aid functional safety system design

- 3.5V to 40V input range (45V absolute maximum)

- Reverse input protection down to -40V

- Integrated 11V charge pump

- Low quiescent current, 35µA in operation

- Low 1.5µA shutdown current (EN/UVLO = Low)

- Two strong gate drivers (2A src/sink) for back-toback MOSFET driving with separate control inputs (INP1, INP2)

- Variants with active high (TPS12100-Q1) and active low (TPS12101-Q1) inputs

- Adjustable short-circuit protection (ISCP) using external Rsense or MOSFET VDS sensing with adjustable delay (TMR)

- High or low-side current sense configuration (CS SEL)

- Fault indication (FLT) during short-circuit fault, charge pump under voltage, input undervoltage, and short-circuit comparator diagnosis (SCP\_TEST)

- Adjustable input undervoltage lockout (UVLO)

# 2 Applications

- Automotive 12V BMS

- DC/DC converter

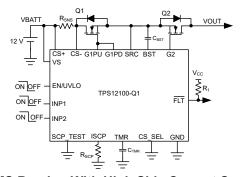

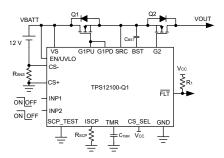

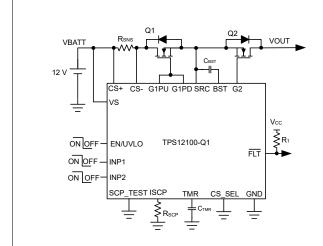

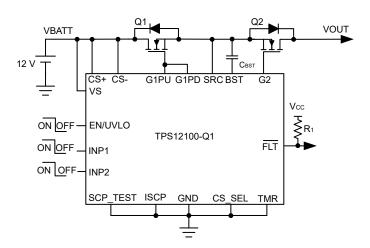

**BMS Breaker With High Side Current Sense**

# 3 Description

The TPS1210x-Q1 family is a 45V, low I<sub>O</sub>, smart high side driver with protection and diagnostics. With wide operating voltage range of 3.5V-40V, the device is designed for 12V system designs. The device can withstand and protect the loads from negative supply voltages down to -40V.

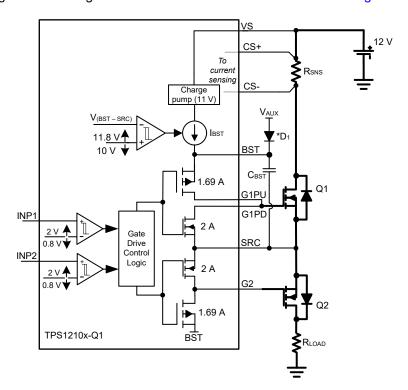

The device has two strong (2A) GATE drivers with separate control inputs (INP1, INP2) to drive backto-back MOSFETs in common source configuration. TPS12100-Q1 has active high control inputs and TPS12101-Q1 has active low control inputs.

provides adjustable device short-circuit protection. Auto-retry and latch-off fault behavior can be configured. Current sensing can be done either by an external sense resistor or by MOSFET VDS sensing. High side or low side current sense resistor configuration is possible by using CS SEL pin input. The device also features diagnosis of the internal short circuit comparator using external control on SCP TEST input.

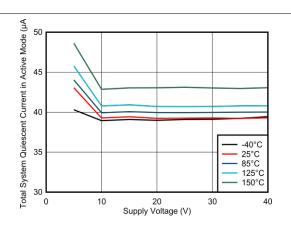

Low Quiescent current 35µA (typical) in operation enables always ON system designs. Quiescent current reduces to 1.5µA (typical) with EN/UVLO low.

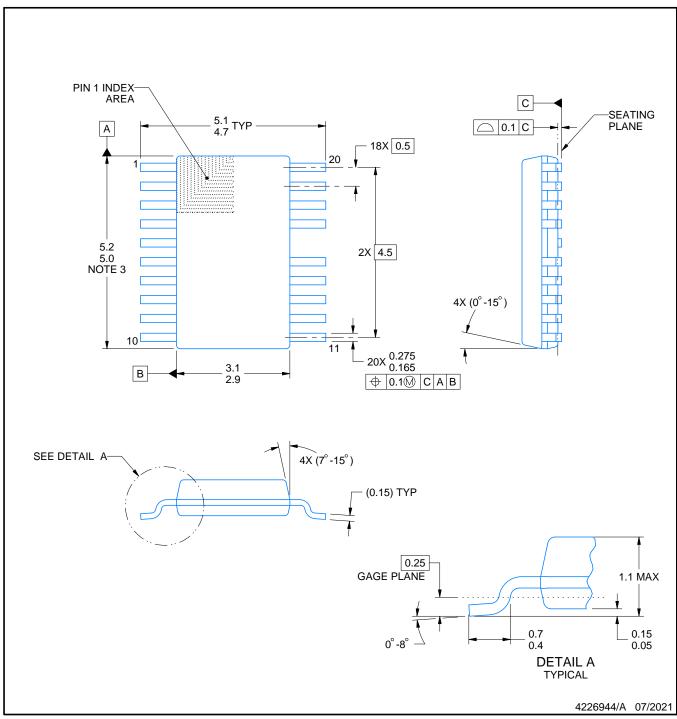

The TPS1210x-Q1 is available in a 19-pin VSSOP package.

### **Package Information**

| PART NUMBER                                | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|--------------------------------------------|------------------------|-----------------------------|

| TPS12100-Q1,<br>TPS12101-Q1 <sup>(3)</sup> | DGX (VSSOP, 19)        | 5.1mm × 3.0mm               |

- For all available packages, see Section 12.

- The package size (length × width) is a nominal value and (2)includes pins, where applicable.

- Product preview.

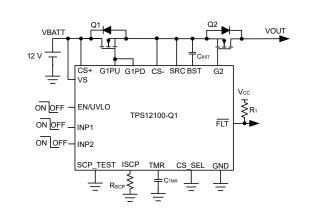

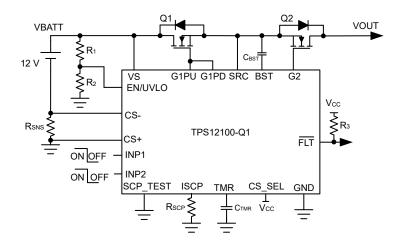

**BMS Breaker With Low Side Current Sense**

# **Table of Contents**

| 1 Features1                           | 8.4 Device F  |

|---------------------------------------|---------------|

| 2 Applications1                       | 9 Application |

| 3 Description1                        | 9.1 Applicat  |

| 4 Device Comparison3                  | 9.2 Typical / |

| 5 Pin Configuration and Functions3    | Managem       |

| 6 Specifications5                     | Current S     |

| 6.1 Absolute Maximum Ratings5         | 9.3 Power S   |

| 6.2 ESD Ratings5                      | 9.4 Layout    |

| 6.3 Recommended Operating Conditions5 | 10 Device and |

| 6.4 Thermal Information6              | 10.1 Receiv   |

| 6.5 Electrical Characteristics6       | 10.2 Suppor   |

| 6.6 Switching Characteristics7        | 10.3 Traden   |

| 6.7 Typical Characteristics8          | 10.4 Electro  |

| 7 Parameter Measurement Information10 | 10.5 Glossa   |

| 8 Detailed Description11              | 11 Revision F |

| 8.1 Overview11                        | 12 Mechanica  |

| 8.2 Functional Block Diagram11        | Information   |

| 8.3 Feature Description 12            |               |

| 8.4 Device Functional Modes                          | .19 |

|------------------------------------------------------|-----|

| Application and Implementation                       | 20  |

| 9.1 Application Information                          | 20  |

| 9.2 Typical Application: Circuit Breaker in Battery  |     |

| Management System (BMS) using Low Side               |     |

| Current Sense                                        | 20  |

| 9.3 Power Supply Recommendations                     | 25  |

| 9.4 Layout                                           | 26  |

| 0 Device and Documentation Support                   | .28 |

| 10.1 Receiving Notification of Documentation Updates | 28  |

| 10.2 Support Resources                               | 28  |

| 10.3 Trademarks                                      | 28  |

| 10.4 Electrostatic Discharge Caution                 | 28  |

| 10.5 Glossary                                        | 28  |

| 1 Revision History                                   | 28  |

| 2 Mechanical, Packaging, and Orderable               |     |

| Information                                          | 28  |

|                                                      |     |

# **4 Device Comparison**

|                             | TPS12100-Q1       | TPS12101-Q1      |

|-----------------------------|-------------------|------------------|

| Input controls (INP1, INP2) | Active High logic | Active Low logic |

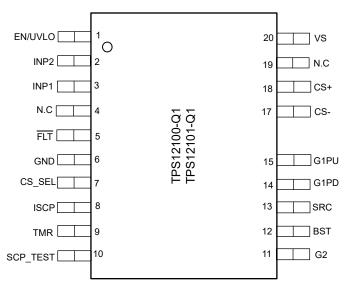

# **5 Pin Configuration and Functions**

Figure 5-1. DGX Package, 19-Pin VSSOP (Top View)

**Table 5-1. Pin Functions**

|         | PIN | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | ITPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EN/UVLO | 1   | I       | EN/UVLO Input. A voltage on this pin above 1.21V enables normal operation. Forcing this pin below 0.3V shuts down the device reducing quiescent current to approximately 1.6µA (typical). Optionally connect to the input supply through a resistive divider to set the undervoltage lockout.  When EN/UVLO is left floating an internal pull down of 100nA pulls EN/UVLO low and keeps the device in shutdown state.               |

| INP2    | 2   | I       | Input Signal for external charge FET control. In TPS12100-Q1 drive INP2 high to drive G2 high. Drive INP2 low to pull G2 low.  INP2 has an internal weak 100nA pulldown to GND to keep G2 pulled low to SRC when INP2 is left floating.  In TPS12101-Q1 drive INP2 low to drive G2 high. Drive INP2 high to pull G2 low.  INP2 has an internal weak pulldown of 100nA to GND to keep G2 high when INP2 is left floating.            |

| INP1    | 3   | I       | Input Signal for external charge FET control. In TPS12100-Q1 drive INP1 high to drive G1PU high. Drive INP1 low to pull G1PD low. INP1 has an internal weak pulldown of 100nA to GND to keep G1PD pulled to SRC when INP1 is left floating.  In TPS12101-Q1, drive INP1 low to drive G1PU high. Drive INP1 high to pull G1PD low. INP1 has an internal weak pull down of 100nA to GND to keep G1PU high when INP1 is left floating. |

| N.C     | 4   | _       | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FLT     | 5   | 0       | Open Drain Fault Output. This pin asserts low during short-circuit fault, charge pump UVLO, input UVLO and during SCP comparator diagnosis. If FLT feature is not desired then connect it to GND.                                                                                                                                                                                                                                   |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

# **Table 5-1. Pin Functions (continued)**

| PIN |                                          |                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | TYPE <sup>(1)</sup>                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |

| 6   | G                                        | Connect GND to system ground.                                                                                                                                                                                                                                                                                                                                          |

| 7   | I                                        | Current sense select input. Connect this pin to ground to activate high side current sense. Drive this pin to >2V to activate low side current sensing. CS_SEL has an internal weak pull down of 100nA to GND.                                                                                                                                                         |

| 8   | I                                        | Short-circuit detection setting. A resistor across ISCP to GND sets the short circuit current comparator threshold.  If short-circuit protection feature is not desired then connect CS+, CS-, VS pins together and connect ISCP, TMR pins to GND.                                                                                                                     |

| 9   | I                                        | Fault Timer Input. A capacitor across TMR pin to GND sets the delay time for short-circuit fault turn-off.  Leave this pin open for fastest response setting. If short-circuit protection feature is not desired then connect CS+, CS-, VS pins together and connect ISCP, TMR pins to GND.                                                                            |

| 10  | ı                                        | Internal short-circuit comparator (SCP) diagnosis input.  When SCP_TEST is driven low to high with INP1 pulled high, the internal SCP comparator operation is checked. FLT goes low and G1PD gets pulled to SRC if SCP comparator is functional.  Connect SCP_TEST pin to GND if this feature is not desired.  SCP_TEST has an internal weak pulldown of 100nA to GND. |

| 11  | 0                                        | Charging FET gate drive output. This pin has 1.69A peak source and 2A sink capacity. Leave the G2 pin floating if the G2 drive functionality is unused.                                                                                                                                                                                                                |

| 12  | 0                                        | High Side Bootstrapped Supply. An external capacitor with a minimum value of > $Q_{g(tot)}$ of the external FET must be connected between this pin and SRC.                                                                                                                                                                                                            |

| 13  | 0                                        | Source connection of the external FET.                                                                                                                                                                                                                                                                                                                                 |

| 14  | 0                                        | High Current Gate Driver Pull-Down. This pin pulls down to SRC. For the fastest turn-off, tie this pin directly to the gate of the external high side MOSFET.                                                                                                                                                                                                          |

| 15  | 0                                        | High Current Gate Driver Pull-Up. This pin pulls up to BST. Connect this pin to G1PD for maximum gate drive transition speed. A resistor can be connected between this pin and the gate of the external MOSFET to control the in-rush current during turn-on.                                                                                                          |

| 17  | I                                        | Current sense negative input.                                                                                                                                                                                                                                                                                                                                          |

| 18  | I                                        | Current sense positive input.                                                                                                                                                                                                                                                                                                                                          |

| 19  | _                                        | No connect.                                                                                                                                                                                                                                                                                                                                                            |

| 20  | Р                                        | Supply pin of the controller.                                                                                                                                                                                                                                                                                                                                          |

|     | NO. 6 7 8 8 9 10 11 12 13 14 15 17 18 19 | PIN NO. 6 G 7 I 8 I 9 I 11 O 12 O 13 O 14 O 15 O 17 I 18 I 19 —                                                                                                                                                                                                                                                                                                        |

<sup>(1)</sup> I = input, O = output, I/O = input and output, P = power, G = ground

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                               |                                                      | MIN               | MAX               | UNIT |  |

|---------------------------------------------------------------|------------------------------------------------------|-------------------|-------------------|------|--|

| Input Pins                                                    | VS, CS+, CS- to GND                                  | -40               | 45                |      |  |

|                                                               | SRC to GND                                           | -40               | 45                |      |  |

|                                                               | G1PU, G1PD, G2, BST to SRC                           | -0.3              | 19                | V    |  |

|                                                               | ISCP, TMR, SCP_TEST to GND                           | -0.3              | 5.5               | V    |  |

|                                                               | EN/UVLO, INP1, INP2, CS_SEL, V <sub>(VS)</sub> > 0 V | -1                | 45                |      |  |

|                                                               | EN/UVLO, INP1, INP2, CS_SEL, V <sub>(VS)</sub> ≤ 0 V | V <sub>(VS)</sub> | $(40 + V_{(VS)})$ |      |  |

|                                                               | CS+ to CS-                                           | -1                | 45                | V    |  |

|                                                               | FLT to GND                                           | -1                | 20                | V    |  |

| Cink ourrant                                                  | I <sub>(FLT)</sub>                                   |                   | 10                | mA   |  |

| Sink current                                                  | I <sub>(CS+)</sub> , I <sub>(CS-)</sub> , 1msec      | -100              | 100               | mA   |  |

| Output Pins G1PU, G1PD, G2, BST to GND                        |                                                      | -40               | 60                | V    |  |

| Operating junction temperature, T <sub>j</sub> <sup>(2)</sup> |                                                      | -40               | 150               | °C   |  |

| Storage temperature,                                          | $T_{stg}$                                            | -55               | 150               | C    |  |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                                            |                                                 |                                         |                         | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------|-----------------------------------------|-------------------------|-------|------|

|                                            |                                                 | Human body model (HBM), per AEC         | Q100-002 <sup>(1)</sup> | ±2000 |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per<br>AEC Q100-011 | Corner pins (EN/UVLO, VS, SCP_TEST, G2) | ±750                    | V     |      |

|                                            |                                                 | AEC Q100-011                            | Other pins              | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                |                                                        | MIN | NOM MAX | UNIT |

|----------------|--------------------------------------------------------|-----|---------|------|

|                | VS to GND                                              | 3.5 | 40      |      |

| Input Pins     | Minimum voltage on VS pin for Short Circuit Protection | 4   |         | V    |

|                | EN/UVLO, INP1, INP2 to GND                             | 0   | 40      |      |

| Output<br>Pins | FLT to GND                                             | 0   | 15      | V    |

| External       | VS, SRC to GND                                         | 22  |         | nF   |

| Capacitor      | BST to SRC                                             | 0.1 |         | μF   |

| Tj             | Operating Junction temperature <sup>(2)</sup>          | -40 | 150     | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# **6.4 Thermal Information**

|                       |                                              | TPS1210-Q1 |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGX        | UNIT |

|                       |                                              | 19 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 92.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 28.6       | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 47.5       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.6        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 47.2       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

$T_J = -40 \,^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ .  $V_{(VS)} = 12 \,\text{V}$ ,  $V_{(BST-SRC)} = 11 \,\text{V}$

|                            | $\frac{125^{\circ}\text{C. V}_{(VS)} = 12 \text{ V, V}_{(BST-SRC)} = 11}{\text{PARAMETER}}$ | TEST CONDITIONS                                                               | MIN        | TYP   | MAX      | UNIT |

|----------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------|-------|----------|------|

| SUPPLY VOLTA               | GE                                                                                          |                                                                               |            |       | <u> </u> |      |

| VS                         | Operating input voltage                                                                     |                                                                               | 3.5        |       | 40       | V    |

| V <sub>(S_PORR)</sub>      | Input supply POR threshold, rising                                                          |                                                                               | 1.85       | 2.55  | 3.3      | V    |

| V <sub>(S_PORF)</sub>      | Input supply POR threshold, falling                                                         |                                                                               | 1.71       | 2.33  | 3.05     | V    |

| I <sub>(Q)</sub>           | Total System Quiescent current, I <sub>(GND)</sub>                                          | V <sub>(EN/UVLO)</sub> = 2 V                                                  |            | 35    | 45       | μA   |

|                            | Total System Quiescent current, I <sub>(GND)</sub>                                          | V <sub>(EN/UVLO)</sub> = 2 V, −40°C ≤ T <sub>J</sub> ≤ +85°C                  |            |       | 44       | μA   |

| I <sub>(SHDN)</sub>        | SHDN current, I <sub>(GND)</sub>                                                            | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(SRC)</sub> = 0 V                        |            | 0.86  | 3.3      | μΑ   |

| I <sub>(REV)</sub>         | I <sub>(VS)</sub> leakage current during Reverse<br>Polarity                                | V <sub>(VS)</sub> = -40 V                                                     | 11         | 13    | 23       | μA   |

| ENABLE, UNDE               | RVOLTAGE LOCKOUT (EN/UVLO), SHO                                                             | RT CIRCUIT COMPARATOR TEST (SCF                                               | P_TEST) IN | IPUT  | '        |      |

| V <sub>(UVLOR)</sub>       | UVLO threshold voltage, rising                                                              |                                                                               | 1.176      | 1.23  | 1.287    | V    |

| V <sub>(UVLOF)</sub>       | UVLO threshold voltage, falling                                                             |                                                                               | 1.09       | 1.138 | 1.184    | V    |

| V <sub>(ENR)</sub>         | Enable threshold voltage for low Iq shutdown, rising                                        |                                                                               |            |       | 1        | V    |

| V <sub>(ENF)</sub>         | Enable threshold voltage for low Iq shutdown, falling                                       |                                                                               | 0.3        |       |          | V    |

| I <sub>(EN/UVLO)</sub>     | Enable input leakage current                                                                | V <sub>(EN/UVLO)</sub> = 12 V                                                 |            | 170   | 310      | nA   |

| V <sub>(SCP_TEST_H)</sub>  | SCP test mode rising threshold                                                              |                                                                               |            |       | 2        | V    |

| V <sub>(SCP_TEST_L)</sub>  | SCP test mode falling threshold                                                             |                                                                               | 0.8        |       |          | V    |

| I <sub>(SCP_TEST)</sub>    | SCP_TEST input leakage current                                                              |                                                                               |            | 90    | 700      | nA   |

| CHARGE PUMP                | (BST-SRC)                                                                                   |                                                                               |            |       |          |      |

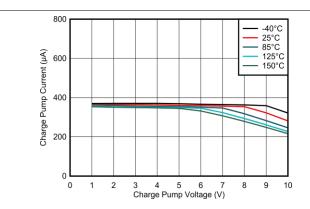

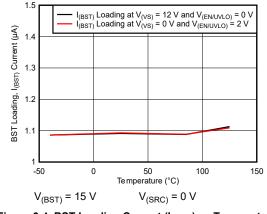

| I <sub>(BST)</sub>         | Charge Pump Supply current                                                                  | V <sub>(BST - SRC)</sub> = 10 V, V <sub>(EN/UVLO)</sub> = 2 V                 | 190        | 345   | 466      | μΑ   |

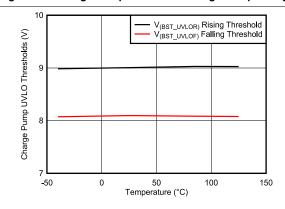

| V <sub>(BST_UVLOR)</sub>   | V <sub>(BST - SRC)</sub> UVLO voltage threshold, rising                                     | V <sub>(EN/UVLO)</sub> = 2 V                                                  | 8.1        | 9     | 9.9      | V    |

| V <sub>(BST_UVLOF)</sub>   | V <sub>(BST - SRC)</sub> UVLO voltage threshold, falling                                    | V <sub>(EN/UVLO)</sub> = 2 V                                                  | 7.31       | 8.2   | 8.9      | V    |

| V <sub>(BST-SRC_ON)</sub>  | Charge Pump Turn ON voltage                                                                 | V <sub>(EN/UVLO)</sub> = 2 V                                                  | 9.3        | 10.3  | 11.4     | V    |

| V <sub>(BST-SRC_OFF)</sub> | Charge Pump Turn OFF voltage                                                                | V <sub>(EN/UVLO)</sub> = 2 V                                                  | 10.4       | 11.6  | 12.8     | V    |

| V <sub>(BST-SRC)</sub>     | Charge Pump Voltage at V <sub>(VS)</sub> = 3.5 V                                            | V <sub>(EN/UVLO)</sub> = 2 V                                                  | 9.1        | 10.5  | 11.6     | V    |

| I <sub>(SRC)</sub>         | SRC pin leakage current                                                                     | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(INP1)</sub> = V <sub>(INP2)</sub> = 0 V |            | 0.4   |          | μΑ   |

| GATE DRIVER C              | OUTPUTS (G1PU, G1PD, G2)                                                                    |                                                                               |            |       |          |      |

| V <sub>(G1_GOOD)</sub>     | G1 Good rising threshold                                                                    |                                                                               | 5.5        | 7     | 8.3      | V    |

| I <sub>(G1PU)</sub>        | Peak Source Current                                                                         |                                                                               |            | 1.69  |          | Α    |

| I <sub>(G1PD)</sub>        | Peak Sink Current                                                                           |                                                                               |            | 2     |          | Α    |

Submit Document Feedback

# **6.5 Electrical Characteristics (continued)**

$T_J = -40 \, ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ .  $V_{(VS)} = 12 \, \text{V}$ ,  $V_{(BST-SRC)} = 11 \, \text{V}$

|                                               | PARAMETER                                            | TEST CONDITIONS                      | MIN  | TYP  | MAX   | UNIT |

|-----------------------------------------------|------------------------------------------------------|--------------------------------------|------|------|-------|------|

| I <sub>(G2)</sub>                             | G2 Peak Source Current                               |                                      |      | 1.69 |       | Α    |

| I <sub>(G2)</sub>                             | G2 Peak Sink Current                                 |                                      |      | 2    |       | Α    |

| SHORT CIRCUIT F                               | PROTECTION (ISCP)                                    |                                      |      |      |       |      |

| I <sub>SCP</sub>                              | SCP Input Bias current                               |                                      | 8.4  | 10   | 12.33 | μΑ   |

|                                               |                                                      | $R_{(ISCP)} = 140.5 \text{ k}\Omega$ |      | 300  |       | mV   |

|                                               |                                                      | $R_{(ISCP)} = 28 k\Omega$            | 60   | 75   | 90.5  | mV   |

| V <sub>(SCP)</sub>                            | SCP threshold                                        | $R_{(ISCP)} = 10.5 \text{ k}\Omega$  | 32   | 40   | 48.9  | mV   |

|                                               |                                                      | $R_{(ISCP)} = 500 \Omega$            | 15   | 20   | 25    | mV   |

|                                               |                                                      | R <sub>(ISCP)</sub> = Open           |      |      | 757   | mV   |

|                                               |                                                      | V <sub>(ISCP)</sub> = 1.405 V        | 283  | 300  | 316   | mV   |

| V <sub>(SCP)</sub>                            | SCP threshold with external bias voltage on ISCP pin | V <sub>(ISCP)</sub> = 280 mV         | 68.7 | 75   | 82.5  | mV   |

| voltage of 130F pill                          | V <sub>(ISCP)</sub> = 105 mV                         | 34.5                                 | 40   | 46.5 | mV    |      |

| DELAY TIMER (TN                               | IR)                                                  |                                      |      |      |       |      |

| I <sub>(TMR_SRC_CB)</sub>                     | TMR source current                                   |                                      | 67   | 87   | 104   | μA   |

| I <sub>(TMR_SRC_FLT)</sub>                    | TMR source current                                   |                                      | 1.4  | 2.73 | 3.8   | μA   |

| I <sub>(TMR_SNK)</sub>                        | TMR sink current                                     |                                      | 2.17 | 2.8  | 3.4   | μΑ   |

| V <sub>(TMR_SC)</sub>                         |                                                      |                                      | 0.93 | 1.1  | 1.2   | V    |

| V <sub>(TMR_LOW)</sub>                        |                                                      |                                      | 0.15 | 0.21 | 0.25  | V    |

| N <sub>(A-R Count)</sub>                      |                                                      |                                      |      | 32   |       |      |

| INPUT CONTROLS                                | S (INP1, INP2), CURRENT SENSE S                      | ELECT (CS_SEL) & FAULT FLAG (FLT)    |      |      |       |      |

| R <sub>(FLT)</sub>                            | FLT Pull-down resistance                             |                                      | 53   | 83   | 107   | Ω    |

| I <sub>(FLT)</sub>                            | FLT Input leakage current                            | 0 V ≤ V <sub>(FLT)</sub> ≤ 20 V      |      |      | 410   | nA   |

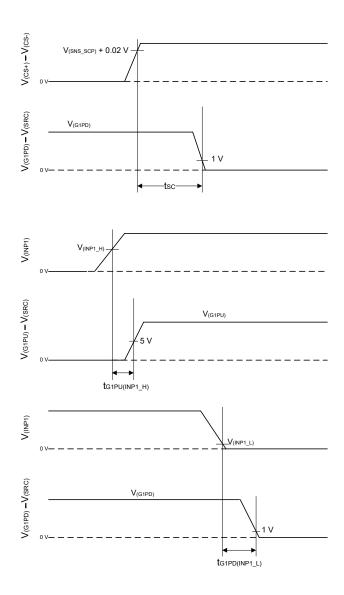

| V <sub>(INP1_H)</sub> , V <sub>(INP2_H)</sub> |                                                      |                                      |      |      | 2     | V    |

| V <sub>(INP1_L)</sub> , V <sub>(INP2_L)</sub> |                                                      |                                      | 0.8  |      |       | V    |

| I <sub>(INP1)</sub> , I <sub>(INP2)</sub>     | INP Input leakage current                            |                                      |      | 98   | 206   | nA   |

| V <sub>(CS_SEL_H)</sub>                       | CS_SEL threshold for low side sensing                |                                      |      |      | 2     | V    |

| V <sub>(CS_SEL_L)</sub>                       | CS_SEL threshold for high side sensing               |                                      | 0.8  |      |       | V    |

# **6.6 Switching Characteristics**

$T_J = -40 \,^{\circ}\text{C}$  to +125°C.  $V_{(VS)} = 12 \,\text{V}$ ,  $V_{(BST - SRC)} = 11 \,\text{V}$

|                           | PARAMETER                                                                            | TEST CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNIT |

|---------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>G1PU(INP_H)</sub>  | INP1 Turn ON propogation Delay                                                       | INP1 ↑ to G1PU ↑, C <sub>L</sub> = 47 nF                                                 | 0.19 |      | 1.53 | μs   |

| t <sub>G2(INP2_H)</sub>   | INP2 Turn ON propogation Delay                                                       | INP2 ↑ to G2 ↑, C <sub>L</sub> = 47 nF                                                   | 2.7  | 4.5  | 6.7  | μs   |

| t <sub>G1PD(INP_L)</sub>  | INP1Turn OFF propogation Delay                                                       | INP1 ↓ to G1PD ↓, C <sub>L</sub> = 47 nF                                                 |      | 0.29 | 0.85 | μs   |

| t <sub>G2(INP2_L)</sub>   | INP2 Turn OFF propogation Delay                                                      | INP2 ↓ to G2 ↓, C <sub>L</sub> = 47 nF                                                   | 2.7  | 4.4  | 6.79 | μs   |

| t <sub>PD(EN_OFF)</sub>   | EN Turn OFF Propogation Delay                                                        | EN ↓ to G1PD ↓, C <sub>L</sub> = 47 nF                                                   | 2.2  | 4.6  | 6    | μs   |

| t <sub>PD(UVLO_OFF)</sub> | UVLO Turn OFF Propogation Delay                                                      | UVLO $\downarrow$ to G1PD $\downarrow$ and $\overline{FLT}$ $\downarrow$ , $C_L$ = 47 nF | 2.8  | 4.2  | 6    | μs   |

| t <sub>sc</sub>           | Hard Short-circuit protection propogation delay                                      | $V_{(CS+-CS-)} \uparrow V_{(SCP)}$ to G1PD $\downarrow$ , CL = 47 nF, $C_{(TMR)}$ = Open |      |      | 4    | μs   |

| t <sub>SC_PUS</sub>       | Short-circuit protection propogation delay during power up with output short circuit | C <sub>TMR</sub> = Open                                                                  |      |      | 10   | μs   |

# **6.6 Switching Characteristics (continued)**

$T_J = -40 \,^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ .  $V_{(VS)} = 12 \,\text{V}$ ,  $V_{(BST-SRC)} = 11 \,\text{V}$

| PARAMETER                                      |  | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|------------------------------------------------|--|-----------------|-----|------|-----|------|

| F <sub>ISCP</sub> ISCP Pulse current frequency |  |                 |     | 1.18 |     | kHz  |

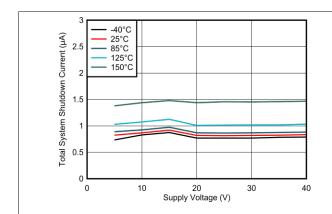

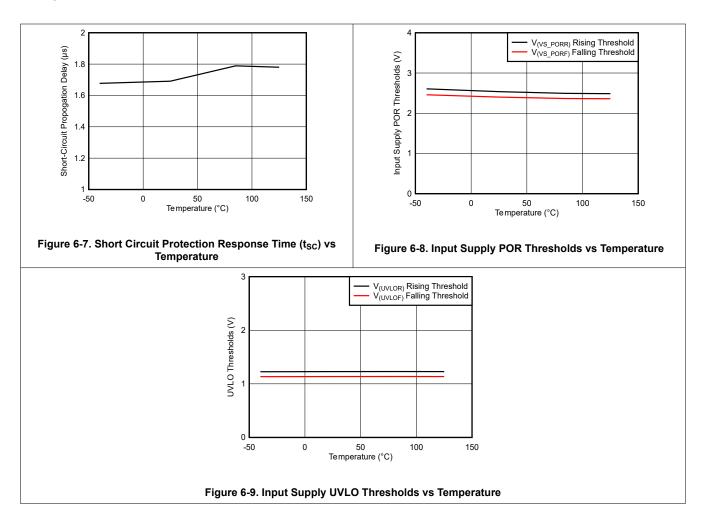

# **6.7 Typical Characteristics**

Figure 6-1. Shutdown Supply Current vs Supply Voltage

Figure 6-2. Operating Quiescent Current in Active Mode vs Supply Voltage

Figure 6-3. Charge Pump Current vs Charge Pump Voltage

Figure 6-4. BST Loading Current ( $I_{(BST)}$ ) vs Temperature

Figure 6-5. Charge Pump UVLO Thresholds vs Temperature

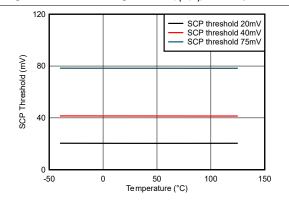

Figure 6-6. Short-Circuit Threshold  $(V_{(SCP)})$  vs Temperature

Submit Document Feedback

# **6.7 Typical Characteristics (continued)**

# 7 Parameter Measurement Information

Figure 7-1. Timing Waveforms

Submit Document Feedback

# 8 Detailed Description

### 8.1 Overview

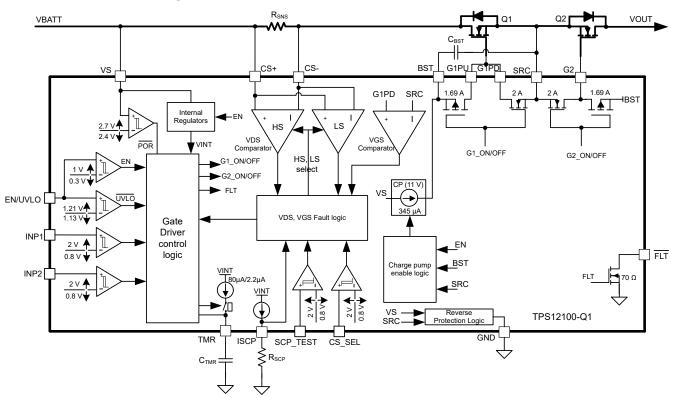

The TPS1210x-Q1 family is a 45-V, low IQ, smart high side driver with protection and diagnostics. With wide operating voltage range of 3.5 V - 40 V, the device is designed for 12-V, system designs. The device can withstand and protect the loads from negative supply voltages down to -40 V.

The device has two strong (2-A) GATE drivers with separate control inputs (INP1, INP2) to drive back-to-back MOSFETs in common source configuration. Strong GATE driving enables power switching using parallel FETs in high current system designs. TPS12100-Q1 has active high control inputs and TPS12101-Q1 has active low control inputs.

The device provides configurable short-circuit protection using ISCP and TMR pins for adjusting the threshold and response time respectively. Auto-retry and latch-off fault behavior can be configured. With TPS1210x-Q1, current sensing an be done either by an external sense resistor or by MOSFET VDS sensing. High side or low side current sense resistor configuration is possible by using CS\_SEL pin input. Diagnosis of the integrated short circuit comparator is possible using external control on SCP\_TEST input.

The device indicates fault (FLT) on open drain output during short circuit, charge pump undervoltage, and input undervoltage conditions.

Low Quiescent Current of 35  $\mu$ A in operation enables always ON system designs. Quiescent current reduces to 1.5  $\mu$ A (typical) with EN/UVLO low.

# 8.2 Functional Block Diagram

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

### 8.3 Feature Description

### 8.3.1 Charge Pump and Gate Driver Output (VS, G1PU, G1PD, G2, BST, SRC)

Figure 8-1 shows a simplified diagram of the charge pump and gate driver circuit implementation. The device houses two strong 1.69-A/2-A peak source/sink gate drivers enabling paralleling of FETs in high power system designs ensuring minimum transition time in saturation region. A 11-V,  $345-\mu$ A charge pump is derived from VS terminal and charges the external boot-strap capacitor,  $C_{BST}$  that is placed across the gate driver (BST and SRC).

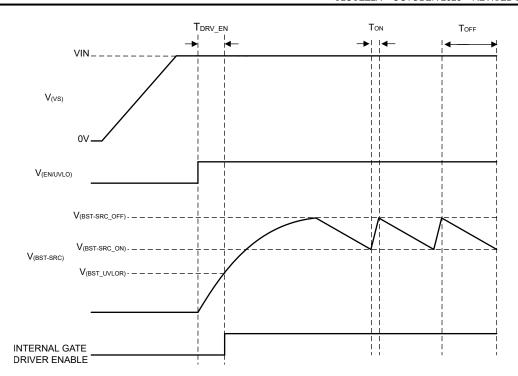

VS is the supply pin to the controller. With VS applied and EN/UVLO pulled high, the charge pump turns ON and charges the  $C_{BST}$  capacitor. After the voltage across  $C_{BST}$  crosses  $V_{(BST\_UVLOR)}$ , the GATE driver section is activated. The device has a 1-V (typical) UVLO hysteresis to ensure chattering less performance during initial GATE turn ON. Choose  $C_{BST}$  based on the external FET  $Q_G$  and allowed dip during FET turn-ON. The charge pump remains enabled until the BST to SRC voltage reaches 11.8 V, typically, at which point the charge pump is disabled decreasing the current draw on the VS pin. The charge pump remains disabled until the BST to SRC voltage discharges to 10 V typically at which point the charge pump is enabled. The voltage between BST and SRC continue to charge and discharge between 11.8 V and 10 V as shown in the Figure 8-2.

Figure 8-1. Gate Drivers

Submit Document Feedback

Figure 8-2. Charge Pump Operation

Use the following equation to calculate the initial gate driver enable delay:

$$T_{DRV\_EN} = \frac{C_{BST} \times V_{(BST\_UVLOR)}}{345 \,\mu\text{A}} \tag{1}$$

Where,

C<sub>BST</sub> is the charge pump capacitance connected across BST and SRC pins.

$V_{(BST\ UVLOR)} = 9.5\ V\ (maximum).$

If  $T_{DRV\_EN}$  must be reduced then pre-bias BST terminal externally using an external  $V_{AUX}$  supply through a low leakage diode  $D_1$  as shown in . With this connection,  $T_{DRV\_EN}$  reduces to 400  $\mu$ s. TPS12100-Q1 application circuit with external supply to BST is shown in Figure 8-3.

Figure 8-3. TPS12100-Q1 Application Circuit With External Supply to BST

### Note

$V_{AUX}$  can be supplied by external regulated supply ranging between 8 V and 18 V.

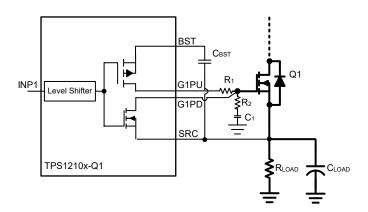

## 8.3.2 Capacitive Load Driving Using FET Gate (G1PU, G1PD) Slew Rate Control

For limiting inrush current during turn-ON of the external FET (Q1) with capacitive loads, use  $R_1$ ,  $R_2$ ,  $C_1$  as shown in Figure 8-4. The  $R_1$  and  $C_1$  components slow down the voltage ramp rate at the gate of Q1 FET. The FET source follows the gate voltage resulting in a controlled voltage ramp across the output capacitors.

Figure 8-4. Inrush Current Limiting Using G1 Gate Drive

Use the Equation 2 to calculate the inrush current during turn-ON of the FET.

$$I_{INRUSH} = C_{LOAD} \times \frac{V_{BATT}}{T_{charge}}$$

(2)

$$C_1 = \frac{0.63 \times V_{(BST - SRC)} \times C_{LOAD}}{R_1 \times I_{INRUSH}}$$

(3)

Submit Document Feedback

Where,

C<sub>LOAD</sub> is the load capacitance.

VBATT is the input voltage and  $T_{charge}$  is the charge time.

V<sub>(BST-SRC)</sub> is the charge pump voltage (11 V),

Use a damping resistor  $R_2$  (approximately 10  $\Omega$ ) in series with  $C_1$ . Equation 3 can be used to compute required  $C_1$  value for a target inrush current. A 100-k $\Omega$  resistor for  $R_1$  can be a good starting point for calculations.

Connecting G1PD pin of TPS1210x-Q1 directly to the gate of the Q1 FET ensures fast turn-OFF without any impact of  $R_1$  and  $C_1$  components.

$C_1$  results in an additional loading on  $C_{BST}$  to charge during turn-ON. Use below equation to calculate the required  $C_{BST}$  value:

$$C_{BST} = \frac{Q_{g(total)}}{\Delta V_{BST}} + 10 \times C_1$$

(4)

Where,

Q<sub>q(total)</sub> is the total gate charge of the FET,

$\Delta V_{BST}$  (1 V typical) is the ripple voltage across BST to SRC pins.

### 8.3.3 Short-Circuit Protection

The TPS1210x-Q1 feature adjustable short-circuit protection. The threshold and response time can be adjusted using  $R_{SCP}$  resistor and  $C_{TMR}$  capacitor respectively. The device senses the voltage across CS+ and CS- pins.

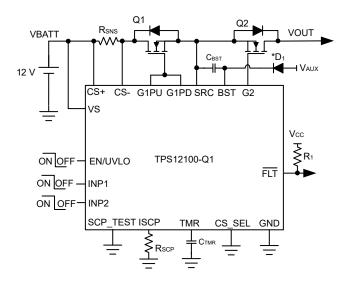

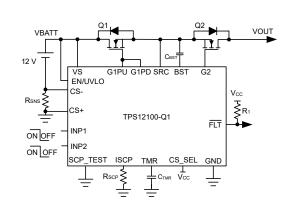

These pins can be connected across an external high and low side current sense resistor (R<sub>SNS</sub>) or across the FET drain and source terminals for FET RDSON sensing as shown in Figure 8-5, Figure 8-6 and Figure 8-7 respectively.

Figure 8-5. TPS12100-Q1 Application Circuit With External Sense Resistor RSNS based High Side Current Sensing

Figure 8-6. TPS12100-Q1 Application Circuit With MOSFET RDSON based Current Sensing

Figure 8-7. TPS12100-Q1 Application Circuit with External Sense Resistor RSNS based Low Side Current Sensing

Set the short-circuit detection threshold using an external  $R_{SCP}$  resistor across ISCP and GND pins. Use Equation 5 to calculate the required  $R_{SCP}$  value:

$$R_{SCP}\left(\Omega\right) = \frac{(I_{SC} \times R_{SNS} - 19 \text{ mV})}{2 \mu A}$$

(5)

Where.

R<sub>SNS</sub> is the current sense resistor value or the FET R<sub>DSON</sub> value.

I<sub>SC</sub> is the desired short-circuit current level.

The short-circuit protection response is fastest with no C<sub>TMR</sub> cap connected across TMR and GND pins.

With the device powered ON and EN/UVLO, INP1 pulled high, During Q1 turn-ON, first VGS of external FET Q1 (G1 gate drive) is sensed by monitoring the voltage across G1PD to SRC. Once G1PD to SRC voltage raises above  $V_{(G1\_GOOD)}$  threshold which ensures that the external FET is enhanced, then the SCP comparator output is monitored. If the sensed voltage across CS+ and CS- exceeds the short-circuit set point ( $V_{(SCP)}$ ), G1PD pulls low to SRC and  $\overline{FLT}$  asserts low. Subsequent events can be set either to be auto-retry or latch off as described in following sections.

VGS of external FET (Q1) is only monitored when CS\_SEL is pulled low. VGS of external FET (Q1) is not monitored for low side current sensing.

#### Note

Short-circuit threshold can also be set by connecting external bias voltage on ISCP pin via buffer instead of  $R_{SCP}$  resistor enabling system design with improved SCP threshold accuracy as mentioned in electrical characteristics table. The external bias voltage to be forced on ISCP pin can be calculated by below eqaution:

$V_{(SCP\_BIAS)}$  in mV =  $I_{SC}$  x  $R_{SNS}$  x 5 - 95mV

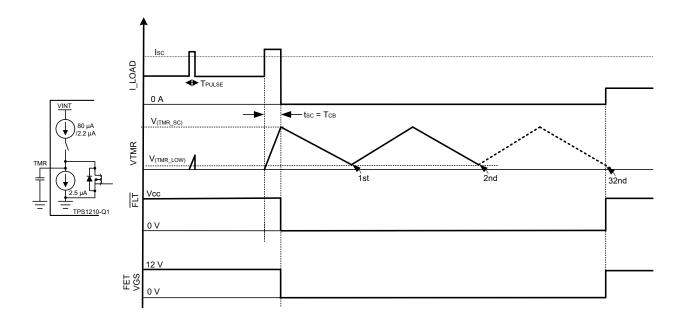

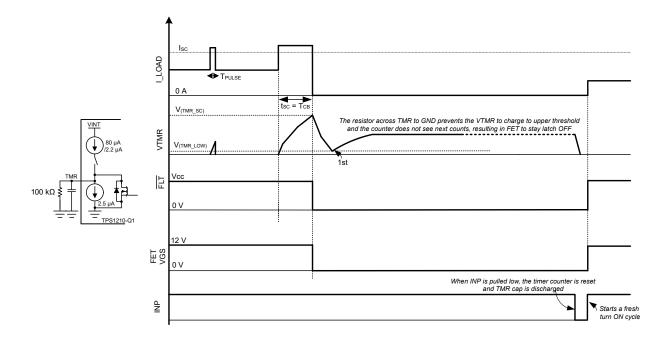

### 8.3.3.1 Short-Circuit Protection With Auto-Retry

The  $C_{TMR}$  programs the short-circuit protection delay ( $t_{SC}$ ) and auto-retry time ( $t_{RETRY}$ ). After the voltage across CS+ and CS- exceeds the set point, the  $C_{TMR}$  starts charging with 80- $\mu$ A pullup current.

After  $C_{TMR}$  charges to  $V_{(TMR\_SC)}$ , G1PD pulls low to SRC and  $\overline{FLT}$  asserts low providing warning on impending FET turn-OFF. Post this event, the auto-retry behavior starts. The  $C_{TMR}$  capacitor starts discharging with 2.5-uA

Submit Document Feedback

pulldown current. After the voltage reaches  $V_{(TMR\_LOW)}$  level, the capacitor starts charging with 2.2-uA pullup. After 32 charging-discharging cycles of  $C_{TMR}$  the FET turns ON back and FLT de-asserts.

The device retry time (t<sub>RETRY</sub>) is based on C<sub>TMR</sub> for the first time as per Equation 7.

Use Equation 6 to calculate the C<sub>TMR</sub> capacitor to be connected across TMR and GND.

$$C_{\text{TMR}} = \frac{I_{\text{TMR}} \times t_{\text{SC}}}{1.1} \tag{6}$$

Where,

I<sub>TMR</sub> is internal pullup current of 80 μA.

t<sub>SC</sub> is the desired short-circuit response time.

Leave TMR floating for fastest short-circuit response time.

$$t_{RETRY} = 22.7 \times 10^6 \times C_{TMR} \tag{7}$$

If the short-circuit pulse duration is below  $t_{SC}$  then the FET remains ON and  $C_{TMR}$  gets discharged using internal pulldown switch.

Figure 8-8. Short-Circuit Protection With Auto-Retry

### 8.3.3.2 Short-Circuit Protection With Latch-Off

Connect an approximately  $100-k\Omega$  resistor across  $C_{TMR}$  as shown in Figure 8-9. With this resistor, during the charging cycle, the voltage across  $C_{TMR}$  gets clamped to a level below  $V_{(TMR\_SC)}$  resulting in a latch-off behavior and  $\overline{FLT}$  asserts low at same time.

Use Equation 8 to calculate  $C_{TMR}$  capacitor to be connected between TMR and GND for  $R_{TMR}$  = 100 k $\Omega$ .

$$C_{\text{TMR}} = \frac{t_{\text{SC}}}{R_{\text{TMR}} \times \ln \left( \frac{1}{1 - \frac{1.1}{R_{\text{TMR}} \times 80 \,\mu\text{A}}} \right)}$$

(8)

Where,

I<sub>TMR</sub> is internal pullup current of 80 μA.

t<sub>SC</sub> is the desired short-circuit response time.

Toggle INP or EN/UVLO (below  $V_{(ENF)}$ ) or power cycle VS below  $V_{(VS\_PORF)}$  to reset the latch. At low edge, the timer counter is reset and C<sub>TMR</sub> is discharged. G1PU pulls up to BST when INP is pulled high.

Figure 8-9. Short-Circuit Protection With Latch-Off

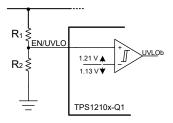

### 8.3.4 Undervoltage Protection (UVLO)

TPS1210x-Q1 has an accurate undervoltage protection (< ±2%) using EN/UVLO pin providing robust protection. Connect a resistor ladder as shown in Figure 8-10 for undervoltage protection threshold programming.

Figure 8-10. Programming Undervoltage Protection

### 8.3.5 Reverse Polarity Protection

The TPS1210x-Q1 devices features integrated reverse polarity protection to protect the device from failing during input and output reverse polarity faults. Reverse polarity faults occur during installation and maintenance

Product Folder Links: TPS1210-Q1

of the end equipments. The device is tolerant to reverse polarity voltages down to -45 V both on input and on the output.

On the output side, the device can see transient negative voltages during regular operation due to output cable harness inductance kickbacks when the switches are turned OFF. In such systems the output negative voltage level is limited by the output side TVS or a diode.

# 8.3.6 Short-Circuit Protection Diagnosis (SCP\_TEST)

In the safety critical designs, the short-circuit protection (SCP) feature and the diagnosis are important.

The TPS1210x-Q1 features the diagnosis of the internal short-circuit protection. When SCP\_TEST is driven low to high, then a voltage is applied internally across the SCP comparator inputs to simulate a short-circuit event. The comparator output controls the gate drive (G1PU/G1PD) and also the  $\overline{\text{FLT}}$ . If the gate drive goes low (with initially being high) and  $\overline{\text{FLT}}$  also goes low, then this action indicates that the SCP is good otherwise is to be treated as the SCP feature is not functional.

If the SCP\_TEST feature is not used, then connect SCP\_TEST pin to GND.

### 8.3.7 TPS1210x-Q1 as a Simple Gate Driver

Figure 8-11 shows application schematics of TPS1210x-Q1 as a simple gate driver in load connect-disconnect switch driving back-to-back FETs topology. The short-ciruit protection feature is disabled.

Figure 8-11. TPS12100-Q1 Application Circuit for Simple Gate Driver

### 8.4 Device Functional Modes

The TPS1210x-Q1 has two modes of operation. Active mode and low IQ shutdown mode.

If the EN/UVLO pin voltage is greater than  $V_{(ENR)}$  rising threshold, then the device is in active mode. In active state the internal charge pump is enabled, gate drivers, all the protection and diagnostic features are enabled.

If the EN/UVLO voltage is pulled below  $V_{(ENF)}$  falling threshold, the device enters into low IQ shutdown mode. In this mode, the charge pump, gate drivers and all the protection features are disabled. The gate drive and external FETs turn OFF. The TPS1210x-Q1 consumes low IQ of 1.5  $\mu$ A (typical) in this mode.

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

# 9 Application and Implementation

### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

# 9.1 Application Information

The TPS1210x-Q1 family is a 45-V, low IQ, smart high side driver with protection and diagnostics. The TPS1210x-Q1 device architecture is design to drive and control back-to-back N-Channel MOSFETs independently in common source configuration with separate control inputs (INP1, INP2), which makes TPS1210x-Q1 an excellent choice to realize circuit breaker in battery management system (BMS). The strong (2-A) GATE drivers enable switching parallel MOSFETs in high current applications such as circuit breaker in powertrain (DC/DC converter), driving loads in power distribution unit, circuit breaker in 12-V BMS, and so forth.

The TPS1210x-Q1 device provides configurable short-circuit protection using ISCP and TMR pins for adjusting the threshold and response time respectively. Auto-retry and latch-off fault behavior can be configured. By using CS+ and CS- pins, current sensing can be done either by an external sense resistor or by MOSFET VDS sensing. High side or low side current sense resistor configuration is possible by using CS\_SEL pin input. The device also features diagnosis of the internal short circuit comparator using external control on SCP TEST input.

The following design procedure can be used to select the supporting component values based on the application requirement.

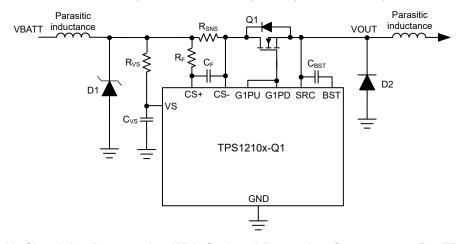

# 9.2 Typical Application: Circuit Breaker in Battery Management System (BMS) using Low Side Current Sense

Figure 9-1. Typical Application Schematic: BMS Circuit Breaker With Low Side Current Sense

Product Folder Links: TPS1210-Q1

### 9.2.1 Design Requirements

The following table shows the design parameters for this application example.

Table 9-1. Design Parameters

| PARAMETER                                           | VALUE      |

|-----------------------------------------------------|------------|

| Typical input voltage, V <sub>IN</sub>              | 12 V       |

| Undervoltage lockout set point, VIN <sub>UVLO</sub> | 6.5 V      |

| Maximum load current, I <sub>OUT</sub>              | 25 A       |

| Short-circuit protection threshold, I <sub>SC</sub> | 40 A       |

| Short-circuit protection delay (t <sub>SC</sub> )   | 1 ms       |

| Fault response                                      | Auto-retry |

| Current sensing                                     | Low-side   |

### 9.2.2 Detailed Design Procedure

### Selection of Current Sense Resistor, R<sub>SNS</sub>

The recommended range of the overcurrent protection threshold voltage,  $V_{(SCP)}$ , extends from 30 mV to 300 mV. Values near the low threshold of 30 mV can be affected by the system noise. Values near the upper threshold of 300 mV can cause high power dissipation in the current sense resistor. To minimize both the concerns, 40 mV is selected as the short-circuit protection threshold voltage. Use the following equation to calculate the current sense resistor,  $R_{\rm SNS}$ .

$$R_{SNS} = \frac{V(SCP)}{I_{SC}}$$

(9)

The next smaller available sense resistor 1 m $\Omega$ , 1% is chosen.

To improve signal to noise ratio or for better short-circuit protection accuracy, higher short-circuit protection threshold voltage,  $V_{(SCP)}$  can be selected.

### Programming the Short-Circuit Protection Threshold – R SCP Selection

The R<sub>SCP</sub> sets the short-circuit protection threshold. Use the following equation to calculate the value.

$$R_{SCP}\left(\Omega\right) = \frac{(I_{SC} \times R_{SNS} - 19 \text{ mV})}{2 \mu A} \tag{10}$$

To set 30-A as short-circuit protection threshold,  $R_{SCP}$  value is calculated to be 5.5 k $\Omega$ .

Choose the closest available standard value:  $5.3 \text{ k}\Omega$ , 1%.

In case where large di/dt is involved, the system and layout parasitic inductances can generate large differential signal voltages between CS+ and CS- pins. This action can trigger false short-circuit protection and nuisance trips in the system. To overcome such scenario, TI suggests to add placeholder for RC filter components across sense resistor ( $R_{SNS}$ ) and tweak the values during test in the real system. The RC filter components should not be used in current sense designs by MOSFET VDS sensing to avoid impact on the short-circuit protection response.

### Programming the Short-Circuit Protection Delay – C<sub>TMR</sub> Selection

For the design example under discussion, overcurrent transients are allowed for 1-ms duration. This short-circuit protection delay,  $t_{SC}$  can be set by selecting appropriate capacitor  $C_{TMR}$  from TMR pin to ground. Use the following equation to calculate the value of  $C_{TMR}$  to set 1 ms for  $t_{SC}$ .

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

$$C_{\text{TMR}} = \frac{80 \,\mu \times t_{\text{SC}}}{1.1} = 72.72 \,\text{nF} \tag{11}$$

Choose closest available standard value: 82 nF, 10%.

### Selection of MOSFETs, Q<sub>1</sub> and Q<sub>2</sub>

For selecting the MOSFET  $Q_1$  and  $Q_2$  important electrical parameters are the maximum continuous drain current  $I_D$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the maximum drain-to-source voltage  $V_{GS(MAX)}$ , and the drain-to-source ON-resistance  $R_{DSON}$ .

The maximum continuous drain current, ID, rating must exceed the maximum continuous load current.

The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest voltage seen in the application. Considering 35 V as the maximum application voltage, MOSFETs with  $V_{DS}$  voltage rating of 40 V is designed for this application.

The maximum  $V_{GS}$  TPS1210-Q1 can drive is 13 V, so a MOSFET with 15-V minimum  $V_{GS}$  rating must be selected.

To reduce the MOSFET conduction losses, lowest possible R<sub>DS(ON)</sub> is preferred.

Based on the design requirements, BUK7S1R0-40H is selected and the ratings are:

- 40-V  $V_{DS(MAX)}$  and 20-V  $V_{GS(MAX)}$

- $R_{DS(ON)}$  is 0.88-m $\Omega$  typical at 10-V  $V_{GS}$

- Maximum MOSFET Q<sub>g(total)</sub> is 137 nC

### Selection of Bootstrap Capacitor, C BST

The internal charge pump charges the external bootstrap capacitor (connected between BST and SRC pins) with approximately 345  $\mu$ A. Use the following equation to calculate the minimum required value of the bootstrap capacitor for driving two BUK7S1R0-40H MOSFETs.

$$C_{BST} = \frac{Q_{g(total)}}{1 \text{ V}} = 274 \text{ nF}$$

(12)

Choose closest available standard value: 330 nF, 10 %.

### Setting the Undervoltage Lockout

The undervoltage lockout (UVLO) can be adjusted using an external voltage divider network of  $R_1$  and  $R_2$  connected between VS, EN/UVLO and GND pins of the device. The values required for setting the undervoltage and overvoltage are calculated by solving Equation 13.

$$V_{(UVLOR)} = \frac{R_2}{(R_1 + R_2)} \times VIN_{UVLO}$$

(13)

For minimizing the input current drawn from the power supply, TI recommends to use higher values of resistance for  $R_1$  and  $R_2$ . However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current,  $I(R_{12})$  must be chosen to be 20 times greater than the leakage current of UVLO pin.

From the device electrical specifications,  $V_{(UVLOR)} = 1.21$  V. From the design requirements,  $VIN_{UVLO}$  is 6.5 V. To solve the equation, first choose the value of  $R_1 = 470$  k $\Omega$  and use Equation 13 to solve for  $R_2 = 107.5$  k $\Omega$ . Choose the closest standard 1% resistor values:  $R_1 = 470$  k $\Omega$ , and  $R_2 = 105$  k $\Omega$ .

Product Folder Links: TPS1210-Q1

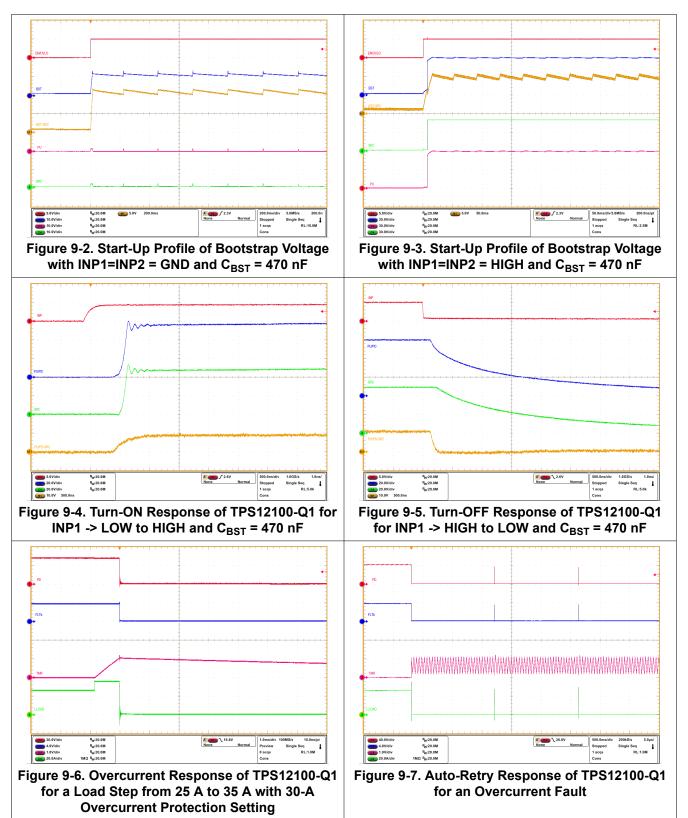

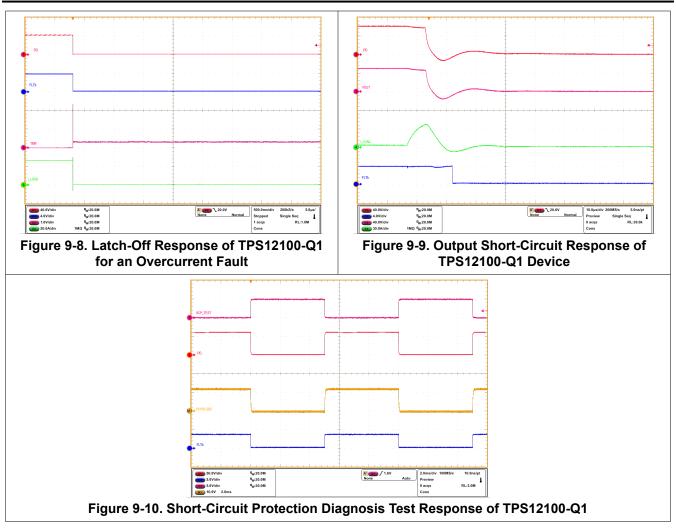

### 9.2.3 Application Curves

## 9.3 Power Supply Recommendations

When the external MOSFETs turn-OFF during the conditions such as INP1 control, overcurrent protection causing an interruption of the current flow, the input parasitic line inductance generates a positive voltage spike on the input and output parasitic inductance generates a negative voltage spike on the output. The peak amplitude of voltage spikes (transients) depends on the value of inductance in series to the input or output of the device. These transients can exceed the *Absolute Maximum Ratings* of the device if steps are not taken to address the issue. Typical methods for addressing transients include:

- Use of a TVS diode and input capacitor filter combination across input to and GND to absorb the energy and dampen the positive transients.

- Use of a diode or a TVS diode across the output and GND to absorb negative spikes.

The TPS1210-Q1 gets powered from the VS pin. Voltage at this pin must be maintained above  $V_{(VS\_PORR)}$  level to ensure proper operation. If the input power supply source is noisy with transients, then TI recommends to place a  $R_{VS}-C_{VS}$  filter between the input supply line and VS pin to filter out the supply noise. TI recommends  $R_{VS}$  value around  $100\Omega$ .

In case where large di/dt is involved, the system and layout parasitic inductances can generate large differential signal voltages between CS+ and CS- pins. This action can trigger false short-circuit protection and nuisance trips in the system. To overcome such scenario, TI suggests to add placeholder for RC filter components across sense resistor ( $R_{SNS}$ ) and tweak the values during test in the real system. The RC filter components must not be used in current sense designs by MOSFET VDS sensing to avoid impact on the short-circuit protection response.

The following figure shows the circuit implementation with optional protection components.

Figure 9-11. Circuit Implementation With Optional Protection Components For TPS1210-Q1

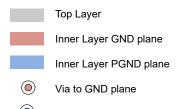

# 9.4 Layout

### 9.4.1 Layout Guidelines

- Place the sense resistor (R<sub>SNS</sub>) close to the TPS1210x-Q1 and then connect R<sub>SNS</sub> using the Kelvin techniques. Refer to Choosing the Right Sense Resistor Layout for more information on the Kelvin techniques.

- Choose a 0.1 µF or higher value ceramic decoupling capacitor between VS terminal and GND for all the

applications. Consider adding RC network at the supply pin (VS) of the controller to improve decoupling

against the power line disturbances.

- Make the high-current path from the board input to the load, and the return path, parallel and close to each other to minimize loop inductance.

- Place the external MOSFETs close to the controller GATE drive pins (G1PU/PD and G2) such that the GATE

of the MOSFETs are close to the controller GATE drive pins and forms a shorter GATE loop. Consider adding

a place holder for a resistor in series with the Gate of each external MOSFET to damp high frequency

oscillations if need arises.

- Place a TVS diode at the input to clamp the voltage transients during hot-plug and fast turn-off events.

- Place the external boot-strap capacitor close to BST and SRC pins to form very short loop.

- Connect the ground connections for the various components around the TPS1210x-Q1 directly to each other, and to the TPS1210x-Q1 GND, and then connected to the system ground at one point. Do not connect the various component grounds to each other through the high current ground line.

Product Folder Links: TPS1210-Q1

## 9.4.2 Layout Example

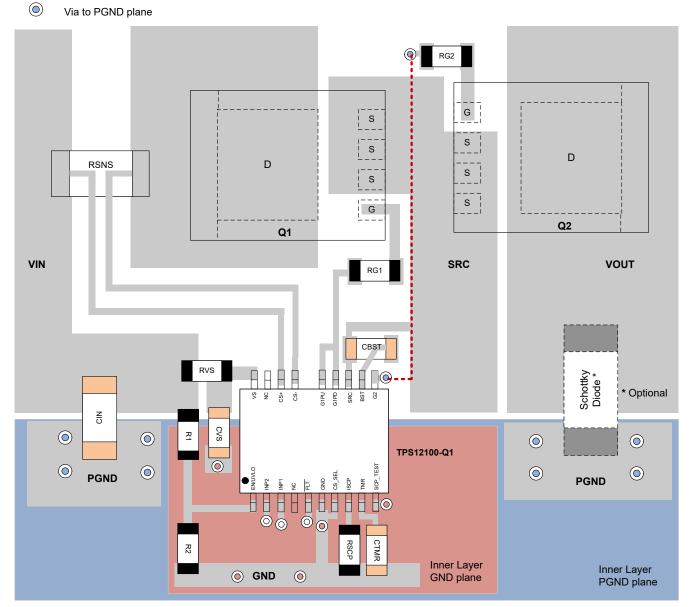

Figure 9-12. Typical PCB Layout Example for TPS1210-Q1 With B2B MOSFETs

# 10 Device and Documentation Support

# 10.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Notifications* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 10.2 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

### 10.3 Trademarks

TI E2E™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

## 10.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# 10.5 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

### 11 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision \* (October 2023) to Revision A (December 2024)

**Page**

Changed the document status From: Advance Information To: Production Data ......

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

www.ti.com 28-Dec-2024

### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| PTPS12100QDGXRQ1 | ACTIVE     | VSSOP        | DGX                | 19   | 5000           | TBD          | (6)<br>Call TI                | Call TI             | -40 to 125   |                      | Samples |

| PTPS12101QDGXRQ1 | ACTIVE     | VSSOP        | DGX                | 19   | 5000           | TBD          | Call TI                       | Call TI             | -40 to 125   |                      | Samples |

| TPS12100QDGXRQ1  | ACTIVE     | VSSOP        | DGX                | 19   | 5000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 1210                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 28-Dec-2024

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 29-Dec-2024

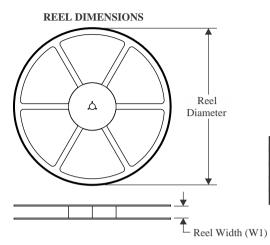

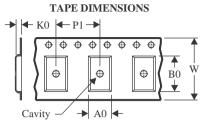

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

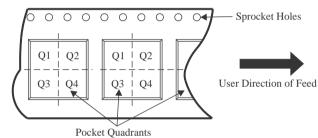

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device          | U     | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS12100QDGXRQ1 | VSSOP | DGX                | 19 | 5000 | 330.0                    | 16.4                     | 5.4        | 5.4        | 1.45       | 8.0        | 16.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 29-Dec-2024

# \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS12100QDGXRQ1 | VSSOP        | DGX             | 19   | 5000 | 353.0       | 353.0      | 32.0        |

SMALL OUTLINE PACKAGE

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. No JEDEC registration as of July 2021.

5. Features may differ or may not be present.

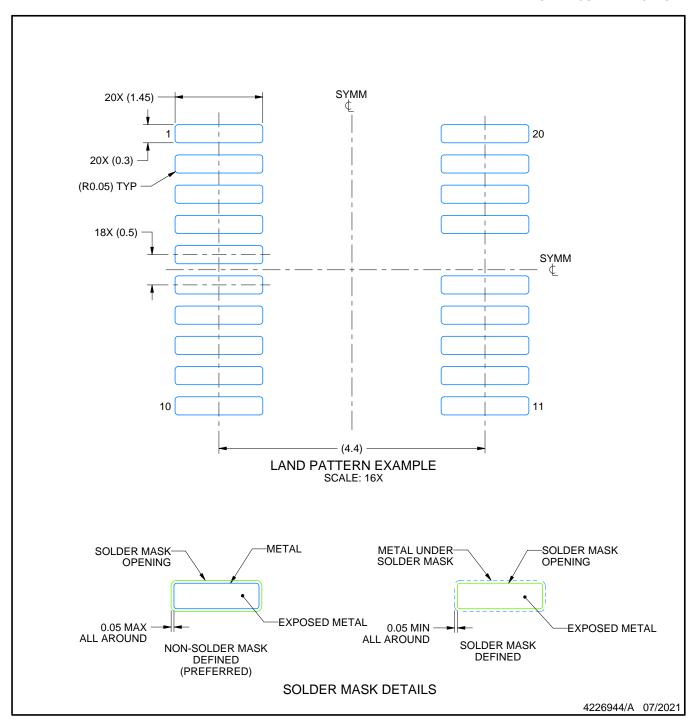

SMALL OUTLINE PACKAGE

### NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- 10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

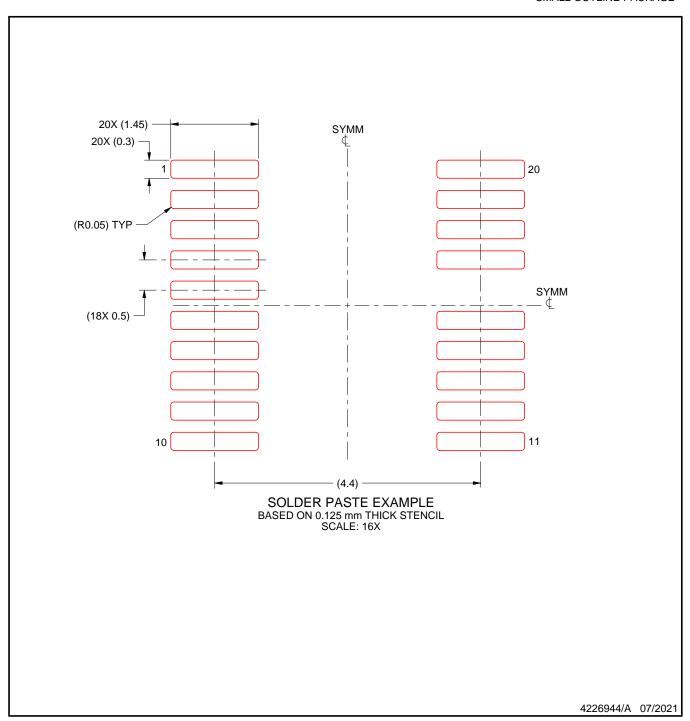

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated