# Circuit for driving high-voltage SAR ADCs for high-voltage, true differential signal acquisition

#### Dale Li

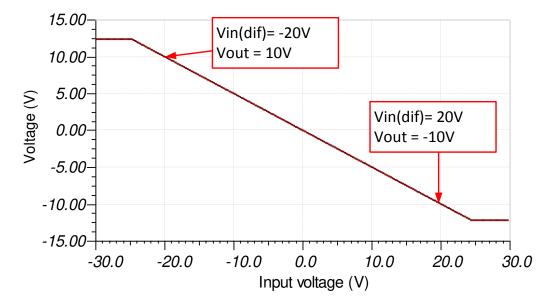

| Input             | ADC Input   | Digital Output ADS7042                     |

|-------------------|-------------|--------------------------------------------|

| VinDiffMin = -20V | CH_x = +10V | 7FFF <sub>H</sub> , or 32767 <sub>10</sub> |

| VinDiffMax = +20V | CH_x = -10V | 8000 <sub>H</sub> , or 32768 <sub>10</sub> |

| Power Supplies |      |                        |                        |

|----------------|------|------------------------|------------------------|

| AVDD           | DVDD | V <sub>CC</sub> (HVDD) | V <sub>SS</sub> (HVSS) |

| 5.0V           | 3.3V | +15V                   | -15V                   |

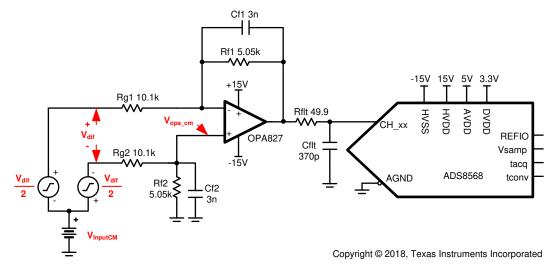

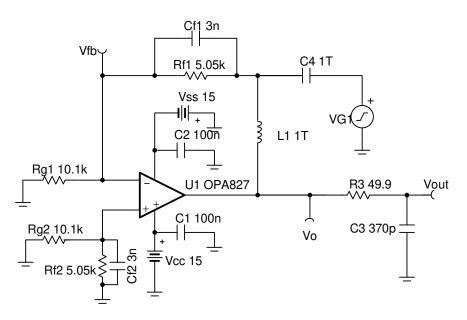

### **Design Description**

This design shows a design to drive high-voltage SAR ADC to implement data capture for high-voltage fully differential signal which can have a wide common-mode voltage range depended on the power supply and input amplitude signal of the amplifier. A general high-voltage precision amplifier performs the differential to single-ended conversion and drives high-voltage SAR ADC single-ended input scale of ±10V at highest throughput. This type of application is popular in end equipment such as: *Multi-Function Relays*, *AC Analog Input Modules*, and *Control Units for Rail Transport*. The values in the *component selection* section can be adjusted to allow for different level differential input signal, different ADC data throughput rates, and different bandwidth amplifiers.

# **Specifications**

| Specification                              | OPA827 Calculated  | OPA827 Simulated    | OPA192 Calculated  | OPA192 Simulated   |

|--------------------------------------------|--------------------|---------------------|--------------------|--------------------|

| Common Mode Input Range (with Vdif = ±20V) | ±26V               | ±26V                | ±35V               | ±35V               |

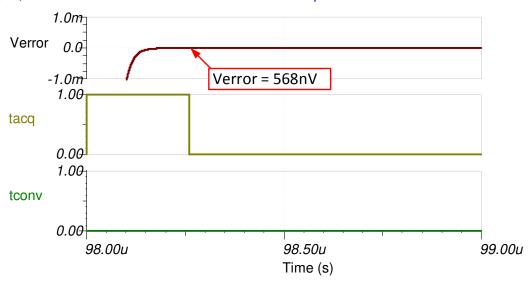

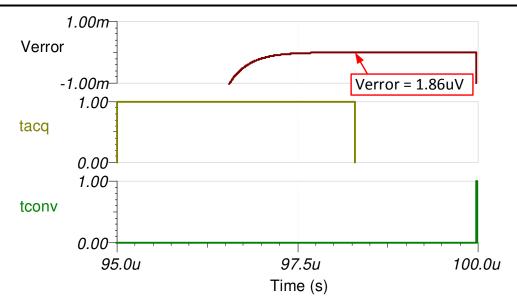

| Transient ADC Input Settling Error         | < 1/2LSB (< 152μV) | 0.002 LSB (0.568µV) | < 1/2LSB (< 152µV) | 0.006 LSB (1.86μV) |

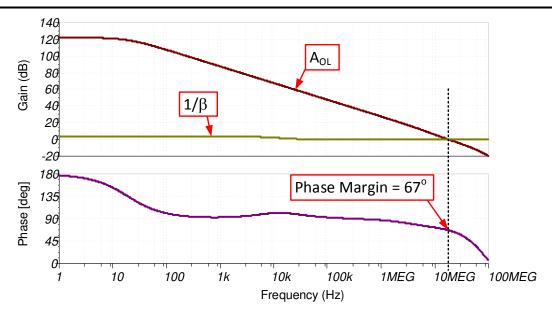

| Phase Margin of driver                     | > 45°              | 67.1°               | > 45°              | 68.6°              |

| (continued) |

|-------------|

|-------------|

| Specification        | OPA827 Calculated | OPA827 Simulated | OPA192 Calculated | OPA192 Simulated |

|----------------------|-------------------|------------------|-------------------|------------------|

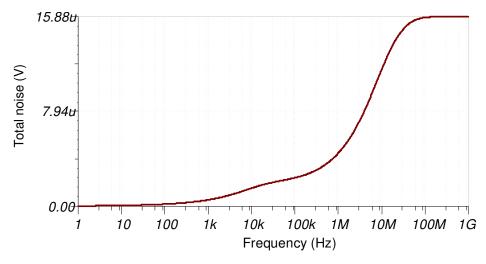

| Noise (at ADC Input) | 14.128µVrms       | 15.88µVrms       | 5.699µVrms        | 6.44µVrms        |

### **Design Notes**

- 1. Determine the amplifier gain based on the differential input signal level, the ADC's configuration for input range. This is covered in the *component selection* section.

- Determine amplifier's linear range based on common mode voltage, input swing, and power supplies. This is covered in the component selection section.

- In this design circuit, the common-mode voltage of the input signal can be any value in the range of V<sub>InputCM</sub>. The derivation of this range is provided in the *component selection* section for the OPA827 and OPA192.

- 4. Select COG capacitors to minimize distortion.

- 5. Use 0.1% 20ppm/°C film resistors or better for good accuracy, low gain drift, and to minimize distortion. Review *Statistics Behind Error Analysis* for methods to minimize gain, offset, drift, and noise errors.

- 6. Refer to Introduction to SAR ADC Front-End Component Selection for an explanation of how to select Rfilt and Cfilt for best settling and AC performance. These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here provide good settling and AC performance for the amplifier and data converter in this example. If the design is modified, select a different RC filter.

## **Component Selection**

1. Find the gain based on differential input signal and ADC full-scale input range.

$$Gain_{OPA} = \frac{\pm V_{ADC}(range)}{\pm V_{DifIn}(range)} = \frac{\pm 10V}{\pm 20V} = 0.5V/V$$

Find standard resistor values for differential gain. Use the Analog Engineer's Calculator ("Amplifier and Comparator\Find Amplifier Gain" section) to find standard values for Rf/Rg ratio.

$$Gain_{OPA} = \frac{R_f}{R_g} = \frac{5.05k\Omega}{10.1k\Omega} = 0.5$$

Find the amplifier's maximum and minimum input for linear operation (that is, the common mode range of the amplifier, V<sub>cm amp</sub>). For this example, the OPA827 is used.

$$V_- + 3V < V_{cm \ opa} < V_+ - 3V$$

from the OPA827 common mode specification

$$-12V < V_{cm\_opa} < 12V$$

for  $\pm 15V$  supplies

Calculate the maximum common-mode voltage range based on the input range and previously shown

configuration of the amplifier. Refer to the schematic diagram on the first page for better understanding of

how V<sub>cm opa</sub>, V<sub>InputCM</sub>, and V<sub>dif</sub> relate to the circuit.

$$V_{cm\_opa} = \left(V_{InputCM} \pm \frac{V_{dif}}{2}\right) \cdot \left(\frac{R_f}{R_f + R_g}\right)$$

$$V_{cm\_opaMin} \cdot \left(\frac{R_f + R_g}{R_f}\right) + \frac{V_{dif}}{2} < V_{InputCM} < V_{cm\_opaMax} \cdot \left(\frac{R_f + R_g}{R_f}\right) - \frac{V_{dif}}{2}$$

5. Solve the equation for the input common-mode range V<sub>InputCM</sub> for the amplifier. For this example (OPA827), the common mode input can be ±26V with a ±20-V differential input. Using the same method on OPA192 shows a common mode range of ±35V with a ±20-V differential input. Exceeding this common-mode range distorts the signal. Note that this common-mode range was calculated using ±15-V power supplies. The common mode range can be extended by increasing the supply (maximum ±18V).

$$V_{cm\_opaMin} \cdot \left(\frac{R_f + R_g}{R_f}\right) + \frac{V_{dif}}{2} < V_{InputCM} < V_{cm\_opaMax} \cdot \left(\frac{R_f + R_g}{R_f}\right) - \frac{V_{dif}}{2}$$

2

$$\begin{split} &\left(-12V\right)\cdot\left(\frac{5.05k\Omega+10.1k\Omega}{5.05k\Omega}\right)+\frac{20V}{2} < V_{InputCM} < \left(12V\right)\cdot\left(\frac{5.05k\Omega+10.1k\Omega}{5.05k\Omega}\right)-\frac{20V}{2} \\ &-26V < V_{InputCM} < 26V \end{split}$$

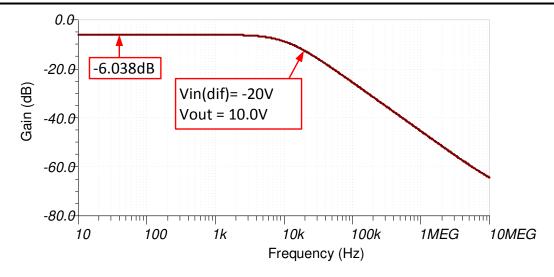

6. Find the value for Cf that achieves the desired closed-loop bandwidth. In this example, users need a 10kHz bandwidth. Note: if users adjust the bandwidth, then users need to verify the charge bucket filter settling (C<sub>filt</sub> and R<sub>filt</sub>) as the closed-loop bandwidth effects settling.

$$C_f = \frac{1}{2 \cdot \pi \cdot R_f \cdot f_C} = \frac{1}{2 \cdot \pi \cdot (5.05 k\Omega) \cdot (10 kHz)} = 3.1 nF \quad or \quad 3nF \quad standard \quad value$$

Find the value for Cfilt and Rfilt using TINA SPICE and the methods described in Introduction to SAR ADC

Front-End Component Selection. The value of Rfilt and Cfilt shown in this document works for these circuits;

however, if users use different amplifiers or different gain settings, then users must use TINA SPICE to find

new values.

#### **DC Transfer Characteristics**

The following graph shows a linear output response for inputs from differential –20V to +20V. The full-scale range (FSR) of the ADC falls within the linear range of the op amp. Refer to *Determining a SAR ADC's Linear Range when using Operational Amplifiers* for detailed theory on this subject.

## **AC Transfer Characteristics**

The bandwidth is simulated to be 10.58kHz and the gain is –6.038dB which is a linear gain of 0.5V/V. See the *Op Amps: Bandwidth 1* video for more details on this subject.

# Transient ADC Input Settling Simulation Highest Sampling rate - 510ksps on ADS8568+OPA827

The following simulation shows settling to a 20V DC input signal with OPA827. This type of simulation shows that the sample and hold kickback circuit is properly selected to within  $\frac{1}{2}$  of a LSB (152 $\mu$ V). For detailed theory on this subject, refer to *Introduction to SAR ADC Front-End Component Selection*.

### Transient ADC Input Settling Simulation Lower Sampling rate - 200ksps on ADS8568+OPA192

The following simulation shows settling to a 20V DC input signal with OPA192. This type of simulation shows that the sample and hold kickback circuit is properly selected to within  $\frac{1}{2}$  of a LSB (152 $\mu$ V).

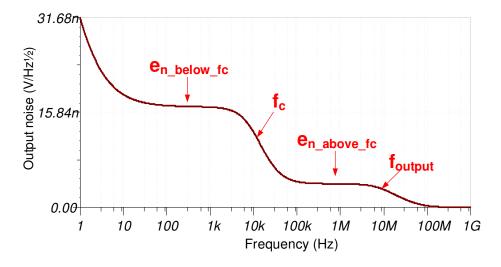

#### **Noise Calculation**

This section demonstrates a full-noise analysis including resistor noise. Also, look at the noise below  $f_c$  (Noise Gain = 1.5), and the noise above  $f_c$  (noise Gain = 1). In this example, the noise is dominated by wide band amplifier noise so the resistors do not contribute significantly. However, in many cases the resistor noise can be important, so the full noise calculation is provided. For more detailed theory on this subject, refer to *Calculating the Total Noise for ADC Systems* and *Op Amps: Noise 1*.

Bandwidth for feedback loop:

$$f_c = \frac{1}{2 \cdot \pi \cdot R_f \cdot C_f} = \frac{1}{2 \cdot \pi \cdot (5.05 \text{k}\Omega) \cdot (3 \text{nF})} = 10.6 \text{kHz}$$

Noise from OPA827: 3.8nV/rtHz

$$E_{n\_amp1} = e_{n\_827} \cdot \sqrt{K_n \cdot f_c} = \left(3.8 nV / \sqrt{Hz}\right) \cdot \sqrt{(1.57) \cdot (10.6 kHz)} = 490 nV rms$$

Thermal noise density from feedback loop ( $R_{f1}$  and  $R_{g1}$ ) and RC non-inverting input ( $R_{f2}$  and  $R_{g2}$ ):

$$\begin{split} R_{eq} &= R_f \, \bigg| \, \bigg| R_g &= \frac{R_f \cdot R_g}{R_f + R_g} = \frac{(5.05 k\Omega) \cdot (10.1 k\Omega)}{5.05 k\Omega + 10.1 k\Omega} = 3.37 k\Omega \\ e_{n\_feedback} &= \sqrt{4 \cdot K_n \cdot T_K \cdot R_{eq}} = \sqrt{4 \cdot \left(1.38 \cdot 10^{-23}\right) \cdot \left(298\right) \cdot \left(3.37 k\Omega\right)} = 7.4 nV / \sqrt{Hz} \\ E_{n\_feedback} &= e_{n\_feedback} \cdot \sqrt{K_n \cdot f_c} = \left(7.4 nV / \sqrt{Hz}\right) \cdot \sqrt{(1.57) \cdot (10.6 kHz)} = 0.955 \mu V rms \end{split}$$

Noise from resistors on the non-inverting input is the same as noise from the feedback resistors.

$$E_{n input} = E_{n feedback} = 0.955 \mu Vrms$$

Total noise (in gain) referred to output of amplifier:

$$E_{n\_below\_fc} = (G_n)\sqrt{E_{n\_amp1}^2 + E_{n\_feedback}^2 + E_{n\_input}^2}$$

$$E_{n\_below\_fc} = (1.5)\sqrt{(0.49\mu V)^2 + (0.995\mu V)^2 + (0.995\mu V)^2} = 2.155\mu Vrms$$

Noise above fc is limited by the output filter (cutoff given below):

$$f_{output} = \frac{1}{2 \cdot \pi \cdot R_{filt} \cdot C_{filt}} = \frac{1}{2 \cdot \pi \cdot (49.9\Omega) \cdot (370pF)} = 8.6 MHz$$

$$E_{n\ above\ fc} = e_{n\ 827} \cdot \sqrt{K_n \cdot f_{output}} = \left(2.8 nV / \sqrt{Hz}\right) \cdot \sqrt{(1.57) \cdot (8.6 MHz)} = 13.963 \mu V$$

Total noise applied to input of the ADC:

$$E_{n\_total} = \sqrt{E_{n\_below\_fc}^2 + E_{n\_above\_fc}^2} = \sqrt{\left(2.155\mu V\right)^2 + \left(13.963\mu V\right)^2} = 14.128\mu Vrms$$

### **Noise Simulation**

The simulated results compare well with the calculated results (that is, simulated =  $15.88\mu$ Vrms, calculated =  $14.128\mu$ Vrms).

### **Stability Test**

6

The phase margin for this OPA827 driving circuit is 67.1°, which meets the >45° requirement and is stable. For detailed theory explaining stability analysis, refer to *Op Amps: Stability 1*.

#### **Design Featured Devices**

| Device      | Key Features                                                                            | Link                       | Similar Devices  |

|-------------|-----------------------------------------------------------------------------------------|----------------------------|------------------|

| ADS8568 (1) | 16-bit, 8 Channel Simultaneous-Sampling, Bipolar-Input SAR ADC                          | www.ti.com/product/ADS8568 | www.ti.com/adcs  |

| OPA827      | Low-Noise, High-Precision, JFET-Input Operational Amplifier                             | www.ti.com/product/OPA827  | www.ti.com/opamp |

| OPA192      | High-Voltage, Rail-to-Rail Input/Output, 5μV, 0.2μV/°C, Precision operational amplifier | www.ti.com/product/OPA192  | www.ti.com/opamp |

(1) The ADS8568 has integrated a precision voltage reference which can meet most design requirements, but an external REF5050 can be directly connected to the ADS8568 without any additional buffer because the ADS8568 has a built in internal reference buffer for every ADC channel pair. Also, REF5050 has the required low noise and drift for precision SAR applications. C1 is added to balance CMRR (common-mode rejection ratio). Clean analog power supplies are required to achieve best performance specified in the data sheet of the ADC.

#### **Design References**

For TI's comprehensive circuit library, refer to Analog Engineer's Circuit Cookbooks.

Trademarks | INSTRUMENTS | www.ti.com

## Link to Key Files (TINA)

Design files for this circuit – http://www.ti.com/lit/zip/sbac180.

#### **Trademarks**

All trademarks are the property of their respective owners.

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

####

# Changes from Revision \* (January 2018) to Revision A (March 2019)

**Page**

• Downstyle the title and changed title role to Data Converters. Added link to circuit cookbook landing page.... 1

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated