SBAS689D June 2015 – December 2016 AFE4404

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5

Register Map

- 8.5.1 Register 0h (address = 0h) [reset = 0h]

- 8.5.2 Register 1h (address = 1h) [reset = 0h]

- 8.5.3 Register 2h (address = 2h) [reset = 0h]

- 8.5.4 Register 3h (address = 3h) [reset = 0h]

- 8.5.5 Register 4h (address = 4h) [reset = 0h]

- 8.5.6 Register 5h (address = 5h) [reset = 0h]

- 8.5.7 Register 6h (address = 6h) [reset = 0h]

- 8.5.8 Register 7h (address = 7h) [reset = 0h]

- 8.5.9 Register 8h (address = 8h) [reset = 0h]

- 8.5.10 Register 9h (address = 9h) [reset = 0h]

- 8.5.11 Register Ah (address = Ah) [reset = 0h]

- 8.5.12 Register Bh (address = Bh) [reset = 0h]

- 8.5.13 Register Ch (address = Ch) [reset = 0h]

- 8.5.14 Register Dh (address = Dh) [reset = 0h]

- 8.5.15 Register Eh (address = Eh) [reset = 0h]

- 8.5.16 Register Fh (address = Fh) [reset = 0h]

- 8.5.17 Register 10h (address = 10h) [reset = 0h]

- 8.5.18 Register 11h (address = 11h) [reset = 0h]

- 8.5.19 Register 12h (address = 12h) [reset = 0h]

- 8.5.20 Register 13h (address = 13h) [reset = 0h]

- 8.5.21 Register 14h (address = 14h) [reset = 0h]

- 8.5.22 Register 15h (address = 15h) [reset = 0h]

- 8.5.23 Register 16h (address = 16h) [reset = 0h]

- 8.5.24 Register 17h (address = 17h) [reset = 0h]

- 8.5.25 Register 18h (address = 18h) [reset = 0h]

- 8.5.26 Register 19h (address = 19h) [reset = 0h]

- 8.5.27 Register 1Ah (address = 1Ah) [reset = 0h]

- 8.5.28 Register 1Bh (address = 1Bh) [reset = 0h]

- 8.5.29 Register 1Ch (address = 1Ch) [reset = 0h]

- 8.5.30 Register 1Dh (address = 1Dh) [reset = 0h]

- 8.5.31 Register 1Eh (address = 1Eh) [reset = 0h]

- 8.5.32 Register 20h (address = 20h) [reset = 0h]

- 8.5.33 Register 21h (address = 21h) [reset = 0h]

- 8.5.34 Register 22h (address = 22h) [reset = 0h]

- 8.5.35 Register 23h (address = 23h) [reset = 0h]

- 8.5.36 Register 29h (address = 29h) [reset = 0h]

- 8.5.37 Register 2Ah (address = 2Ah) [reset = 0h]

- 8.5.38 Register 2Bh (address = 2Bh) [reset = 0h]

- 8.5.39 Register 2Ch (address = 2Ch) [reset = 0h]

- 8.5.40 Register 2Dh (address = 2Dh) [reset = 0h]

- 8.5.41 Register 2Eh (address = 2Eh) [reset = 0h]

- 8.5.42 Register 2Fh (address = 2Fh) [reset = 0h]

- 8.5.43 Register 31h (address = 31h) [reset = 0h]

- 8.5.44 Register 32h (address = 32h) [reset = 0h]

- 8.5.45 Register 33h (address = 33h) [reset = 0h]

- 8.5.46 Register 34h (address = 34h) [reset = 0h]

- 8.5.47 Register 35h (address = 35h) [reset = 0h]

- 8.5.48 Register 36h (address = 36h) [reset = 0h]

- 8.5.49 Register 37h (address = 37h) [reset = 0h]

- 8.5.50 Register 39h (address = 39h) [reset = 0h]

- 8.5.51 Register 3Ah (address = 3Ah) [reset = 0h]

- 8.5.52 Register 3Dh (address = 3Dh) [reset = 0h]

- 8.5.53 Register 3Fh (address = 3Fh) [reset = 0h]

- 8.5.54 Register 40h (address = 40h) [reset = 0h]

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- YZP|15

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8 Detailed Description

8.1 Overview

The AFE has an integrated transmitter and receiver for optical heart-rate monitoring and pulse oximetry applications. The system is characterized by a parameter termed the pulse repetition frequency (PRF) that determines the repetition periodicity of a sequence of operations. Every cycle of a PRF results in four 24-bit digital samples at the output of the AFE, each of which is stored in a separate register.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 TIA and Switched RC Filter

The receiver input pins (INP, INM) are meant to be connected differentially to a photodiode. The signal current from the photodiode is converted to a differential voltage using a transimpedance amplifier (TIA). The TIA gain is set by its feedback resistor (Rf) and can be programmed from 10 kΩ to 2 MΩ. The transimpedance gain between the input current and output differential voltage of the TIA is equal to 2 × Rf. At the output of the TIA is a switched RC filter. There are four parallel instances of the filter, each of which are connected to the TIA output signal during one of four sampling phases.

The signal chain is kept fully differential throughout the receiver channel in order to enable excellent rejection of common-mode noise as well as noise on power supplies. For simplicity, the scheme with the four parallel filters is shown in Figure 23 for a single-ended representation of the signal chain. The ADCRST signal corresponds to the collection of active phases of four ADCRST pulses: ADCRST0, ADCRST1, ADCRST2, and ADCRST3.

8.3.1.1 Operation with Two and Three LEDs

The four sampling phases can correspond to either of the following signal state sequences received by the photodiode:

- 2-LED mode: LED2 → ambient phase 2 → LED1 → ambient phase 1

- 3-LED mode: LED2 → LED3 → LED1 → ambient

Figure 24. Sequence of Four Sampling and Conversion Phases

Figure 24. Sequence of Four Sampling and Conversion Phases

In the 2-LED mode, LED1 and LED2 are pulsed during the corresponding sampling instants. In the 3-LED mode, LED1, LED2, and LED3 are pulsed during the corresponding sampling instants. As mentioned in the TIA Gain Settings and Operation with Two and Three LEDs sections, the TIA gain (Rf) and feedback capacitor (Cf) can be programmed differently between two sets: Rf1 / Cf1 and Rf2 / Cf2. The way these sets are applied to the four phases is shown in Figure 24.

8.3.1.1.1 LED Current Setting

The default LED current range is from 0 mA to 50 mA. The individual currents of each of the three LEDs can be controlled independently, each with a separate 6-bit control.

Taken as a decimal number, the 6-bit setting provides 63 equal steps between 0 mA and 50 mA. Each increment of the ILED 6-bit code causes the LED current setting to increment by approximately 0.8 mA. For details, see register 22h.

The LED current range can be doubled by setting the ILED_2X bit to 1. The accuracy of higher current settings close to 100 mA can be low because of current saturation of the driver. Each increment of the ILED 6-bit code causes the LED current to increment by approximately 1.6 mA when ILED_2X is set to 1.

8.3.1.2 TIA Gain Settings

The TIA gain is set by programming the value of Rf (the feedback resistor of the TIA). The Rf setting is controlled using the TIA_GAIN register bit. For details see register 21h.

By default, the same TIA_GAIN setting is applied for all four phases of the receiver. Separate gains can be set for two of the four phases by setting the EN_SEP_GAIN bit. When the EN_SEP_GAIN bit is enabled, the TIA_GAIN register controls the Rf1 setting and the TIA_GAIN_SEP register controls the Rf2 settings.

Mapping of the Rf1 / Rf2 values to the two sets of 3-bit controls is described in Table 50.

8.3.1.3 TIA Bandwidth Settings

TIA bandwidth settings are similar to TIA gain settings. The TIA bandwidth is set by programming the value of Cf (the feedback capacitance of the TIA). The product of Rf and Cf gives the time constant of the TIA and must be set approximately 1/5th (or less) of the LED or sampling pulse durations. This choice of time constant allows the TIA to pass the incoming pulses from the photodiode.

Cf is controlled using the TIA_CF register bit. For details, see register 21.

By default, the same TIA_CF setting is applied for all four phases of the receiver. Similar to the TIA gain settings, a separate Cf can be set for two of the four phases by setting the EN_SEP_GAIN bit. When the EN_SEP_GAIN bit is enabled, the TIA_CF register controls the Cf1 settings and TIA_CF_SEP controls the Cf2 settings. Mapping the Cf1 / Cf2 values to the two sets of 3-bit controls is the same as illustrated in Table 51.

8.3.2 Power Management

The AFE has three independent supplies for the transmitter, receiver, and I/O.

8.3.2.1 Transmitter Supply (TX_SUP)

The transmitter supply has a range of 3.0 V to 5.25 V. In the most common arrangement, this supply can be the same supply that the anodes of the LEDs are tied to, as shown in Figure 25.

Figure 25. LED to Pin Connections

Figure 25. LED to Pin Connections

When the LEDs must be tied to a different supply, care must be taken to ensure that the LED supply is within

0.3 V of TX_SUP. This consideration of the LED supply voltage prevents the electrostatic discharge (ESD) diodes inside the AFE from turning on during the off state of the LEDs.

8.3.2.2 Receiver Supply (RX_SUP)

The receiver supply has a range of 2.0 V to 3.6 V. The AFE has internal low-dropout (LDO) regulators operating at 1.8 V that regulate both the analog and digital blocks inside the AFE. This rejection of supply noise from the internal LDOs, coupled with the differential nature of the architecture, enables excellent noise rejection on the supplies (for instance, 50-Hz noise).

8.3.2.3 I/O Supply (IO_SUP)

The I/O supply can either be tied to RX_SUP or can be separately driven. The motivation for a separate I/O supply is to interface with certain microcontrollers (MCUs) that require a 1.8-V I/O current. In this case, IO_SUP can be driven separately from RX_SUP and can be tied to 1.8 V.

8.3.2.4 Boost Converters Selection

If the supply voltage for TX_SUP (and the LEDs) is unavailable in the system, a boost converter may be required to generate the supply voltage. TI has a portfolio of boost converters from which an appropriate device can be selected. Some choices are listed in Table 1.

Table 1. TI Boost Converter Details(1)

| TI PART NUMBER | SIZE (mm, L × W × H) |

INPUT SUPPLY (V) | OUTPUT SUPPLY | TYPICAL QUIESCENT CURRENT (µA) | EXTERNAL COMPONENTS |

|---|---|---|---|---|---|

| TPS61254 | 1.2 × 1.3 × 0.625 | 2.3 to 5.5 | Different parts with a fixed voltage up to 5 V |

36 | 2 capacitors, 1 inductor |

| TPS61240 | 0.9 × 1.3 × 0.625 | 2.3 to 5.5 | 5 V (fixed) | 30 | 2 capacitors, 1 inductor |

| TPS61252 | 2 × 2 × 0.75 | 2.3 to 6 | Adjustable up to 6.5 V | 30 | 3 capacitors, 1 inductor, 4 resistors |

| TPS61220 | 2 × 2.2 × 1 | 0.7 to 5.5 | Adjustable from 1.8 V to 6 V | 5.5 | 2 capacitors, 1 inductor, 2 resistors |

8.3.3 Offset Cancellation DAC

A typical optical heart-rate signal has a dc component and an ac component. Although a higher TIA gain maximizes the ac signal at the AFE output, the magnitude of the dc component limits the maximum gain possible in the TIA. In order to decouple the affect of the dc level on the allowed ac signal gain, a current digital-to-analog converter (DAC) is placed at the input of the device. By setting a programmable cancellation current (based on the dc current signal level), the effective signal that is gained up by the TIA can be reduced. This reduction in the effective signal current into the TIA results in the ability to set a higher TIA gain than what is otherwise possible without enabling the offset correction. In each of the four phases of operation, a separate programmable current value can be set by programming four different sets of register bits. These cancellation currents are automatically presented to the input of the TIA in the appropriate phase. The ability to set a different cancellation current in each of the four phases can be used to cancel out the ambient current in the ambient phase. In the LED on phase, this ability can be used to cancel out the sum of the ambient current and dc current of the heart-rate signal. The polarities of the signal current and offset cancellation current is illustrated in Figure 26. The polarity of the offset cancellation current can be reversed by programming the POL_OFFDAC bits.

With zero input current and zero current in the offset cancellation DAC, the output of the AFE will be close to zero. Based on the channel offset, the output voltage for zero input current could be a small positive or negative value, usually in the range of several mV. With the photodiode connected as shown in Figure 26 and a signal current coming from the photodiode, the output code of the device is expected to be positive with the offset cancellation DAC set to zero (Ioffset = 0). With Ioffset set negative (POL_OFFFAC = 1), a dc offset can be subtracted from the signal and the ac signal can be amplified with a higher gain than what is otherwise possible.

Figure 26. Offset Cancellation Current Polarity Diagram

Figure 26. Offset Cancellation Current Polarity Diagram

A breakdown of the signal current and voltage levels is provided in Table 2 for a variety of signal levels. In Table 2, the current transfer ratio (CTR) is used to describe the relationship between the set LED current and the resulting photodiode current (IPD). CTR is the ratio of the photodiode current for a given LED current and is a function of the optical and mechanical parameters as well as human physiology.

Table 2. Signal Current and Voltage Levels for a Hypothetical Use Case(1)

| PHASE | ILED (mA) | CTR (µA / mA) |

Isig (µA) | Iamb (µA) | IPD (µA) | I_OFFDAC (µA) | Ieff (µA) | Rf (MΩ) | TIA_diff (V) |

|---|---|---|---|---|---|---|---|---|---|

| LED2 | 25 | 0.025 | 0.625 | 1 | 1.625 | –1.4 | 0.225 | 1 | 0.45 |

| LED3 | 50 | 0.025 | 1.25 | 1 | 2.25 | –1.87 | 0.38 | 0.5 | 0.38 |

| LED1 | 12.5 | 0.025 | 0.3125 | 1 | 1.3125 | –0.93 | 0.3825 | 0.5 | 0.3825 |

| AMB1 | 0 | 0.025 | 0 | 1 | 1 | –0.93 | 0.07 | 2 | 0.28 |

8.3.3.1 Offset Cancellation DAC Controls

The I_OFFDAC bits control the magnitude of the current subtracted (or added) at the TIA input. The POL_OFFDAC bits control the polarity of the current and determine whether the current is subtracted from or added to the input. For details, see register 3Ah.

8.3.4 Analog-to-Digital Converter (ADC)

The AFE has an ADC that provides a 22-bit representation of the current from the photodiode. The ADC codes corresponding to the various sampling phases can be read out from 24-bit registers in twos complement format. The ADC full-scale input range is ±1.2 V and spans bits 21 to 0. The mapping of the ADC input voltage to the ADC code is shown in Table 3.

Table 3. Mapping the ADC Input Voltage to the ADC Code

| DIFFERENTIAL INPUT VOLTAGE AT ADC INPUT | 24-BIT ADC OUTPUT CODE |

|---|---|

| –1.2 V | 111000000000000000000000 |

| (–1.2 / 221) V | 111111111111111111111111 |

| 0 | 000000000000000000000000 |

| (1.2 / 221) V | 000000000000000000000001 |

| 1.2 V | 000111111111111111111111 |

The two MSBs of the 24-bit word serve as sign-extension bits to the 22-bit ADC code and are equal to the MSB of the 22-bit ADC code when the input to the ADC is within its full-scale range, as shown in Table 4.

Table 4. Using Sign-Extension Bits to Determine the Input Operating Voltage

| BITS 23-21 | INPUT STATUS |

|---|---|

| 000 | Positive and lower than positive full-scale (within full-scale range) |

| 111 | Negative and higher than negative full-scale (within full-scale range) |

| 001 | Positive and higher than positive full-scale (outside full-scale range) |

| 110 | Negative and lower than negative full-scale (outside full-scale range) |

Noted that the TIA has an operating range of ±1 V even though the ADC input full-scale range is ±1.2 V, as shown in Figure 27. When setting the TIA gain, ensure that the signal at the TIA output does not exceed ±1 V.

Figure 27. TIA and ADC Dynamic Ranges

Figure 27. TIA and ADC Dynamic Ranges

8.3.5 I2C Interface

The AFE has an I2C interface for communication. The I2C_CLK and I2C_DAT lines require external pullup resistors to IO_SUP. See the I2C protocol standards documents for details of the I2C interface. This section only describes certain key features of the interface. The data on I2C_DAT must be stable during the high level of I2C_CLK and may transition during the low level of I2C_CLK, as shown in Figure 28.

Figure 28. Allowed Transition of I2C_DAT while Transmission of Data Bits

Figure 28. Allowed Transition of I2C_DAT while Transmission of Data Bits

The start condition is indicated by a high-to-low transition of the I2C_DAT line when the I2C_CLK is high. A stop condition is indicated by a low-to-high transition of the I2C_DAT line when the I2C_CLK is high. Figure 29 shows the start and stop conditions.

Figure 29. Transition of I2C_DAT during Start and Stop Conditions

Figure 29. Transition of I2C_DAT during Start and Stop Conditions

With the previously mentioned protocols for data, start, and stop conditions in place, the write and read operations are as shown in Figure 30 and Figure 31, respectively. In Figure 30 and Figure 31, the slave address for the AFE (indicated as SA6 to SA0) is a 7-bit representation of address 58h. The R/W bit is the read/write bit and is set to '1' for Read and '0' for Write. Only the ADC output registers (addressed from 2Ah to 2Fh) can be read out without the need for setting the REG_READ bit. Prior to reading out any other register, the REG_READ bit needs to be additionally set to '1'. In Figure 30 and Figure 31, the activity performed by the host is shown in black whereas activity from the AFE is shown in red. Thus, after the host sends the slave address during a write operation, the AFE pulls the I2C_DAT line low (shown as ACK) if the slave address matches 58h. Similarly, the host pulls the I2C_DAT line high (shown as NACK) as acknowledgment of a successfully completed read operation involving three bytes of data. Continuous read/write mode is not supported.

Figure 31. I2C Read Option Timing1

Figure 31. I2C Read Option Timing1

8.3.6 Timing Engine

The AFE has a fully-integrated timing engine that can be programmed to generate all clock phases for synchronized transmit drive, receive sampling, and data conversion. To enable the timing engine (after powering up the device), enable the TIMEREN bit.

8.3.6.1 Timer and PRF Controls

The timing engine inside the AFE has a 16-bit counter. The duration of the count with respect to an internal clock (the timer clock) determines the pulse repetition period. The pulse repetition frequency (PRF) can be set using the PRPCT register bits that represent the high value of the counter (the low value of the counter is 0). The counter automatically counts until reaching PRPCT and then returns to 0 to start the next count. To suspend the count and keep the counter in reset state, enable the TM_COUNT_RST bit.

8.3.6.2 Timing Control Registers

The start and stop counts for the various dynamic signals generated by the timing engine are shown in Table 5. The timing edge numbers are in reference to Figure 32.

Table 5. Timing Register and Edge Details

| TIMING SIGNAL | DESCRIPTION | REGISTER ADDRESS (Hex) | TIMING EDGE |

|---|---|---|---|

| LED2STC | Sample LED2 start | 1h | TE3 |

| LED2ENDC | Sample LED2 end | 2h | TE4 |

| LED1LEDSTC | LED1 start | 3h | TE17 |

| LED1LEDENDC | LED1 end | 4h | TE18 |

| ALED2STC\LED3STC | Sample ambient 2 (or sample LED3) start | 5h | TE11 |

| ALED2ENDC\LED3ENDC | Sample ambient 2 (or sample LED3) end | 6h | TE12 |

| LED1STC | Sample LED1 start | 7h | TE19 |

| LED1ENDC | Sample LED1 end | 8h | TE20 |

| LED2LEDSTC | LED2 start | 9h | TE1 |

| LED2LEDENDC | LED2 end | Ah | TE2 |

| ALED1STC | Sample ambient 1 start | Bh | TE25 |

| ALED1ENDC | Sample ambient 1 end | Ch | TE26 |

| LED2CONVST | LED2 convert phase start | Dh | TE7 |

| LED2CONVEND | LED2 convert phase end | Eh | TE8 |

| ALED2CONVST\LED3CONVST | Ambient 2 (or LED3) convert phase start | Fh | TE15 |

| ALED2CONVEND\LED3CONVEND | Ambient 2 (or LED3) convert phase end | 10h | TE16 |

| LED1CONVST | LED1 convert phase start | 11h | TE23 |

| LED1CONVEND | LED1 convert phase end | 12h | TE24 |

| ALED1CONVST | Ambient 1 convert phase start | 13h | TE29 |

| ALED1CONVEND | Ambient 1 convert phase end | 14h | TE30 |

| ADCRSTSTCT0 | ADC reset phase 0 start | 15h | TE5 |

| ADCRSTENDCT0 | ADC reset phase 0 end | 16h | TE6 |

| ADCRSTSTCT1 | ADC reset phase 1 start | 17h | TE13 |

| ADCRSTENDCT1 | ADC reset phase 1 end | 18h | TE14 |

| ADCRSTSTCT2 | ADC reset phase 2 start | 19h | TE21 |

| ADCRSTENDCT2 | ADC reset phase 2 end | 1Ah | TE22 |

| ADCRSTSTCT3 | ADC reset phase 3 start | 1Bh | TE27 |

| ADCRSTENDCT3 | ADC reset phase 3 end | 1Ch | TE28 |

When three LEDs are used within a single period, the Ambient2 phase is replaced by the LED3 phase. The timing controls for driving the third LED are as shown in Table 6.

Table 6. Timing Controls for Driving the Third LED

| TIMING SIGNAL | DESCRIPTION | REGISTER ADDRESS (Hex) | TIMING EDGE |

|---|---|---|---|

| LED3LEDSTC | LED3 start | 36h | TE9 |

| LED3LEDENDC | LED3 end | 37h | TE10 |

The timing diagram for when all three LEDs are active is shown in Figure 32.

Figure 32. Timing Diagram

Figure 32. Timing Diagram

8.3.6.3 Receiver Timing

The timing engine can be programmed to set the different phases of the receiver. The relative timings of the LED phase, sampling phase, ADC reset phase, and ADC conversion phases are shown in Figure 33 and Table 7.

Figure 33. Receiver Timing Guidelines

Figure 33. Receiver Timing Guidelines

Table 7. Receiver Timing Details

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| t1 | Start of LED to start of sampling | Max [25, (0.2 × LED pulse duration)] | µs | |

| t2 | End of LED to start of ADC reset phase | 2 | Counts(1) | |

| t3 | Duration of ADC reset phase | 6 | Counts | |

| t4 | End of ADC reset phase to start of ADC conversion phase | 2 | 2 | Count |

| t5 | Duration of ADC conversion phase(2) | (NUMAV + 2) × 200 × tADC + 15(3) | µs | |

The fourth ADCRST signal (ADCRST3) in a period also defines the start of the ADC_RDY pulse. The rising edge of the ADC_RDY signal can be used as an interrupt by the MCU to readout the registers corresponding to the preceding four conversions in that period. If any of the four conversion phases are not needed, then their duration can be set to 0. However, the corresponding ADCRSTx pulse must still be defined. All four ADCRSTx pulses must be defined in order to generate the ADC_RDY pulse. A scheme of the ADC_RDY pulse generation is shown in Figure 34. The ADC_RDY pulse timing is shown in Table 8.

Figure 34. ADC_RDY Generation Scheme

Figure 34. ADC_RDY Generation Scheme

Table 8. ADC_RDY Timing Details

| TYP | MAX | UNIT | ||

|---|---|---|---|---|

| t6 | End of fourth ADC reset phase to start of ADC_RDY pulse | (NUMAV + 1) × 200 × tADC | (NUMAV + 2) × 200 × tADC + 15 | µs |

| t7 | ADC_RDY pulse duration | tADC(1) | µs | |

8.3.6.4 Dynamic Power-Down Timing

The dynamic power-down feature can be used to shut down the receiver inside every cycle to save power, as shown in Figure 35 and Table 9.

Figure 35. Dynamic Power-Down Timing Diagram

Figure 35. Dynamic Power-Down Timing Diagram

Table 9. Dynamic Power-Down Timing Details

| MIN | UNIT | ||

|---|---|---|---|

| t8 | End of 4th conversion phase to the start of PDNCYCLE | 200 | µs |

| t9 | End of PDNCYCLE to start of next period | 200 | µs |

The timing controls for the PDNCYCLE pulse are shown in Table 10.

8.3.6.5 Sample Register Values

Table 11 lists a sample of the register settings for generating the different timing signals. These sample settings correspond to CLK_INT = 4 MHz and a PRF of 100 Hz. Three LEDs are used in a cycle, each with a duty cycle of 1%, corresponding to a pulse duration of 100 µs. The conversion durations are set in order to accommodate four averages (NUMAV = 3). Two cases are described in Table 11: one for CLKDIV_PRF = 1 (CLK_TE = 4 MHz) and the other for CLKDIV_PRF = 16 (CLK_TE = 250 kHz).

Table 11. Sample Register Settings

| SIGNAL(3) | REGISTER FIELD | NO DIVISION OF CLOCK TO TIMING ENGINE CLOCK (CLKDIV_PRF = 1) |

ADC CLOCK TO TIMING ENGINE CLOCK DIVIDED BY 16 (CLKDIV_PRF = 16) |

||

|---|---|---|---|---|---|

| TIME DURATION (µs) | REGISTER SETTING(1) | TIME DURATION (µs) | REGISTER SETTING(1) | ||

| PRF COUNTER | PRPCT | 10000 | 39999(2) | 10000 | 2499(2) |

| LED2 | LED2LEDSTC | 100 | 0 | 100 | 0 |

| LED2LEDENDC | 399 | 24 | |||

| SLED2 | LED2STC | 75 | 100 | 72 | 7 |

| LED2ENDC | 399 | 24 | |||

| ADCRST0 | ADCRSTSTCT0 | 1.75 | 401 | 4 | 26 |

| ADCRSTENDCT0 | 407 | 26 | |||

| CONVLED2 | LED2CONVST | 265 | 409 | 268 | 28 |

| LED2CONVEND | 1468 | 94 | |||

| LED3 | LED3LEDSTC | 100 | 401 | 100 | 26 |

| LED3LEDENDC | 800 | 50 | |||

| SLED3 | ALED2STC\ LED3STC |

75 | 501 | 72 | 33 |

| ALED2ENDC\ LED3ENDC |

800 | 50 | |||

| ADCRST1 | ADCRSTSTCT1 | 1.75 | 1470 | 4 | 96 |

| ADCRSTENDCT1 | 1476 | 96 | |||

| CONVLED3 | ALED2CONVST\ LED3CONVST |

265 | 1478 | 268 | 98 |

| ALED2CONVEND\ LED3CONVEND |

2537 | 164 | |||

| LED1 | LED1LEDSTC | 100 | 802 | 100 | 52 |

| LED1LEDENDC | 1201 | 76 | |||

| SLED1 | LED1STC | 75 | 902 | 72 | 59 |

| LED1ENDC | 1201 | 76 | |||

| ADCRST2 | ADCRSTSTCT2 | 1.75 | 2539 | 4 | 166 |

| ADCRSTENDCT2 | 2545 | 166 | |||

| CONVLED1 | LED1CONVST | 265 | 2547 | 268 | 168 |

| LED1CONVEND | 3606 | 234 | |||

| SLED_AMB | ALED1STC | 75 | 1303 | 72 | 85 |

| ALED1ENDC | 1602 | 102 | |||

| ADCRST3 | ADCRSTSTCT3 | 1.75 | 3608 | 4 | 236 |

| ADCRSTENDCT3 | 3614 | 236 | |||

| CONVLED_AMB | ALED1CONVST | 265 | 3616 | 268 | 238 |

| ALED1CONVEND | 4675 | 304 | |||

| PDNCYCLE | PDNCYCLESTC | 8431.25 | 5475 | 8384 | 354 |

| PDNCYCLEENDC | 39199 | 2449 | |||

The timing described in Table 11 minimizes the active time, thereby enabling the signal chain to be in the dynamic power-down state for the maximum fraction of time. In this timing, the LED active phase overlaps with the conversion phase corresponding to a previous LED. The ground bounce from the LED switching can couple into the receiver and cause a small interference between one phase and the next. In most intended applications, this bounce is not expected to cause any problems. However, if the lowest level of interference across phases must be attained, the timing registers can be programmed as shown in Table 12.

Table 12. Sample Register Settings for Low Interference Across Phases

| SIGNAL(3) | REGISTER FIELD | NO DIVISION OF CLOCK TO TIMING ENGINE CLOCK (CLKDIV_PRF = 1) |

|

|---|---|---|---|

| TIME DURATION (µs) | REGISTER SETTING | ||

| PRF COUNTER | PRPCT | 10000 | 39999 |

| LED2 | LED2LEDSTC | 99.75 | 0 |

| LED2LEDENDC | 398 | ||

| SLED2 | LED2STC | 74.75 | 100 |

| LED2ENDC | 398 | ||

| ADCRST0 | ADCRSTSTCT0 | 1.75 | 5600 |

| ADCRSTENDCT0 | 5606 | ||

| CONVLED2 | LED2CONVST | 115 | 5608 |

| LED2CONVEND | 6067 | ||

| LED3 | LED3LEDSTC | 99.75 | 400 |

| LED3LEDENDC | 798 | ||

| SLED3 | ALED2STC\ LED3STC |

74.75 | 500 |

| ALED2ENDC\ LED3ENDC |

798 | ||

| ADCRST1 | ADCRSTSTCT1 | 1.75 | 6069 |

| ADCRSTENDCT1 | 6075 | ||

| CONVLED3 | ALED2CONVST\ LED3CONVST |

115 | 6077 |

| ALED2CONVEND\ LED3CONVEND |

6536 | ||

| LED1 | LED1LEDSTC | 99.75 | 800 |

| LED1LEDENDC | 1198 | ||

| SLED1 | LED1STC | 74.75 | 900 |

| LED1ENDC | 1198 | ||

| ADCRST2 | ADCRSTSTCT2 | 1.75 | 6538 |

| ADCRSTENDCT2 | 6544 | ||

| CONVLED1 | LED1CONVST | 115.25 | 6546 |

| LED1CONVEND | 7006 | ||

| SLED_AMB | ALED1STC | 74.75 | 1300 |

| ALED1ENDC | 1598 | ||

| ADCRST3 | ADCRSTSTCT3 | 1.75 | 7008 |

| ADCRSTENDCT3 | 7014 | ||

| CONVLED_AMB | ALED1CONVST | 115 | 7016 |

| ALED1CONVEND | 7475 | ||

| PDNCYCLE | PDNCYCLESTC | 7881.25 | 7675 |

| PDNCYCLEENDC | 39199 | ||

8.4 Device Functional Modes

8.4.1 Power Modes

The AFE has the following power modes:

- Normal mode.

- Hardware power-down mode (PWDN): this mode is set using the RESETZ pin. When the RESETZ pin is pulled low for more than 200 µs, the device enters hardware power-down mode where the power consumption is very low (of a few µA).

- Software power-down mode (PDNAFE) using a register bit.

- Dynamic power-down mode: this mode is enabled by setting the start and end points of the PDN_CYCLE signal that is controlled using the timing engine. During the PDN_CYCLE high phase, the functional blocks (as selected by the DYNAMICx bits) are powered down. When powering down the TIA in dynamic power-down mode, consideration must be given to the dynamics of the photodiode. When the TIA is powered down, the feedback mechanism is no longer available to maintain zero bias across the photodiode, resulting in a voltage drift across the photodiode. When the AFE comes out of dynamic power-down into active mode, a transient recovery time for the photodiode results. Additionally, the INP, INM pins can be shorted through a switch to an internal reference voltage (VCM) to keep the photodiode in zero bias whenever the TIA is in power-down mode. Maintaining zero bias across the photodiode is accomplished by setting the ENABLE_INPUT_SHORT bit to 1. By setting this bit in conjunction with the DYNAMIC3 bit, the dynamics of the photodiode can be better controlled during the dynamic power-down mode.

8.4.2 RESET Modes

The AFE has internal registers that must be reset before valid operation. There are two ways to reset the device:

- Either through the RESETZ pin (a reset signal can be issued by pulsing the RESETZ pin low for a duration of time between 25 to 50 µs) or

- A software reset via the SW_RESET register bit.

8.4.3 Clocking Modes

The AFE has an internal oscillator that can generate a 4-MHz clock. This clock can be made to come out of the CLK pin for use by the rest of the system. The default mode is to use an external clock. The frequency range of this external clock is between 4 MHz to 60 MHz. A programmable internal division ratio between 1 to 12 must be set so that the divided clock is between 4 MHz to 6 MHz. For high-accuracy measurements, operating the AFE using an input (external) clock with high accuracy is preferable. If a high-accuracy measurement is required when using the internal oscillator, a correction scheme can be used in the MCU to digitally compensate for the inaccuracy in the oscillator. One method of this approach is to accurately estimate the PRF by measuring the ADC_RDY periodicity in terms of a high-accuracy MCU clock (for example, a 32-kHz clock) to establish the accurate PRF. This information can then be used to digitally correct the heart rate computation.

8.4.4 PRF Programmability

By default, the internal clock is 4 MHz. This clock also goes to the timing engine that has a 16-bit counter. The maximum setting of this counter (all 16 bits set to 1) determines the lowest value of PRF, resulting in a minimum PRF of 61 Hz. To extend the lower range of PRF, an independent programmable divider is introduced in the clock going to the timing engine. By programming this divider between 1 to 16 with the CLKDIV_PRF register control, the lower range of PRF can be extended from 61 Hz to approximately 4 Hz (limit the minimum PRF to

10 Hz). The various clocking domains and controls are described in Figure 36 and Table 13.

Figure 36. Clocking Domains Diagram

Figure 36. Clocking Domains Diagram

Table 13. Clock Domains and Operating Ranges

| CLOCK | DESCRIPTION | FREQUENCY | FREQUENCY RANGE | COMMENTS |

|---|---|---|---|---|

| CLK_INT | Clock generated by the internal oscillator | fINT | 4 MHz (1) | Internal clock when the oscillator is enabled |

| CLK_EXT | External clock | fEXT | 4 MHz to 60 MHz | Set the division ratio with CLKDIV_EXTMODE so that CLK_ADC is 4 MHz to 6 MHz |

| CLK_ADC | Clock used by the ADC for conversion | fADC | 4 MHz to 6 MHz | Selected as either an internal clock or a divided version of the external clock |

| CLK_TE | Clock used by the timing engine | fTE | fADC divided by 1 to 16 | Division ratio is set by CLKDIV_PRF |

| ADC_RDY | Interrupt to MCU at the same rate as the PRF | fPRF | Limit to 10 Hz-1000 Hz, limited to 1000 / (division ratio as set by CLKDIV_PRF) | Set by PRPCT and fTE |

8.4.5 Averaging Modes

To reduce the noise, the input to the ADC (sampled on the CSAMPx capacitors) can be converted by the ADC multiple times and averaged. The number of averages is set using the NUMAV register control based on Equation 1:

By default, NUMAV = 0. Therefore, the default mode corresponds to when the ADC converts its input one time in each of the four phases and stores the content in the register corresponding to that phase.

When NUMAV is programmed (for example if NUMAV = 3), the ADC converts its input four times in each phase, averages the four conversions, and stores the averaged value in the register corresponding to that phase.

Averaging only helps in reducing ADC noise and not the front end noise because the input to the ADC is the same sampled voltage across all the ADC conversions used to generate the average (this voltage corresponds to the voltage sampled on the four CSAMPx capacitors in Figure 23). The number of samples that can be averaged ranges from 1 to 16 (when NUMAV is programmed from 0 to 15). A higher number of averages results in larger conversion times; see Table 7.

Averaging is implemented in the following manner:

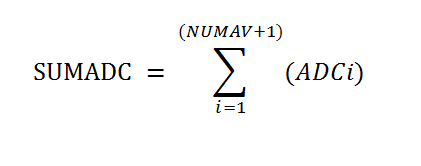

The number of ADC samples corresponding to the number of averages (NUMAV + 1) are accumulated, as shown in Equation 2.

where

- ADCi = the ith sample converted by the ADC.

The accumulator output (SUMADC) is then divided by a factor D that is obtained by D = 128 ÷ X , with X being an integer.

The averaged output is shown in Equation 3:

where

- D = 128 ÷ X, with X being an integer.

This implementation gives an averaging function that is exact when the number of averages is a power of 2 but deviates from ideal values for other settings, as shown in Table 14.

8.4.6 Decimation Mode

The AFE4404 has a decimation mode that can be used to improve the performance at low pulse repetition frequencies (PRFs). In this mode, up to N (N = 2, 4, 8, or 16) consecutive data samples can be averaged. The averaged output comes out one time every N clock cycles. The ADC_RDY frequency also reduces to PRF / N.

A timing diagram is shown in Figure 37 for where the decimation factor = 4 and PRF = 100 Hz. Figure 37 is only intended to illustrate the change in periodicity of ADC_RDY and the update rate of the registers relative to the pulse repetition period. However, the timing of all other signals continues to be as per the descriptions mentioned in the Timing Engine section.

Figure 37. Decimation Mode Enabled Timing Diagram

Figure 37. Decimation Mode Enabled Timing Diagram(Decimation Factor = 4, PRF = 100 Hz)

8.4.6.1 Decimation Mode Power and Performance

The main advantage of the decimation mode is that this mode can be used to reduce the readout rate of the MCU because the data rate reduces by the decimation factor. Normally, reducing the data rate leads to SNR loss. However, with decimation mode, there is no SNR loss regardless of the lower data rate because of the averaging of consecutive samples. Table 15 compares different modes of operation.

Table 15. Different Modes of Operation

| MODE | RATE OF DEVICE SAMPLES AND CONVERSIONS | RATE OF MCU DATA READS | RELATIVE PERFORMANCE |

|---|---|---|---|

| No decimation, 100-Hz PRF | 100 Hz | 100 Hz | Reference |

| No decimation, 25-Hz PRF | 25 Hz | 25 Hz | SNR is approximately 6 dB lower than reference |

| 4X decimation mode, 100-Hz PRF |

100 Hz | 25 Hz | SNR is comparable to reference |

8.5 Register Map

Table 16. Register Map(1)

| ADDRESS (Hex) | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SW_RESET | 0 | TM_COUNT_RST | REG_READ |

| 01h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED2STC | |||||||||||||||

| 02h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED2ENDC | |||||||||||||||

| 03h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED1LEDSTC | |||||||||||||||

| 04h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED1LEDENDC | |||||||||||||||

| 05h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED2STC\LED3STC | |||||||||||||||

| 06h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED2ENDC\LED3ENDC | |||||||||||||||

| 07h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED1STC | |||||||||||||||

| 08h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED1ENDC | |||||||||||||||

| 09h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED2LEDSTC | |||||||||||||||

| 0Ah | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED2LEDENDC | |||||||||||||||

| 0Bh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED1STC | |||||||||||||||

| 0Ch | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED1ENDC | |||||||||||||||

| 0Dh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED2CONVST | |||||||||||||||

| 0Eh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED2CONVEND | |||||||||||||||

| 0Fh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED2CONVST\LED3CONVST | |||||||||||||||

| 10h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED2CONVEND\LED3CONVEND | |||||||||||||||

| 11h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED1CONVST | |||||||||||||||

| 12h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED1CONVEND | |||||||||||||||

| 13h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED1CONVST | |||||||||||||||

| 14h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ALED1CONVEND | |||||||||||||||

| 15h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTSTCT0 | |||||||||||||||

| 16h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTENDCT0 | |||||||||||||||

| 17h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTSTCT1 | |||||||||||||||

| 18h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTENDCT1 | |||||||||||||||

| 19h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTSTCT2 | |||||||||||||||

| 1Ah | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTENDCT2 | |||||||||||||||

| 1Bh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTSTCT3 | |||||||||||||||

| 1Ch | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ADCRSTENDCT3 | |||||||||||||||

| 1Dh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PRPCT | |||||||||||||||

| 1Eh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | TIMEREN | 0 | 0 | 0 | 0 | NUMAV | |||

| 20h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ENSEPGAIN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | TIA_CF_SEP | TIA_GAIN_SEP | ||||

| 21h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PROG_TG_EN | 0 | 0 | TIA_CF | TIA_GAIN | ||||

| 22h | 0 | 0 | 0 | 0 | 0 | 0 | ILED3 | ILED2 | ILED1 | |||||||||||||||

| 23h | 0 | 0 | 0 | DYNAMIC1 | 0 | 0 | ILED_2X | 0 | 0 | DYNAMIC2 | 0 | 0 | 0 | 0 | OSC_ENABLE | 0 | 0 | 0 | 0 | DYNAMIC3 | DYNAMIC4 | 0 | PDNRX | PDNAFE |

| 28h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 29h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ENABLE_CLKOUT | 0 | 0 | 0 | 0 | CLKDIV_CLKOUT | 0 | |||

| 2Ah | LED2VAL | |||||||||||||||||||||||

| 2Bh | ALED2VAL\LED3VAL | |||||||||||||||||||||||

| 2Ch | LED1VAL | |||||||||||||||||||||||

| 2Dh | ALED1VAL | |||||||||||||||||||||||

| 2Eh | LED2-ALED2VAL(2) | |||||||||||||||||||||||

| 2Fh | LED1-ALED1VAL | |||||||||||||||||||||||

| 31h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PD_DISCONNECT | 0 | 0 | 0 | 0 | ENABLE_INPUT_SHORT | 0 | 0 | CLKDIV_EXTMODE | ||

| 32h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PDNCYCLESTC | |||||||||||||||

| 33h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PDNCYCLEENDC | |||||||||||||||

| 34h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PROG_TG_STC | |||||||||||||||

| 35h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PROG_TG_ENDC | |||||||||||||||

| 36h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED3LEDSTC | |||||||||||||||

| 37h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | LED3LEDENDC | |||||||||||||||

| 39h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | CLKDIV_PRF | ||

| 3Ah | 0 | 0 | 0 | 0 | POL_OFFDAC_LED2 | I_OFFDAC_LED2 | POL_OFFDAC_AMB1 | I_OFFDAC_AMB1 | POL_OFFDAC_LED1 | I_OFFDAC_LED1 | POL_OFFDAC_AMB2\POL_OFFDAC_LED3 | I_OFFDAC_AMB2\ I_OFFDAC_LED3 |

||||||||||||

| 3Dh | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DEC_EN | 0 | DEC_FACTOR | 0 | ||

| 3Fh | AVG_LED2-ALED2VAL | |||||||||||||||||||||||

| 40h | AVG_LED1-ALED1VAL | |||||||||||||||||||||||

8.5.1 Register 0h (address = 0h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | 0 | SW_RESET | 0 | TM_COUNT_ RST |

REG_READ |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| LEGEND: W = Write only; -n = value after reset |

Table 17. Register 0h Field Descriptions

8.5.2 Register 1h (address = 1h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2STC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2STC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 18. Register 1h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED2STC | R/W | 0h | Sample LED2 start |

8.5.3 Register 2h (address = 2h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2ENDC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2ENDC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 19. Register 2h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED2ENDC | R/W | 0h | Sample LED2 end |

8.5.4 Register 3h (address = 3h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1LEDSTC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1LEDSTC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 20. Register 3h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED1LEDSTC | R/W | 0h | LED1 start |

8.5.5 Register 4h (address = 4h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1LEDENDC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1LEDENDC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 21. Register 4h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED1LEDENDC | R/W | 0h | LED1 end |

8.5.6 Register 5h (address = 5h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED2STC\LED3STC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED2STC\LED3STC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 22. Register 5h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED2STC\LED3STC | R/W | 0h | Sample ambient 2 (or sample LED3) start |

8.5.7 Register 6h (address = 6h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED2ENDC\LED3ENDC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED2ENDC\LED3ENDC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 23. Register 6h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED2ENDC\LED3ENDC | R/W | 0h | Sample ambient 2 (or sample LED3) end |

8.5.8 Register 7h (address = 7h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1STC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1STC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 24. Register 7h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED1STC | R/W | 0h | Sample LED1 start |

8.5.9 Register 8h (address = 8h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1ENDC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1ENDC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 25. Register 8h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED1ENDC | R/W | 0h | Sample LED1 end |

8.5.10 Register 9h (address = 9h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2LEDSTC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2LEDSTC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 26. Register 9h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED2LEDSTC | R/W | 0h | LED2 start |

8.5.11 Register Ah (address = Ah) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2LEDENDC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2LEDENDC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 27. Register Ah Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED2LEDENDC | R/W | 0h | LED2 end |

8.5.12 Register Bh (address = Bh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED1STC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED1STC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 28. Register Bh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED1STC | R/W | 0h | Sample ambient 1 start |

8.5.13 Register Ch (address = Ch) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED1ENDC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED1ENDC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 29. Register Ch Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED1ENDC | R/W | 0h | Sample ambient 1 end |

8.5.14 Register Dh (address = Dh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2CONVST | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2CONVST | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 30. Register Dh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED2CONVST | R/W | 0h | LED2 convert phase start |

8.5.15 Register Eh (address = Eh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2CONVEND | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2CONVEND | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 31. Register Eh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED2CONVEND | R/W | 0h | LED2 convert phase end |

8.5.16 Register Fh (address = Fh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED2CONVST\LED3CONVST | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED2CONVST\LED3CONVST | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 32. Register Fh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED2CONVST\LED3CONVST | R/W | 0h | Ambient 2 (or LED3) convert phase start |

8.5.17 Register 10h (address = 10h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED2CONVEND\LED3CONVEND | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED2CONVEND\LED3CONVEND | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 33. Register 10h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED2CONVEND\LED3CONVEND | R/W | 0h | Ambient 2 (or LED3) convert phase end |

8.5.18 Register 11h (address = 11h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1CONVST | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1CONVST | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 34. Register 11h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED1CONVST | R/W | 0h | LED1 convert phase start |

8.5.19 Register 12h (address = 12h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1CONVEND | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1CONVEND | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 35. Register 12h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | LED1CONVEND | R/W | 0h | LED1 convert phase end |

8.5.20 Register 13h (address = 13h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED1CONVST | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED1CONVST | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 36. Register 13h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0 |

| 15-0 | ALED1CONVST | R/W | 0h | Ambient 1 convert phase start |

8.5.21 Register 14h (address = 14h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED1CONVEND | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED1CONVEND | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 37. Register 14h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ALED1CONVEND | R/W | 0h | Ambient 1 convert phase end |

8.5.22 Register 15h (address = 15h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTSTCT0 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTSTCT0 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 38. Register 15h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTSTCT0 | R/W | 0h | ADC reset phase 0 start |

8.5.23 Register 16h (address = 16h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTENDCT0 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTENDCT0 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 39. Register 16h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTENDCT0 | R/W | 0h | ADC reset phase 0 end |

8.5.24 Register 17h (address = 17h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTSTCT1 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTSTCT1 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 40. Register 17h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTSTCT1 | R/W | 0h | ADC reset phase 1 start |

8.5.25 Register 18h (address = 18h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTENDCT1 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTENDCT1 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 41. Register 18h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTENDCT1 | R/W | 0h | ADC reset phase 1 end |

8.5.26 Register 19h (address = 19h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTSTCT2 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTSTCT2 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 42. Register 19h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTSTCT2 | R/W | 0h | ADC reset phase 2 start |

8.5.27 Register 1Ah (address = 1Ah) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTENDCT2 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTENDCT2 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 43. Register 1Ah Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTENDCT2 | R/W | 0h | ADC reset phase 2 end |

8.5.28 Register 1Bh (address = 1Bh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTSTCT3 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTSTCT3 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 44. Register 1Bh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTSTCT3 | R/W | 0h | ADC reset phase 3 start |

8.5.29 Register 1Ch (address = 1Ch) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ADCRSTENDCT3 | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCRSTENDCT3 | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 45. Register 1Ch Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | ADCRSTENDCT3 | R/W | 0h | ADC reset phase 3 end |

8.5.30 Register 1Dh (address = 1Dh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| PRPCT | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PRPCT | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 46. Register 1Dh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15-0 | PRPCT | R/W | 0h | These bits are the count value for the counter that sets the PRF. The counter automatically counts until PRPCT and then returns back to 0 to start the next count. |

8.5.31 Register 1Eh (address = 1Eh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | TIMEREN |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | R/W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | 0 | NUMAV | |||

| W-0h | W-0h | W-0h | W-0h | R/W-0h | |||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 47. Register 1Eh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-9 | 0 | W | 0h | Must write 0. |

| 8 | TIMEREN | R/W | 0h | 0 = Timer module disabled 1 = Enables timer module. This bit enables the timing engine that can be programmed to generate all clock phases for the synchronized transmit drive, receive sampling, and data conversion. |

| 7-4 | 0 | W | 0h | Must write 0. |

| 3-0 | NUMAV | R/W | 0h | These bits determine the number of ADC averages. By programming a higher ADC conversion time, the ADC can be set to do multiple conversions and average these multiple conversions to achieve lower noise. This programmability is set with the NUMAV bit control. The number of samples that are averaged is represented by the decimal equivalent of NUMAV + 1. For example, NUMAV = 0 represents no averaging, NUMAV = 2 represents averaging of three samples, and NUMAV = 15 represents averaging of 16 samples. |

8.5.32 Register 20h (address = 20h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ENSEPGAIN | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | TIA_CF_SEP | TIA_GAIN_SEP | ||||

| W-0h | W-0h | R/W-0h | R/W-0h | ||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 48. Register 20h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |

| 15 | ENSEPGAIN | R/W | 0h | 0 = Single TIA gain for all phases 1 = Enables two separate sets of TIA gains |

| 14-6 | 0 | W | 0h | Must write 0. |

| 5-3 | TIA_CF_SEP | R/W | 0h | When ENSEPGAIN = 1, TIA_CF_SEP is the control for the Cf2 setting. |

| 2-0 | TIA_GAIN_SEP | R/W | 0h | When ENSEPGAIN = 1, TIA_GAIN_SEP is the control for the Rf2 setting. |

8.5.33 Register 21h (address = 21h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | PROG_TG_EN |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | TIA_CF | TIA_GAIN | ||||

| W-0h | W-0h | R/W-0h | R/W-0h | ||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 49. Register 21h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-9 | 0 | W | 0h | Must write 0. |

| 8 | PROG_TG_EN | W | 0h | This bit replaces the ADC_RDY output with a fully-programmable signal from the timing engine. The start and end points of this signal are set using the PROG_TG_STC and PROG_TG_ENDC controls. |

| 7-6 | 0 | W | 0h | Must write 0. |

| 5-3 | TIA_CF | R/W | 0h | When ENSEPGAIN = 0, these bits control the Cf setting (both Cf1 and Cf2); see Table 51 for details. When ENSEPGAIN = 1, these bits control the Cf1 setting. |

| 2-0 | TIA_GAIN | R/W | 0h | When ENSEPGAIN = 0, these bits control the Rf setting (both Rf1 and Rf2); see Table 50 for details. When ENSEPGAIN = 1, these bits control the Rf1 setting. |

Table 50. TIA_GAIN Register Settings

| TIA_GAIN, TIA_GAIN_SEP REGISTER VALUE | Rf |

|---|---|

| 0 | 500 kΩ |

| 1 | 250 kΩ |

| 2 | 100 kΩ |

| 3 | 50 kΩ |

| 4 | 25 kΩ |

| 5 | 10 kΩ |

| 6 | 1 MΩ |

| 7 | 2 MΩ |

Table 51. TIA_CF Register Settings

| TIA_CF, TIA_CF_SEP REGISTER VALUE | Cf |

|---|---|

| 0 | 5 pF |

| 1 | 2.5 pF |

| 2 | 10 pF |

| 3 | 7.5 pF |

| 4 | 20 pF |

| 5 | 17.5 pF |

| 6 | 25 pF |

| 7 | 22.5 pF |

8.5.34 Register 22h (address = 22h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | ILED3 | |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | R/W-0h | |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ILED3 | ILED2 | ||||||

| R/W-0h | R/W-0h | ||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ILED2 | ILED1 | ||||||

| R/W-0h | R/W-0h | ||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 52. Register 22h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-18 | 0 | W | 0h | Must write 0. |

| 17-12 | ILED3 | R/W | 0h | LED3 current control |

| 11-6 | ILED2 | R/W | 0h | LED2 current control |

| 5-0 | ILED1 | R/W | 0h | LED1 current control. Increments of the LED1 current setting are listed in Table 53. |

Table 53. ILED1 Register Settings

| ILED1, ILED2, ILED3 REGISTER VALUES | LED CURRENT SETTING (mA) |

|---|---|

| 0 | 0 |

| 1 | 0.8 |

| 2 | 1.6 |

| 3 | 2.4 |

| … | … |

| 63 | 50 |

8.5.35 Register 23h (address = 23h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | DYNAMIC1 | 0 | 0 | ILED_2X | 0 |

| W-0h | W-0h | W-0h | R/W-0h | W-0h | W-0h | R/W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 0 | DYNAMIC2 | 0 | 0 | 0 | 0 | OSC_ENABLE | 0 |

| W-0h | R/W-0h | W-0h | W-0h | W-0h | W-0h | R/W-0h | W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | DYNAMIC3 | DYNAMIC4 | 0 | PDNRX | PDNAFE |

| W-0h | W-0h | W-0h | R/W-0h | R/W-0h | W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 54. Register 23h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-21 | 0 | W | 0h | Must write 0. |

| 20 | DYNAMIC1 | R/W | 0h | 0 = Transmitter is not powered down 1 = Transmitter is powered down in dynamic power-down mode |

| 19-18 | 0 | W | 0h | Must write 0. |

| 17 | ILED_2X | R/W | 0h | 0 = LED current range is 0 mA to 50 mA 1 = LED current range is 0 mA to 100 mA |

| 16-15 | 0 | W | 0h | Must write 0. |

| 14 | DYNAMIC2 | R/W | 0h | 0 = ADC is not powered down 1 = ADC is powered down in dynamic power-down mode |

| 13-10 | 0 | W | 0h | Must write 0. |

| 9 | OSC_ENABLE | R/W | 0h | 0 = External clock mode (default). In this mode, the CLK pin functions as an input pin where the external clock can be input. 1 = Enables oscillator mode. In this mode, the 4-MHz internal oscillator is enabled. |

| 8-5 | 0 | W | 0h | Must write 0. |

| 4 | DYNAMIC3 | R/W | 0h | 0 = TIA is not powered down 1 = TIA is powered down in dynamic power-down mode |

| 3 | DYNAMIC4 | R/W | 0h | 0 = Rest of ADC is not powered down 1 = Rest of ADC is powered down in dynamic power-down mode |

| 2 | 0 | W | 0h | Must write 0. |

| 1 | PDNRX | R/W | 0h | 0 = Normal mode 1 = RX portion of the AFE is powered down |

| 0 | PDNAFE | R/W | 0h | 0 = Normal mode 1 = Entire AFE is powered down |

8.5.36 Register 29h (address = 29h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 0 | 0 | 0 | 0 | 0 | 0 | ENABLE_ CLKOUT |

0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | R/W-0h | W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | CLKDIV_CLKOUT | 0 | |||

| W-0h | W-0h | W-0h | R/W-0h | W-0h | |||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 55. Register 29h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-10 | 0 | W | 0h | Must write 0. |

| 9 | ENABLE_CLKOUT | R/W | 0h | In internal clock mode, the internally-generated clock can be output on the CLK pin. 0 = Disables the clock output 1 = Enables CLKOUT generation and buffering on the CLK pin. The frequency of the clock output on the CLK pin (in internal clock mode) can be set using a programmable divider controlled by the CLKDIV_CLKOUT register bit. |

| 8-5 | 0 | W | 0h | Must write 0. |

| 4-1 | CLKDIV_CLKOUT | R/W | 0h | Set the frequency of the clock output on the CLK pin (in the internal clock mode), as shown in Table 56. |

Table 56. CLKDIV_CLKOUT Register Settings

| CLKDIV_CLKOUT REGISTER SETTINGS | DIVISION RATIO | FREQUENCY OF OUTPUT CLOCK IN MHz |

|---|---|---|

| 0 | 1 | 4 |

| 1 | 2 | 2 |

| 2 | 4 | 1 |

| 3 | 8 | 0.5 |

| 4 | 16 | 0.25 |

| 5 | 32 | 0.125 |

| 6 | 64 | 0.0625 |

| 7 | 128 | 0.03125 |

| 8..15 | Do not use | Do not use |

8.5.37 Register 2Ah (address = 2Ah) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| LED2VAL | |||||||

| R-0h | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2VAL | |||||||

| R-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2VAL | |||||||

| R-0h | |||||||

| LEGEND: R = Read only; -n = value after reset |

Table 57. Register 2Ah Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-0 | LED2VAL | R | 0h | These bits are the LED2 output code in 24-bit, twos complement format. |

8.5.38 Register 2Bh (address = 2Bh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| ALED2VAL\LED3VAL | |||||||

| R-0h | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED2VAL\LED3VAL | |||||||

| R-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED2VAL\LED3VAL | |||||||

| R-0h | |||||||

| LEGEND: R = Read only; -n = value after reset |

Table 58. Register 2Bh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-0 | ALED2VAL\LED3VAL | R | 0h | These bits are the ambient 2 or LED3 output code in 24-bit, twos complement format. |

8.5.39 Register 2Ch (address = 2Ch) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| LED1VAL | |||||||

| R-0h | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1VAL | |||||||

| R-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1VAL | |||||||

| R-0h | |||||||

| LEGEND: R = Read only; -n = value after reset |

Table 59. Register 2Ch Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-0 | LED1VAL | R | 0h | These bits are the LED1 output code in 24-bit, twos complement format. |

8.5.40 Register 2Dh (address = 2Dh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| ALED1VAL | |||||||

| R-0h | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| ALED1VAL | |||||||

| R-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ALED1VAL | |||||||

| R-0h | |||||||

| LEGEND: R = Read only; -n = value after reset |

Table 60. Register 2Dh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-0 | ALED1VAL | R | 0h | These bits are the ambient 1 output code in 24-bit, twos complement format. |

8.5.41 Register 2Eh (address = 2Eh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| LED2-ALED2VAL | |||||||

| R-0h | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED2-ALED2VAL | |||||||

| R-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED2-ALED2VAL | |||||||

| R-0h | |||||||

| LEGEND: R = Read only; -n = value after reset |

Table 61. Register 2Eh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-0 | LED2-ALED2VAL(1) | R | 0h | These bits are the LED2-ambient2 output code in 24-bit, twos complement format. |

8.5.42 Register 2Fh (address = 2Fh) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| LED1-ALED1VAL | |||||||

| R-0h | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| LED1-ALED1VAL | |||||||

| R-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LED1-ALED1VAL | |||||||

| R-0h | |||||||

| LEGEND: R = Read only; -n = value after reset |

Table 62. Register 2Fh Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-0 | LED1-ALED1VAL | R | 0h | These bits are the LED1-ambient1 output code in 24-bit, twos complement format. |

8.5.43 Register 31h (address = 31h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 0 | 0 | 0 | 0 | 0 | PD_ DISCONNECT |

0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | ENABLE_ INPUT_ SHORT |

0 | 0 | CLKDIV_EXTMODE | ||

| W-0h | W-0h | R/W-0h | R/W-0h | ||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 63. Register 31h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-11 | 0 | W | 0h | Must write 0. |

| 10 | PD_DISCONNECT | W | 0h | This bit disconnects the PD signals (INP, INM) from the TIA inputs. When enabled, the current input to the TIA is determined completely by the offset cancellation DAC current (I_OFFDAC). Note that in this mode, the AFE no longer sets the bias for the PD. |

| 9-6 | 0 | W | 0h | Must write 0. |

| 5 | ENABLE_INPUT_SHORT | R/W | 0h | INP, INN are shorted to VCM whenever the TIA is in power-down. |

| 4-3 | 0 | W | 0h | Must write 0. |

| 2-0 | CLKDIV_EXTMODE | R/W | 0h | These bits are used to set the division ratio to allow flexible clocking in external clock mode. For details, see Table 64. |

Table 64. CLKDIV_EXTMODE Register Settings

| CLKDIV_EXTMODE REGISTER SETTINGS | DIVISION RATIO | ALLOWED FREQUENCY RANGE OF EXTERNAL CLOCK IN MHz |

|---|---|---|

| 0 | 2 | 8-12 |

| 1 | 8 | 32-48 |

| 2 | Do not use | Do not use |

| 3 | 12 | 48-60 |

| 4 | 4 | 16-24 |

| 5 | 1 | 4-6 |

| 6 | 6 | 24-36 |

| 7 | Do not use | Do not use |

8.5.44 Register 32h (address = 32h) [reset = 0h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| PDNCYCLESTC | |||||||

| R/W-0h | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PDNCYCLESTC | |||||||

| R/W-0h | |||||||

| LEGEND: R/W = Read/Write; W = Write only; -n = value after reset |

Table 65. Register 32h Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23-16 | 0 | W | 0h | Must write 0. |