SLASEU7 March 2023 AFE781H1 , AFE881H1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements

- 6.7 Timing Diagrams

- 6.8 Typical Characteristics: VOUT DAC

- 6.9 Typical Characteristics: ADC

- 6.10 Typical Characteristics: Reference

- 6.11 Typical Characteristics: HART Modem

- 6.12 Typical Characteristics: Power Supply

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Digital-to-Analog Converter (DAC) Overview

- 7.3.2 Analog-to-Digital Converter (ADC) Overview

- 7.3.3 Programmable Out-of-Range Alarms

- 7.3.4 IRQ

- 7.3.5

HART Interface

- 7.3.5.1 FIFO Buffers

- 7.3.5.2 HART Modulator

- 7.3.5.3 HART Demodulator

- 7.3.5.4 HART Modem Modes

- 7.3.5.5 HART Modulation and Demodulation Arbitration

- 7.3.5.6 HART Modulator Timing and Preamble Requirements

- 7.3.5.7 HART Demodulator Timing and Preamble Requirements

- 7.3.5.8 IRQ Configuration for HART Communication

- 7.3.5.9 HART Communication Using the SPI

- 7.3.5.10 HART Communication Using UART

- 7.3.5.11 Memory Built-In Self-Test (MBIST)

- 7.3.6 Internal Reference

- 7.3.7 Integrated Precision Oscillator

- 7.3.8 One-Time Programmable (OTP) Memory

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RRU|24

Thermal pad, mechanical data (Package|Pins)

Orderable Information

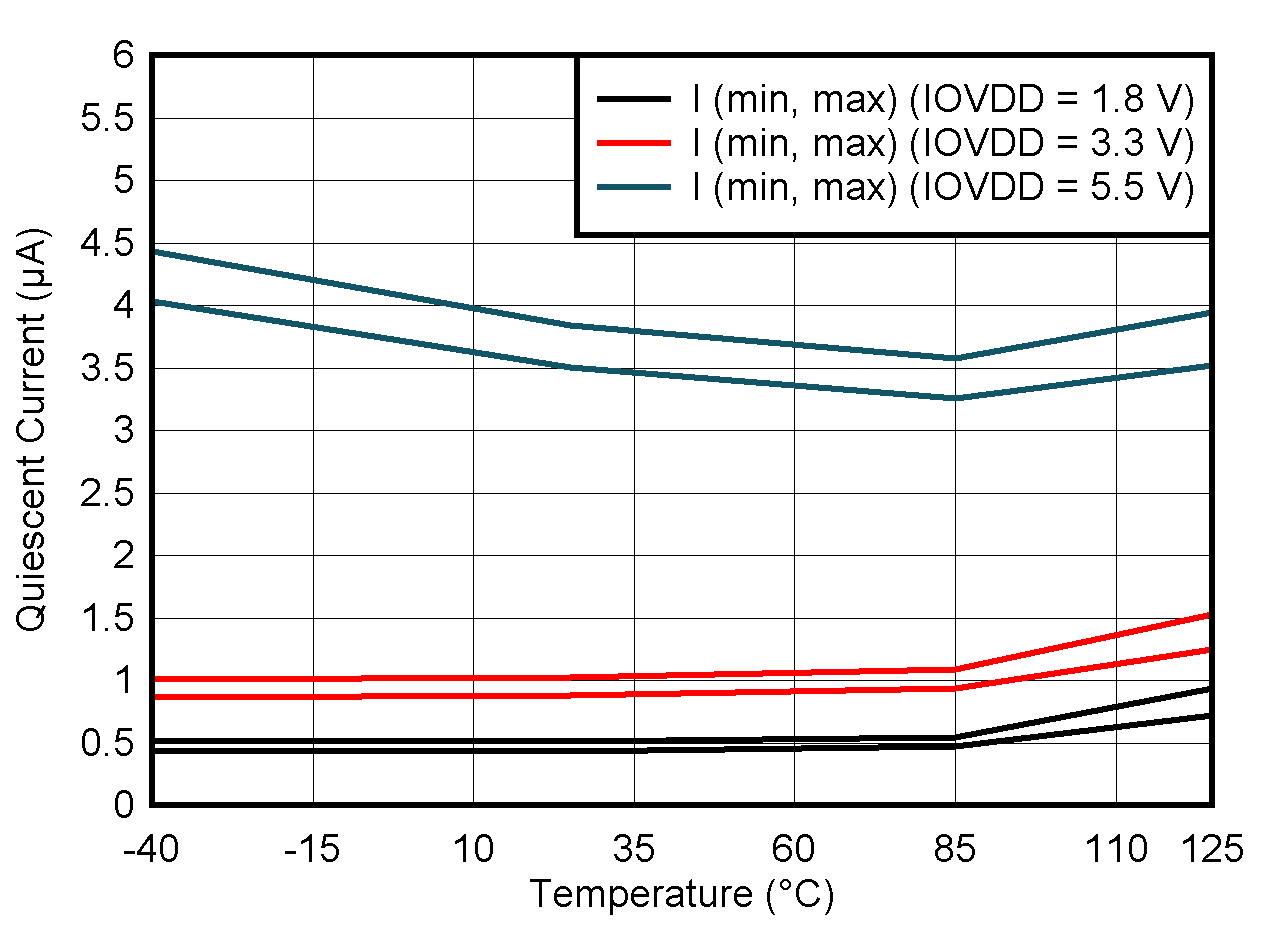

6.12 Typical Characteristics: Power Supply

at TA = 25°C, PVDD = IOVDD = 3.3 V, internal VREFIO, RLOAD = 50 kΩ to GND, CLOAD = 100 pF to GND, and digital inputs at IOVDD or GND (unless otherwise noted)