Typical values at TA = +25°C. Default

conditions at 30MHz: ADC Sampling Rate = 1500 MSPS, output sample rate = 62.5 MSPS

(decimate by 24x), PLL clock mode with fREF = 500 MHz, AIN =

–3 dBFS, DSA setting = 3 dB. Default conditions at 400 MHz: ADC Sampling Rate = 1500

MSPS, output sample rate = 125 MSPS (decimate by 12x), PLL clock mode with

fREF = 500 MHz, AIN = –3 dBFS, DSA setting = 3 dB.

Figure 6-1 RX

In-Band Gain Flatness, fIN = 30 MHz

Figure 6-1 RX

In-Band Gain Flatness, fIN = 30 MHz

| Differential Amplitude Error = PIN(DSA

Setting – 1) – PIN(DSA Setting) + 1 |

Figure 6-3 RX

Calibrated Differential Amplitude Error vs DSA Setting at 30 MHz

| Integrated Amplitude Error = PIN(DSA

Setting) – PIN(DSA Setting = 0) + (DSA

Setting) |

Figure 6-5 RX

Calibrated Integrated Amplitude Error vs DSA Setting at 30 MHz

| Differential Phase Error = PhaseIN(DSA

Setting – 1) – PhaseIN(DSA Setting) |

Figure 6-7 RX

Calibrated Differential Phase Error vs DSA Setting at 30 MHz

| With

0.8 GHz matching |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-9 RX

Calibrated Integrated Phase Error vs DSA Setting at 30 MHz

| AIN = -6 dBFS, fADC = 1500

MSPS, fNCO = 32. , Decimate by 24x |

Figure 6-11 RX

Output FFT at 5 MHz

| AIN = -30 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-13 RX

Output FFT at 5 MHz

| AIN = -3 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-15 RX

Output FFT at 30 MHz

| AIN = -12 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-17 RX

Output FFT at 30 MHz

| AIN = -60 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-19 RX

Output FFT at 30 MHz

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

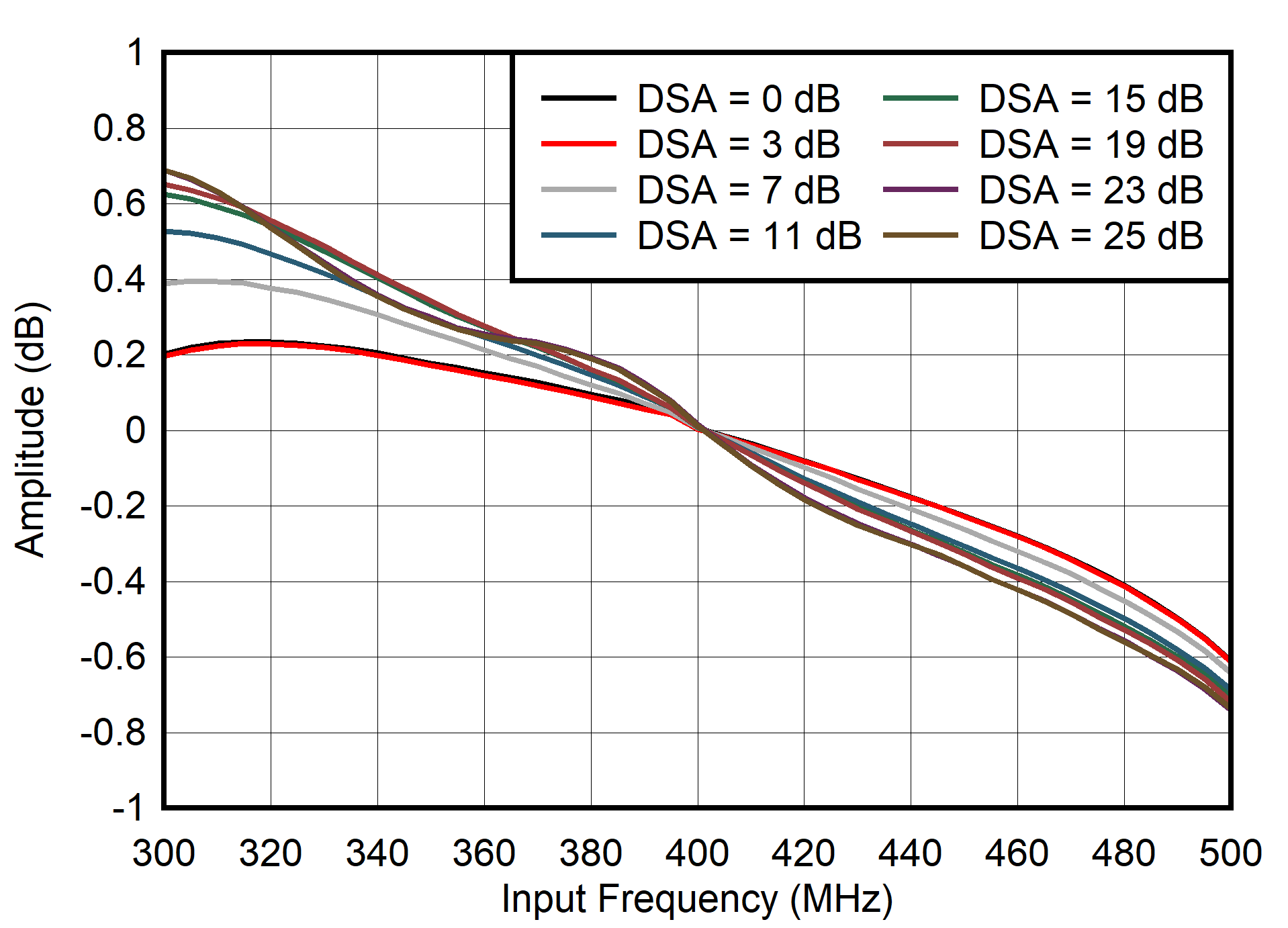

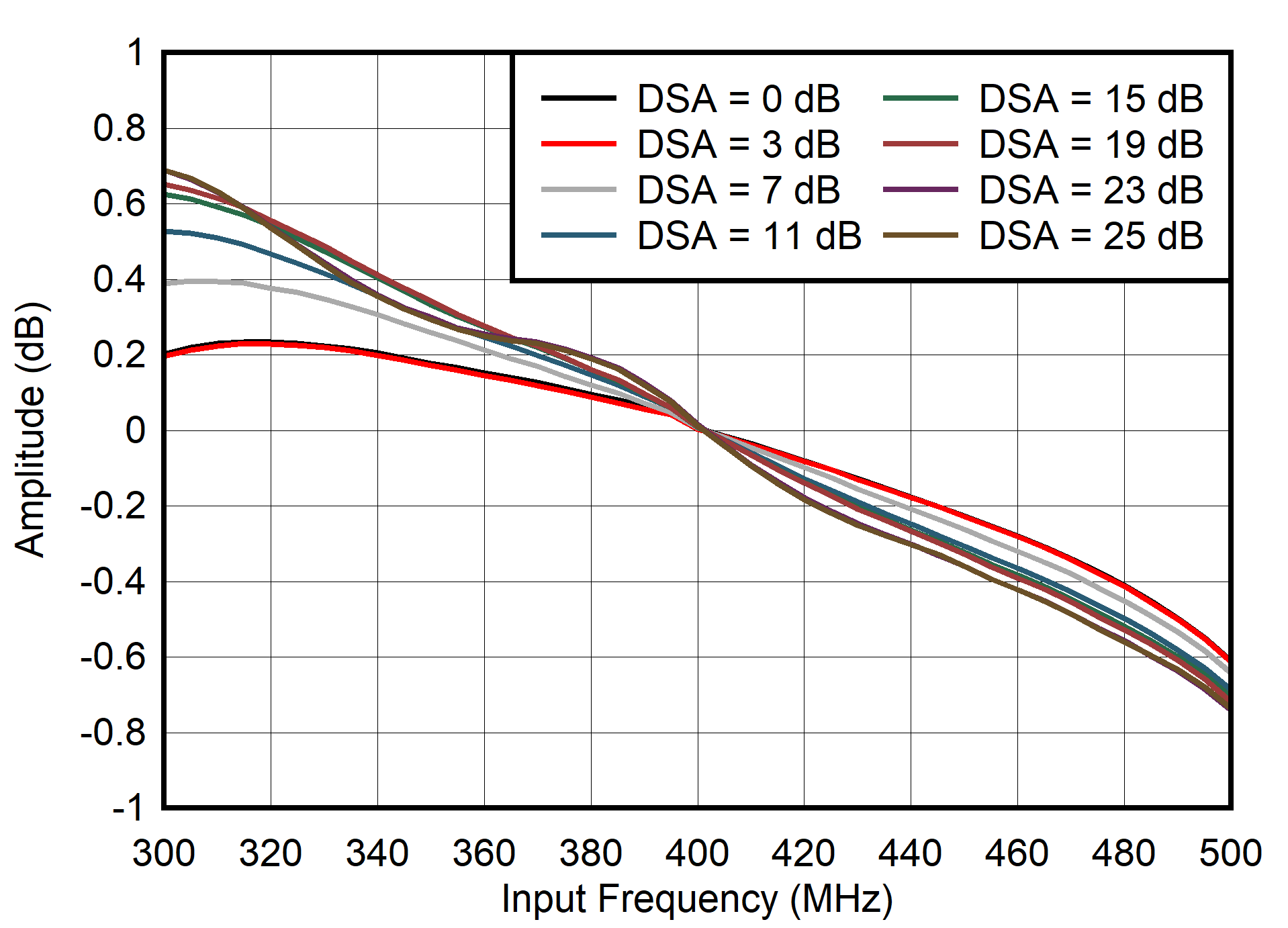

Figure 6-29 RX In-Band Gain Flatness, fIN = 400

MHz

Figure 6-29 RX In-Band Gain Flatness, fIN = 400

MHz

| Differential Amplitude Error = PIN(DSA

Setting – 1) – PIN(DSA Setting) + 1 |

Figure 6-31 RX Calibrated Differential Amplitude Error vs DSA

Setting at 400 MHz

| Integrated Amplitude Error = PIN(DSA

Setting) – PIN(DSA Setting = 0) + (DSA

Setting) |

Figure 6-33 RX Calibrated Integrated Amplitude Error vs DSA

Setting at 400 MHz

| Differential Phase Error = PhaseIN(DSA

Setting – 1) – PhaseIN(DSA Setting) |

Figure 6-35 RX Calibrated Differential Phase Error vs DSA

Setting at 400 MHz

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-37 RX Calibrated Integrated Phase Error vs DSA Setting

at 400 MHz Figure 6-39 RX Output FFT at 405 MHz and -6dBFS

Figure 6-39 RX Output FFT at 405 MHz and -6dBFS Figure 6-41 RX Output FFT at 405 MHz and -30dBFS

Figure 6-41 RX Output FFT at 405 MHz and -30dBFS Figure 6-43 NSD vs Input Amplitude at 400MHz

Figure 6-43 NSD vs Input Amplitude at 400MHz Figure 6-45 IMD3 vs Input Amplitude at 400MHz

Figure 6-45 IMD3 vs Input Amplitude at 400MHz Figure 6-47 IMD3 vs Tone Spacing at 400MHz

Figure 6-47 IMD3 vs Tone Spacing at 400MHz Figure 6-49 HD3 vs DSA Setting at 400MHz

Figure 6-49 HD3 vs DSA Setting at 400MHz

| Differential Amplitude Error = PIN(DSA

Setting – 1) – PIN(DSA Setting) + 1 |

Figure 6-2 RX

Uncalibrated Differential Amplitude Error vs DSA Setting at 30 MHz

| Integrated Amplitude Error = PIN(DSA

Setting) – PIN(DSA Setting = 0) + (DSA

Setting) |

Figure 6-4 RX

Uncalibrated Integrated Amplitude Error vs DSA Setting at 30 MHz

| Differential Phase Error = PhaseIN(DSA

Setting – 1) – PhaseIN(DSA Setting) |

Figure 6-6 RX

Uncalibrated Differential Phase Error vs DSA Setting at 30 MHz

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-8 RX

Uncalibrated Integrated Phase Error vs DSA Setting at 30 MHz

| AIN = -3 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-10 RX

Output FFT at 5 MHz

| AIN = -12 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-12 RX

Output FFT at 5 MHz

| AIN = -60 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-14 RX

Output FFT at 5 MHz

| AIN = -6 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-16 RX

Output FFT at 30 MHz

| AIN = -30 dBFS, fADC = 1500

MSPS, fNCO = 32.13 MHz, Decimate by

24x |

Figure 6-18 RX

Output FFT at 30 MHz

| fADC = 1500MSPS, fNCO = 32.13MHz, Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32. , Decimate by 24x |

| fADC = 1500 MSPS, fNCO =

32.13 MHz, Decimate by 24x |

| Differential Amplitude Error = PIN(DSA

Setting – 1) – PIN(DSA Setting) + 1 |

Figure 6-30 RX Uncalibrated Differential Amplitude Error vs DSA

Setting at 30 MHz

| Integrated Amplitude Error = PIN(DSA

Setting) – PIN(DSA Setting = 0) + (DSA

Setting) |

Figure 6-32 RX Uncalibrated Integrated Amplitude Error vs DSA

Setting at 400 MHz

| Differential Phase Error = PhaseIN(DSA

Setting – 1) – PhaseIN(DSA Setting) |

Figure 6-34 RX Uncalibrated Differential Phase Error vs DSA

Setting at 400 MHz

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-36 RX Uncalibrated Integrated Phase Error vs DSA

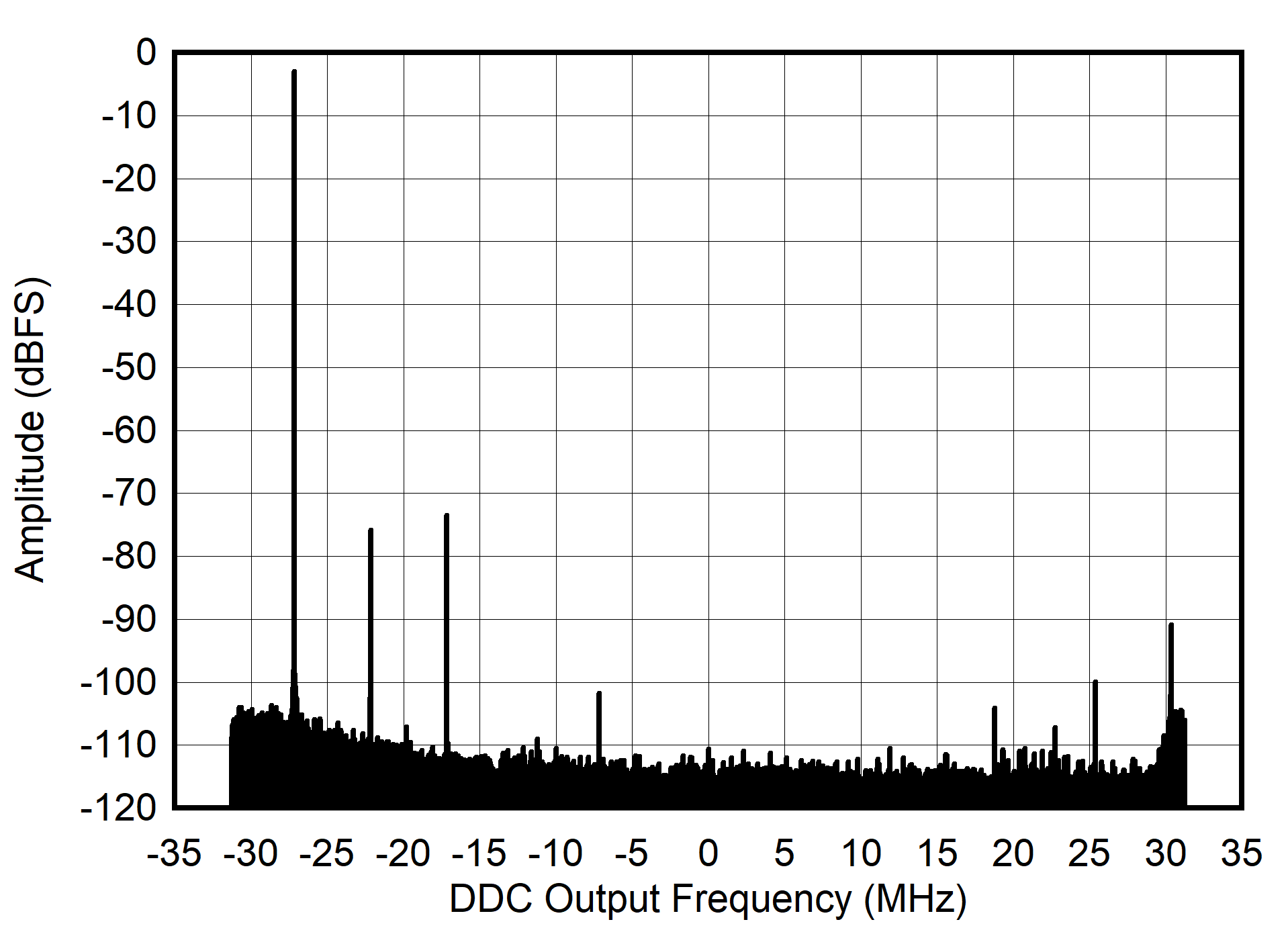

Setting at 400 MHz Figure 6-38 RX Output FFT at 405 MHz and -3dBFS

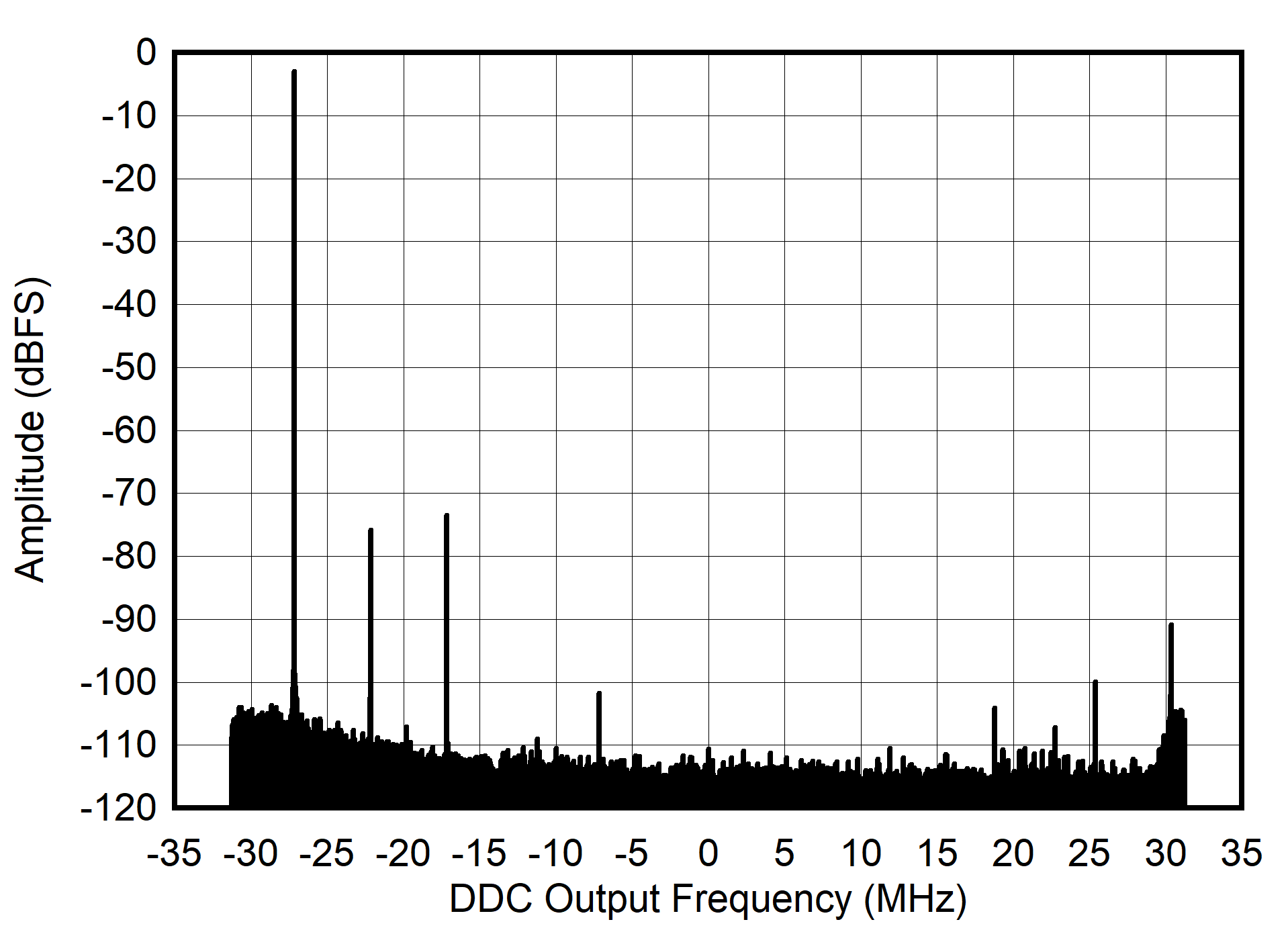

Figure 6-38 RX Output FFT at 405 MHz and -3dBFS Figure 6-40 RX Output FFT at 405 MHz and -12dBFS

Figure 6-40 RX Output FFT at 405 MHz and -12dBFS Figure 6-42 RX Output FFT at 405 MHz and -60dBFS

Figure 6-42 RX Output FFT at 405 MHz and -60dBFS Figure 6-44 NSD vs DSA Setting at 400MHz

Figure 6-44 NSD vs DSA Setting at 400MHz Figure 6-46 IMD3 vs DSA Setting at 400MHz

Figure 6-46 IMD3 vs DSA Setting at 400MHz Figure 6-48 HD3 vs Input Amplitude at 400MHz

Figure 6-48 HD3 vs Input Amplitude at 400MHz