SLUSEG2C September 2022 – February 2024 BQ25620 , BQ25622

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Description (continued)

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Power-On-Reset (POR)

- 8.3.2 Device Power Up from Battery

- 8.3.3 Device Power Up from Input Source

- 8.3.4 Power Path Management

- 8.3.5 Battery Charging Management

- 8.3.6 USB On-The-Go (OTG)

- 8.3.7 Integrated 12-Bit ADC for Monitoring

- 8.3.8 Status Outputs ( PG, STAT, INT)

- 8.3.9 BATFET Control

- 8.3.10 Protections

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Revision History

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RYK|18

Thermal pad, mechanical data (Package|Pins)

Orderable Information

11.2 Layout Example

Figure 11-1 High Frequency Current Path

Figure 11-1 High Frequency Current Path Figure 11-2 Layout Example: Top Layer

(red) and All PGND Internal Layer 2 (brown)

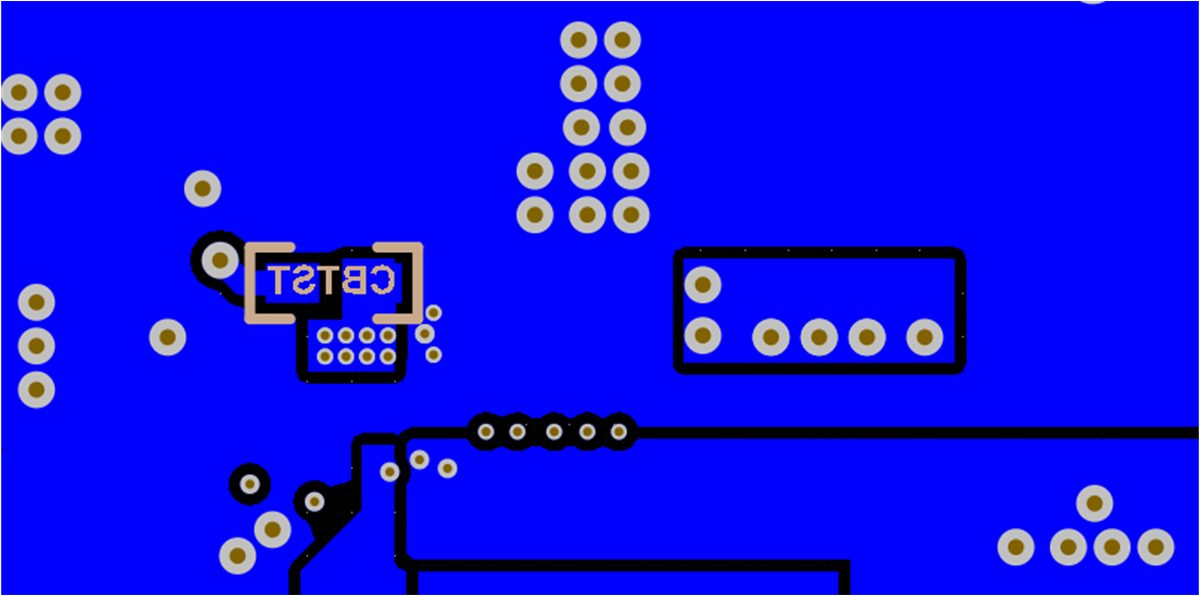

Figure 11-2 Layout Example: Top Layer

(red) and All PGND Internal Layer 2 (brown) Figure 11-3 Layout Example: Inner Layer 3

(AGND pour; SW node pour; signal routing)

Figure 11-3 Layout Example: Inner Layer 3

(AGND pour; SW node pour; signal routing) Figure 11-4 Layout Example: Bottom Layer

X-Ray From Top (PGND pour; BTST capacitor; redundant SW, SYS and BAT

pours)

Figure 11-4 Layout Example: Bottom Layer

X-Ray From Top (PGND pour; BTST capacitor; redundant SW, SYS and BAT

pours)