SLUSEG2C September 2022 – February 2024 BQ25620 , BQ25622

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Description (continued)

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Power-On-Reset (POR)

- 8.3.2 Device Power Up from Battery

- 8.3.3 Device Power Up from Input Source

- 8.3.4 Power Path Management

- 8.3.5 Battery Charging Management

- 8.3.6 USB On-The-Go (OTG)

- 8.3.7 Integrated 12-Bit ADC for Monitoring

- 8.3.8 Status Outputs ( PG, STAT, INT)

- 8.3.9 BATFET Control

- 8.3.10 Protections

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Revision History

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RYK|18

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8.3.8.2 Interrupts and Status, Flag and Mask Bits

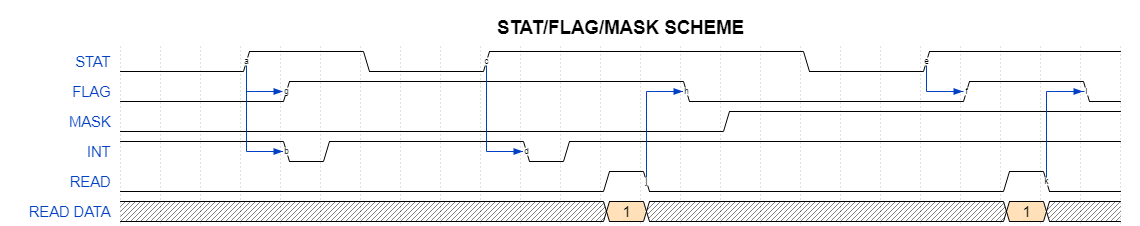

The device incorporates an interrupt pin (INT) to inform a host microcontroller of status changes without requiring microcontroller polling. Each reported event has a status field, a flag bit and a mask bit. The status field reports the status at the time that it is read. The flag bit is latched and, once set to 1, will remain at 1 until the host reads the bit, which will clear it to 0. The mask bit determines whether or not an interrupt pulse will be generated when the flag bit is set.

Figure 8-6 Relationship Between STAT, FLAG, and MASK

The flag bit is set upon certain transitions of the status field. These transitions also generate an INT pulse if the associated mask bit is set to 0. Because the INT is generated from the status field transition and not the flag bit, an INT pulse is sent to the host even if the associated flag is already set to 1 when the status transition occurs. Details of this behavior are shown in Figure 8-6.

The default behavior is to generate a 256-μs INT pulse when any flag bit is set to 1. These pulses may be masked out on a flag-by-flag basis by setting a flag's mask bit to 1. Setting the mask bit does not affect the transition of the flag bit from 0 to 1, only the generation of the 256-μs INT pulse.