SLUSFN3 July 2024 BQ25820

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Device Power-On-Reset

- 7.3.2 Device Power-Up From Battery Without Input Source

- 7.3.3 Device Power Up from Input Source

- 7.3.4 Battery Charging Management

- 7.3.5 Power Path Management

- 7.3.6 Reverse Mode Power Direction

- 7.3.7 Integrated 16-Bit ADC for Monitoring

- 7.3.8 Status Outputs (PG, STAT1, STAT2, and INT)

- 7.3.9 Serial Interface

- 7.4 Device Functional Modes

- 7.5 BQ25820 Registers

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1

Typical Application

- 8.2.1.1 Design Requirements

- 8.2.1.2

Detailed Design Procedure

- 8.2.1.2.1 ACUV / ACOV Input Voltage Operating Window Programming

- 8.2.1.2.2 Charge Voltage Selection

- 8.2.1.2.3 Switching Frequency Selection

- 8.2.1.2.4 Inductor Selection

- 8.2.1.2.5 Input (VAC / SYS) Capacitor

- 8.2.1.2.6 Output (VBAT) Capacitor

- 8.2.1.2.7 Sense Resistor (RAC_SNS and RBAT_SNS) and Current Programming

- 8.2.1.2.8 Power MOSFETs Selection

- 8.2.1.2.9 ACFETs and BATFETs Selection

- 8.2.1.3 Application Curves

- 8.2.1

Typical Application

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- RRV|36

Thermal pad, mechanical data (Package|Pins)

- RRV|36

Orderable Information

10.2 Layout Example

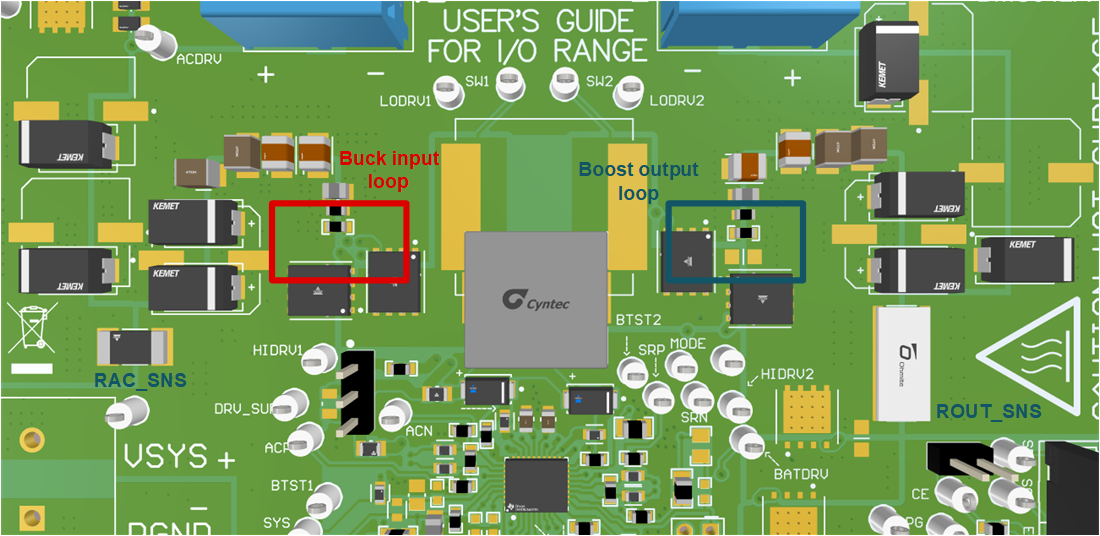

Based on the above layout guidelines, the PCB layout example top view is shown below including all the key power components.

Figure 10-1 PCB Layout Reference Example Top

View

Figure 10-1 PCB Layout Reference Example Top

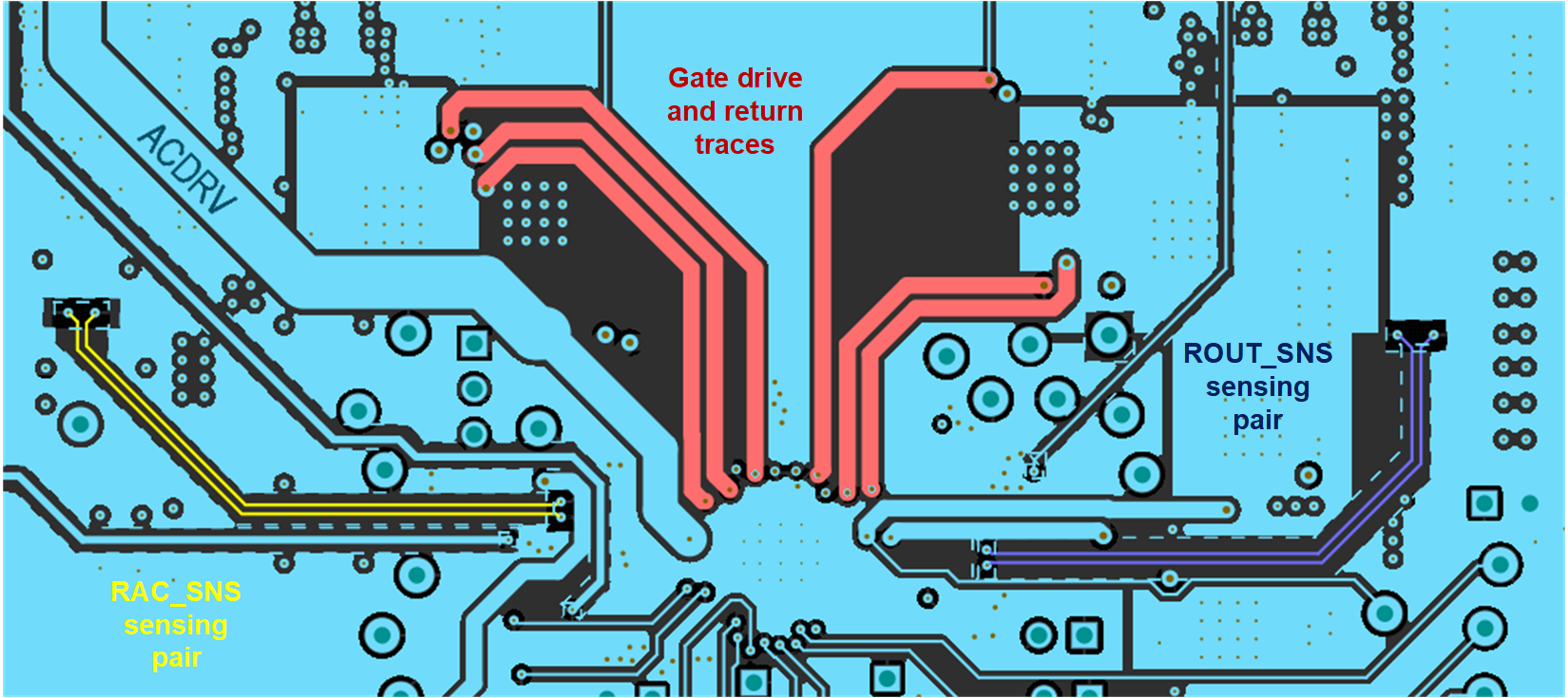

ViewFor both input and output current sensing resistors, differential sensing and routing method are suggested and highlighted in figure below. Use wide trace for gate drive traces, minimum 20-mil trace width. Connect all analog grounds to a dedicated low-impedance copper plane, which is tied to the power ground underneath the IC exposed pad.

Figure 10-2 PCB Layout Gate Drive and Current Sensing Signal Layer Routing

Figure 10-2 PCB Layout Gate Drive and Current Sensing Signal Layer Routing