SCAS918E June 2013 – August 2024 CDCE913-Q1 , CDCEL913-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Register Maps

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PW|14

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.2.1 Design Requirements

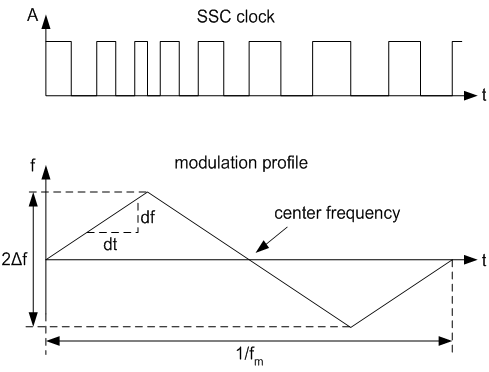

The CDCE913-Q1 device supports spread-spectrum clocking (SSC) with multiple control parameters:

- Modulation amount (%)

- Modulation frequency (>20 kHz)

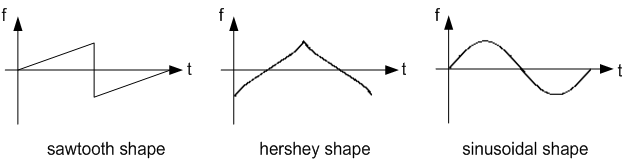

- Modulation shape (triangular, Hershey, and others)

- Center spread or down spread (± or –)

Consider the following sample design requirements:

- EMI ≤ 55 dBmV

- CLK1 frequency = 27 MHz

- CLK2 frequency = 54 MHz

- CLK3 frequency = 108 MHz

For sample calculations of PLL constants, see PLL Frequency Planning.

Figure 9-2 Modulation Frequency (fm) and Modulation Amount

Figure 9-2 Modulation Frequency (fm) and Modulation Amount Figure 9-3 Spread Spectrum Modulation Shapes

Figure 9-3 Spread Spectrum Modulation Shapes