SLASFK2 December 2024 DAC121S101-SEP

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- DGK|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

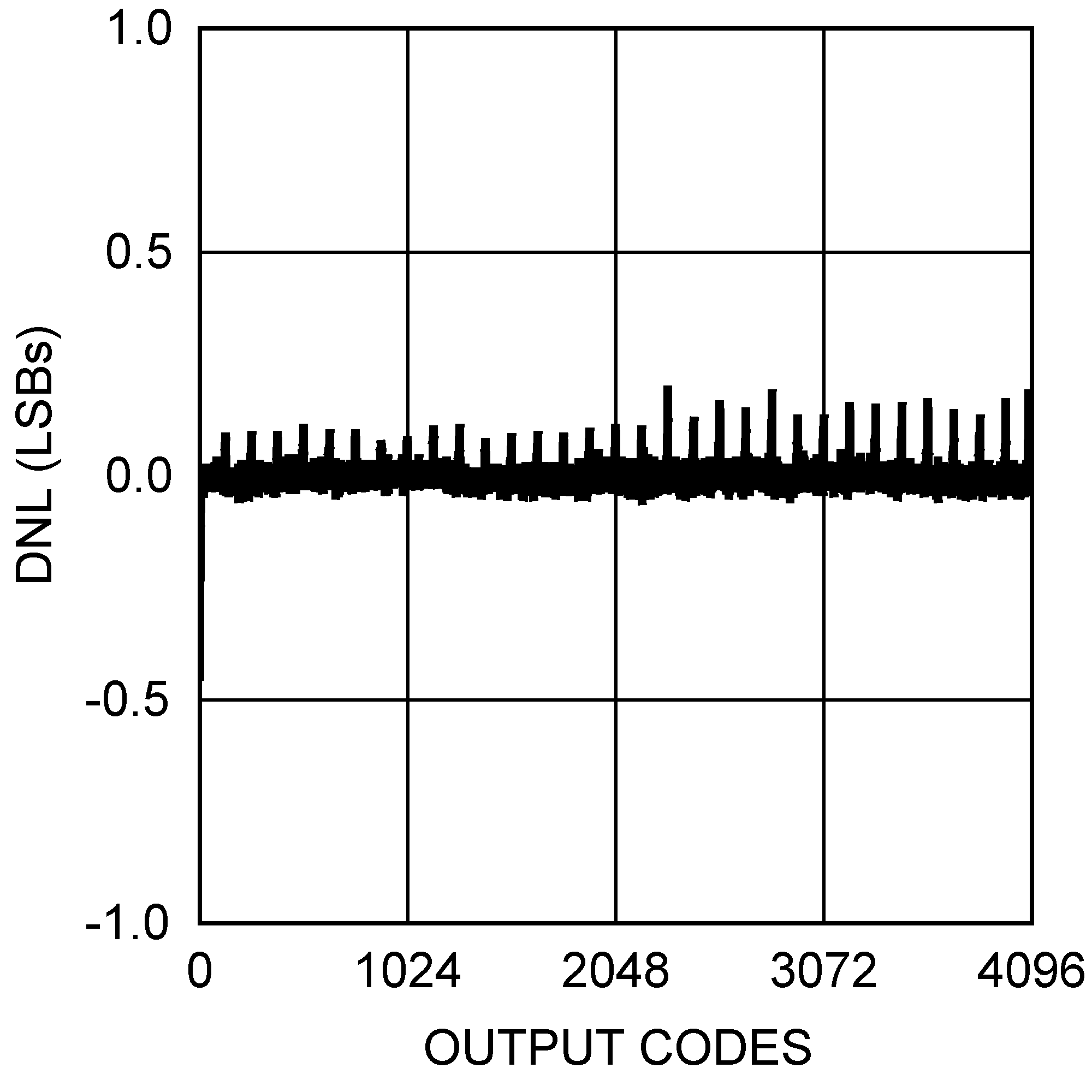

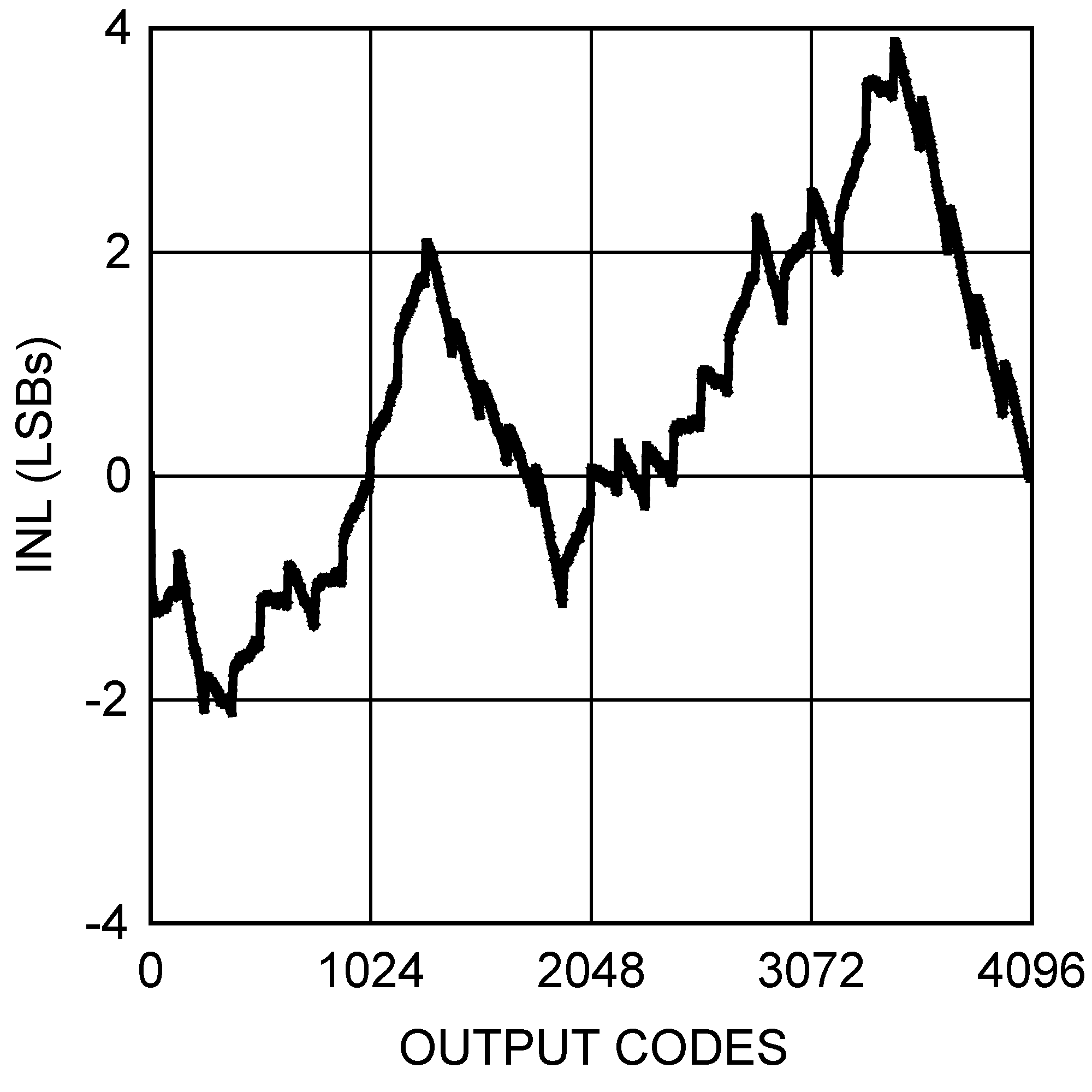

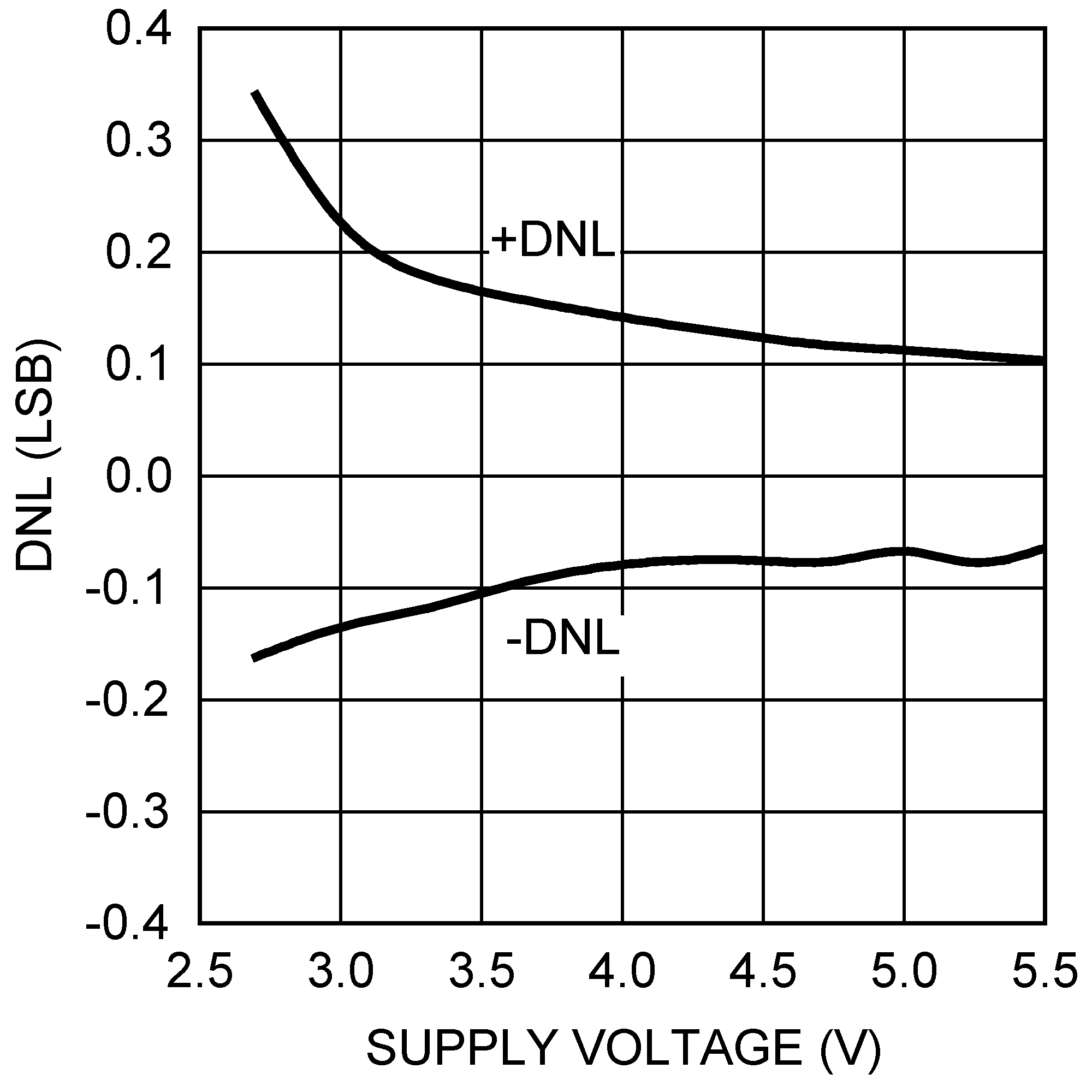

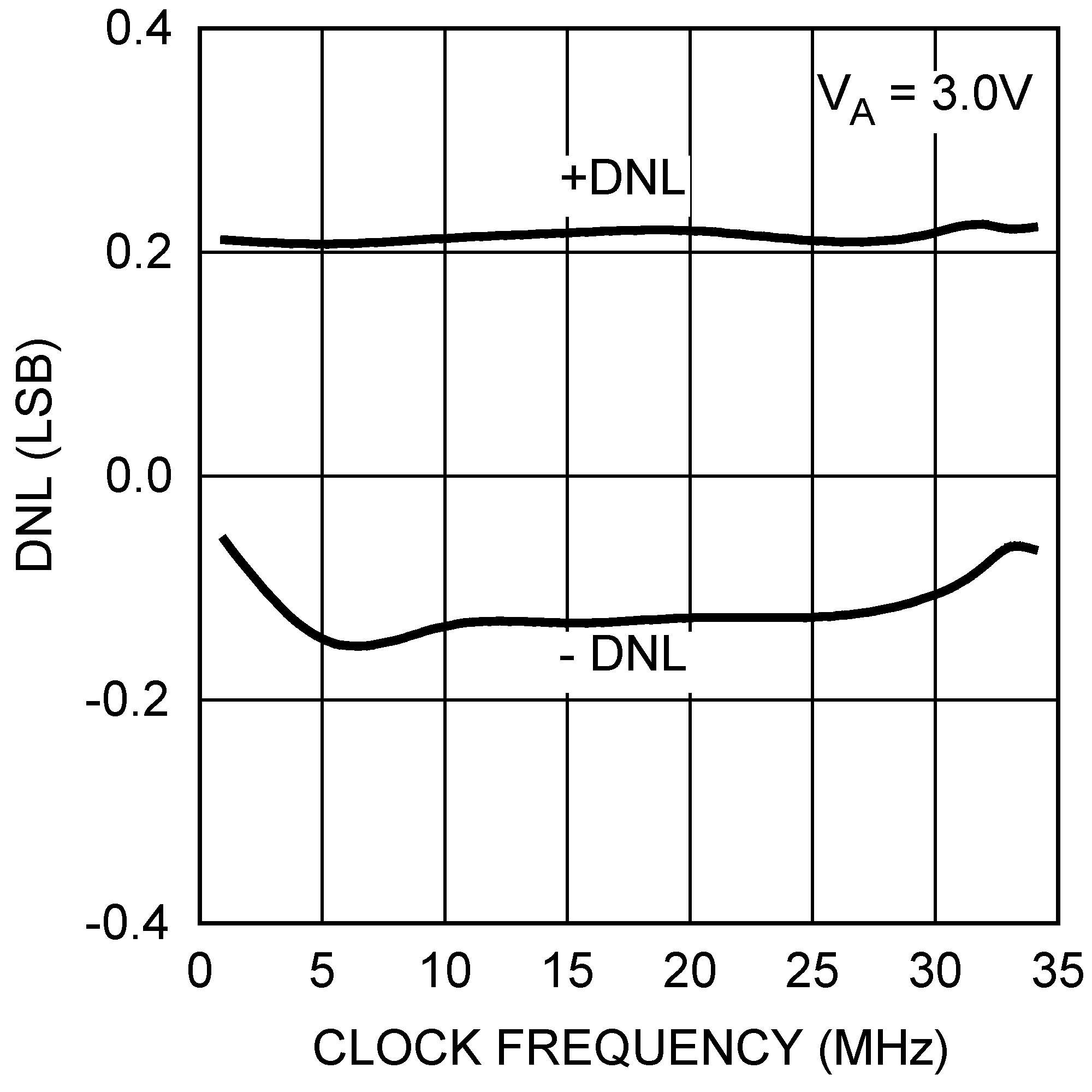

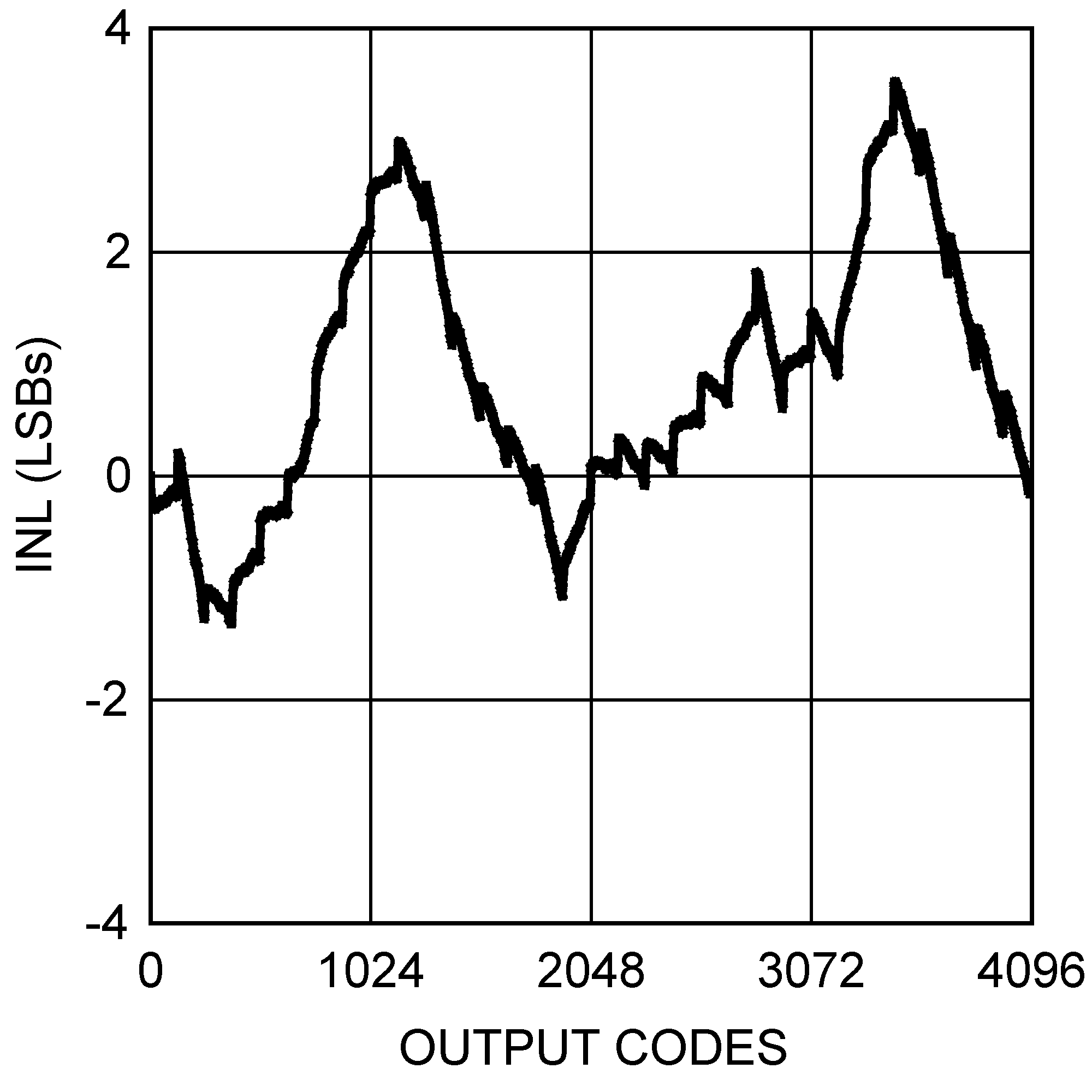

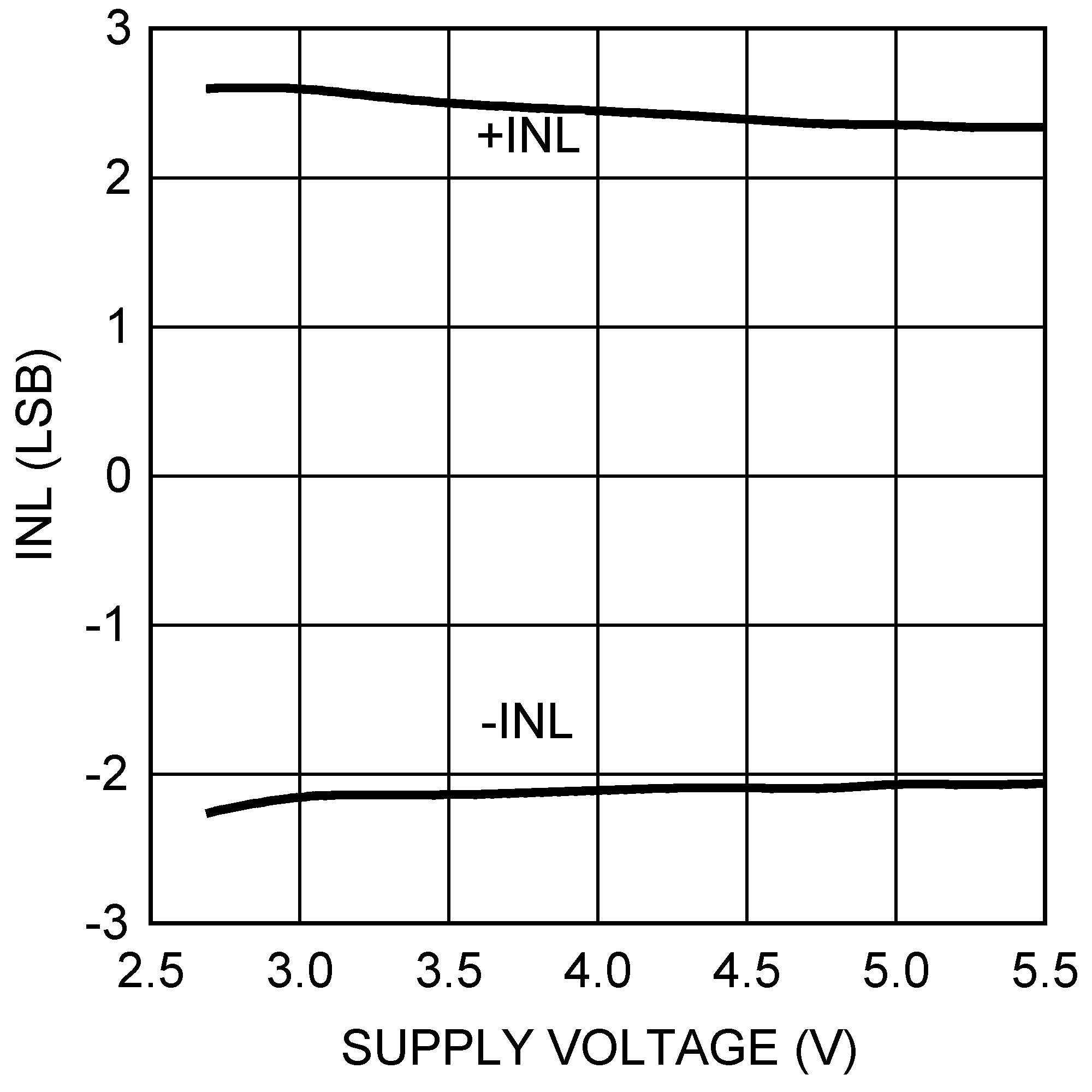

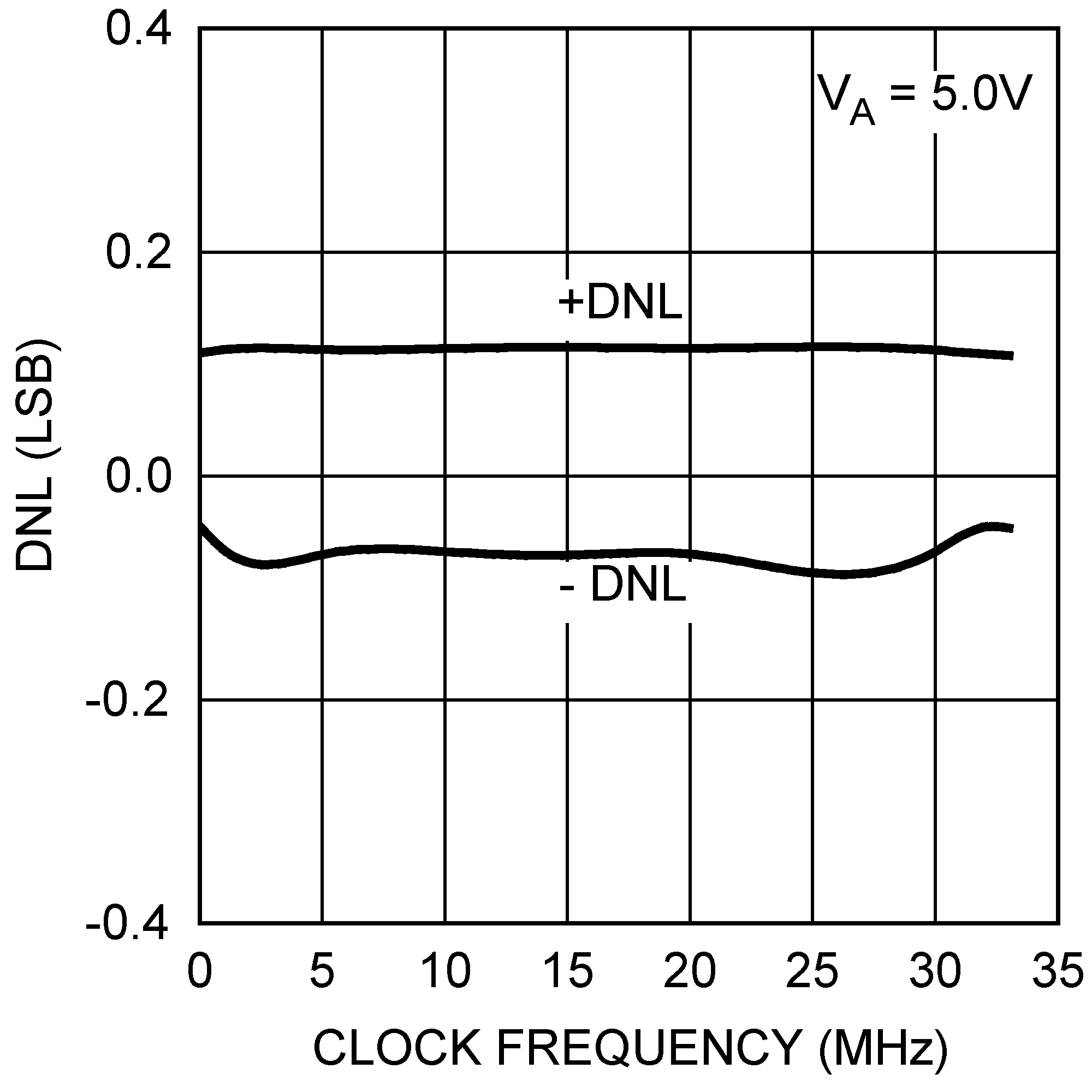

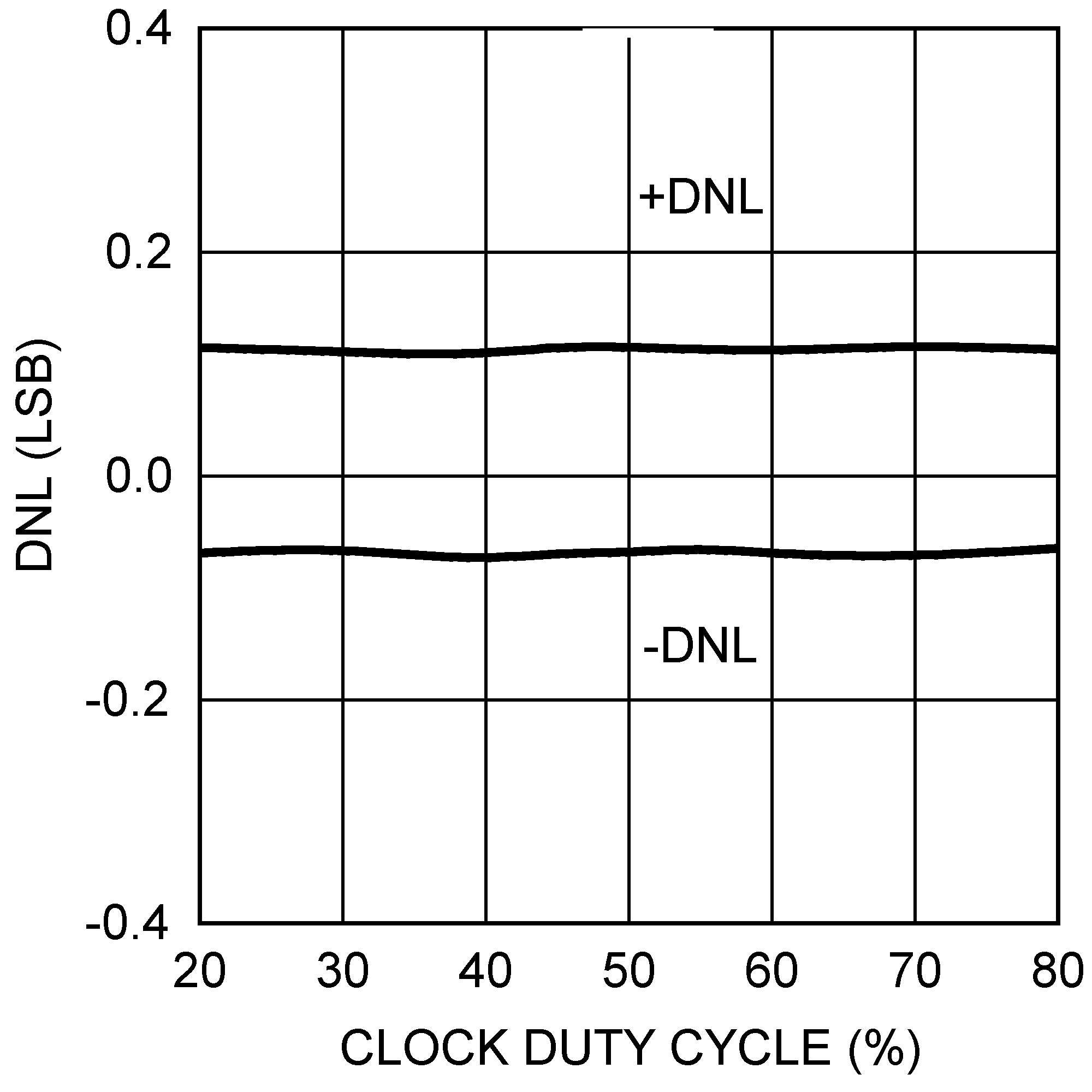

5.8 Typical Characteristics

at fSCLK = 30MHz, TA = 25°C, and input code range = 48 to 4047 (unless otherwise noted)

| VA = 3V | ||

| VA = 3V | ||

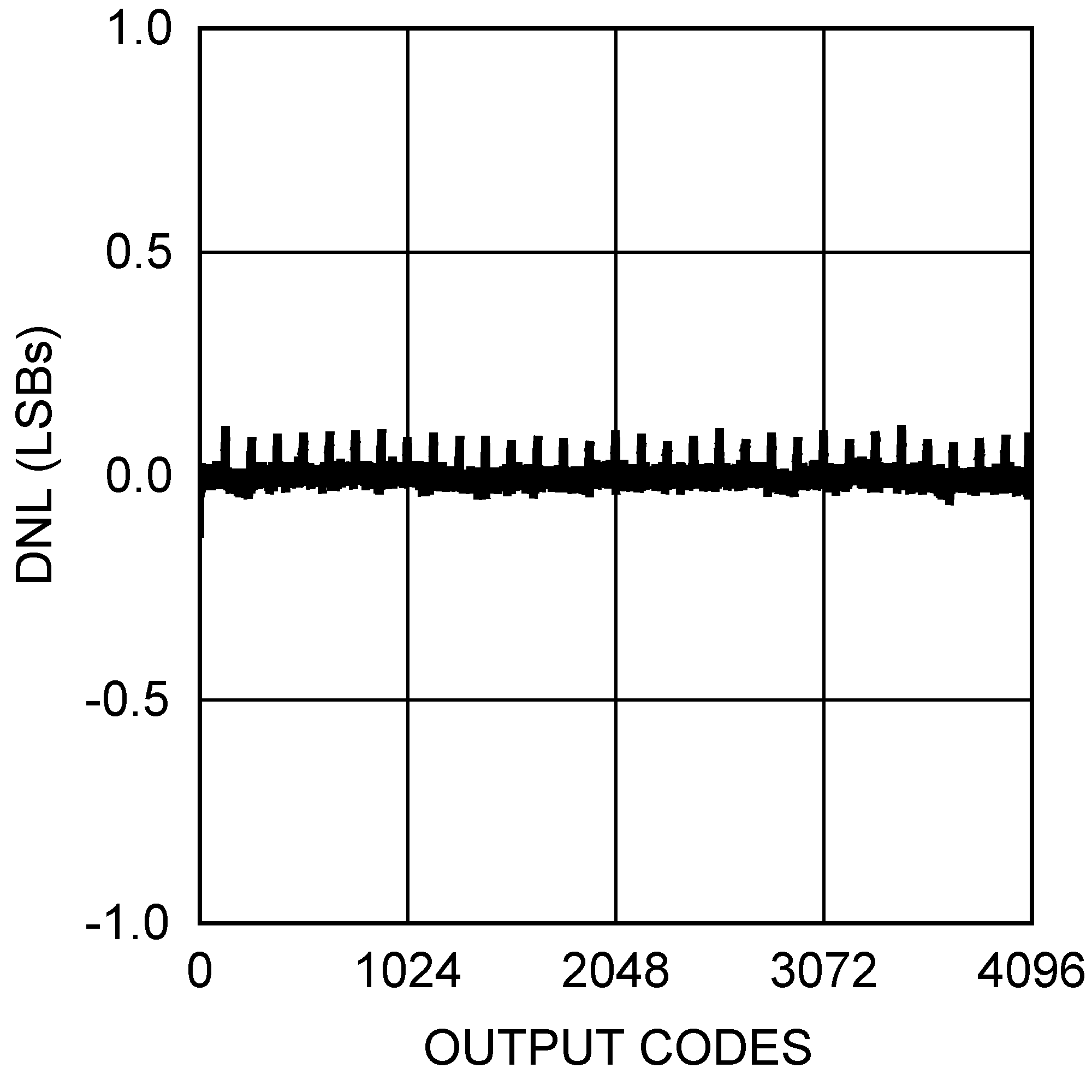

Figure 5-6 DNL vs Supply

Voltage

Figure 5-6 DNL vs Supply

Voltage Figure 5-8 3V DNL vs Clock

Frequency

Figure 5-8 3V DNL vs Clock

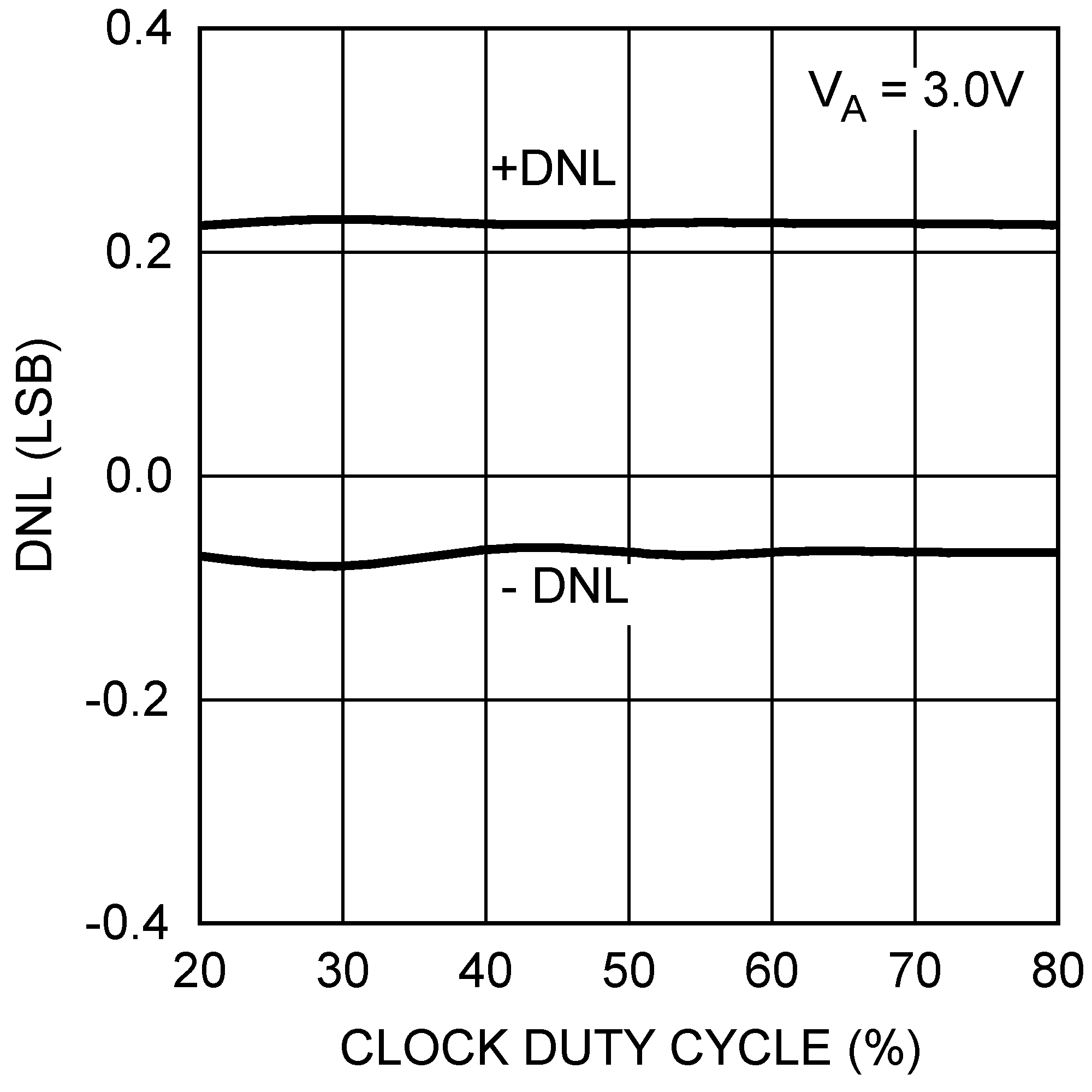

Frequency Figure 5-10 3V DNL vs Clock Duty

Cycle

Figure 5-10 3V DNL vs Clock Duty

Cycle Figure 5-12 3V DNL vs

Temperature

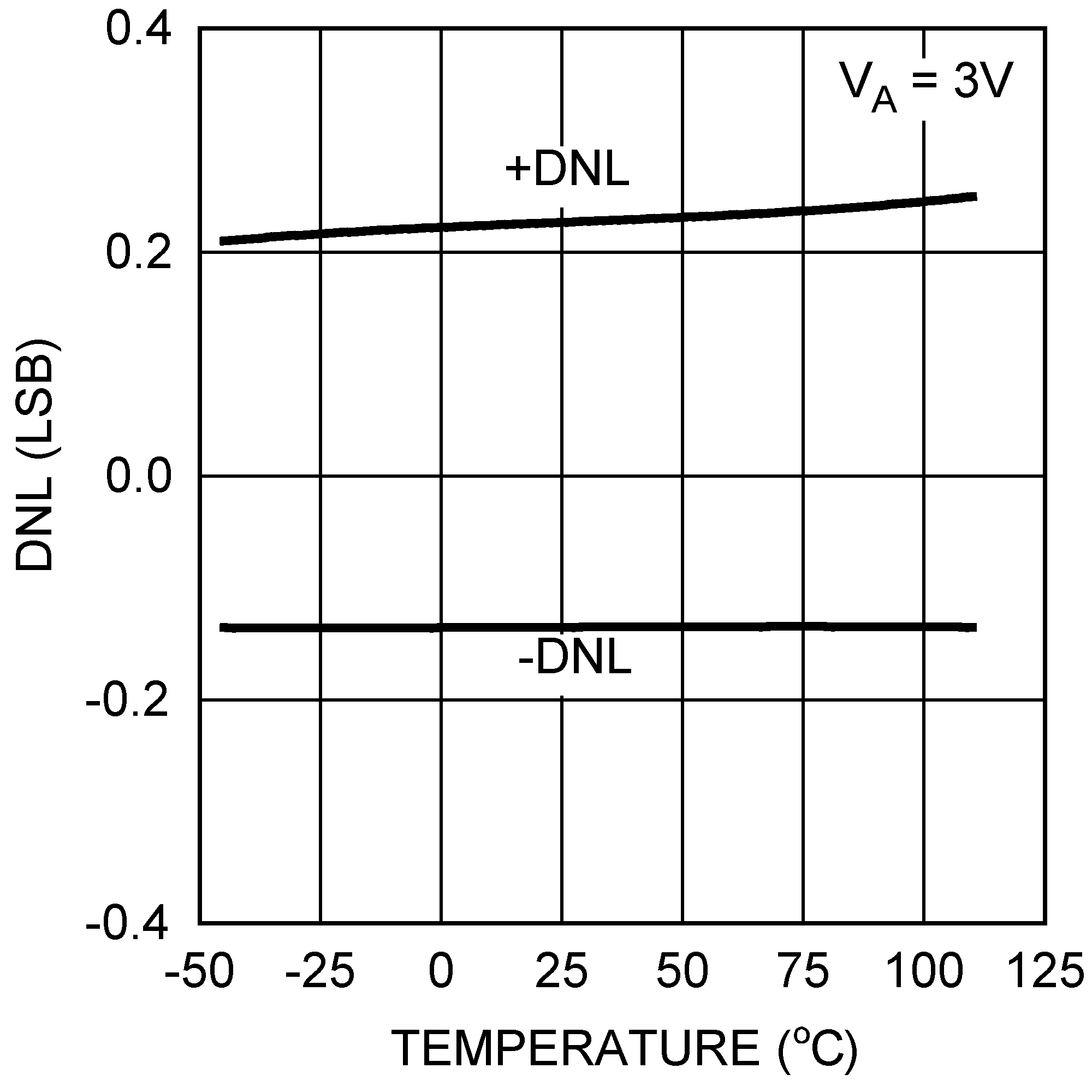

Figure 5-12 3V DNL vs

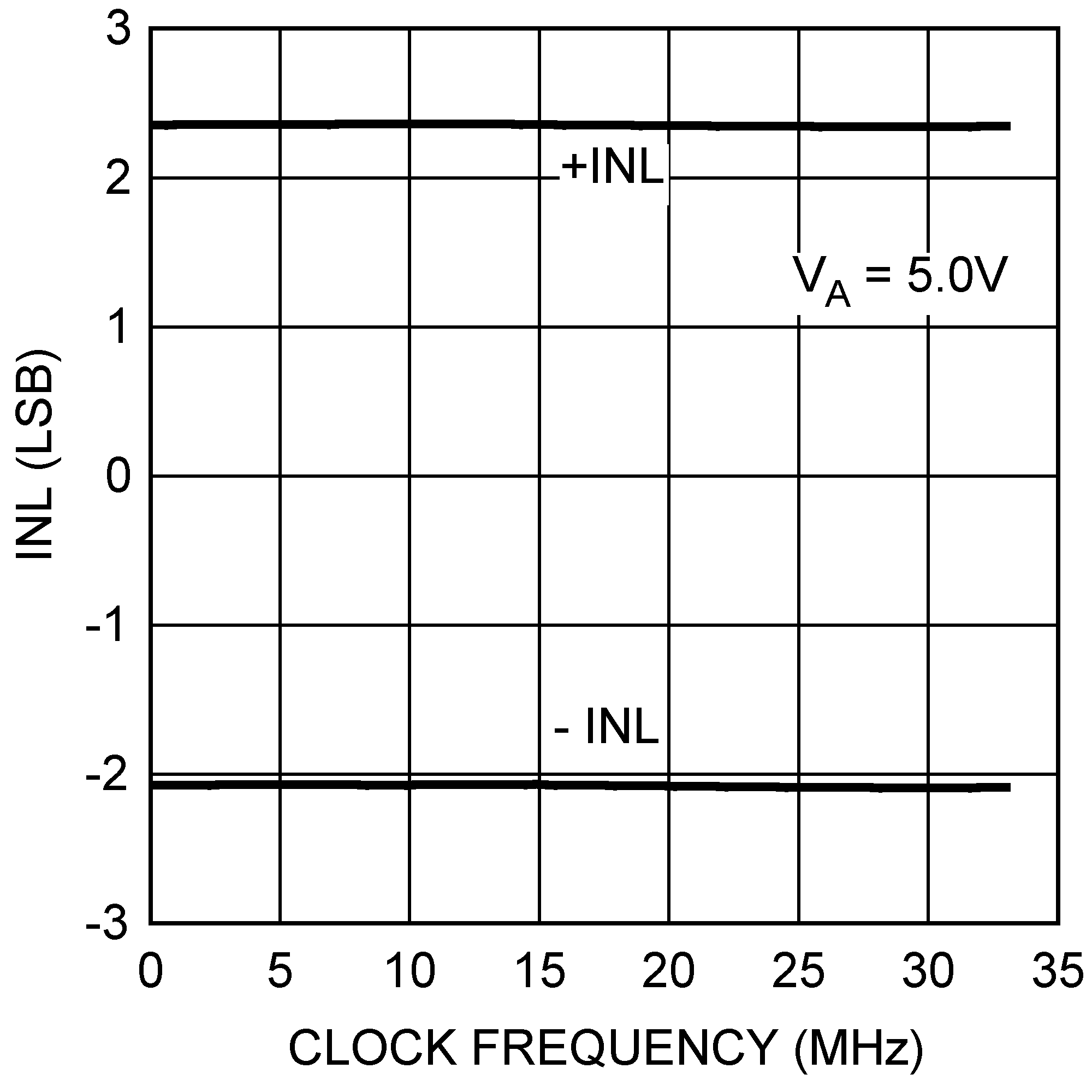

Temperature Figure 5-14 5V INL vs Clock

Frequency

Figure 5-14 5V INL vs Clock

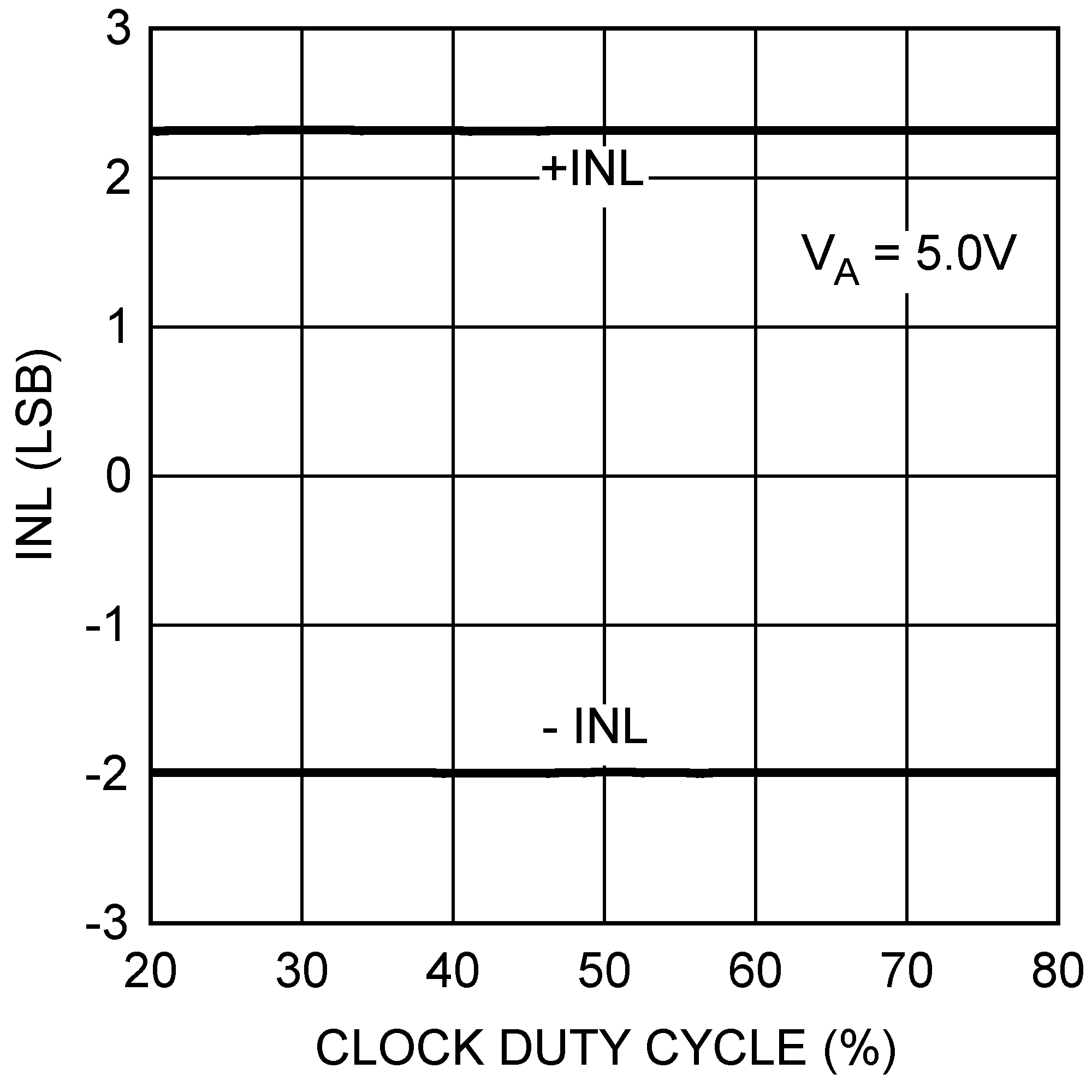

Frequency Figure 5-16 5V INL vs Clock Duty

Cycle

Figure 5-16 5V INL vs Clock Duty

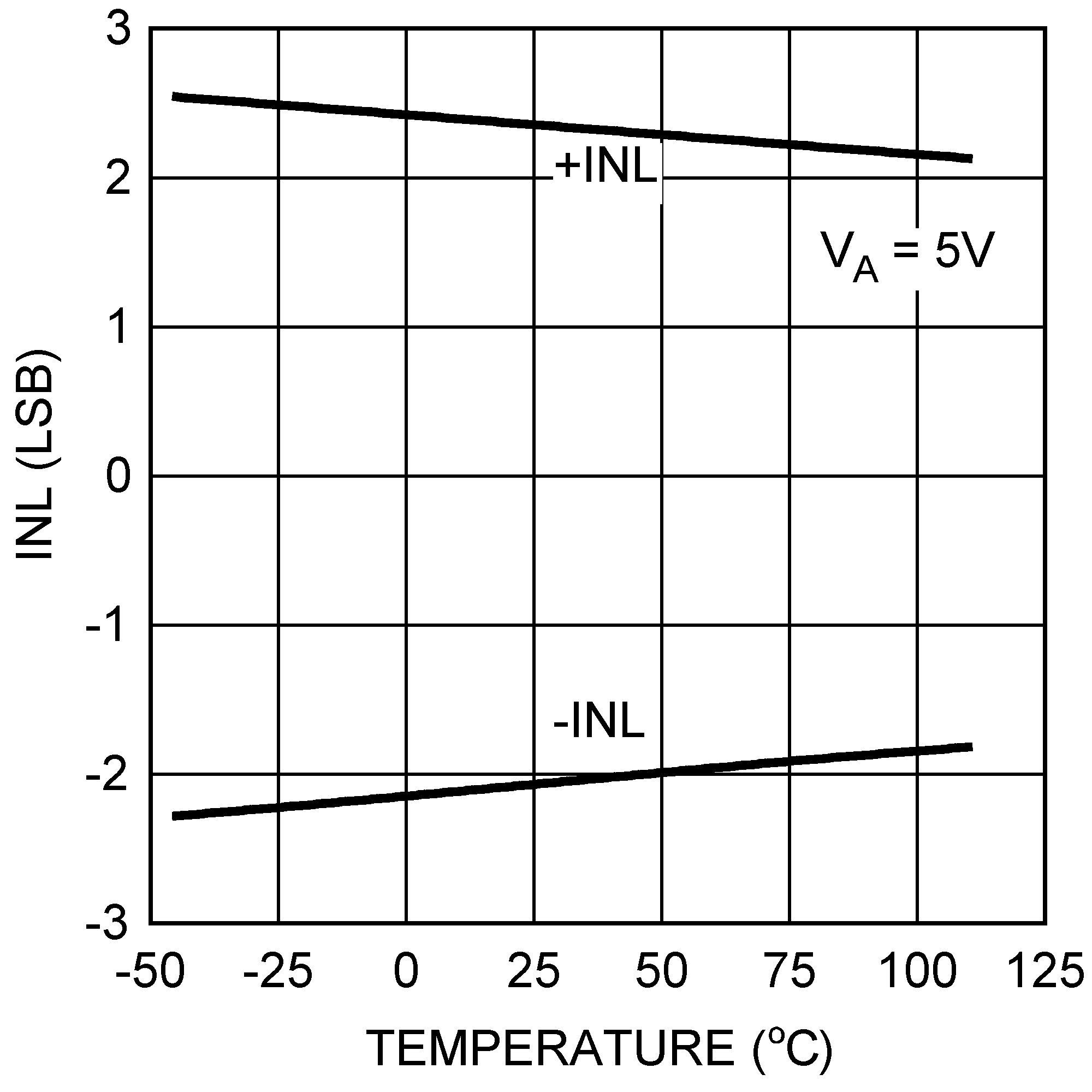

Cycle Figure 5-18 5V INL vs

Temperature

Figure 5-18 5V INL vs

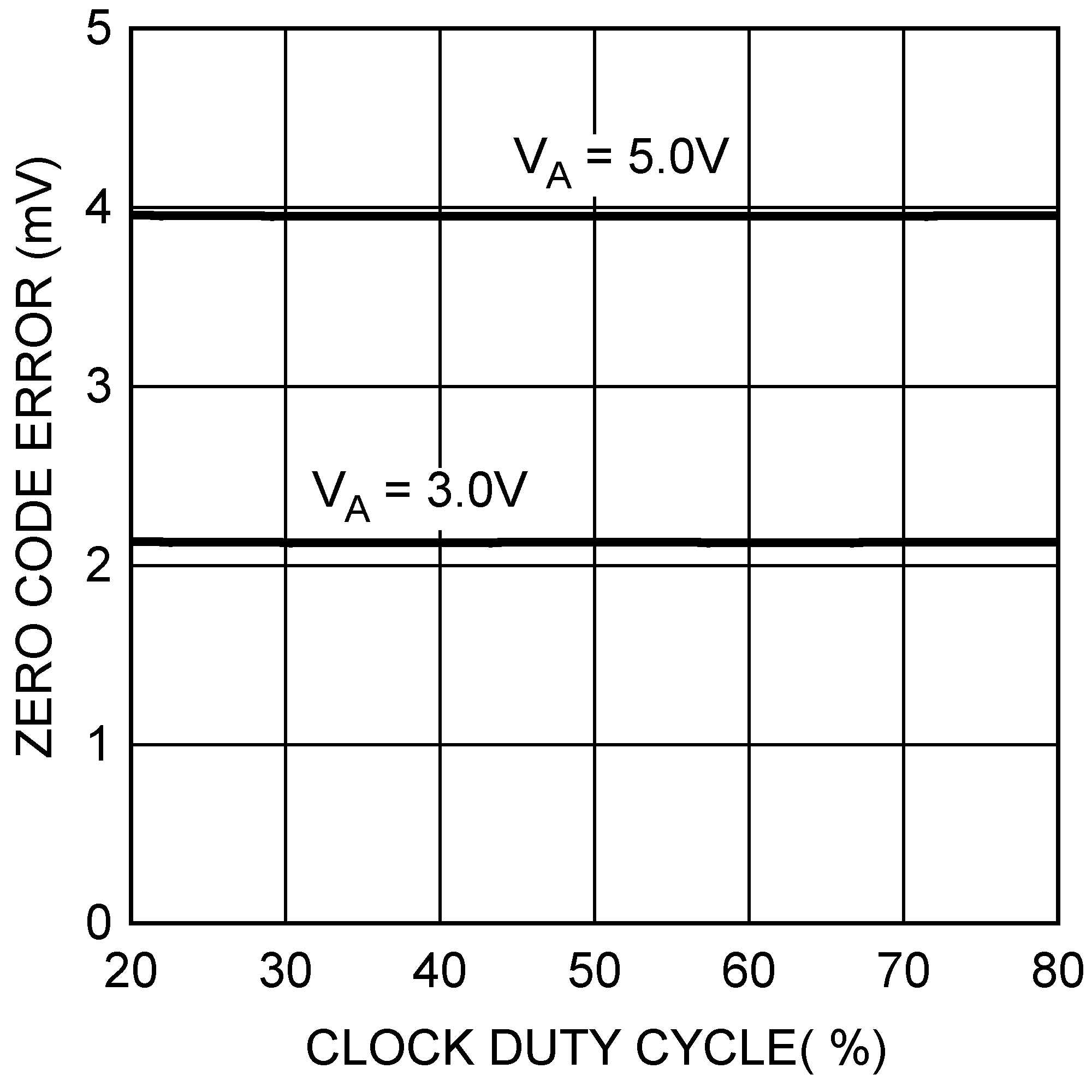

Temperature Figure 5-20 Zero Code Error vs Clock

Duty Cycle

Figure 5-20 Zero Code Error vs Clock

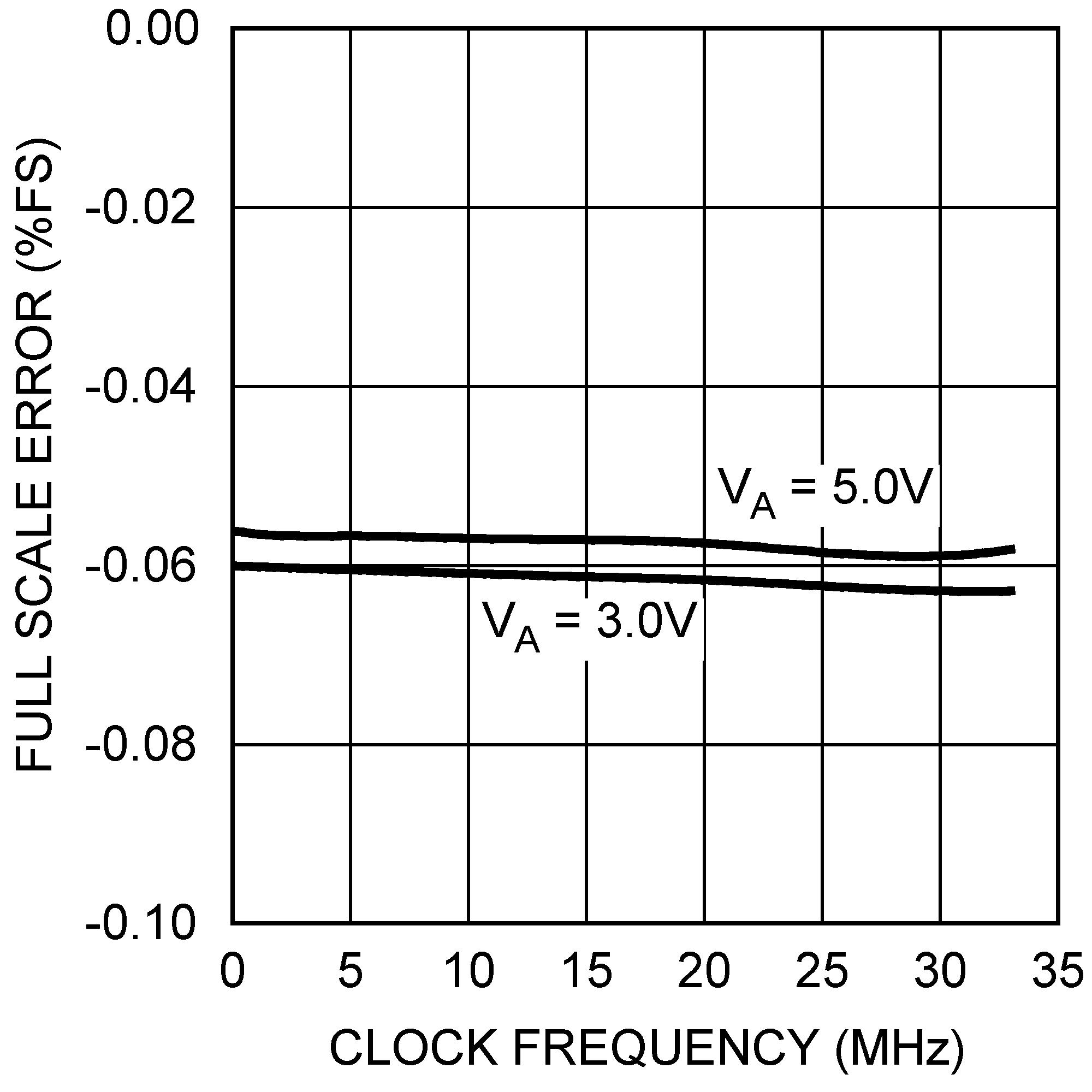

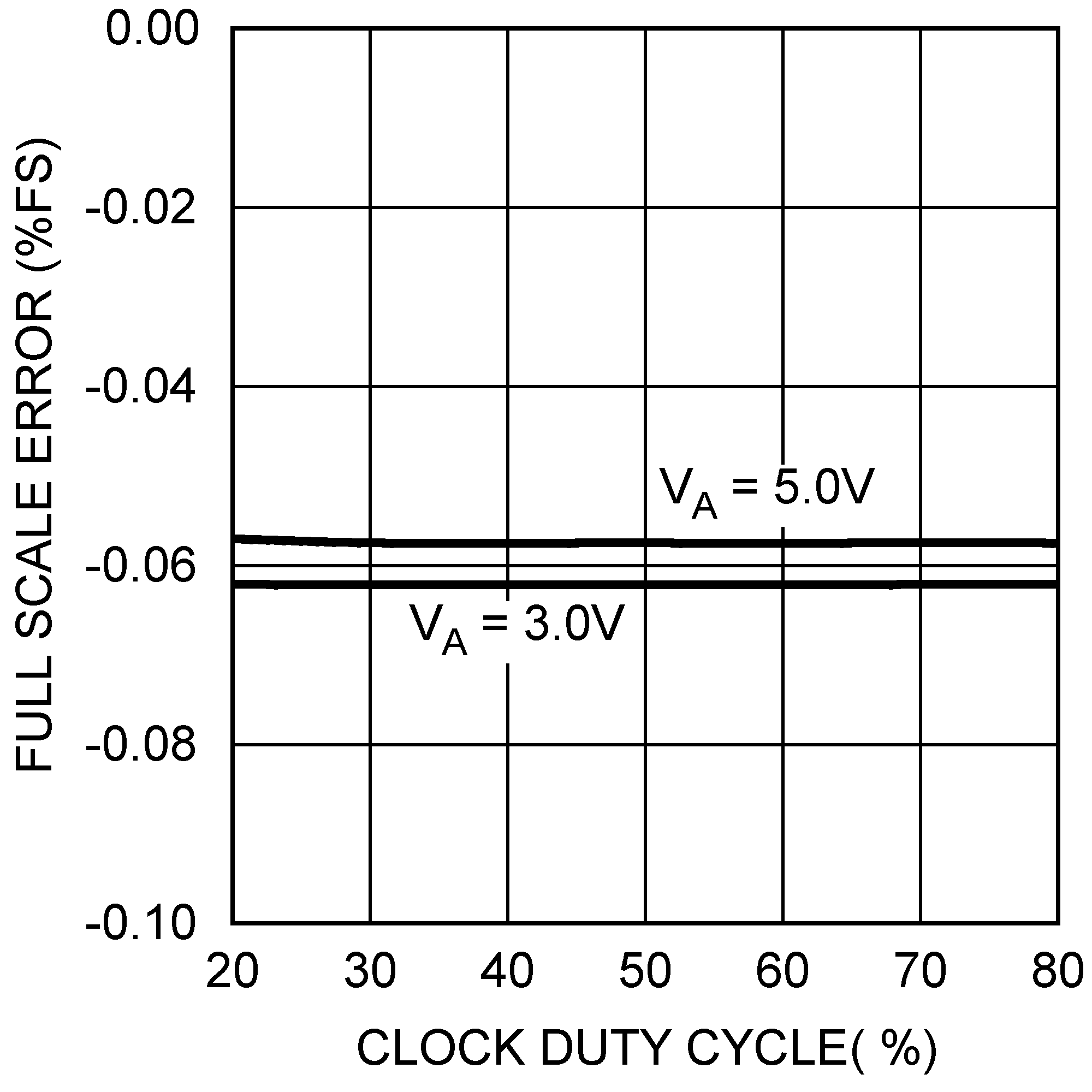

Duty Cycle Figure 5-22 Full-Scale Error vs Clock

Frequency

Figure 5-22 Full-Scale Error vs Clock

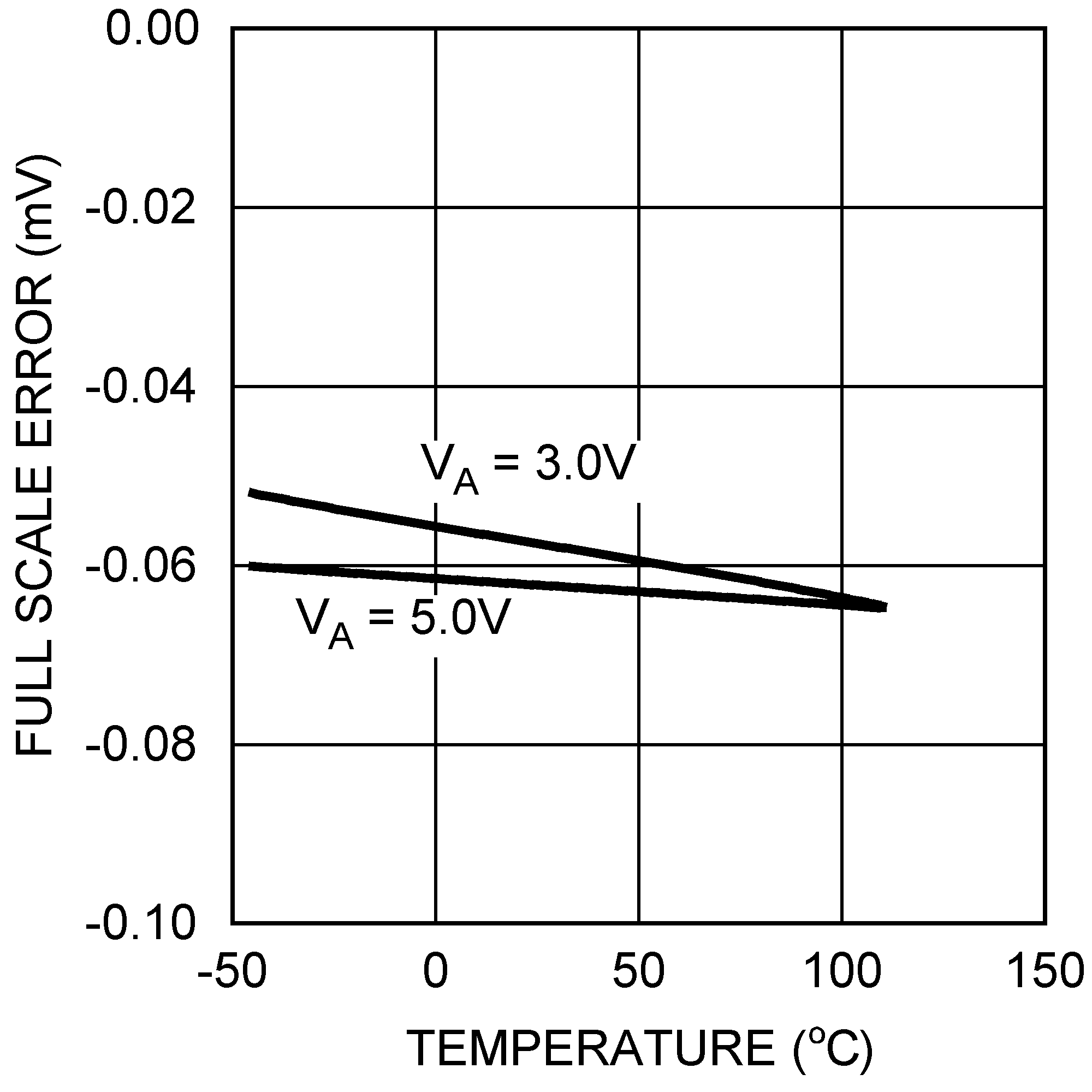

Frequency Figure 5-24 Full-Scale Error vs

Temperature

Figure 5-24 Full-Scale Error vs

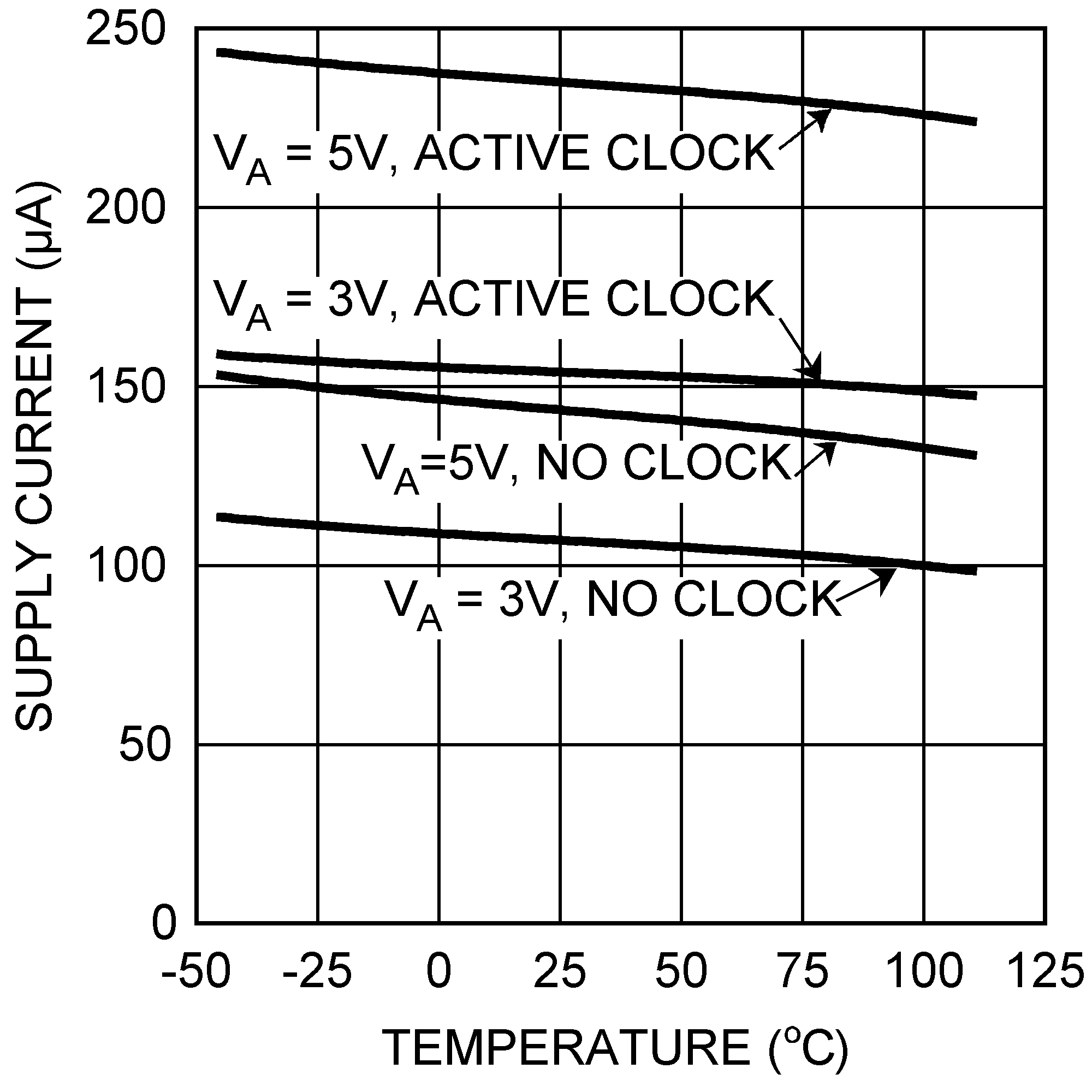

Temperature Figure 5-26 Supply Current vs

Temperature

Figure 5-26 Supply Current vs

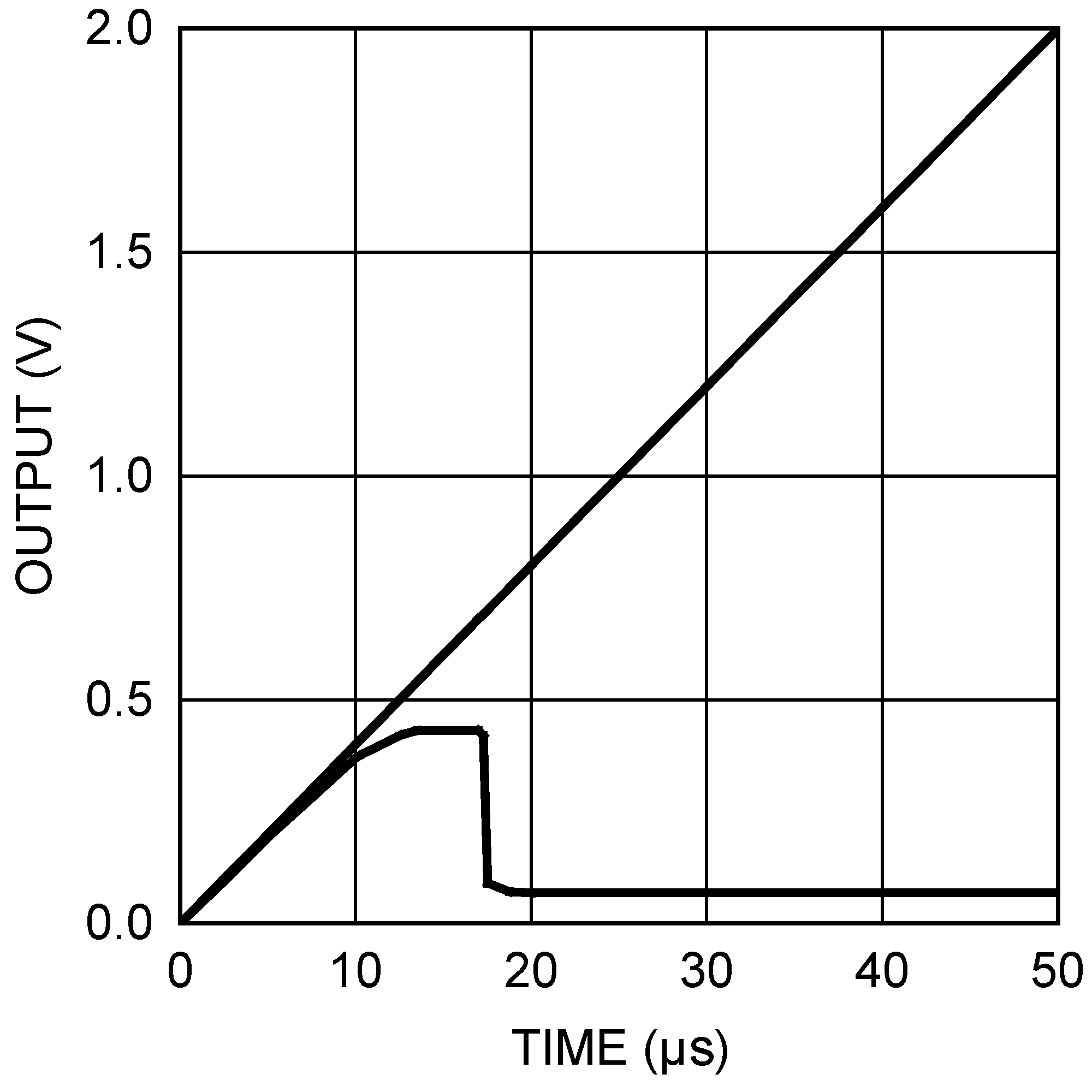

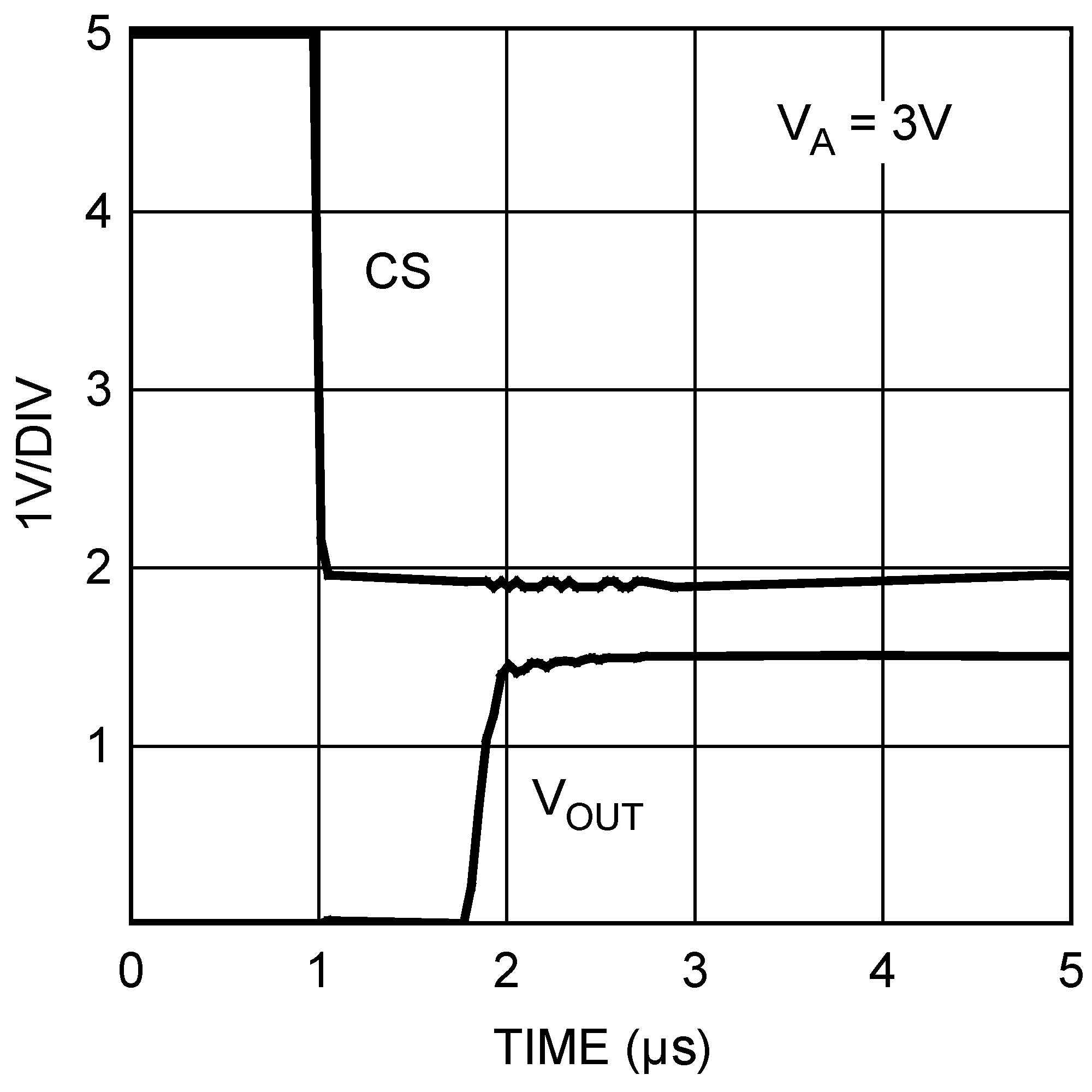

Temperature Figure 5-28 Power-On Reset

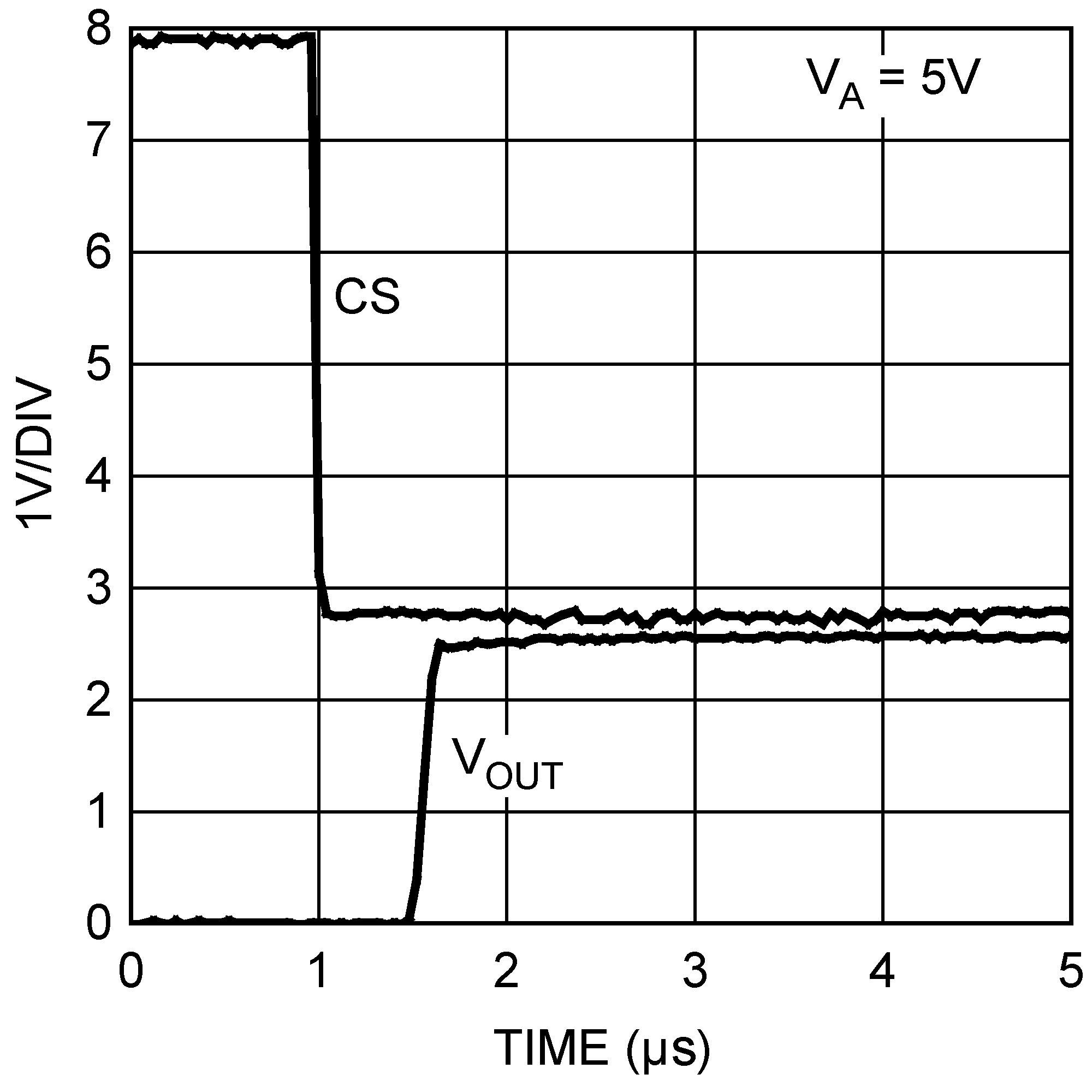

Figure 5-28 Power-On Reset Figure 5-30 5V Wake-Up Time

Figure 5-30 5V Wake-Up Time

| VA = 5V | ||

| VA = 5V | ||

Figure 5-7 INL vs Supply

Voltage

Figure 5-7 INL vs Supply

Voltage Figure 5-9 5V DNL vs Clock

Frequency

Figure 5-9 5V DNL vs Clock

Frequency Figure 5-11 5V DNL vs Clock Duty

Cycle

Figure 5-11 5V DNL vs Clock Duty

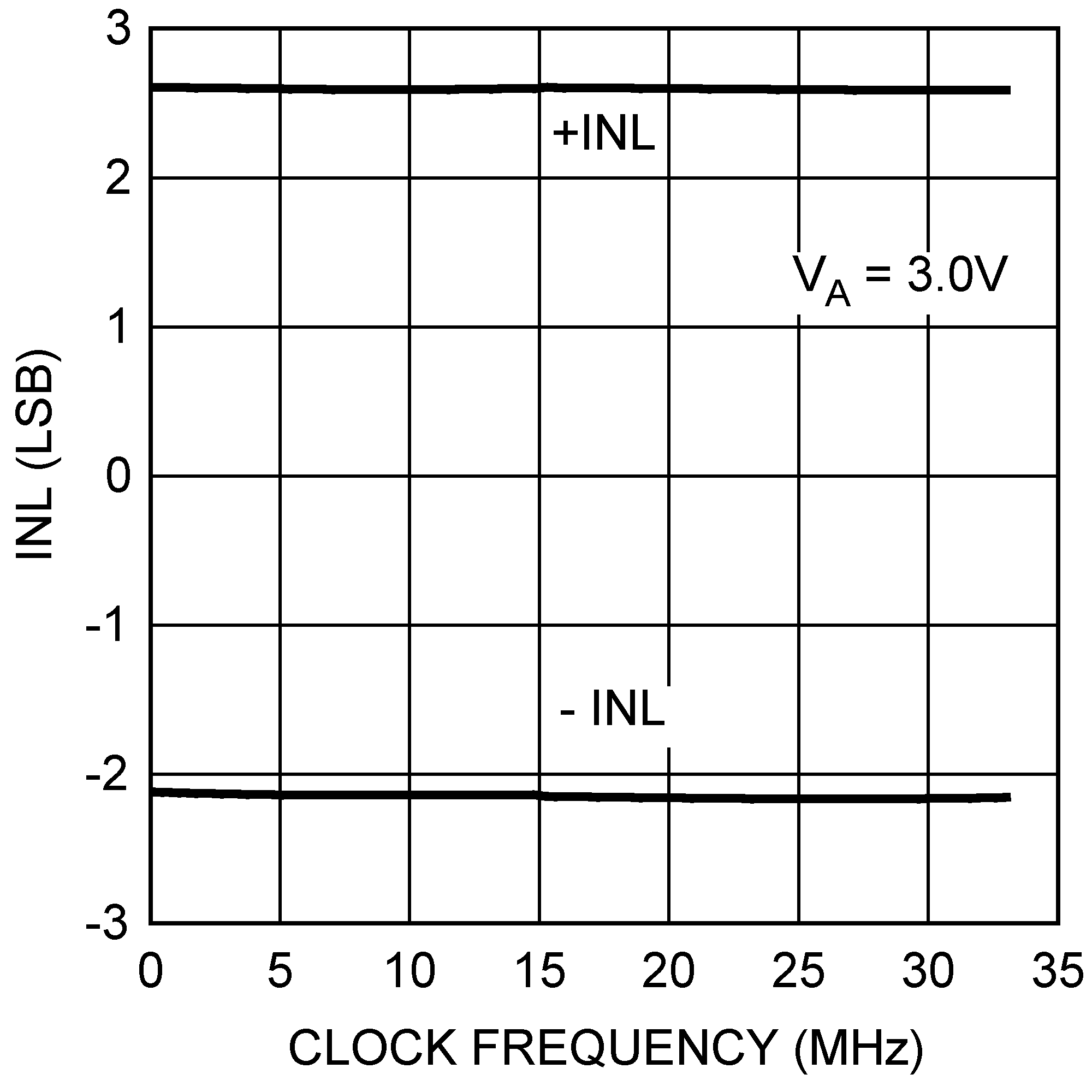

Cycle Figure 5-13 3V INL vs Clock

Frequency

Figure 5-13 3V INL vs Clock

Frequency Figure 5-15 3V INL vs Clock Duty

Cycle

Figure 5-15 3V INL vs Clock Duty

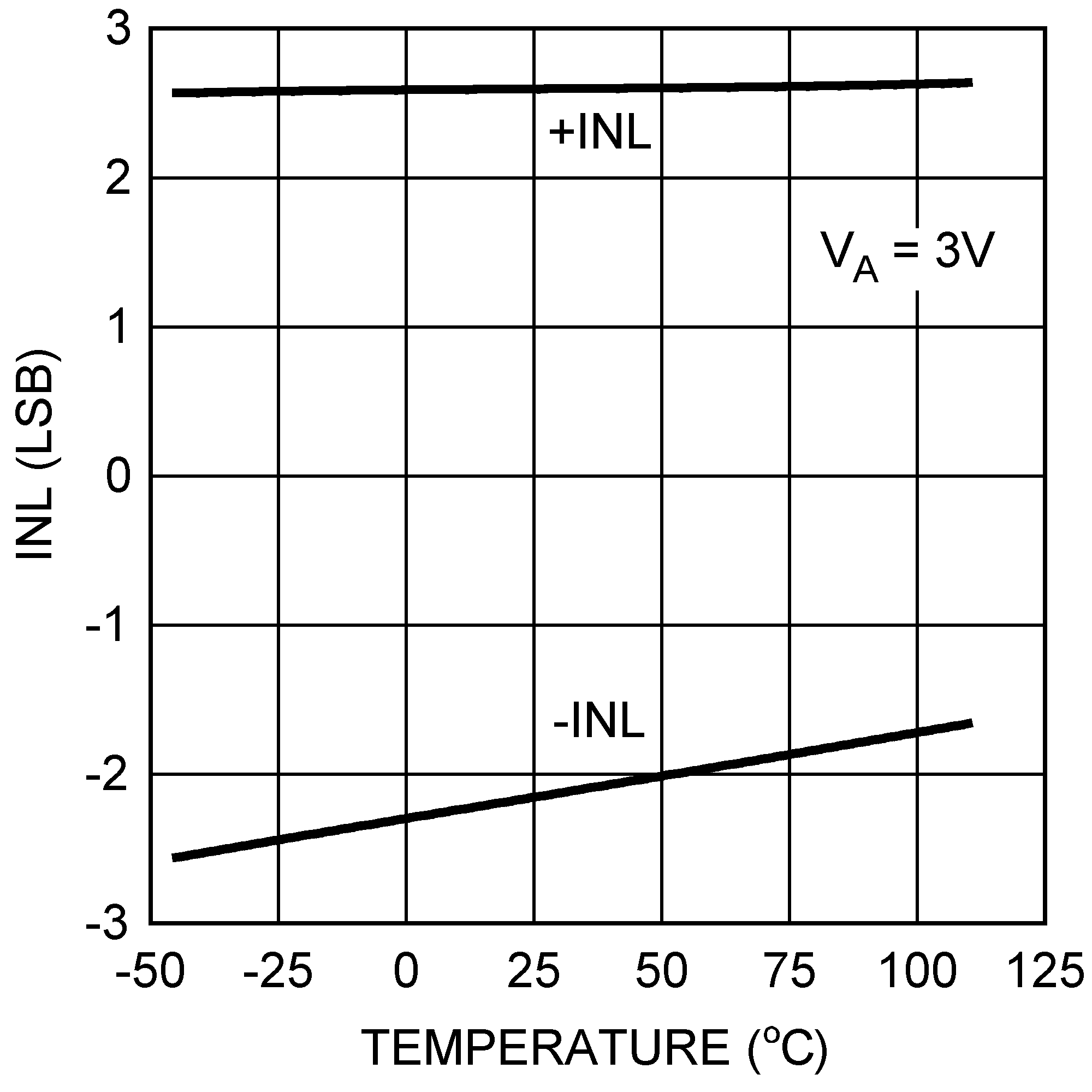

Cycle Figure 5-17 3V INL vs

Temperature

Figure 5-17 3V INL vs

Temperature Figure 5-19 Zero Code Error vs Clock

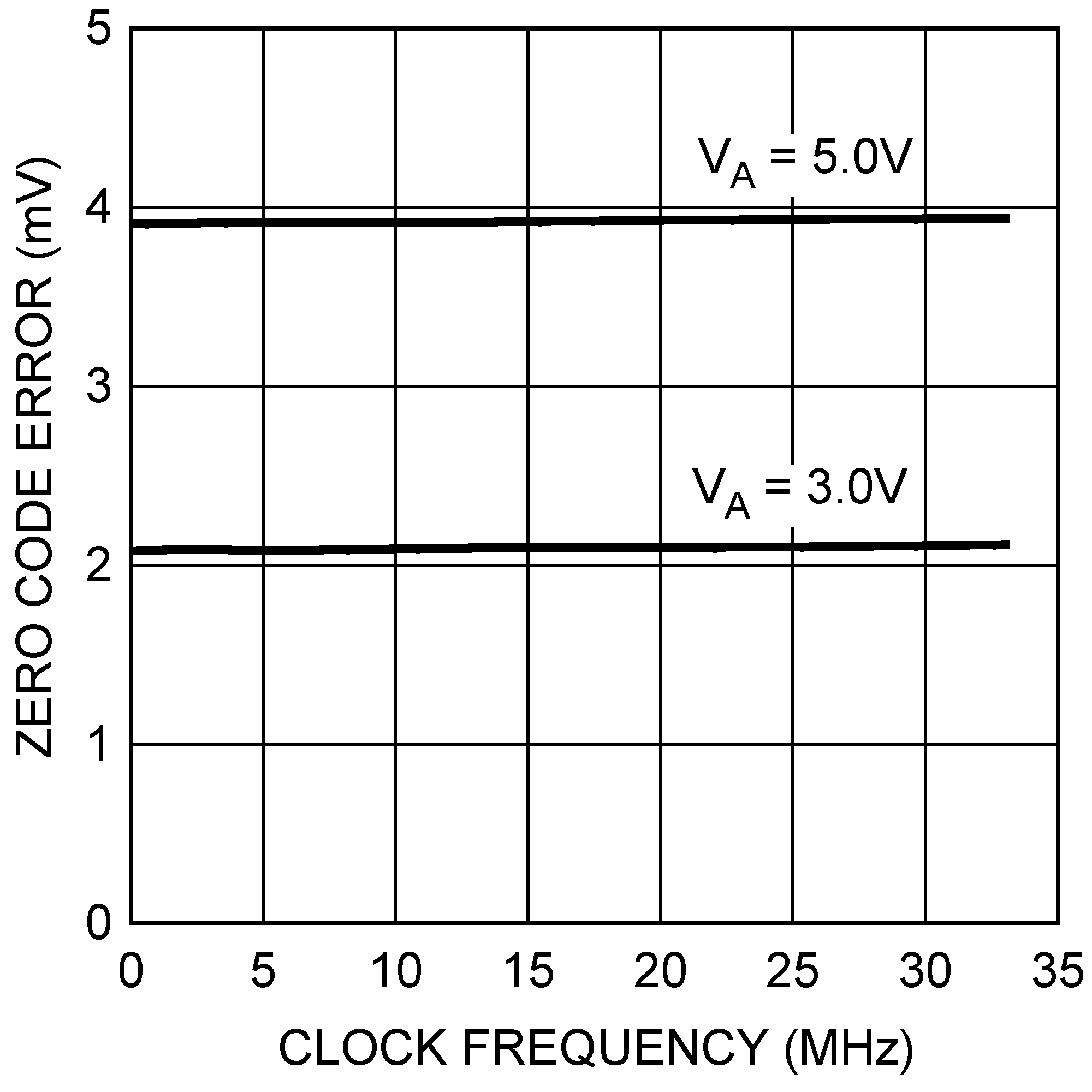

Frequency

Figure 5-19 Zero Code Error vs Clock

Frequency Figure 5-21 Zero Code Error vs

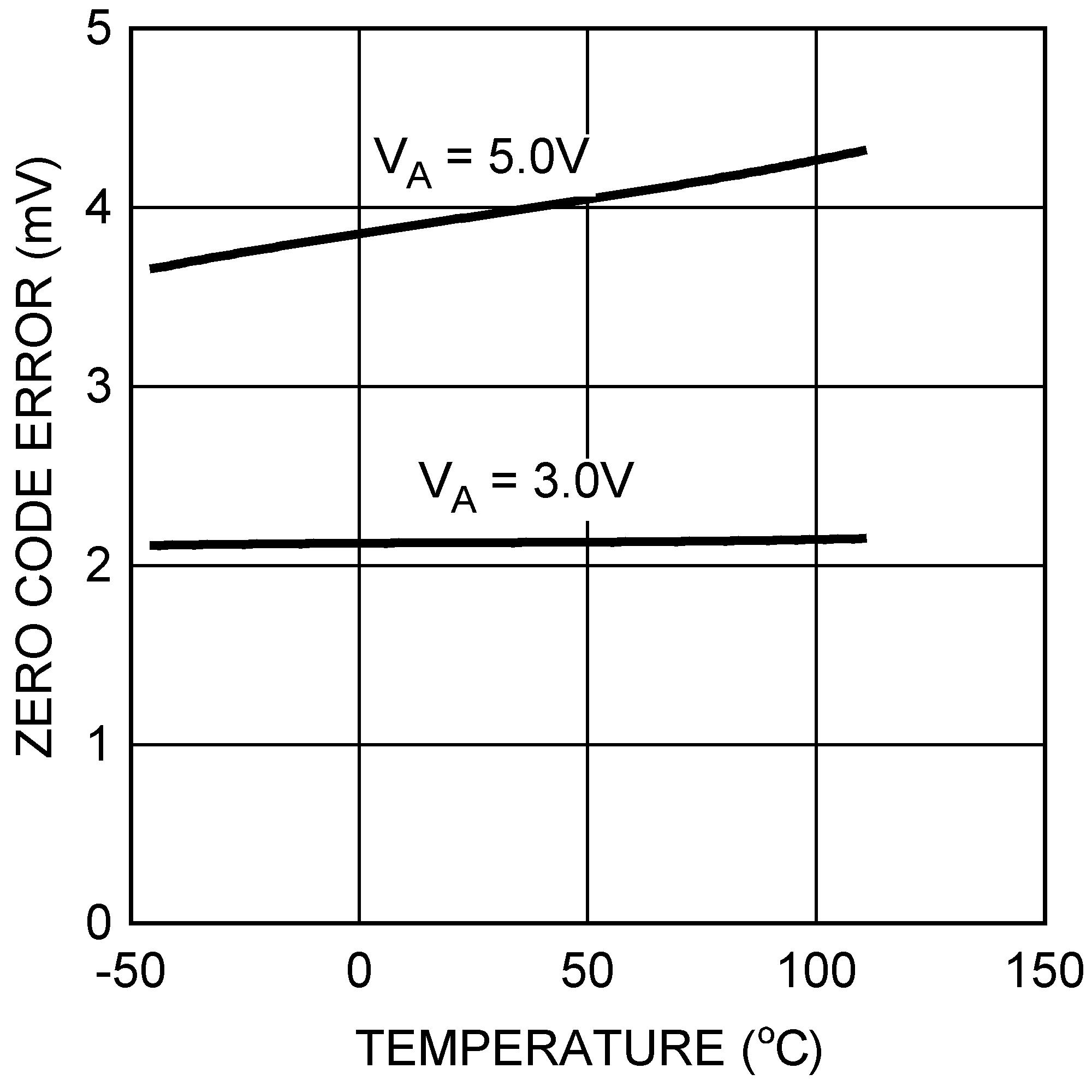

Temperature

Figure 5-21 Zero Code Error vs

Temperature Figure 5-23 Full-Scale Error vs Clock

Duty Cycle

Figure 5-23 Full-Scale Error vs Clock

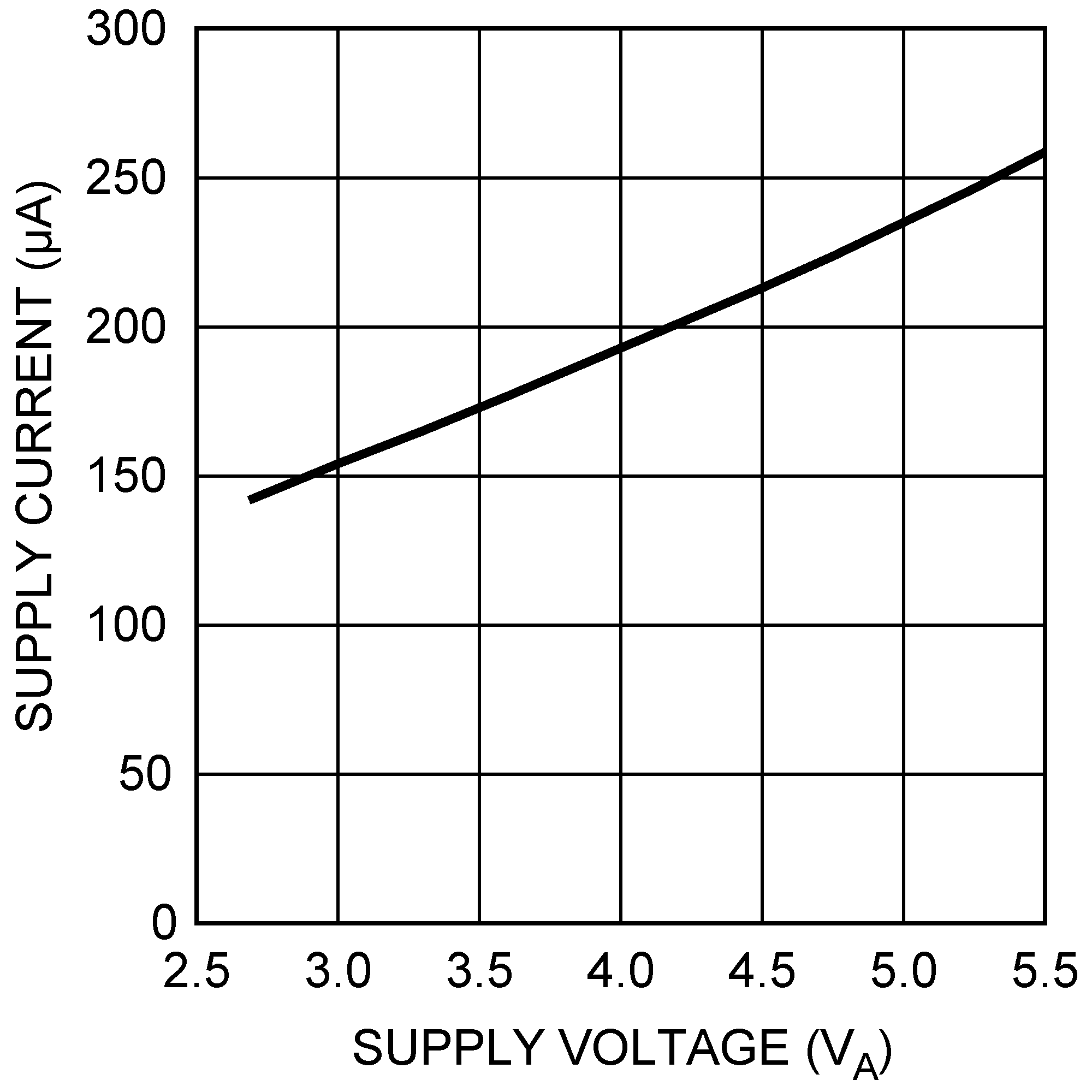

Duty Cycle Figure 5-25 Supply Current vs Supply

Voltage

Figure 5-25 Supply Current vs Supply

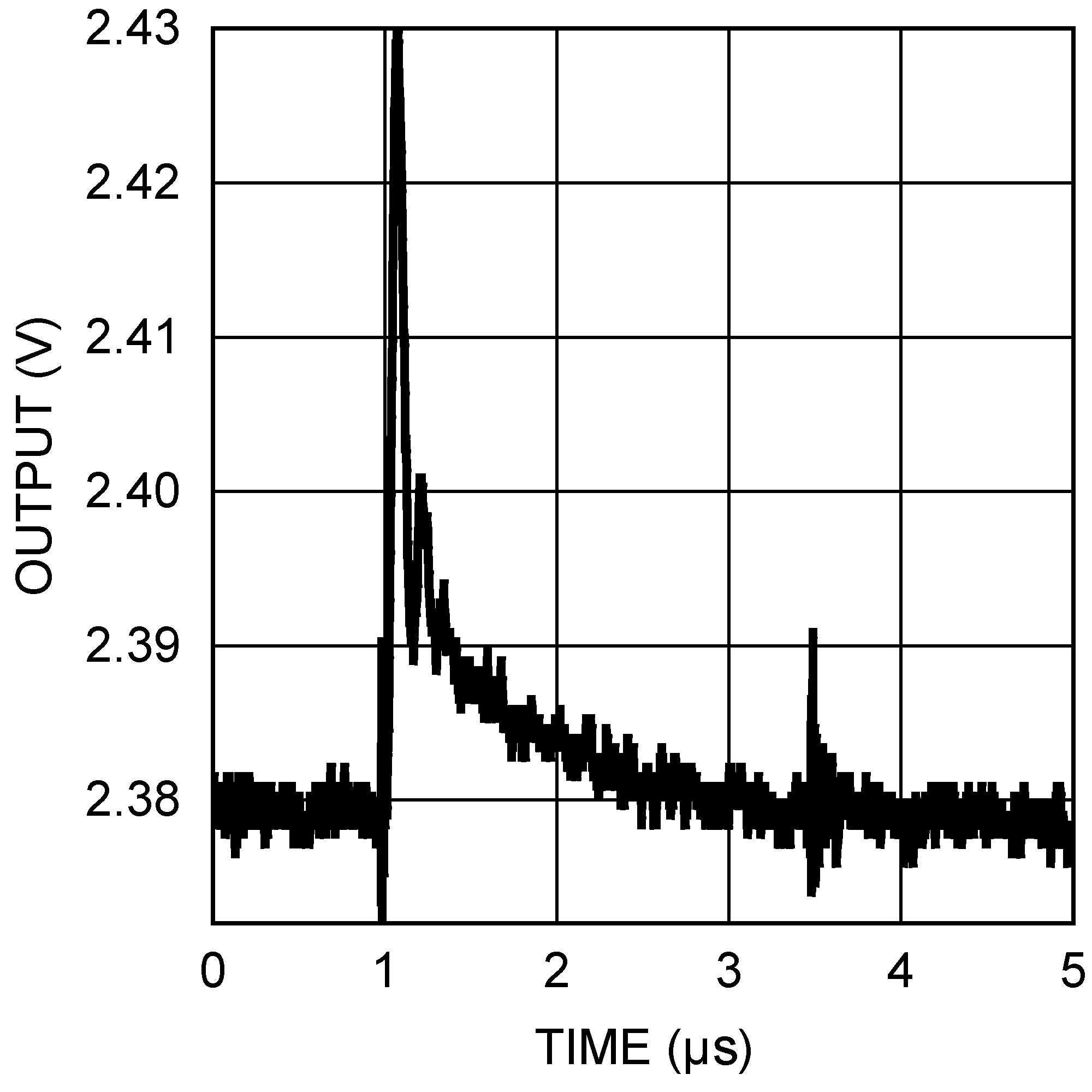

Voltage Figure 5-27 5V Glitch

Response

Figure 5-27 5V Glitch

Response Figure 5-29 3V Wake-Up Time

Figure 5-29 3V Wake-Up Time