SNLS767A April 2024 – October 2024 DP83TC817S-Q1

PRODUCTION DATA

- 1

- 1Features

- 2Applications

- 3Description

- 4Device Comparison Table

- 5Application Information

- 6Device and Documentation Support

- 7Revision History

- 8Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RHA|36

Thermal pad, mechanical data (Package|Pins)

- RHA|36

Orderable Information

5.4 DP83TC817EVM-MC and Software Support

DP83TC817EVM-MC

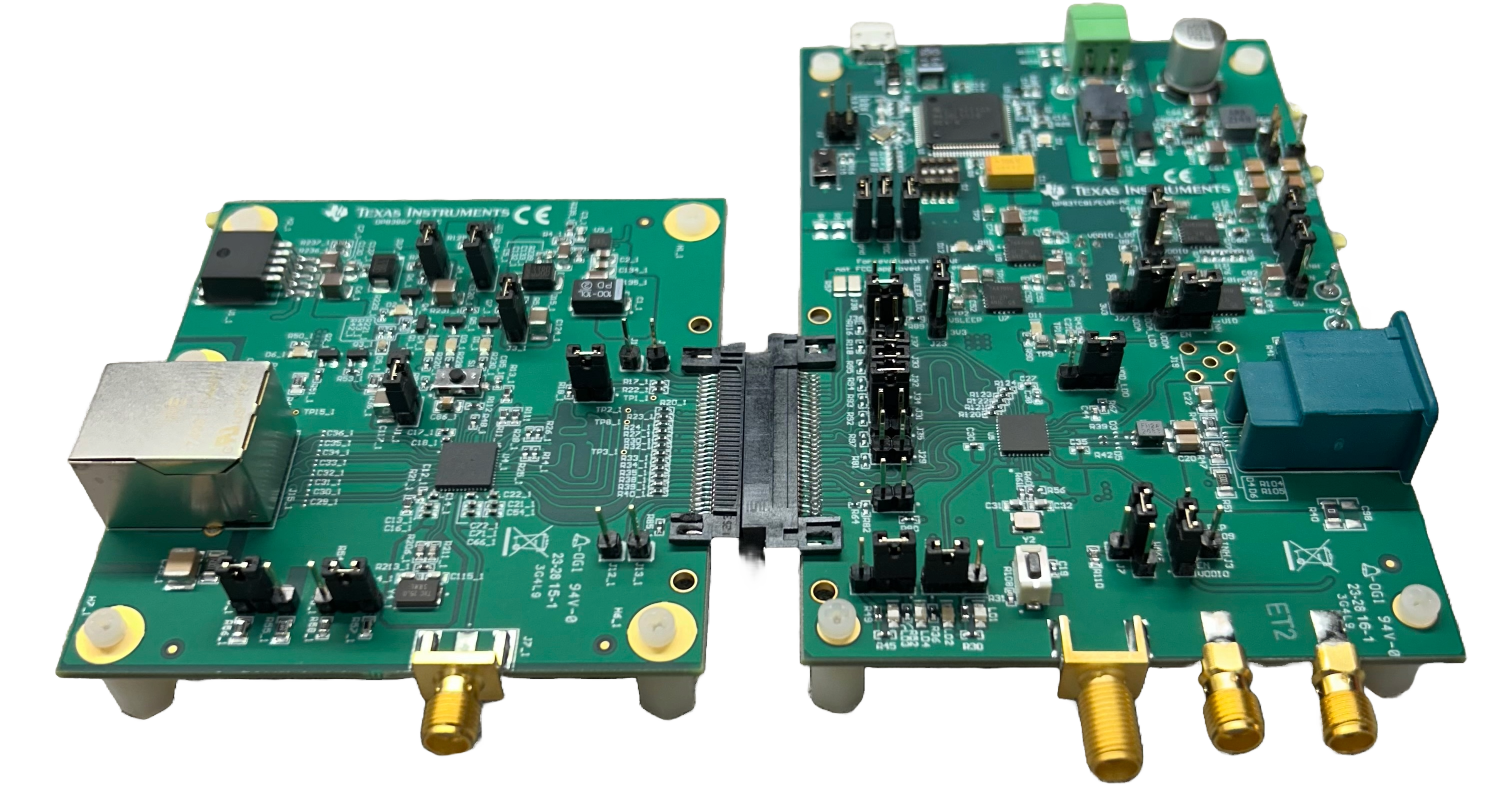

The DP83TC817EVM-MCsupports 100-Mbps speed and is IEEE 802.3bw compliant. This evaluation board is a media converter from 100Base-TX to 100Base-T1. There is an onboard MSP430F5529 for MDIO/MDC register access with the USB2MDIO and DIEP graphical user interface tools. DP83867 is provided for copper (100BASE-TX) support using RGMII MAC interface.

Figure 5-5 DP83TC817EVM-MC

Figure 5-5 DP83TC817EVM-MC- TC10 Support

- Jumpers to customize PHY strap settings

- Option to supply external reference clock

- Additional test points for debug

- Status LEDs

- Link

- Link + Activity

- Power-On

- EVM User's Guide for reference

DIEP offers all your Ethernet PHY debug needs in one place including MDIO bus serial management, device control registers, access to both extended registers and standard registers, and the ability to save data read and run script text files.

|