SNOSD55 June 2017 LF356-MIL

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 AC Electrical Characteristics, TA = TJ = 25°C, VS = ±15 V

- 6.6 DC Electrical Characteristics, TA = TJ = 25°C, VS = ±15 V

- 6.7 DC Electrical Characteristics

- 6.8 Power Dissipation Ratings

- 6.9 Typical Characteristics

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YS|0

- LMC|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(1)(2)| MIN | MAX | UNIT | ||||

|---|---|---|---|---|---|---|

| Supply voltage | ±18 | V | ||||

| Differential input voltage | ±30 | V | ||||

| Input voltage(2) | ±16 | V | ||||

| Output short circuit duration | Continuous | — | ||||

| TJMAX | LMC package | 115 | °C | |||

| P package | 100 | |||||

| D package | 100 | |||||

| Soldering information (lead temp.) |

TO-99 package | Soldering (10 sec.) | 300 | °C | ||

| PDIP package | Soldering (10 sec.) | 260 | ||||

| SOIC package | Vapor phase (60 sec.) | 215 | ||||

| Infrared (15 sec.) | 220 | |||||

| Storage temperature, Tstg | −65 | 150 | °C | |||

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, contact the TI Sales Office/Distributors for availability and specifications.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1)(2) | ±1000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) 100 pF discharged through 1.5-kΩ resistor

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| Supply voltage, VS | ±15 | V | |||

| TA | 0 | TA | 70 | °C | |

6.4 Thermal Information

| THERMAL METRIC(1) | LF356-MIL | UNIT | |||

|---|---|---|---|---|---|

| D (SOIC) | P (PDIP) | ||||

| 8 PINS | 8 PINS | ||||

| RθJA | Junction-to-ambient thermal resistance | 112.5 | 55.2 | °C/W | |

| RθJC(top) | Junction-to-case (top) thermal resistance | 58.8 | 44.5 | °C/W | |

| RθJB | Junction-to-board thermal resistance | 52.8 | 32.4 | °C/W | |

| ψJT | Junction-to-top characterization parameter | 12.8 | 21.7 | °C/W | |

| ψJB | Junction-to-board characterization parameter | 52.3 | 32.3 | °C/W | |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

6.5 AC Electrical Characteristics, TA = TJ = 25°C, VS = ±15 V

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| SR | Slew Rate | AV = 1 | 12 | V/μs | ||||

| GBW | Gain Bandwidth Product | 5 | MHz | |||||

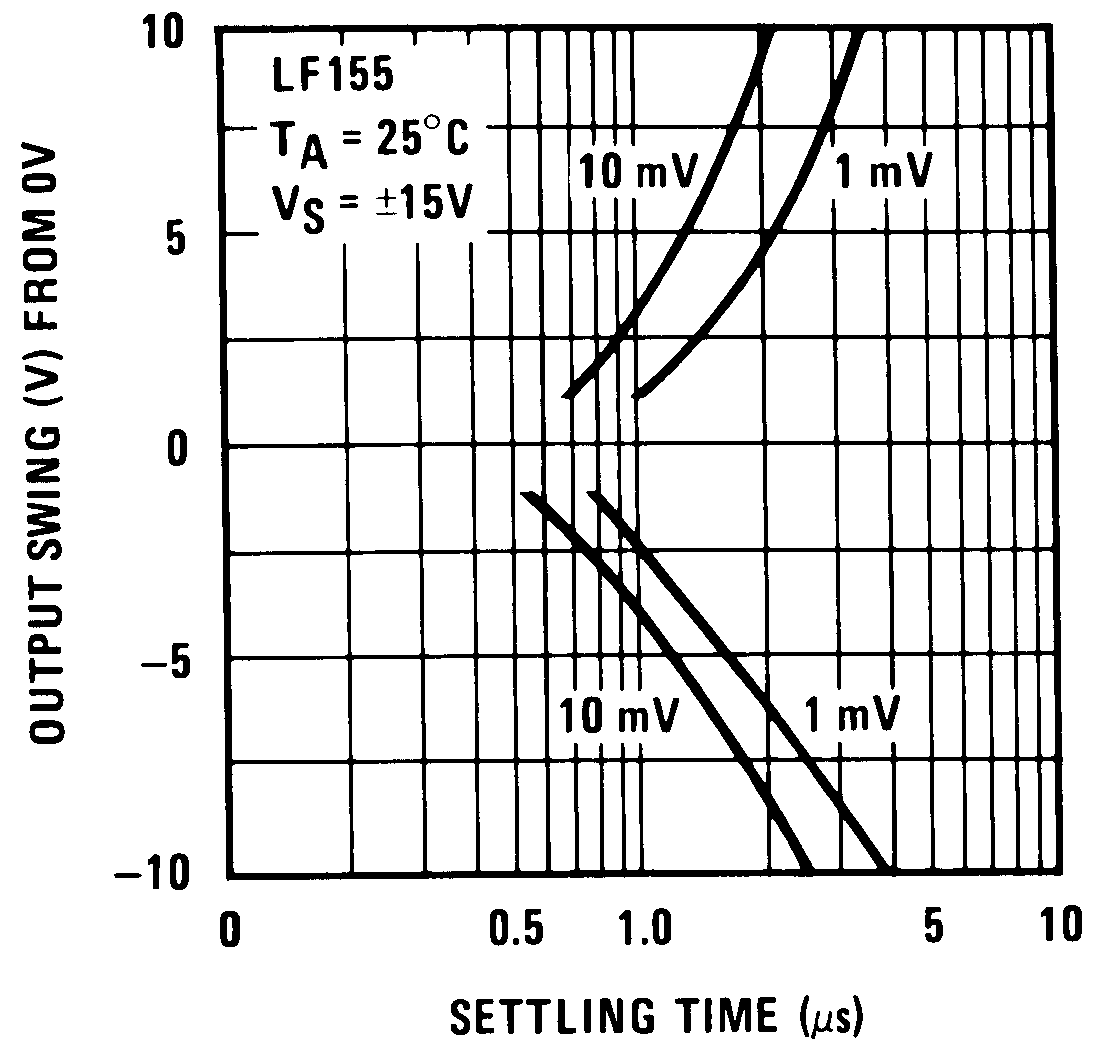

| ts | Settling Time to 0.01%(1) | 1.5 | μs | |||||

| en | Equivalent Input Noise Voltage | RS = 100 Ω | f = 100 Hz | 15 | nV/√Hz | |||

| f = 1000 Hz | 12 | nV/√Hz | ||||||

| in | Equivalent Input Current Noise | f = 100 Hz | 0.01 | pA/√Hz | ||||

| f = 1000 Hz | 0.01 | pA/√Hz | ||||||

| CIN | Input Capacitance | 3 | pF | |||||

(1) Settling time is defined here, for a unity gain inverter connection using 2-kΩ resistors for the LF15x. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 10-V step input is applied to the inverter. For the LF357, AV = −5, the feedback resistor from output to input is 2 kΩ and the output step is 10 V (See Settling Time Test Circuit).

6.6 DC Electrical Characteristics, TA = TJ = 25°C, VS = ±15 V

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|

| Supply current | 5 | 10 | mA |

6.7 DC Electrical Characteristics

See (1)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| VOS | Input offset voltage | RS = 50 Ω | TA = 25°C | 3 | 10 | mV | ||

| Over temperature | 13 | |||||||

| ΔVOS/ΔT | Average TC of input offset voltage |

RS = 50 Ω | 5 | μV/°C | ||||

| ΔTC/ΔVOS | Change in average TC with VOS adjust | RS = 50 Ω(3) | 0.5 | μV/°C per mV |

||||

| IOS | Input offset current | TJ = 25°C(1) (4) | 3 | 50 | pA | |||

| TJ ≤ THIGH | 2 | nA | ||||||

| IB | Input bias current | TJ = 25°C(1) (4) | 30 | 200 | pA | |||

| TJ ≤ THIGH | 8 | nA | ||||||

| RIN | Input resistance | TJ = 25°C | 1012 | Ω | ||||

| AVOL | Large signal voltage gain | VS = ±15 V, VO = ±10 V, RL = 2 kΩ |

TA = 25°C | 25 | 200 | V/mV | ||

| Over temperature | 15 | |||||||

| VO | Output voltage swing | VS = ±15 V, RL = 10 kΩ | ±12 | ±13 | V | |||

| VS = ±15 V, RL= 2 kΩ | ±10 | ±12 | ||||||

| VCM | Input common-mode voltage range |

VS = ±15 V | VCM, High | 10 | 15.1 | V | ||

| VCM, Low | −12 | –10 | ||||||

| CMRR | Common-mode rejection ratio | 80 | 100 | dB | ||||

| PSRR | Supply voltage rejection ratio(5) | 80 | 100 | dB | ||||

(1) Unless otherwise stated, these test conditions apply:

and VOS, IB and IOS are measured at VCM = 0.

| Supply Voltage, VS | VS = ±15 V |

| TA | 0°C ≤ TA ≤ +70°C |

| THIGH | +70°C |

(2) Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

(3) The Temperature Coefficient of the adjusted input offset voltage changes only a small amount (0.5 μV/°C typically) for each mV of adjustment from its original unadjusted value. Common-mode rejection and open-loop voltage gain are also unaffected by offset adjustment.

(4) The input bias currents are junction leakage currents which approximately double for every 10°C increase in the junction temperature, TJ. Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, Pd. TJ = TA + θJA Pd where θJA is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

(5) Supply Voltage Rejection is measured for both supply magnitudes increasing or decreasing simultaneously, in accordance with common practice.

6.8 Power Dissipation Ratings

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Power Dissipation at TA = 25°C (1) (2) |

LMC Package (Still Air) | 400 | mW | ||

| LMC Package (400 LF/Min Air Flow) |

1000 | ||||

| P Package | 670 | ||||

| D Package | 380 | ||||

(1) The maximum power dissipation for these devices must be derated at elevated temperatures and is dictated by TJMAX, θJA, and the ambient temperature, TA. The maximum available power dissipation at any temperature is PD = (TJMAX − TA) / θJA or the 25°C PdMAX, whichever is less.

(2) Maximum power dissipation is defined by the package characteristics. Operating the part near the maximum power dissipation may cause the part to operate outside specified limits.

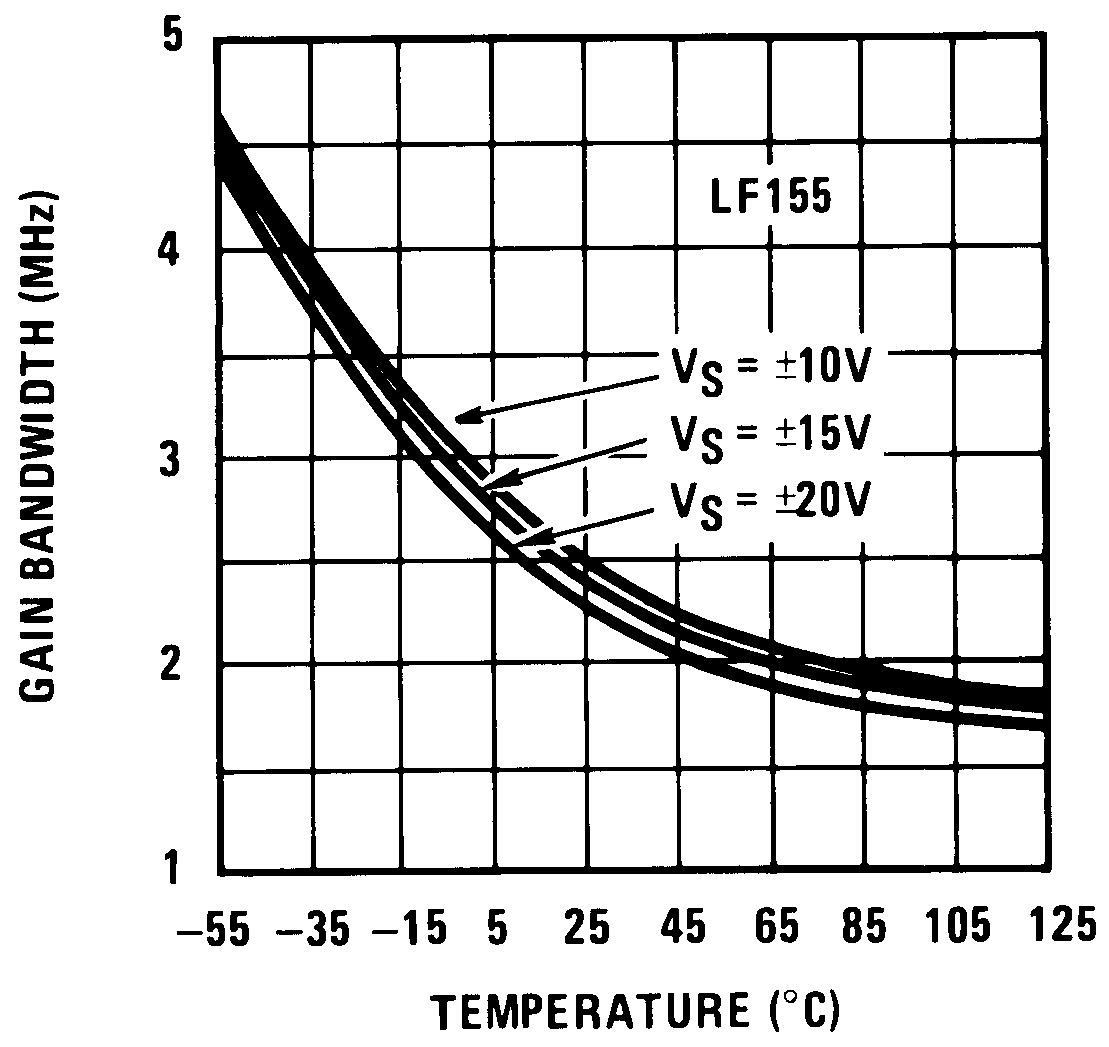

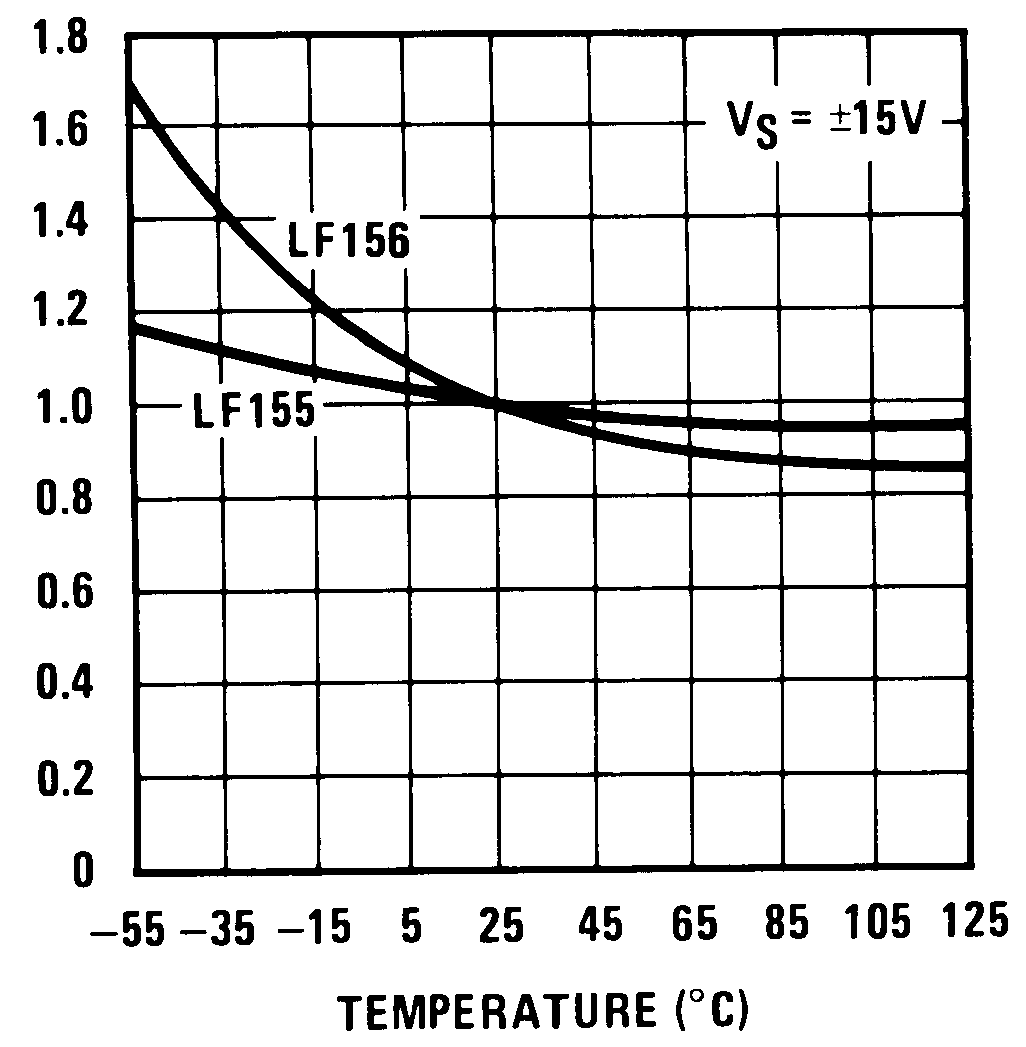

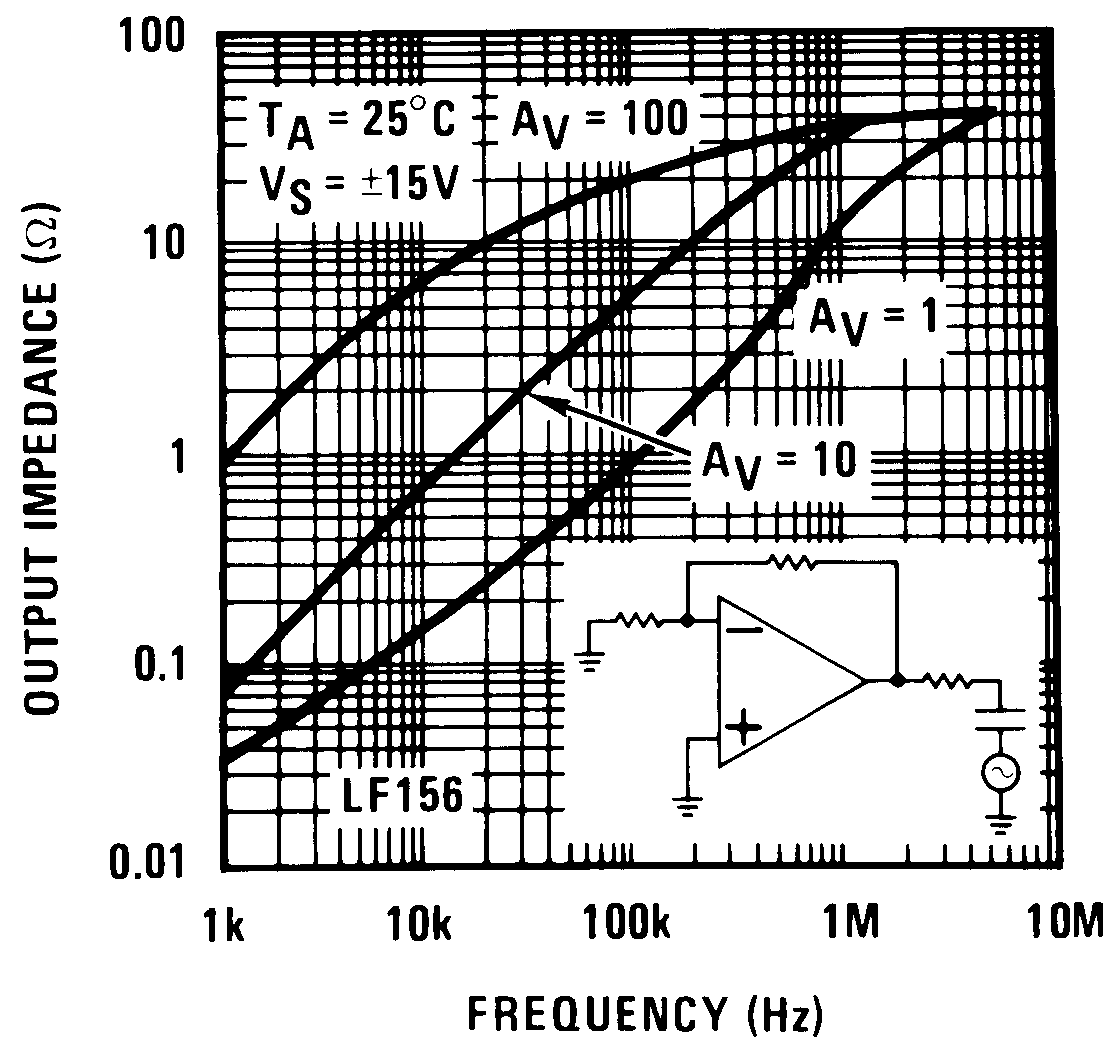

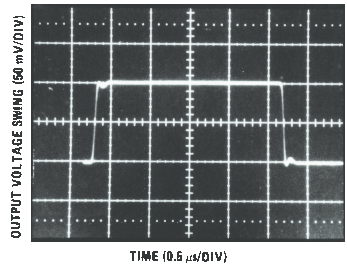

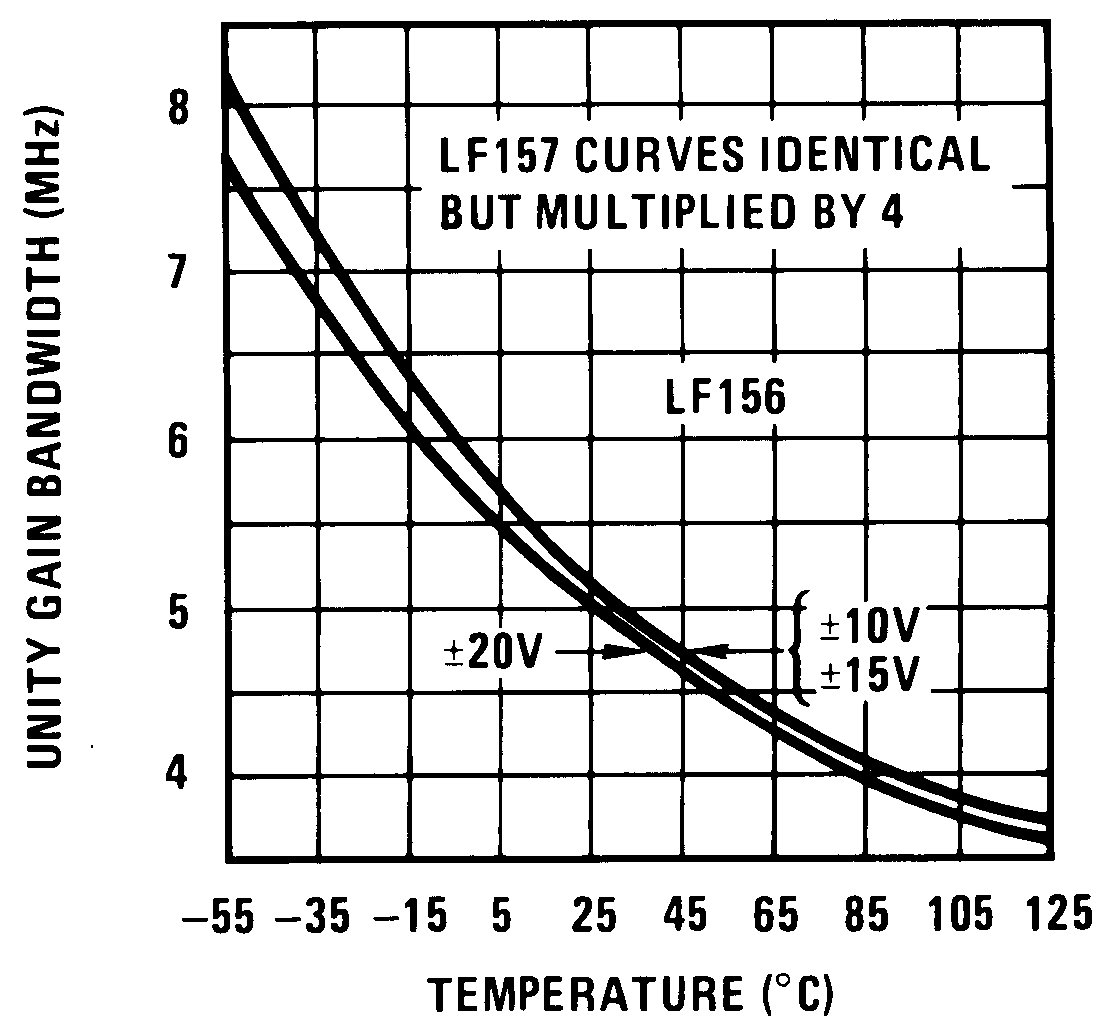

6.9 Typical Characteristics

6.9.1 Typical AC Performance Characteristics

Figure 1. Gain Bandwidth

Figure 1. Gain Bandwidth

Figure 3. Normalized Slew Rate

Figure 3. Normalized Slew Rate

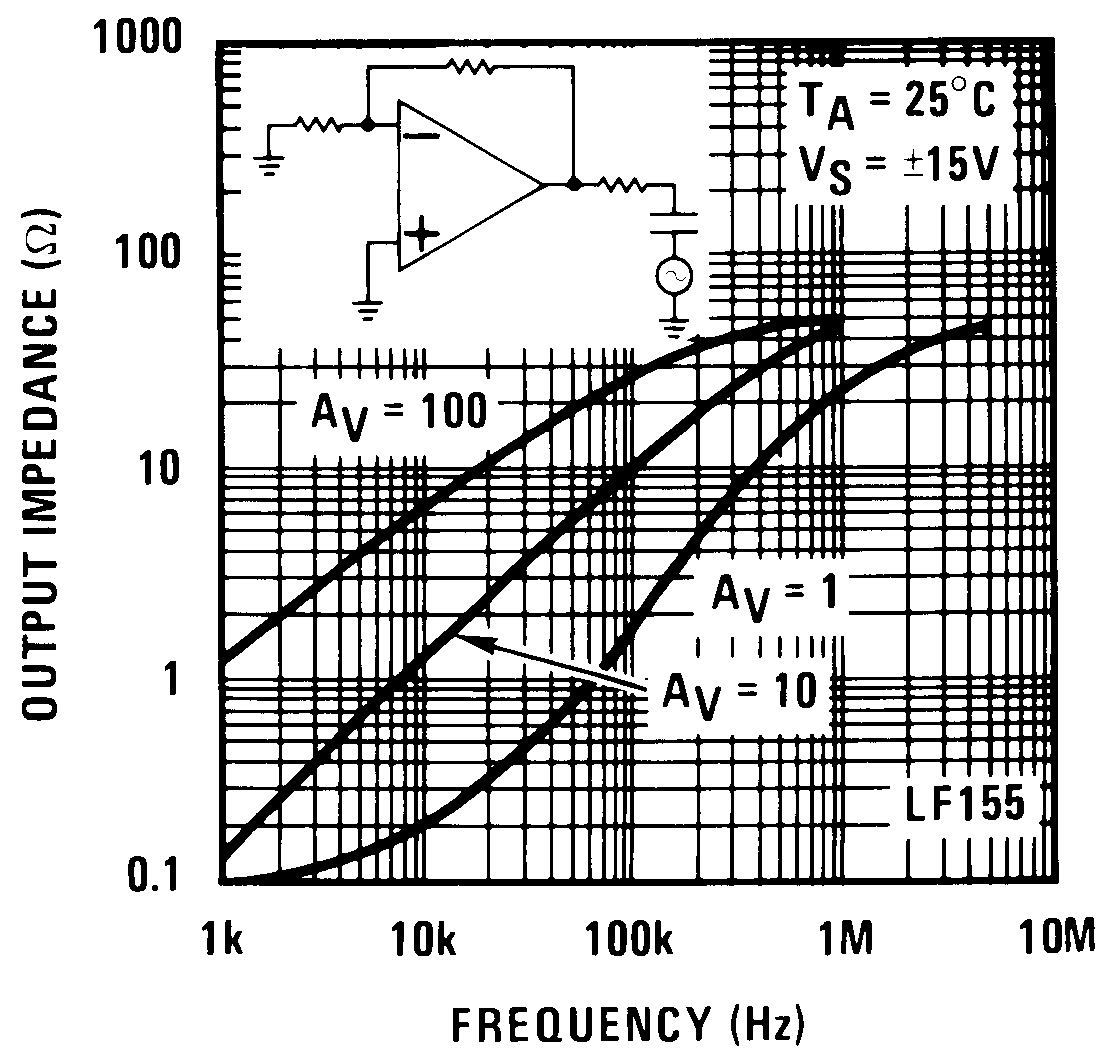

Figure 5. Output Impedance

Figure 5. Output Impedance

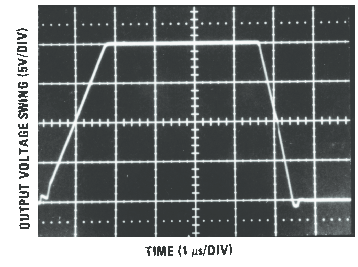

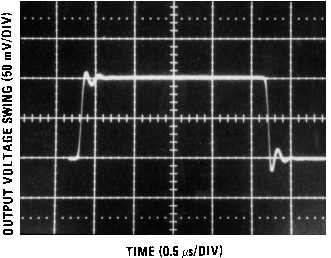

Figure 7. LF156 Small Signal Pulse Response, AV = +1

Figure 7. LF156 Small Signal Pulse Response, AV = +1

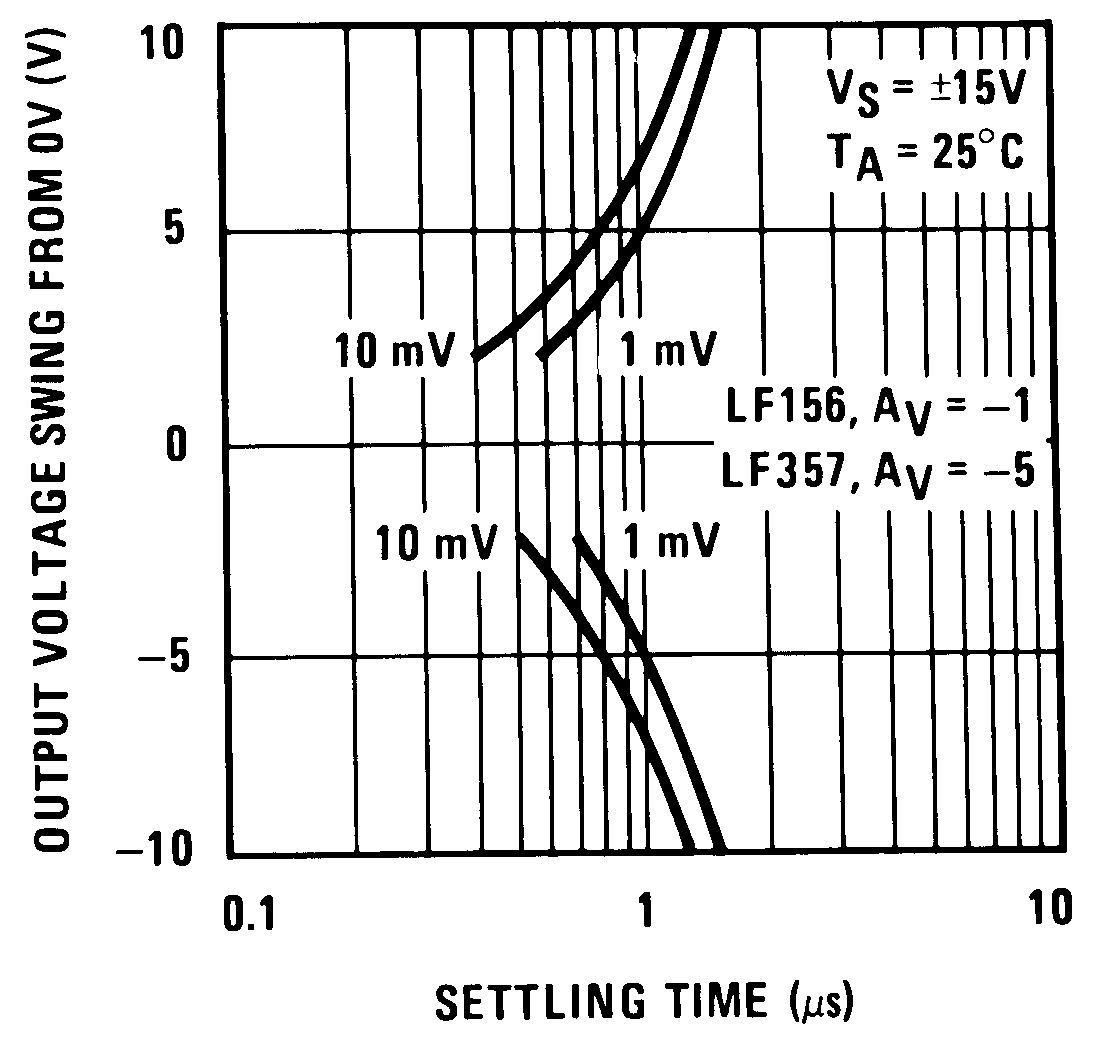

Figure 11. Inverter Settling Time

Figure 11. Inverter Settling Time

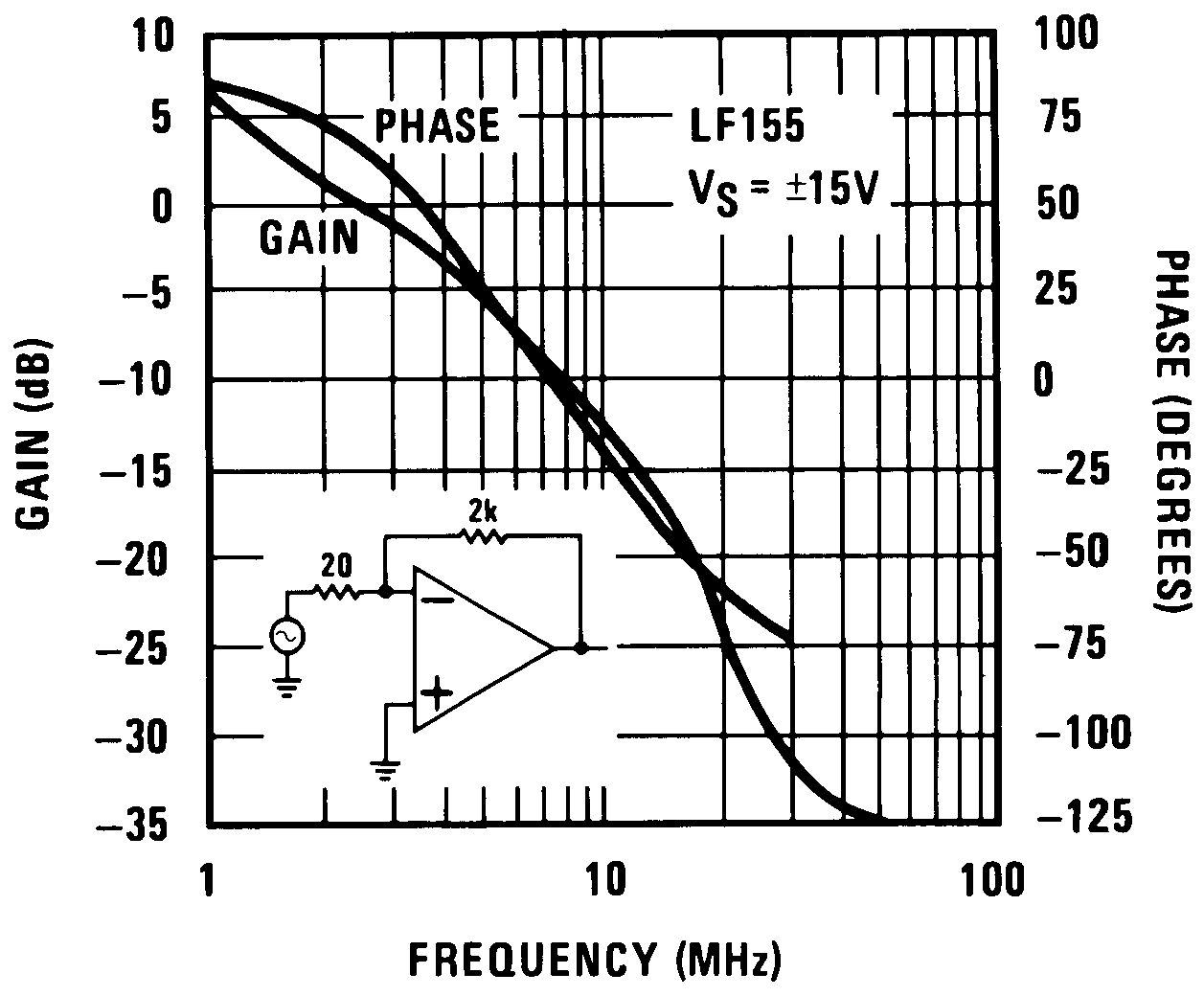

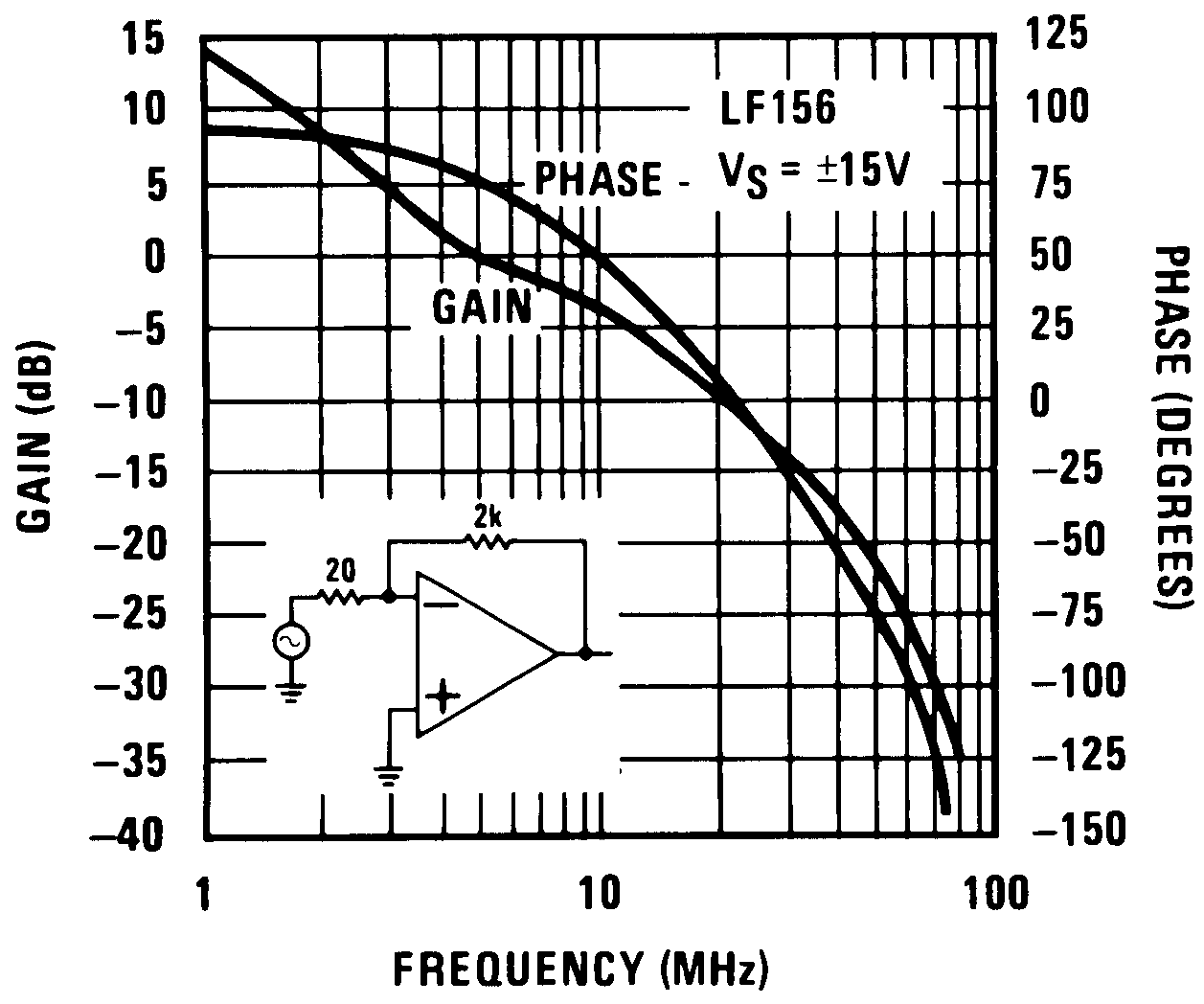

Figure 13. Bode Plot

Figure 13. Bode Plot

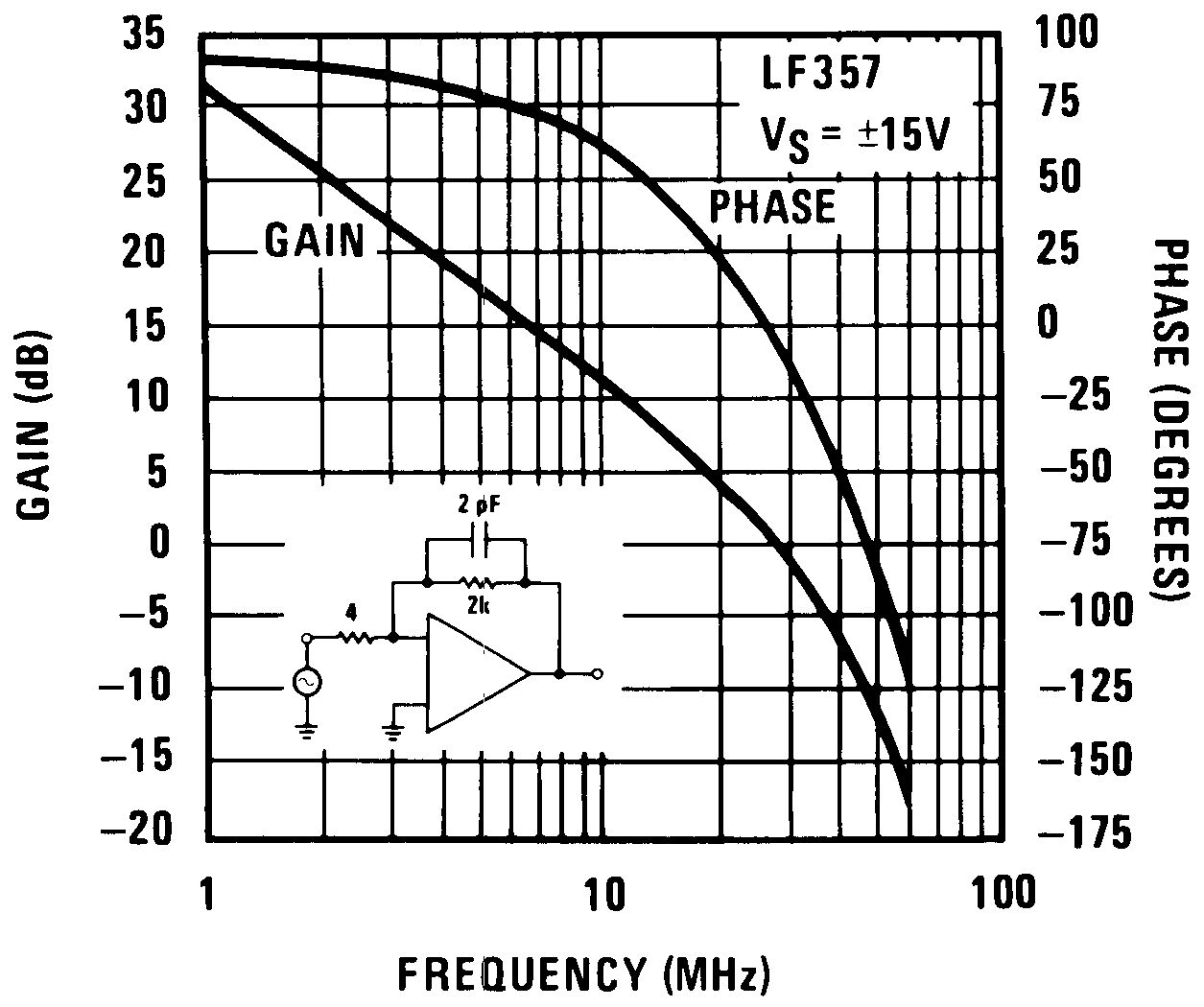

Figure 15. Bode Plot

Figure 15. Bode Plot

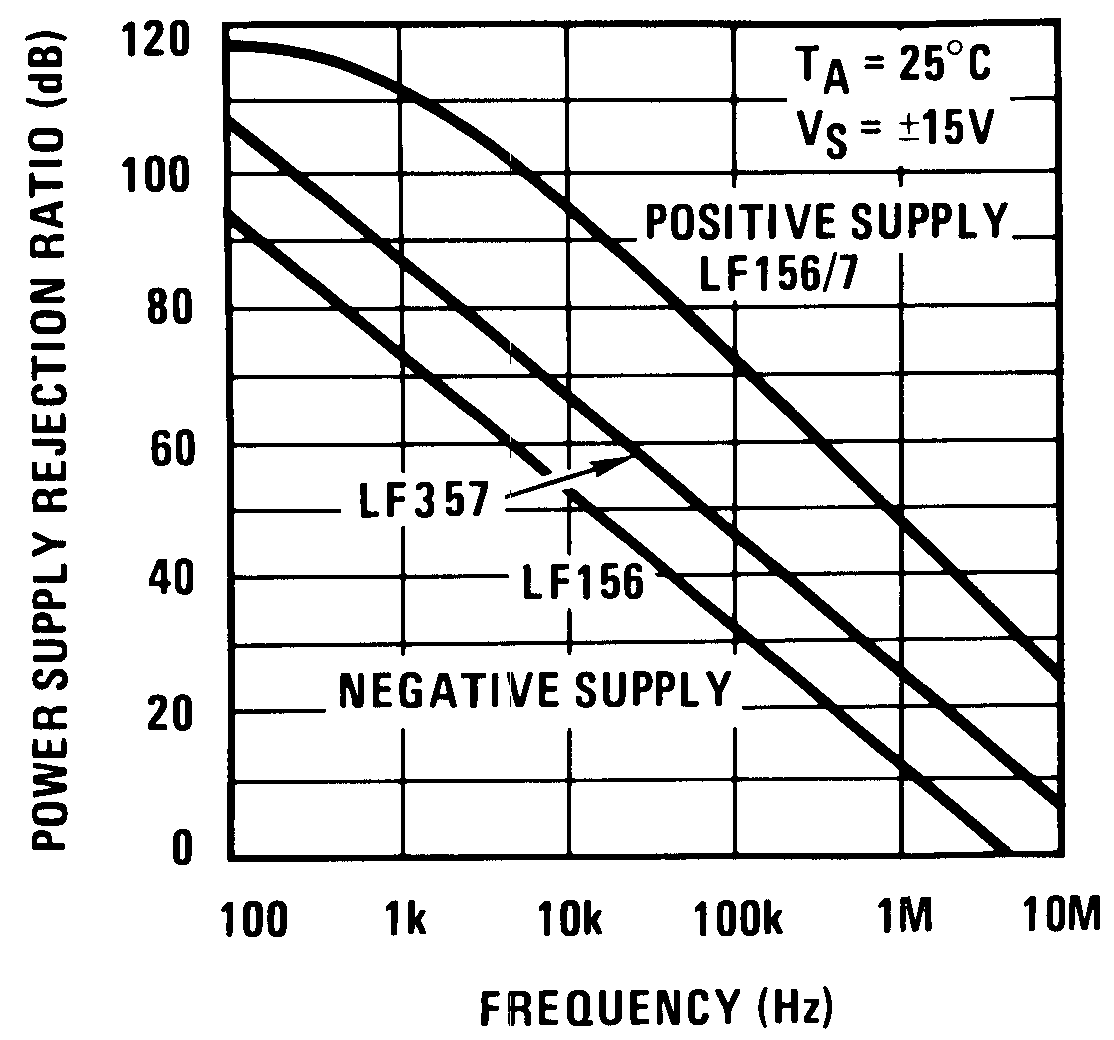

Figure 17. Power Supply Rejection Ratio

Figure 17. Power Supply Rejection Ratio

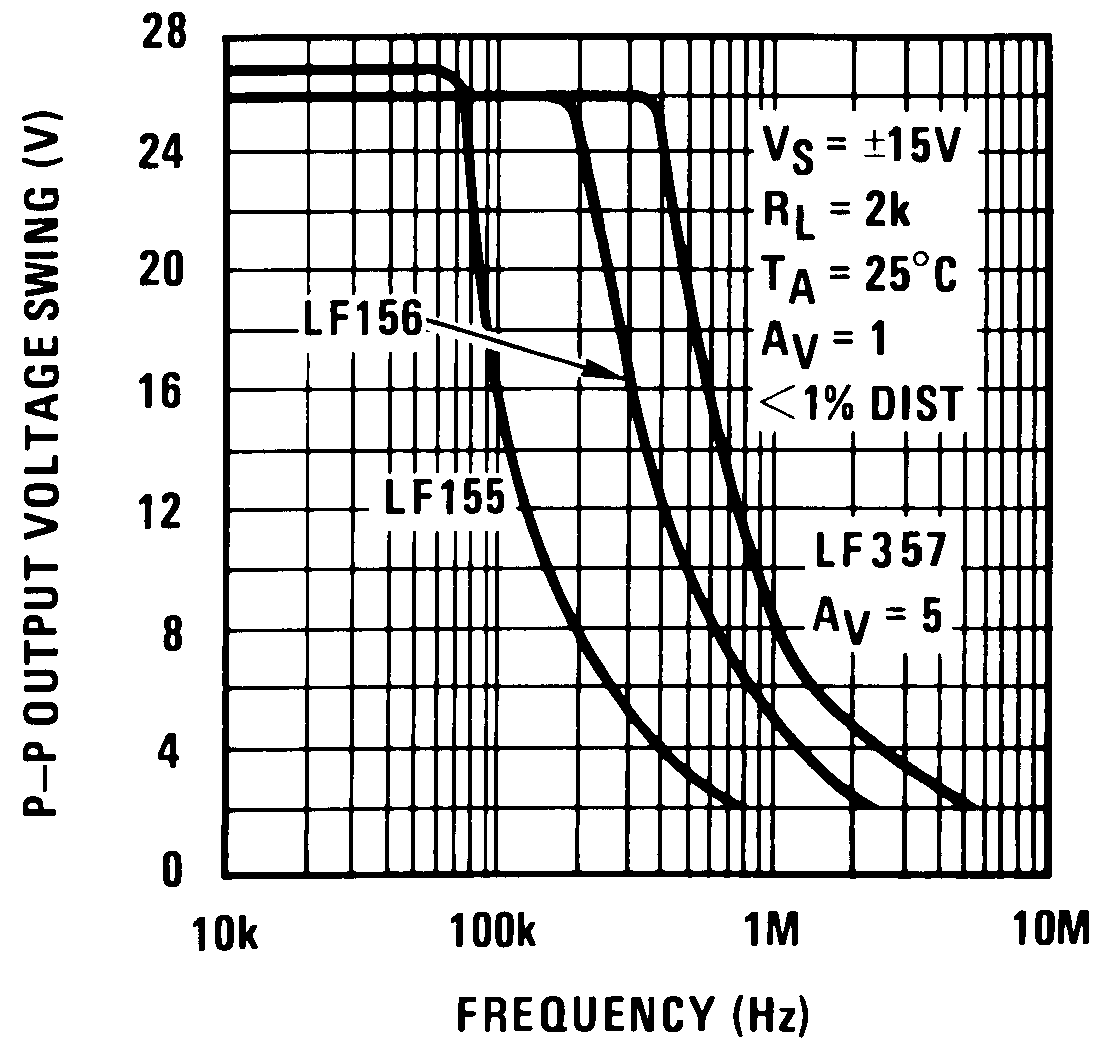

Figure 19. Undistorted Output Voltage Swing

Figure 19. Undistorted Output Voltage Swing

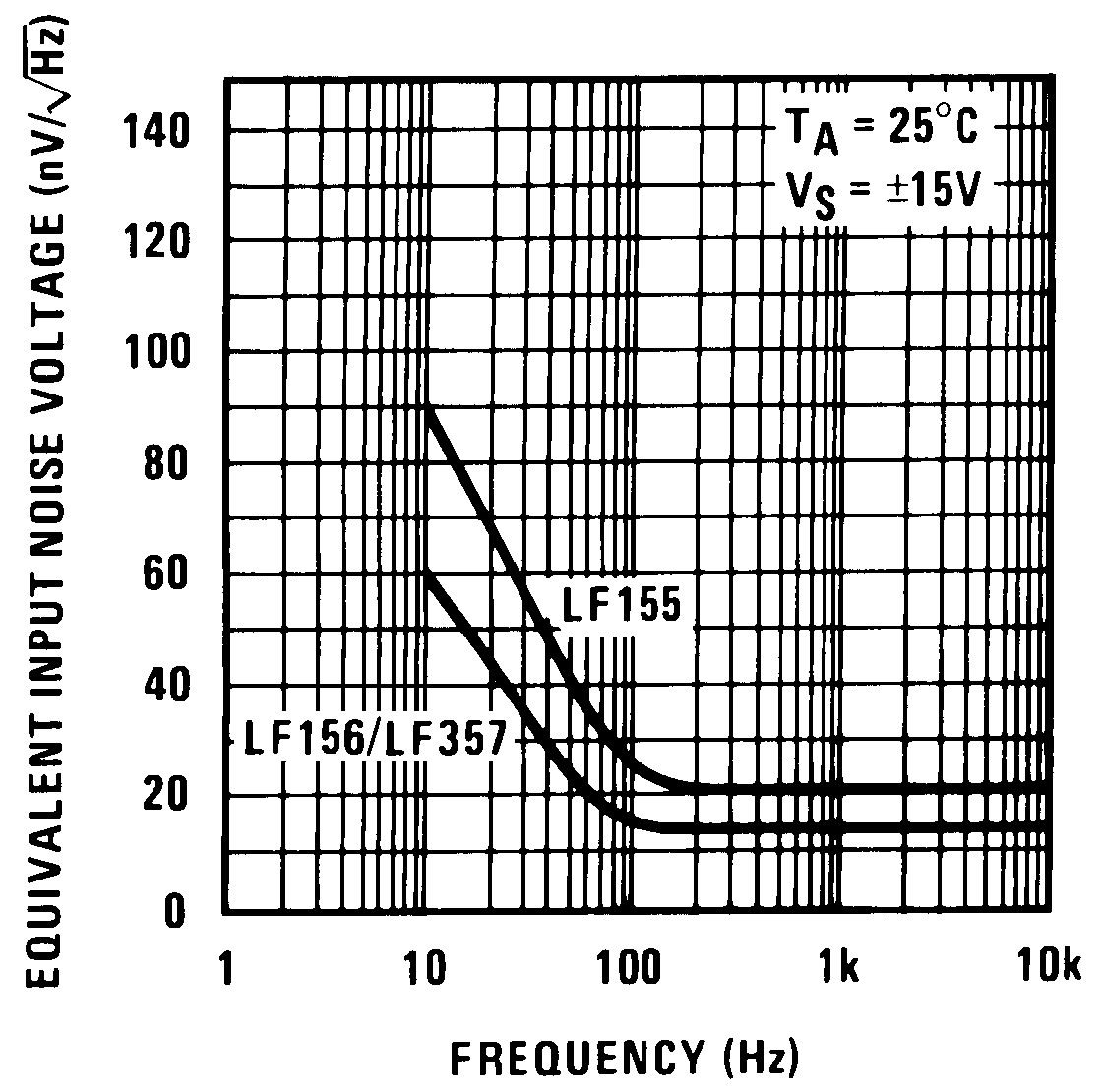

Figure 21. Equivalent Input Noise Voltage (Expanded Scale)

Figure 21. Equivalent Input Noise Voltage (Expanded Scale)

Figure 2. Gain Bandwidth

Figure 2. Gain Bandwidth

Figure 4. Output Impedance

Figure 4. Output Impedance

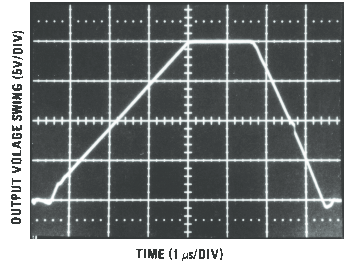

Figure 8. LF155 Large Signal Pulse Response, AV = +1

Figure 8. LF155 Large Signal Pulse Response, AV = +1

Figure 10. Inverter Settling Time

Figure 10. Inverter Settling Time

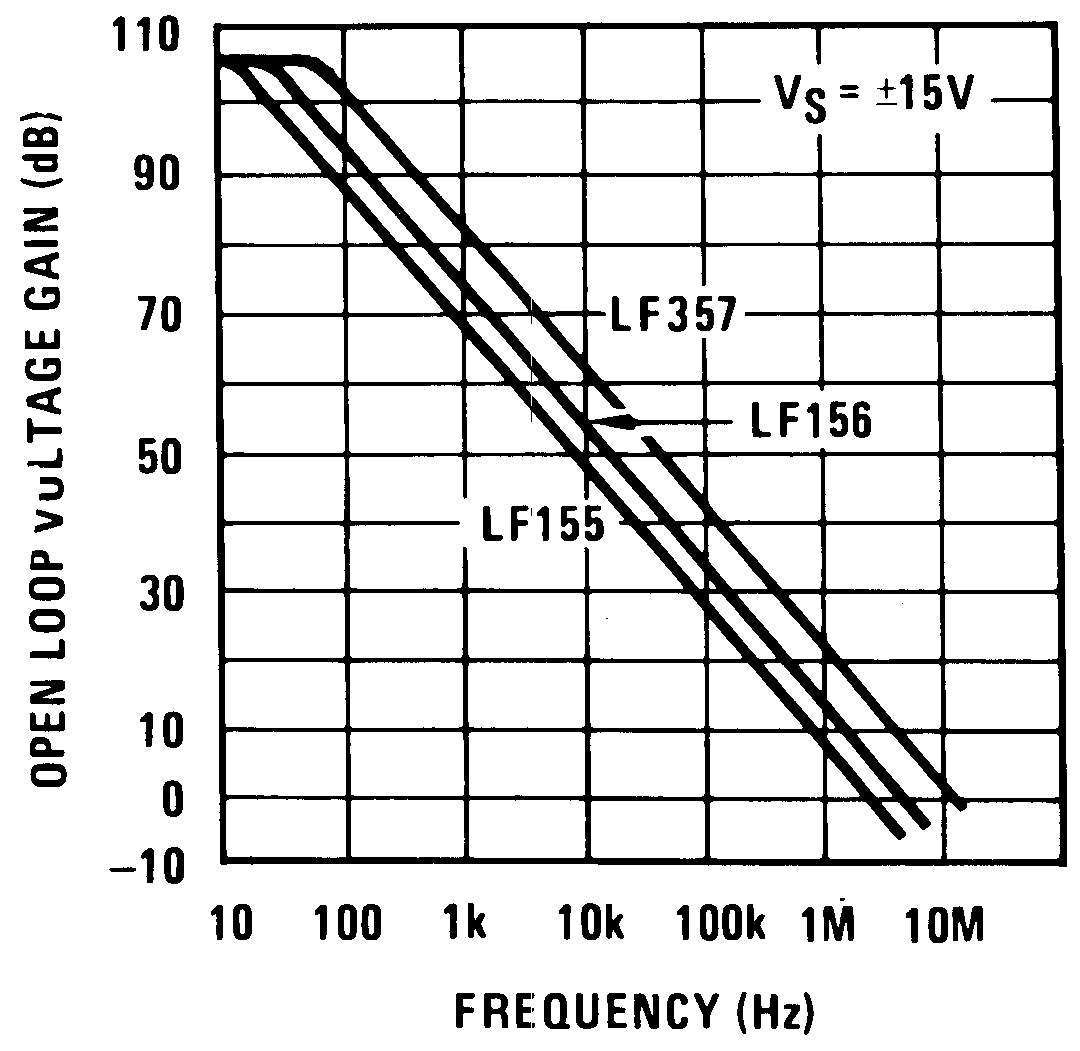

Figure 12. Open-Loop Frequency Response

Figure 12. Open-Loop Frequency Response

Figure 14. Bode Plot

Figure 14. Bode Plot

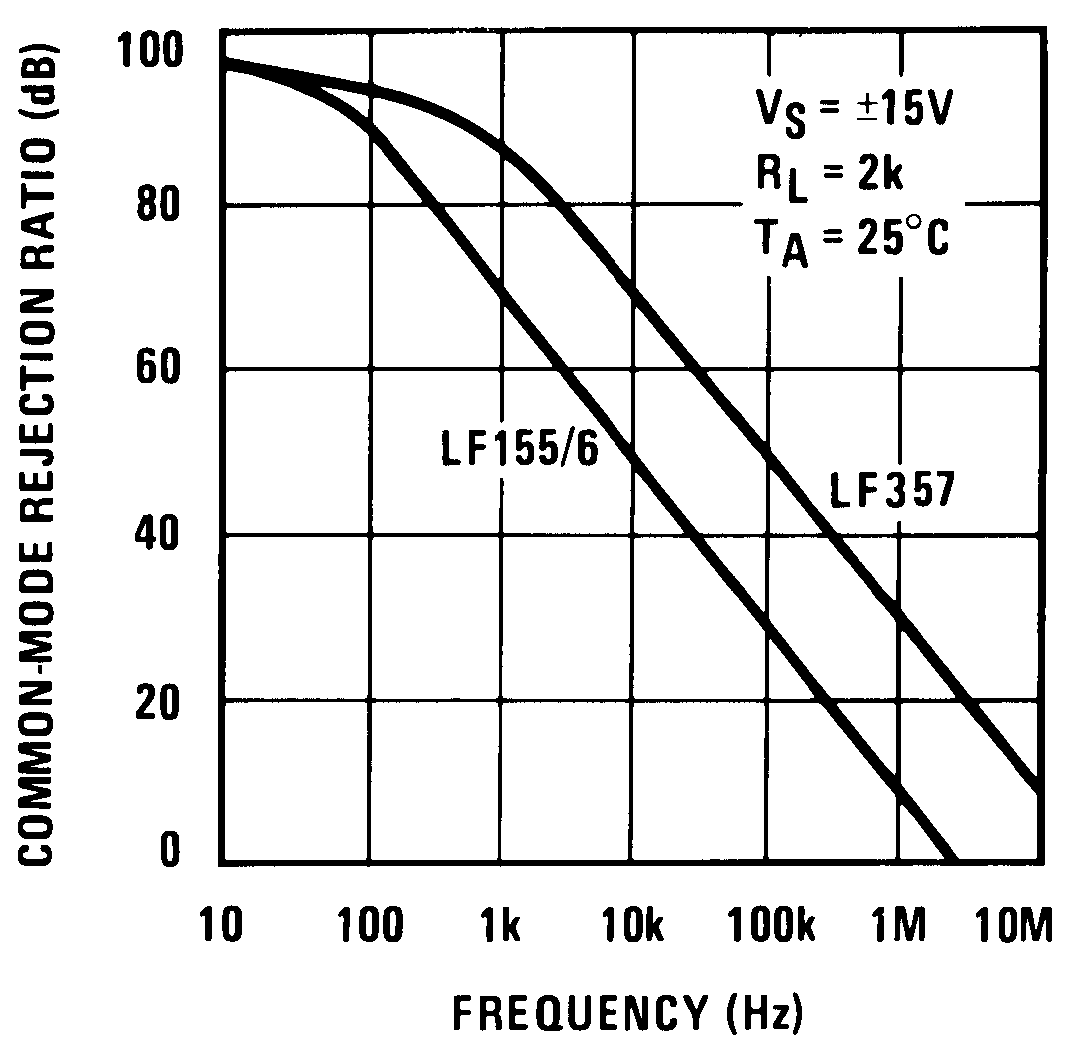

Figure 16. Common-Mode Rejection Ratio

Figure 16. Common-Mode Rejection Ratio

Figure 18. Power Supply Rejection Ratio

Figure 18. Power Supply Rejection Ratio

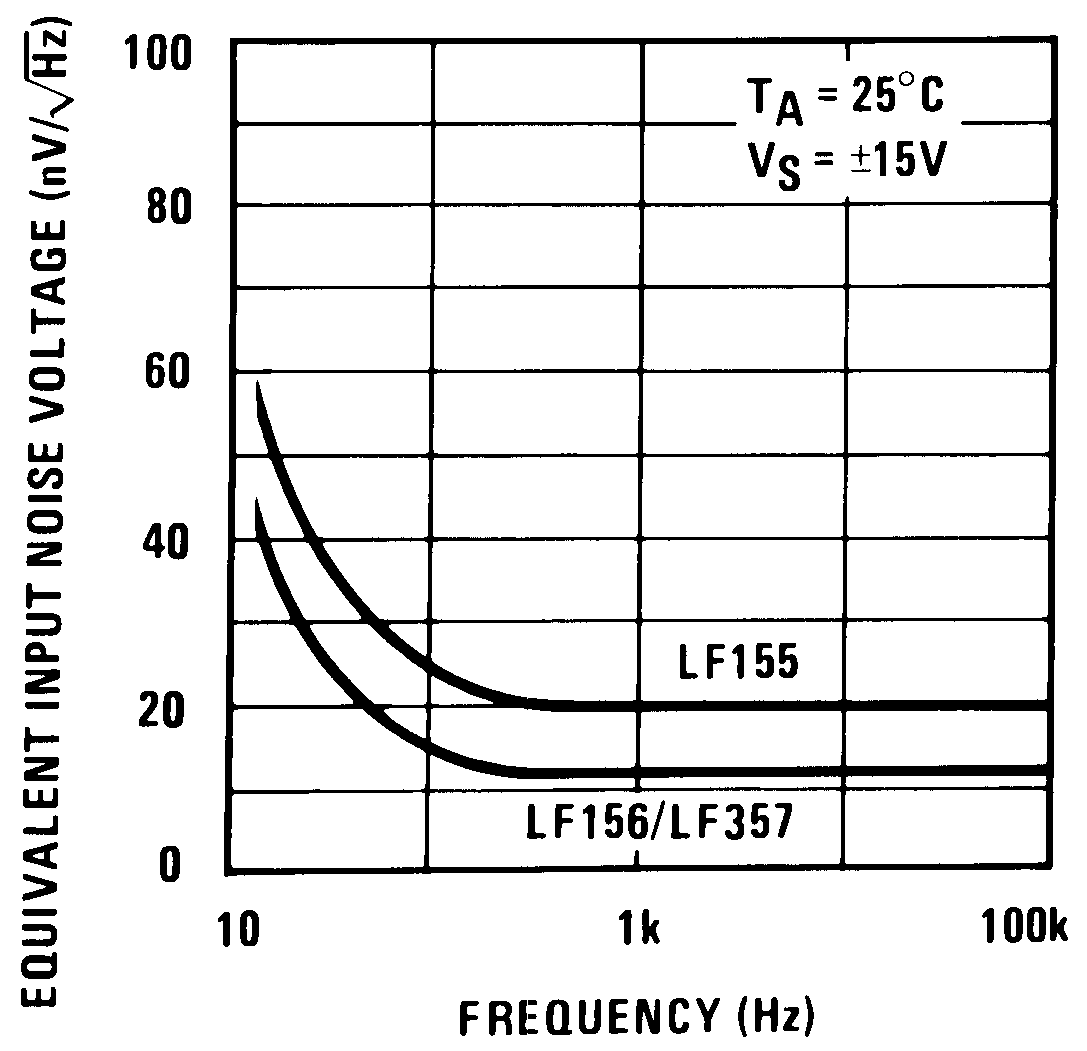

Figure 20. Equivalent Input Noise Voltage

Figure 20. Equivalent Input Noise Voltage