SNOSC51D March 1998 – February 2024 LMC660 , LMC662

PRODUCTION DATA

- 1

- 1Features

- 2Applications

- 3Description

- 4Pin Configuration and Functions

- 5Specifications

- 6Application and Implementation

- 7Device and Documentation Support

- 8Revision History

- 9Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|8

- P|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

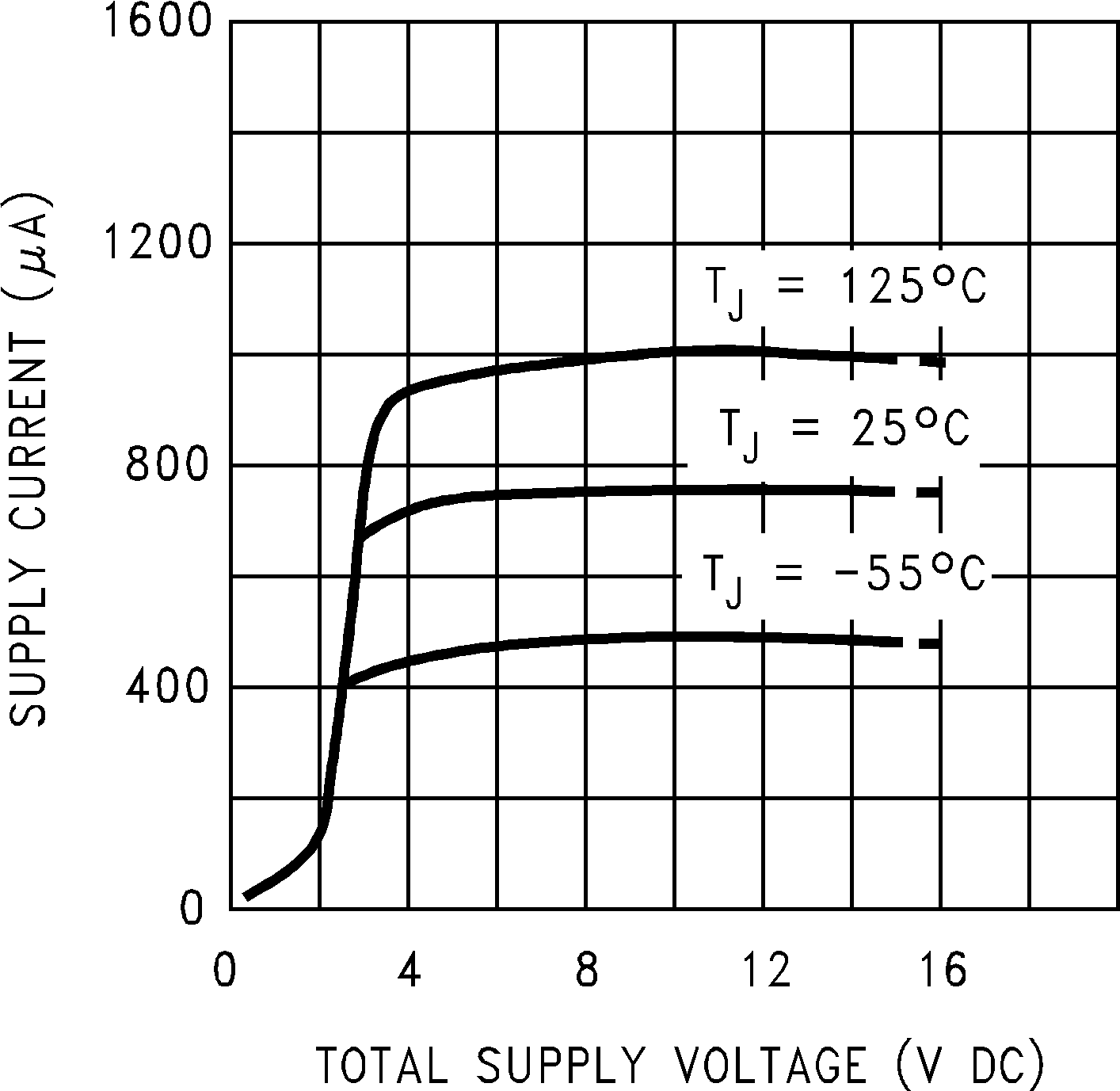

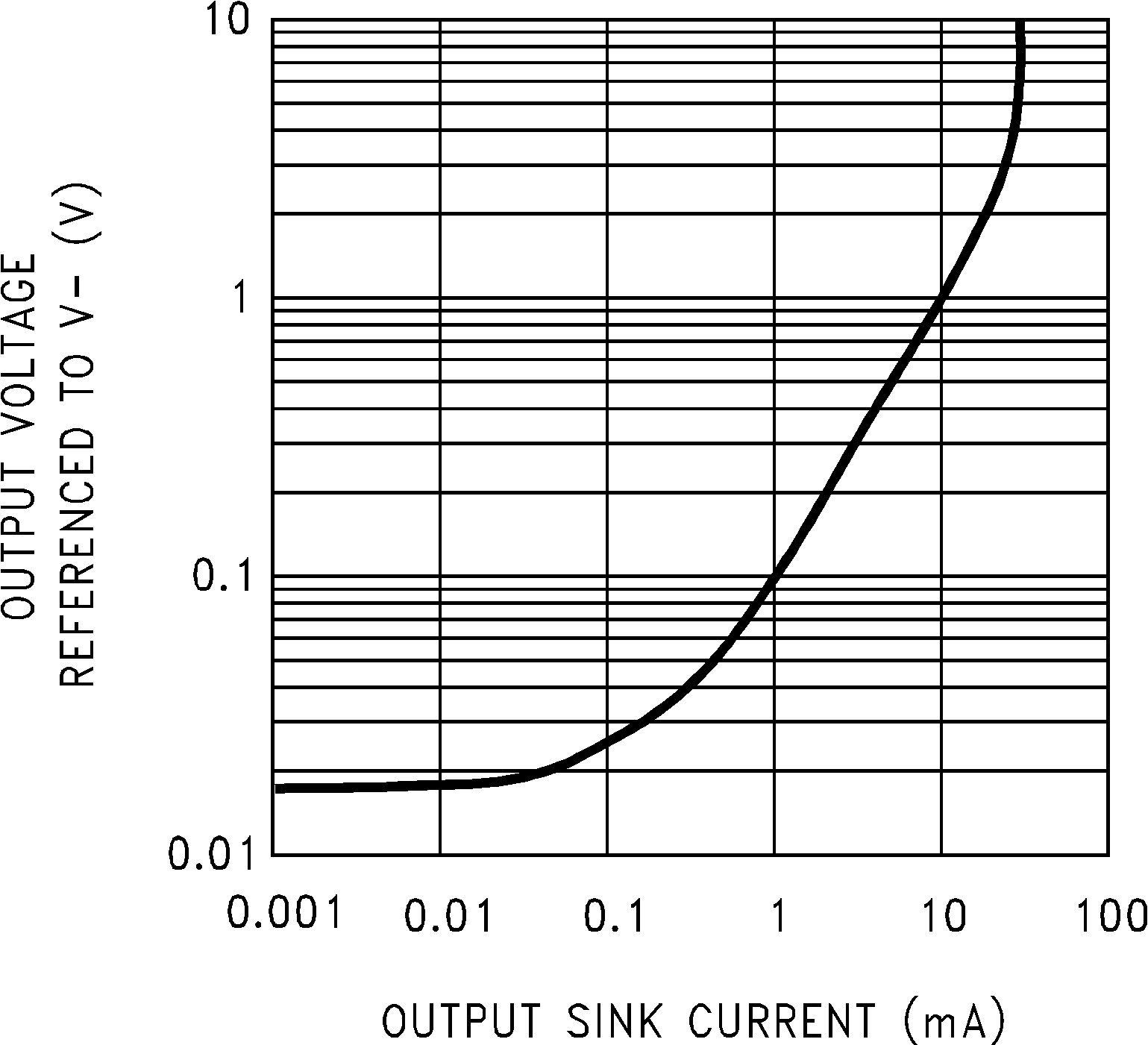

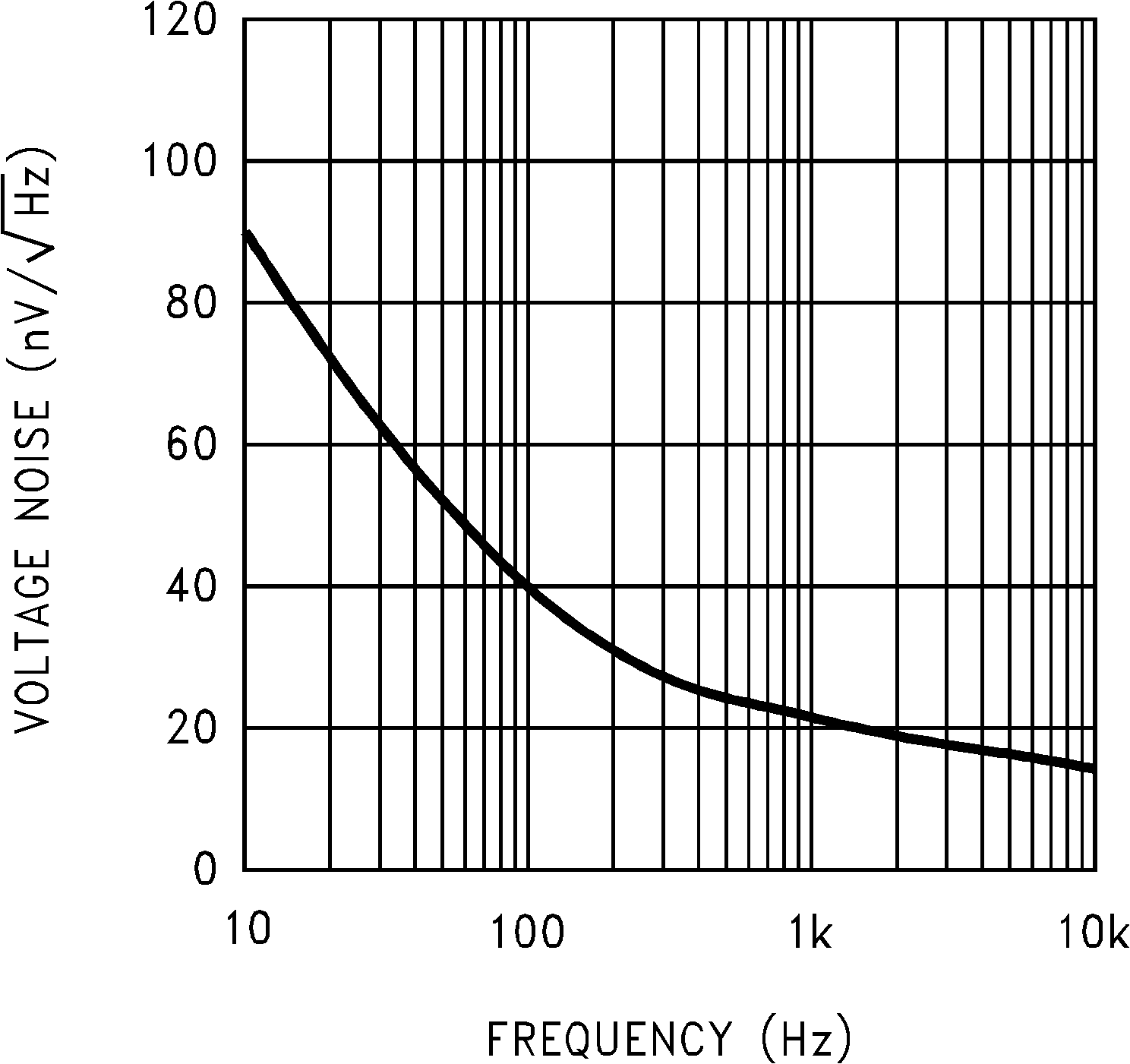

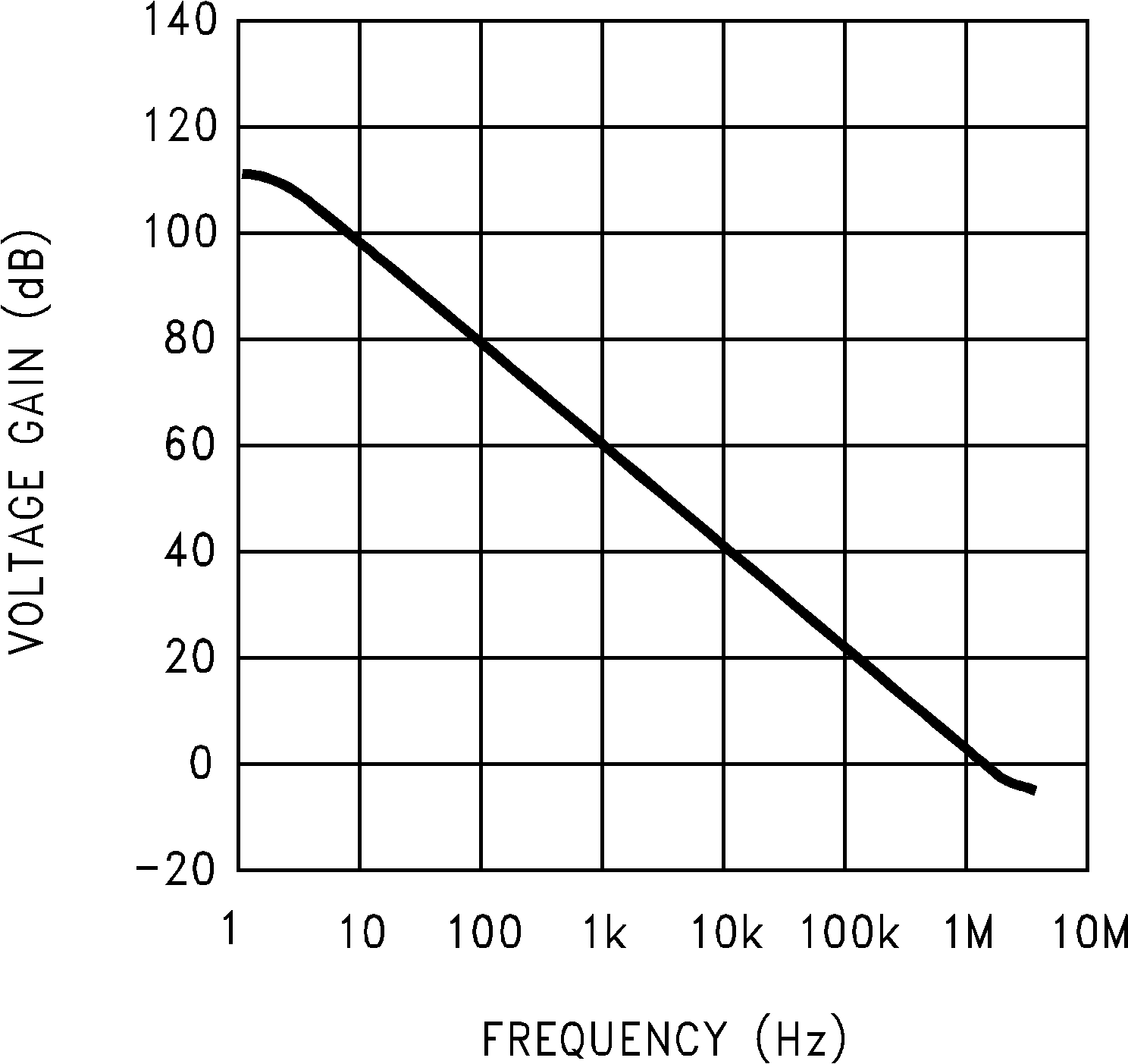

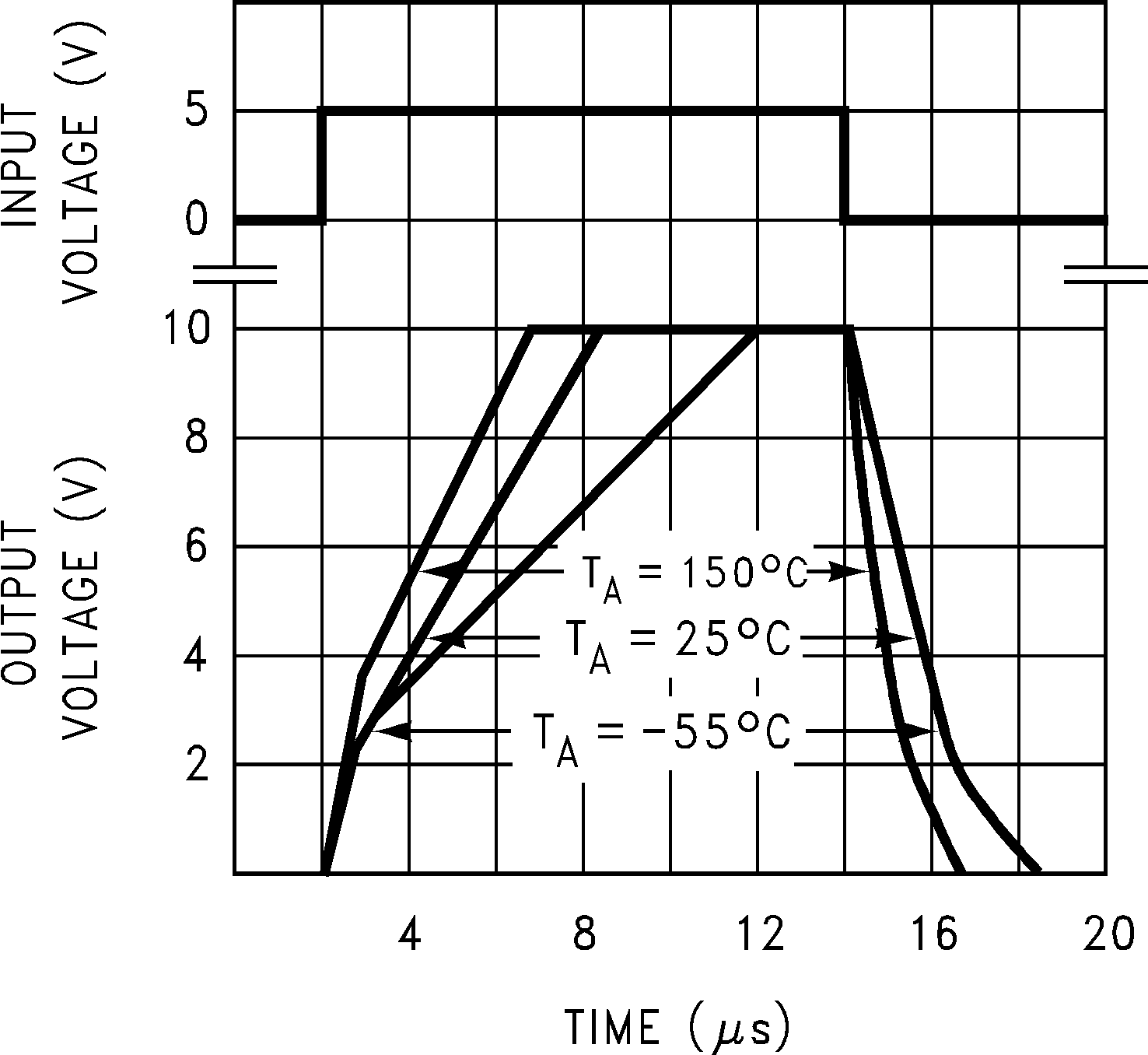

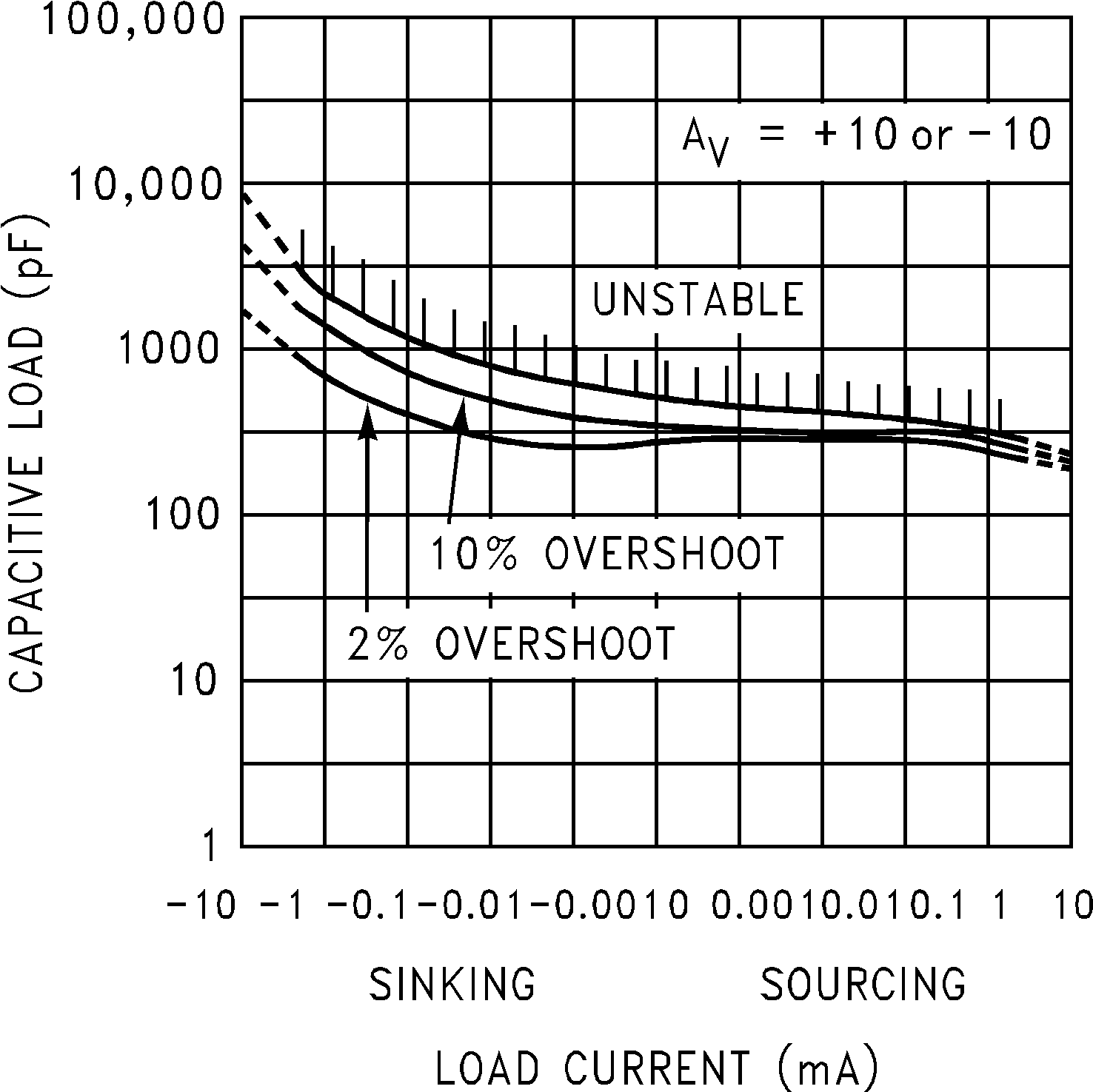

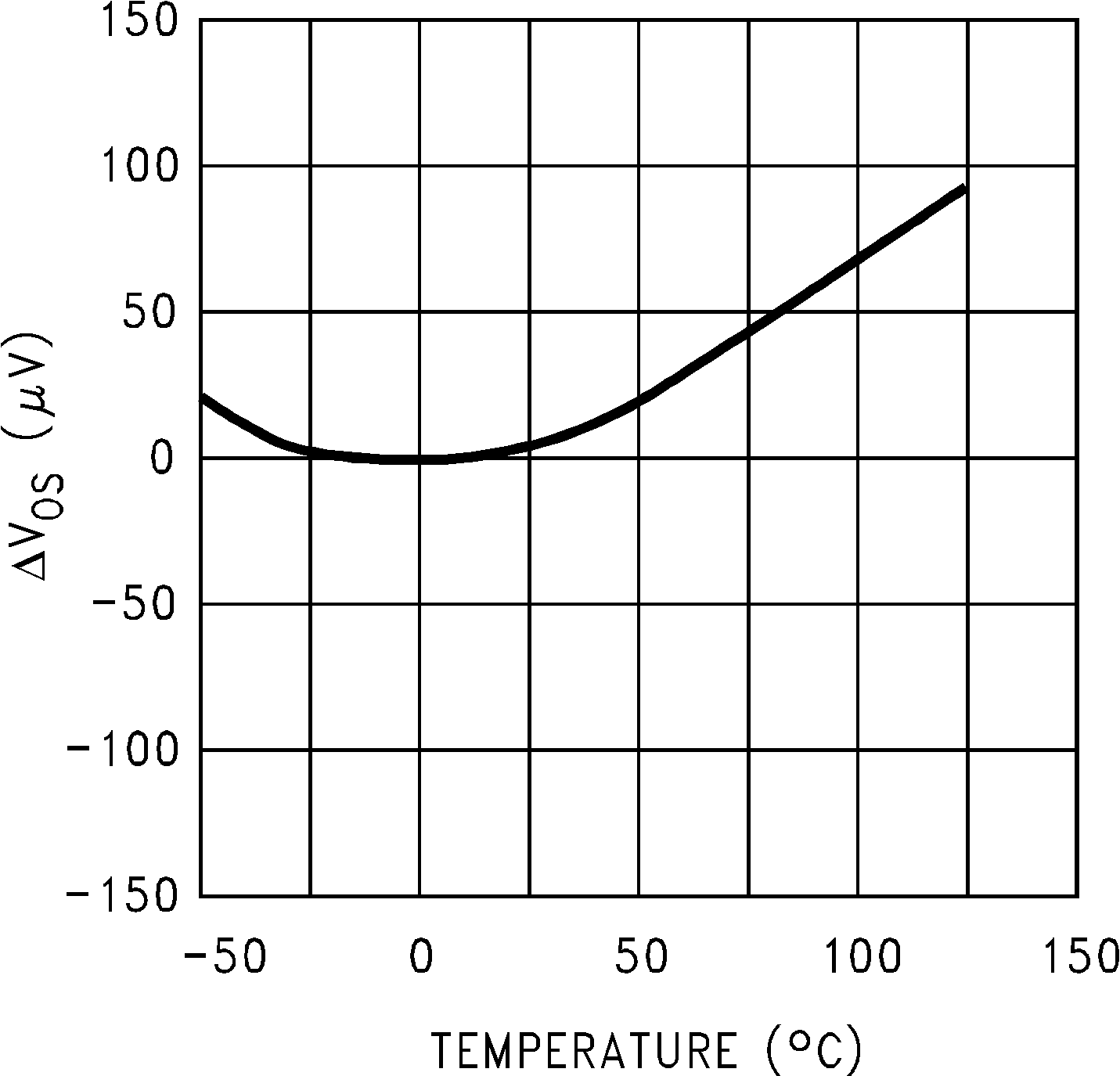

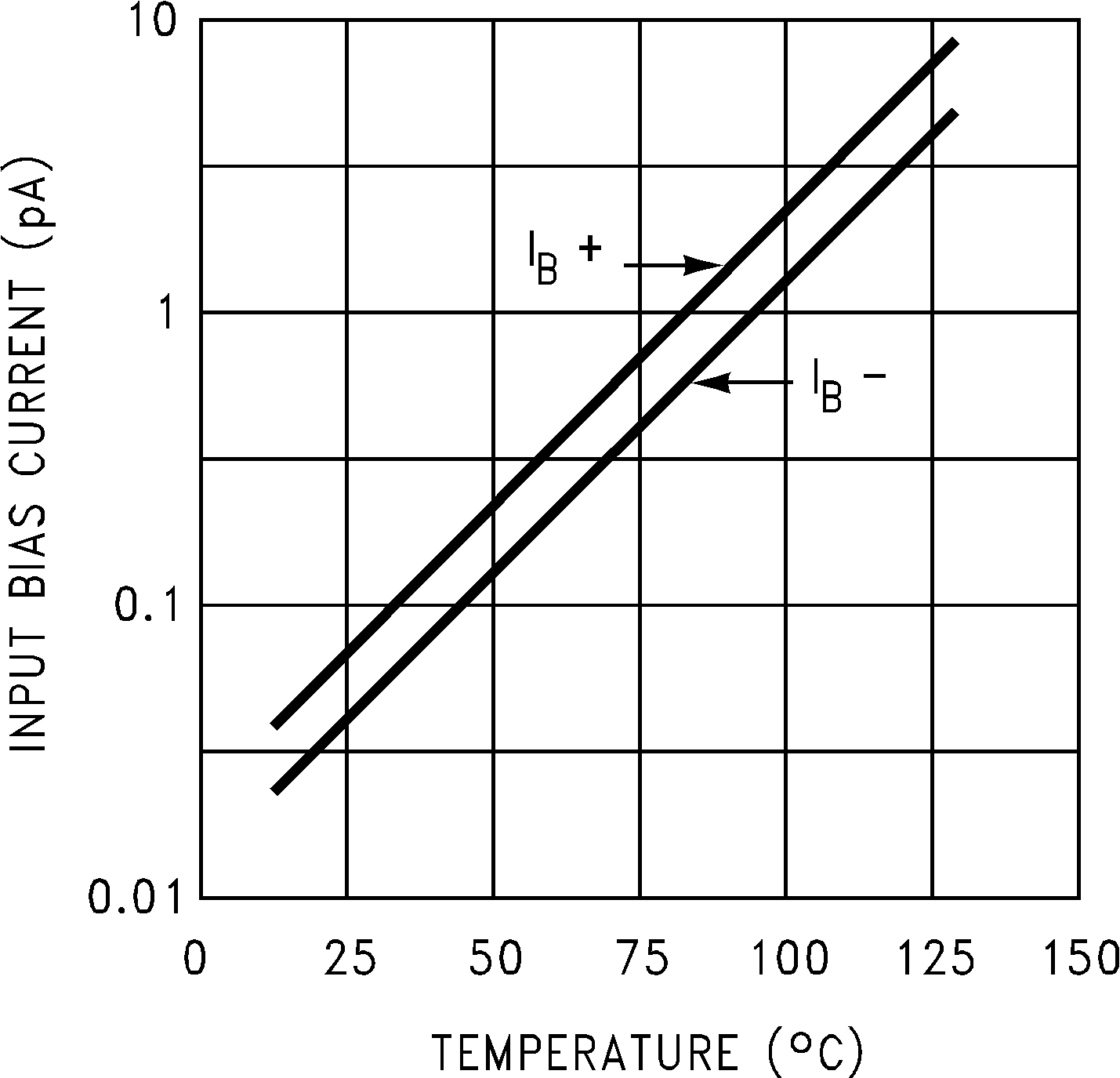

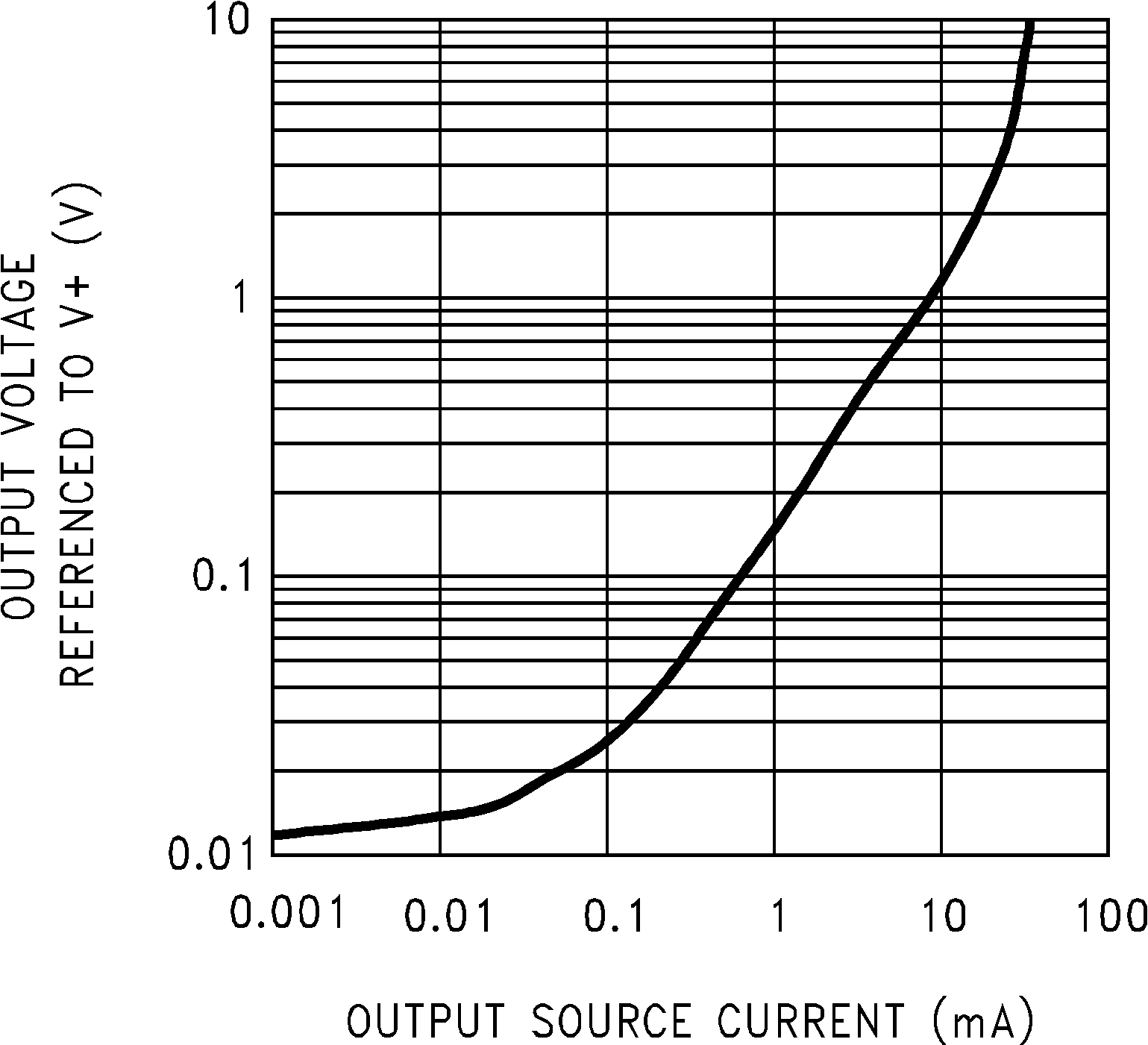

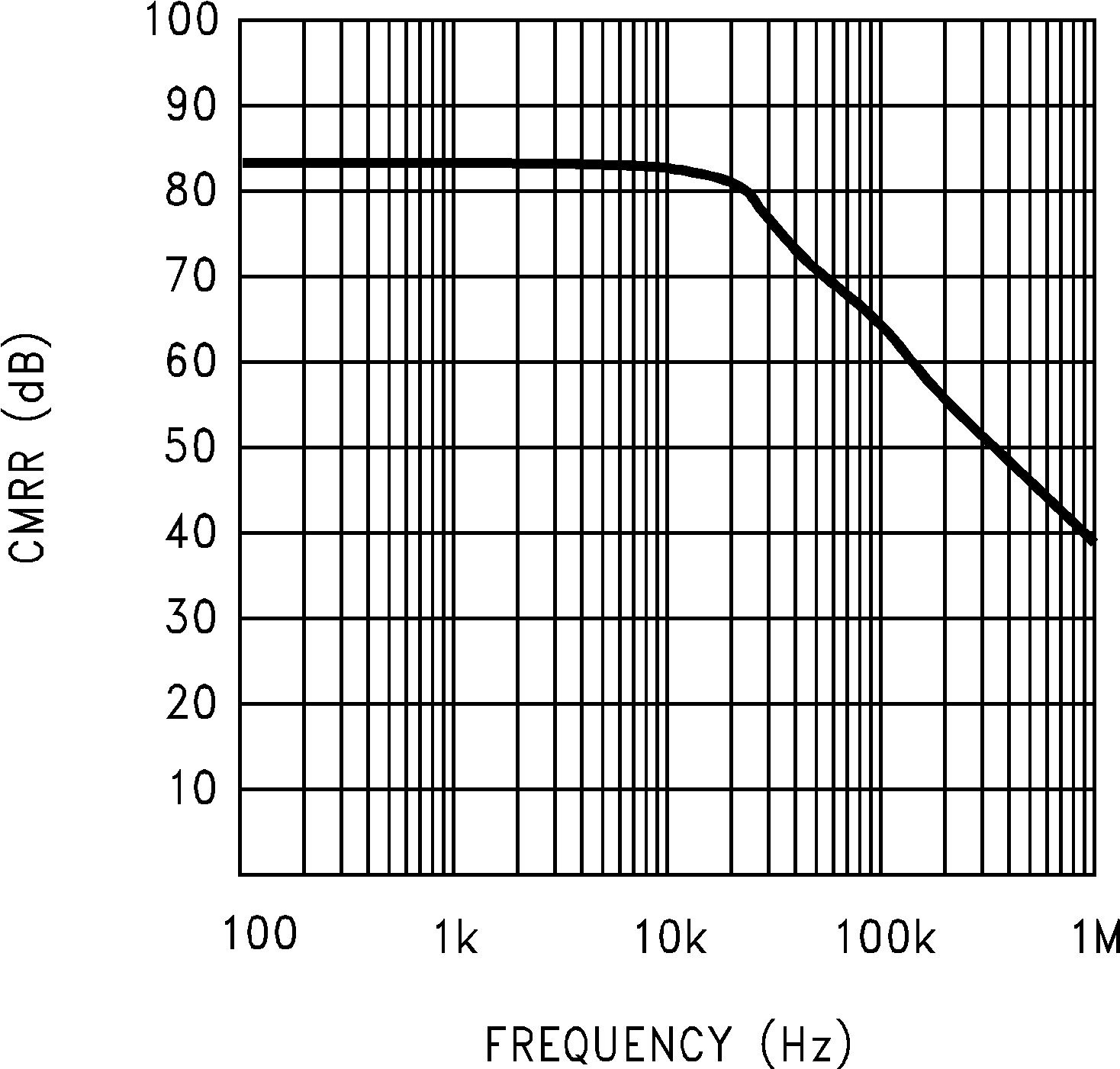

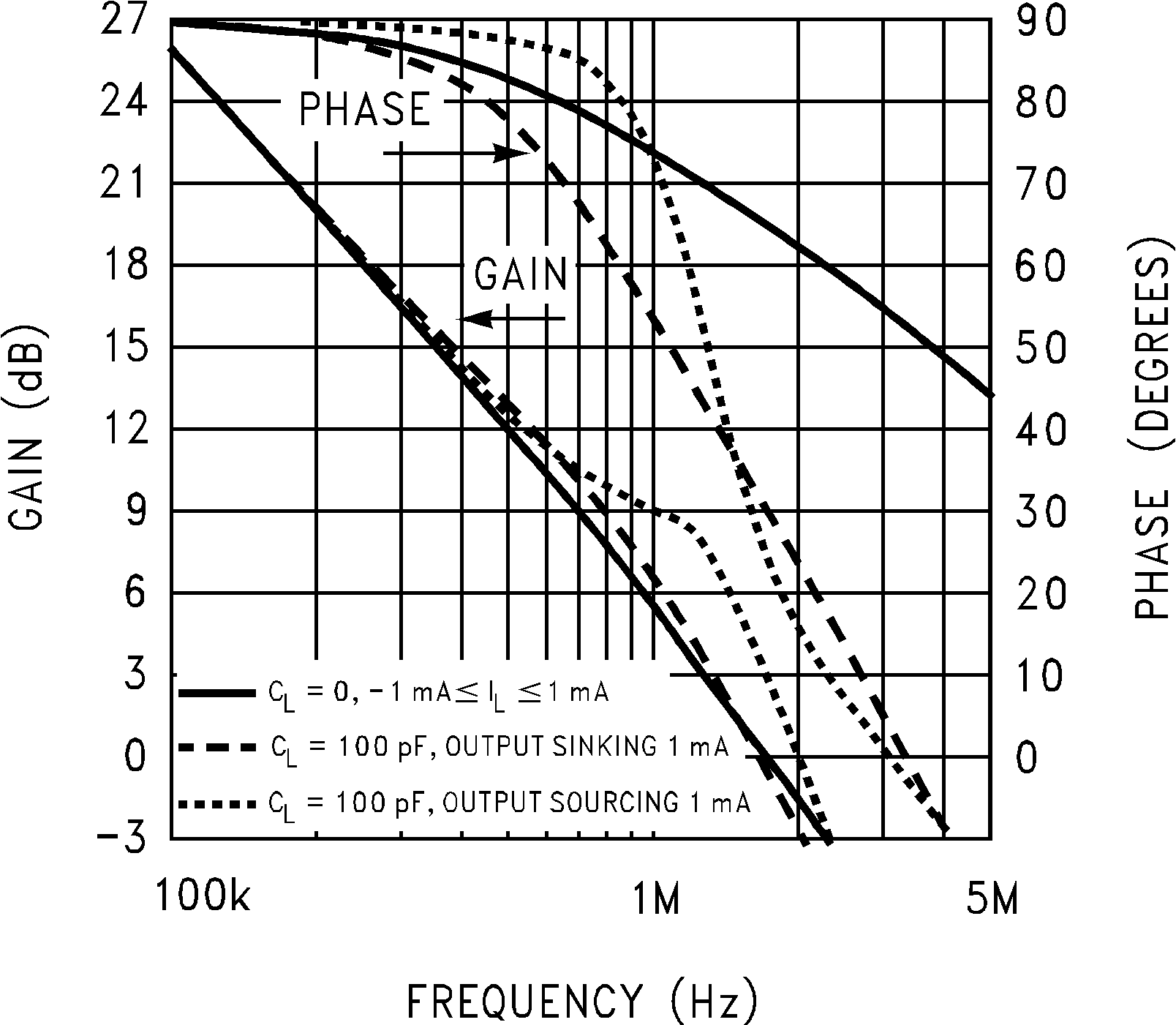

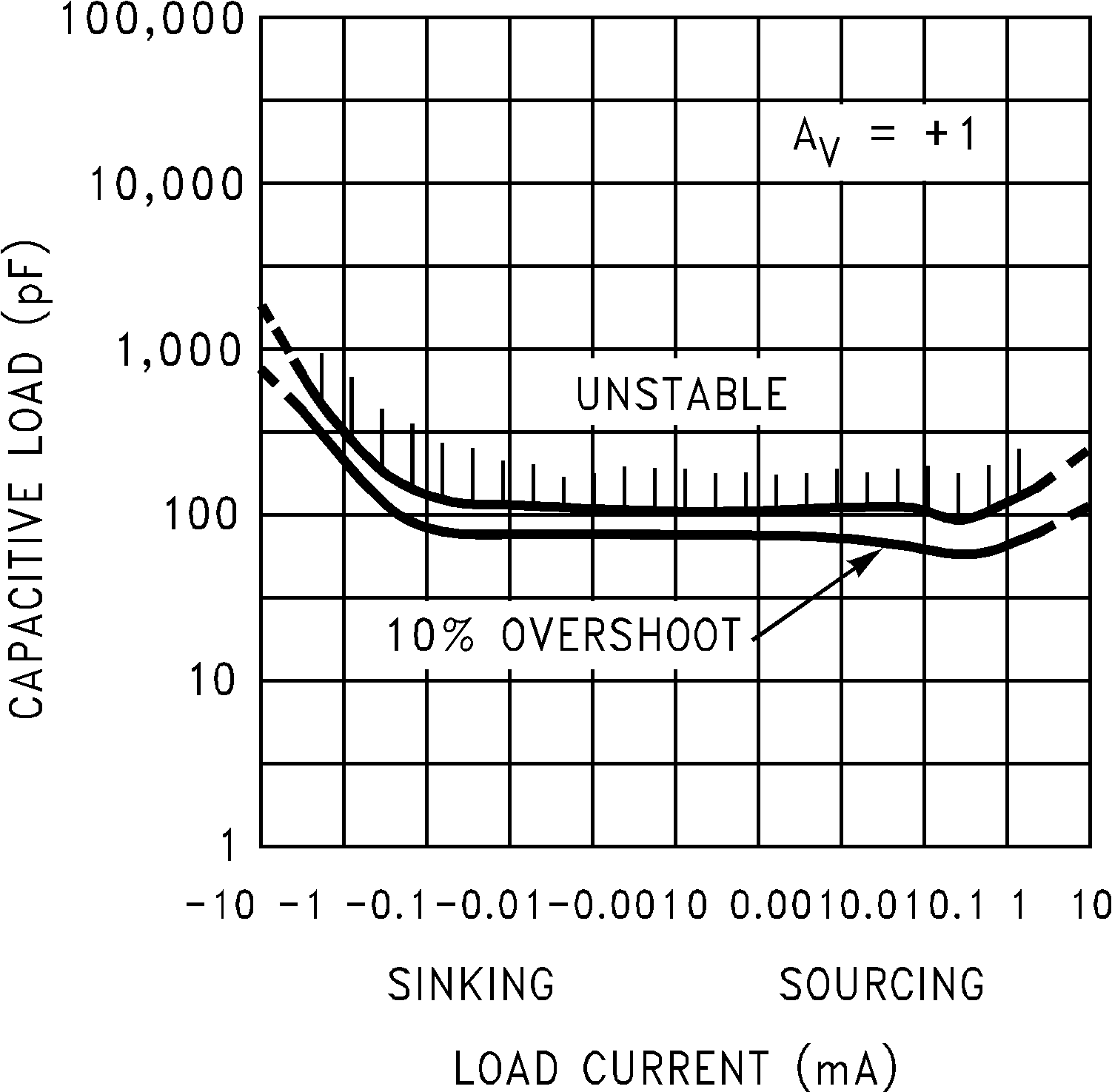

5.7 Typical Characteristics

at TA = 25°C, VS = ±7.5V, VOUT = mid-supply, RL≥ 1MΩ (unless otherwise specified)

| Avoid resistive loads < 500Ω because of possible instability | ||

| VS = ±2.5V | ||

| Avoid resistive loads < 500Ω because of possible instability | ||