SNVS056J May 2000 – June 2015 LP3961 , LP3964

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configurations and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 External Capacitors

- 8.2.2.2 Selecting a Capacitor

- 8.2.2.3 Capacitor Characteristics

- 8.2.2.4 RFI and EMI Susceptibility

- 8.2.2.5 Output Adjustment

- 8.2.2.6 Turnon Characteristics for Output Voltages Programmed to 2.0 V or Below

- 8.2.2.7 Output Noise

- 8.2.2.8 Shutdown Operation

- 8.2.2.9 Maximum Output Current Capability

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- KTT|5

Orderable Information

6 Specifications

6.1 Absolute Maximum Ratings(1)(2)

| MIN | MAX | UNIT | |

|---|---|---|---|

| Power dissipation(3) | Internally Limited | ||

| Input Supply Voltage (Survival) | −0.3 | 7.5 | V |

| Shutdown Input Voltage (Survival) | −0.3 | VIN + 0.3 | V |

| Output Voltage (Survival)(4), (5) | −0.3 | 7.5 | V |

| IOUT (Survival) | Short-Circuit Protected | ||

| Maximum Voltage for ERROR pin | VIN + 0.3 | V | |

| Maximum Voltage for SENSE pin | VOUT + 0.3 | V | |

| Storage temperature, Tstg | –65 | 150 | °C |

(1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but does not ensure specific performance limits. For ensured specifications and test conditions, see Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

(2) If Military- or Aerospace-specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(3) The maximum allowable power dissipation is a function of the maximum junction temperature, TJ(MAX), the junction-to-ambient thermal resistance, RθJA, and the ambient temperature, TA. The maximum allowable power dissipation at any ambient temperature is calculated using: P(MAX) = (TJ(MAX) – TA) / RθJA.

(4) If used in a dual-supply system where the regulator load is returned to a negative supply, the LP396X output must be diode-clamped to ground.

(5) The output PMOS structure contains a diode between the IN and OUT pins. This diode is normally reverse biased. This diode will get forward biased if the voltage at the OUT pin is forced to be higher than the voltage at the IN pin. This diode can typically withstand 200 mA of DC current and 1 A of peak current.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process..

6.3 Recommended Operating Conditions

| MIN | MAX | UNIT | |

|---|---|---|---|

| Input supply voltage (operating)(1) | 2.5 | 7 | V |

| Shutdown input voltage (operating) | −0.3 | VIN + 0.3 | V |

| Maximum operating current (DC) | 0.8 | A | |

| Operating junction temperature | −40 | 125 | °C |

(1) The minimum operating value for VIN is equal to either [VOUT(NOM) + VDROPOUT] or 2.5 V, whichever is greater.

6.4 Thermal Information

| THERMAL METRIC(1) | LP3961, LP3964 | LP3964 | UNIT | ||

|---|---|---|---|---|---|

| NDC | KTT | NDH | |||

| 5 PINS | |||||

| RθJA | Junction-to-ambient thermal resistance | 65.2 | 40.3 | 32.1 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 47.2 | 43.4 | 43.8 | |

| RθJB | Junction-to-board thermal resistance | 9.9 | 23.1 | 18.7 | |

| ψJT | Junction-to-top characterization parameter | 3.4 | 11.5 | 8.8 | |

| ψJB | Junction-to-board characterization parameter | 9.7 | 22.1 | 18.0 | |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | 1.0 | 1.3 | |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

6.5 Electrical Characteristics

Unless otherwise specified: TJ = 25°C, VIN = VO(NOM) + 1 V, IL = 10 mA, COUT = 33 µF, VSD = VIN – 0.3 V.| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | |

|---|---|---|---|---|---|---|

| VO | Output voltage tolerance(3) | 10 mA ≤ IL ≤ 800 mA, VOUT + 1 ≤ VIN ≤ 7 V |

–1.5% | 0% | 1.5% | |

| 10 mA ≤ IL ≤ 800 mA, VOUT + 1 ≤ VIN ≤ 7 V, –40°C ≤ TJ ≤ 125°C |

–3% | 3% | ||||

| VADJ | Adjust pin voltage (ADJ version) | 10 mA ≤ IL ≤ 800 mA, VOUT + 1.5 V ≤ VIN ≤ 7 V |

1.198 | 1.216 | 1.234 | V |

| 10 mA ≤ IL ≤ 800 mA, VOUT + 1.5 V ≤ VIN ≤ 7 V, –40°C ≤ TJ ≤ 125°C |

1.180 | 1.253 | ||||

| ΔVOL | Output voltage line regulation(3) | VOUT + 1 V < VIN < 7 V | 0.02% | |||

| VOUT + 1 V < VIN < 7 V, –40°C ≤ TJ ≤ 125°C |

0.06% | |||||

| ΔVO / ΔIOUT | Output voltage load regulation(3) | 10 mA < IL < 800 mA | 0.02% | |||

| 10 mA < IL < 800 mA, –40°C ≤ TJ ≤ 125°C |

0.08% | |||||

| VIN – VOUT | Dropout voltage(4) | IL = 80 mA | 24 | 30 | mV | |

| IL = 80 mA, –40°C ≤ TJ ≤ 125°C | 35 | |||||

| IL = 800 mA | 240 | 300 | ||||

| IL = 800 mA, –40°C ≤ TJ ≤ 125°C | 350 | |||||

| IGND | Ground pin current in normal operation mode | IL = 80 mA | 3 | 9 | mA | |

| IL = 80 mA, –40°C ≤ TJ ≤ 125°C | 10 | |||||

| IL = 800 mA | 4 | 14 | ||||

| IL = 800 mA, –40°C ≤ TJ ≤ 125°C | 15 | |||||

| IGND | Ground pin current in shutdown mode(5) | VSD ≤ 0.2 V | 15 | 25 | µA | |

| VSD ≤ 0.2 V, –40°C ≤ TJ ≤ 125°C | 75 | |||||

| IO(PK) | Peak output current | See(6) | 1.2 | 1.5 | A | |

| See(6), –40°C ≤ TJ ≤ 125°C | 1.1 | |||||

| SHORT-CIRCUIT PROTECTION | ||||||

| ISC | Short-circuit current | 2.8 | A | |||

| OVERTEMPERATURE PROTECTION | ||||||

| Tsh(t) | Shutdown threshold | 165 | °C | |||

| Tsh(h) | Thermal shutdown hysteresis | 10 | °C | |||

| SHUTDOWN INPUT | ||||||

| VSDT | Shutdown threshold | Output = High | VIN | V | ||

| Output = High, –40°C ≤ TJ ≤ 125°C | VIN – 0.3 | |||||

| Output = Low | 0 | |||||

| Output = Low, –40°C ≤ TJ ≤ 125°C | 0.2 | |||||

| TdOFF | Turnoff delay | IL = 800 mA | 20 | µs | ||

| TdON | Turnon delay | IL = 800 mA | 25 | µs | ||

| ISD | SD input current | VSD = VIN | 1 | nA | ||

| ERROR FLAG COMPARATOR | ||||||

| VT | Threshold | See(7) | 10% | |||

| See(7), –40°C ≤ TJ ≤ 125°C | 5% | 16% | ||||

| VTH | Threshold hysteresis | See(7) | 5% | |||

| See(7), –40°C ≤ TJ ≤ 125°C | 2% | 8% | ||||

| VEF(Sat) | ERROR flag saturation | Isink = 100 µA | 0.02 | V | ||

| Isink = 100 µA | 0.1 | |||||

| Td | Flag reset delay | 1 | µs | |||

| Ilk | ERROR flag pin leakage current | 1 | nA | |||

| Imax | ERROR flag pin sink current | VERROR = 0.5 V (overtemperature) | 1 | mA | ||

| AC PARAMETERS | ||||||

| PSRR | Ripple rejection | VIN = VOUT + 1.5 V, COUT = 100 µF, VOUT = 3.3 V |

60 | dB | ||

| VIN = VOUT + 0.3 V, COUT = 100 µF, VOUT = 3.3 V |

40 | |||||

| ρn(l/f) | Output noise density | f = 120 Hz | 0.8 | µV | ||

| en | Output noise voltage (rms) | BW = 10 Hz to 100 kHz | 150 | µVRMS | ||

| BW = 300 Hz to 300 kHz | 100 | |||||

(1) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate TI's Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely parametric norm.

(3) Output voltage line regulation is defined as the change in output voltage from the nominal value due to change in the input line voltage. Output voltage load regulation is defined as the change in output voltage from the nominal value due to change in load current. The line and load regulation specification contains only the typical number. However, the limits for line and load regulation are included in the output voltage tolerance specification.

(4) Dropout voltage is defined as the minimum input-to-output differential voltage at which the output drops 2% below the nominal value. Dropout voltage specification applies only to output voltages of 2.5 V and above. For output voltages below 2.5 V, the drop-out voltage is nothing but the input-to-output differential voltage because the minimum input voltage is 2.5 V.

(5) This specification has been tested for –40°C ≤ TJ ≤ 85°C because the temperature rise of the device is negligible under shutdown conditions.

(6) The maximum allowable power dissipation is a function of the maximum junction temperature, TJ(MAX), the junction-to-ambient thermal resistance, RθJA, and the ambient temperature, TA. The maximum allowable power dissipation at any ambient temperature is calculated using: P(MAX) = (TJ(MAX) – TA) / RθJA.

(7) ERROR flag threshold and hysteresis are specified as percentage of regulated output voltage.

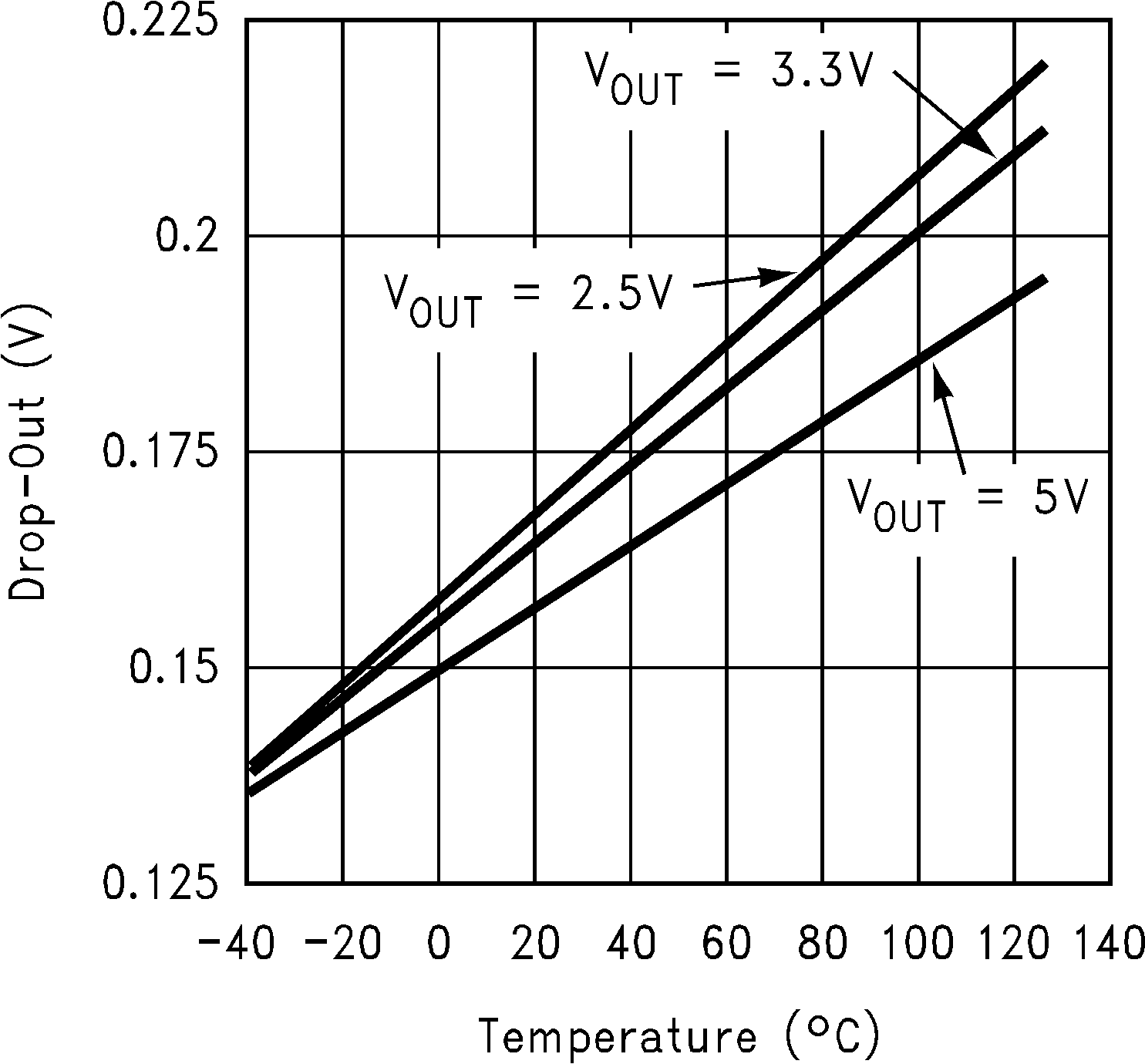

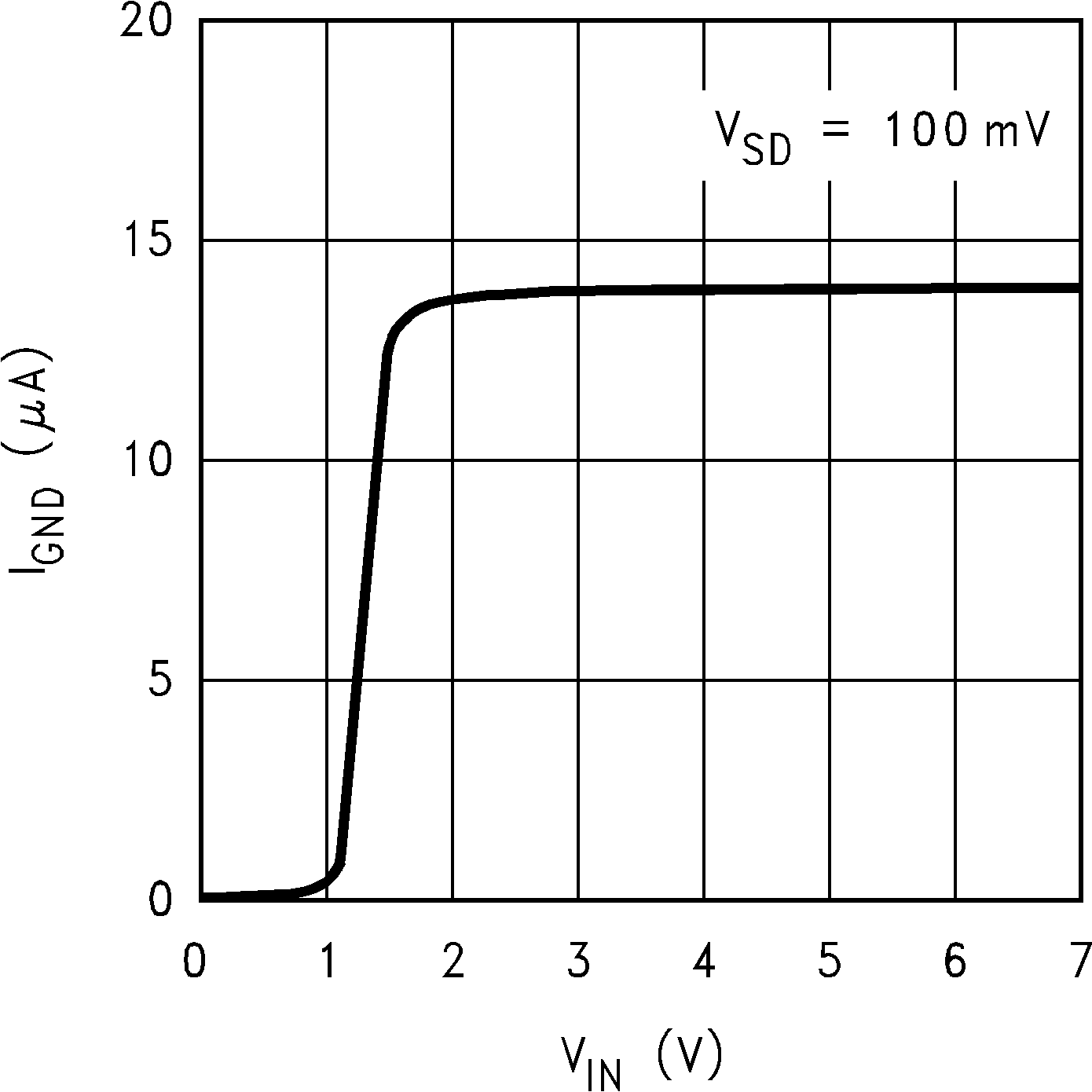

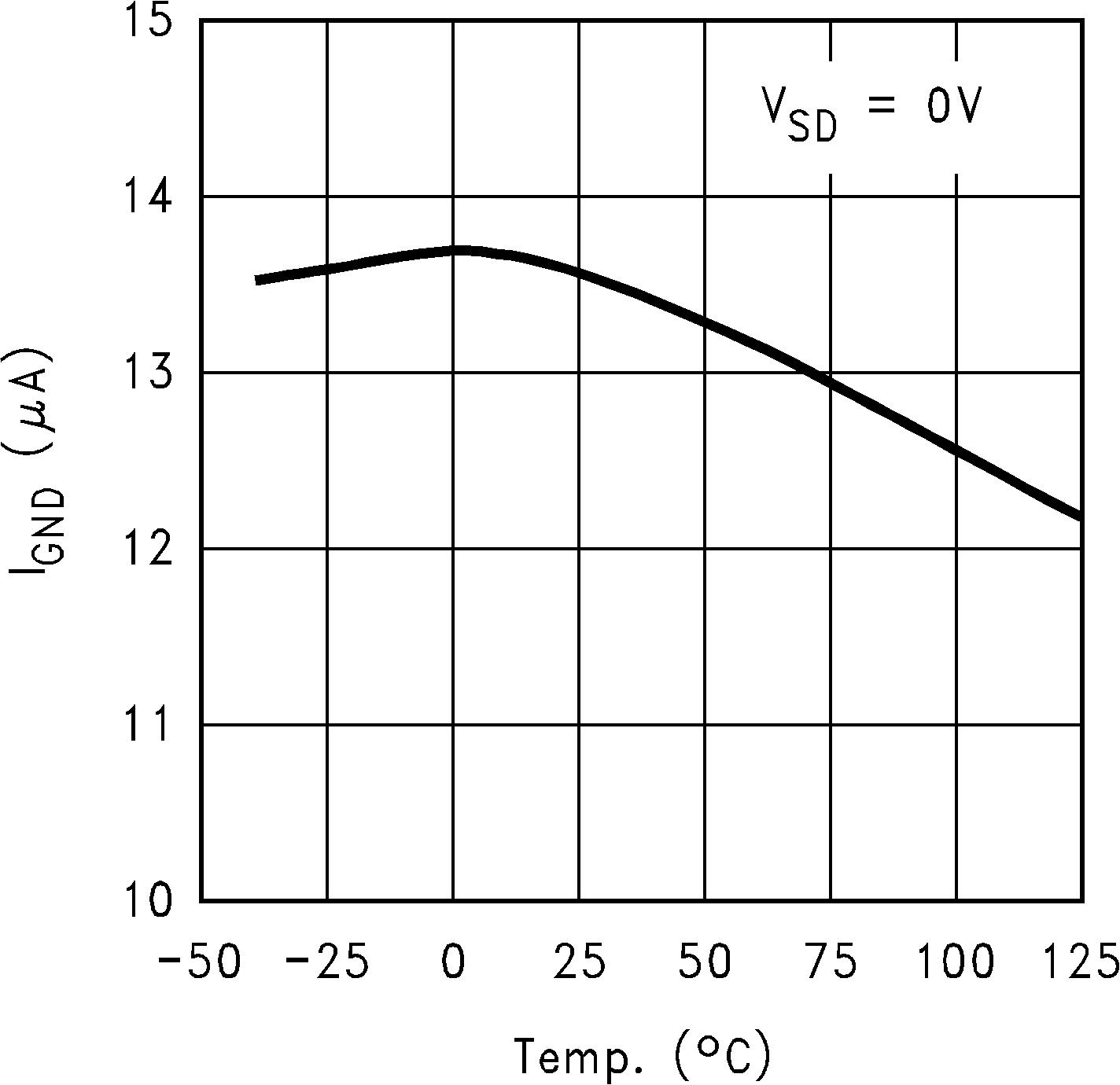

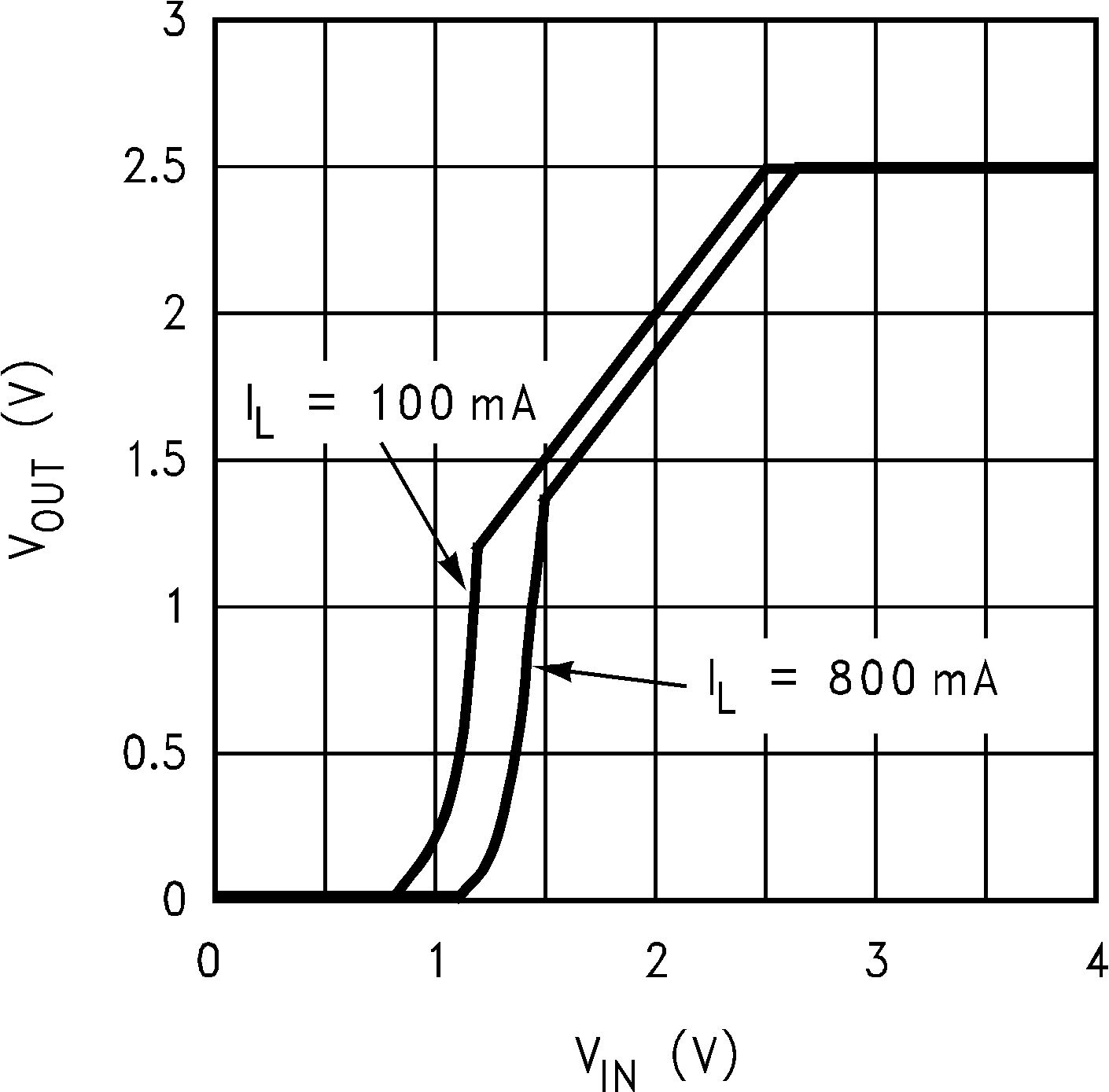

6.6 Typical Characteristics

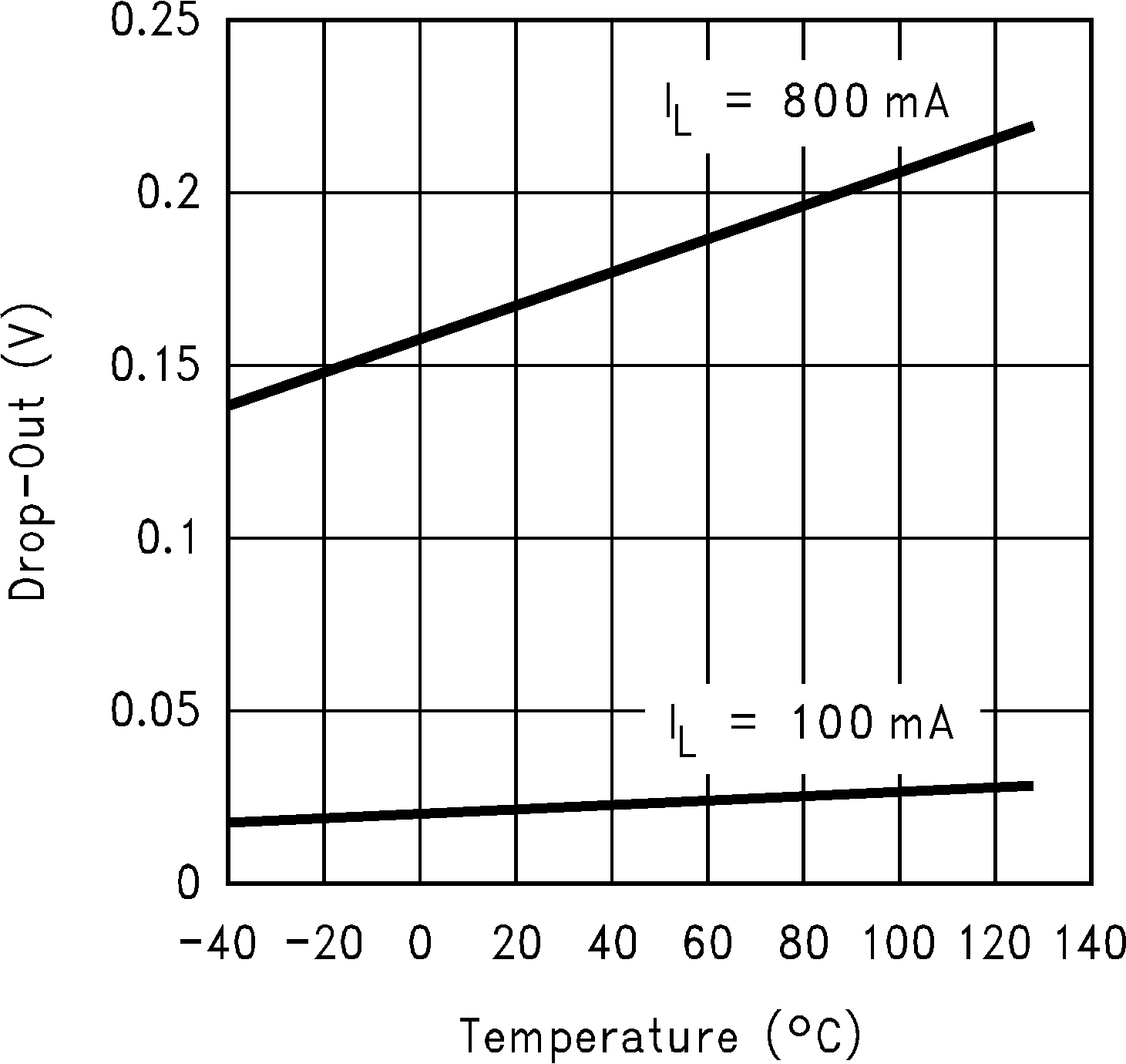

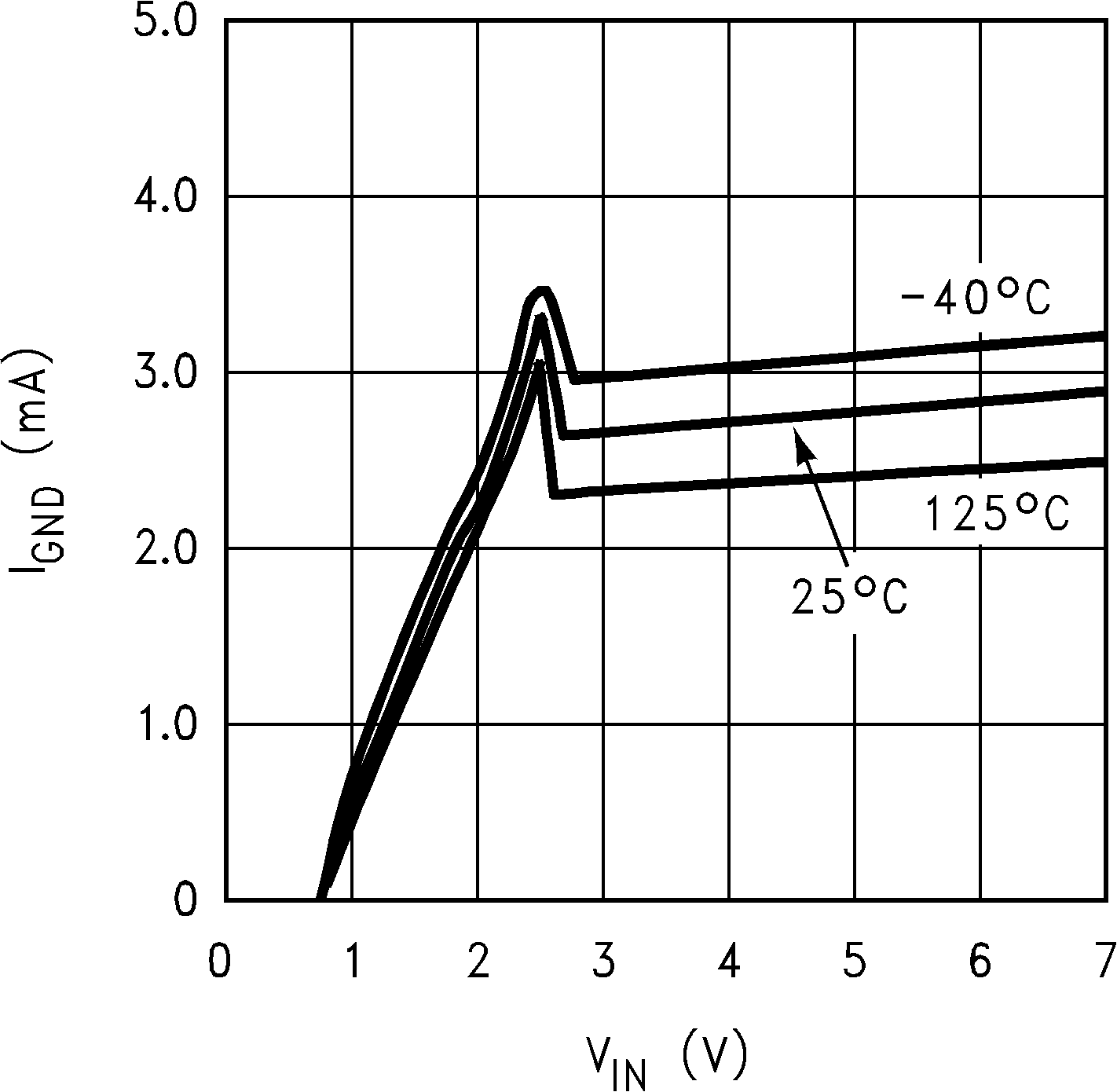

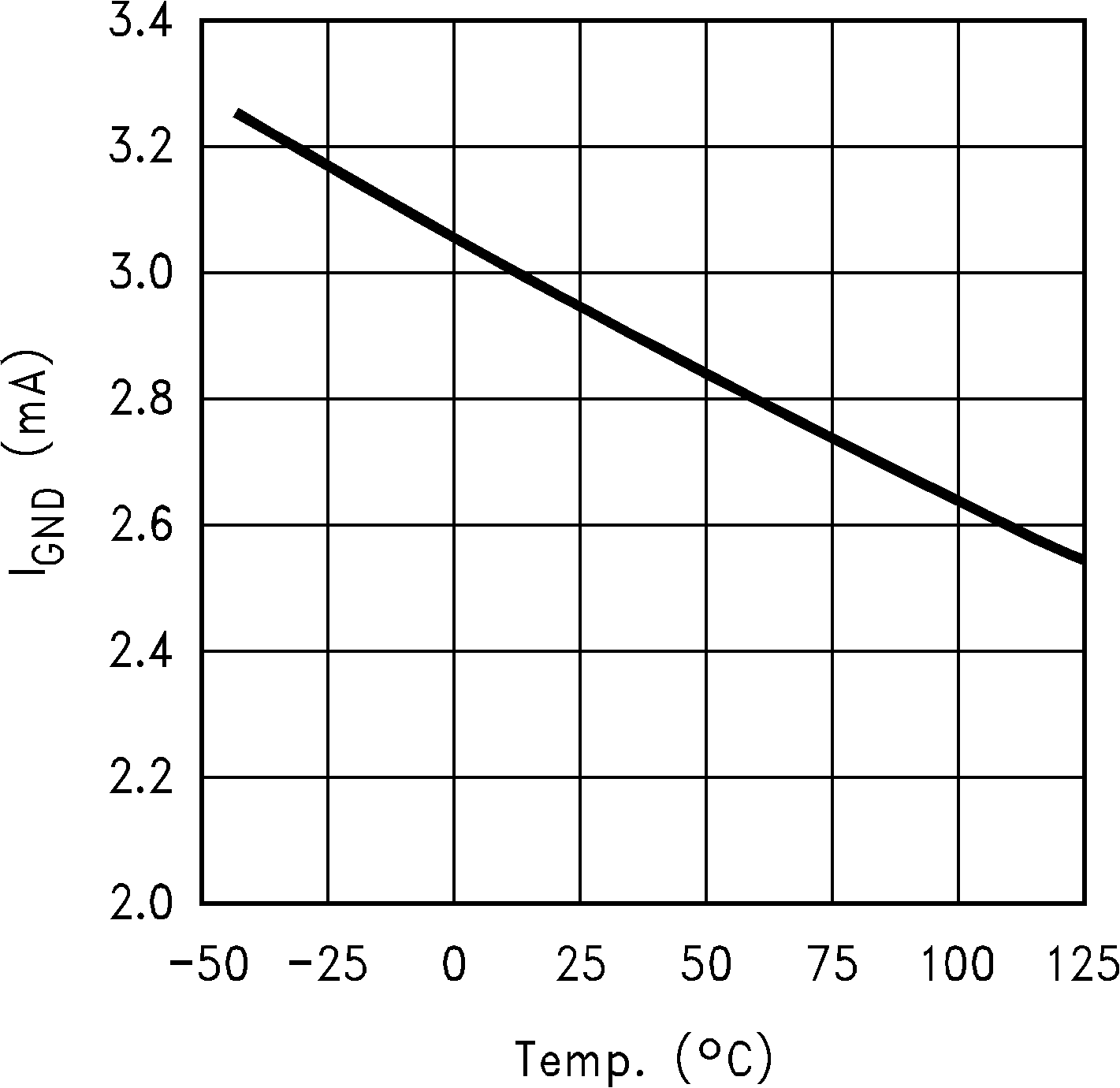

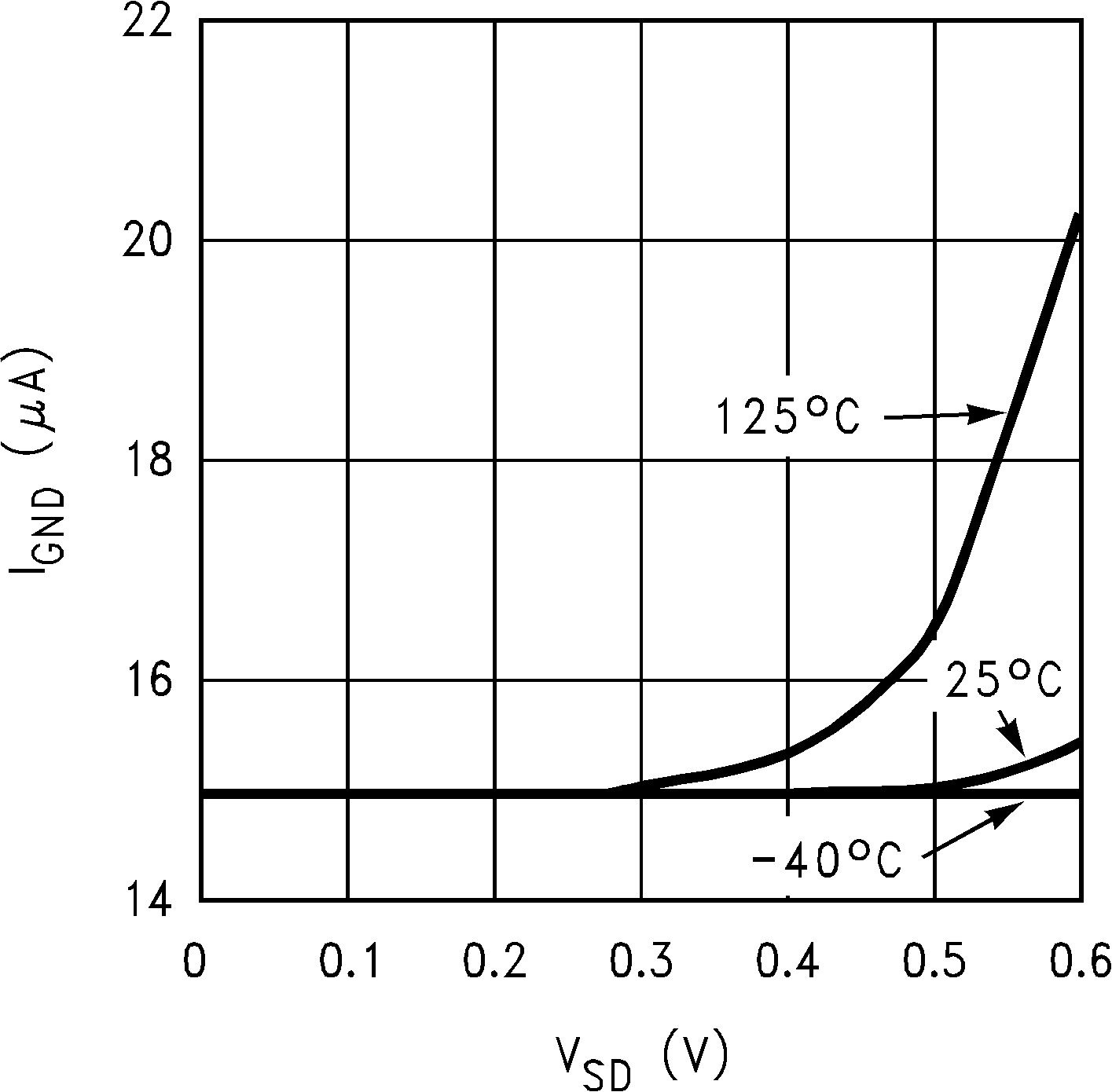

Unless otherwise specified, VIN = VO(NOM) + 1 V, VOUT = 2.5 V, COUT = 33 µF, IOUT = 10 mA, CIN = 68 µF, VSDT = VIN, andTA = 25°C.

Figure 1. Drop-Out Voltage vs Temperature for Different Load Currents

Figure 1. Drop-Out Voltage vs Temperature for Different Load Currents

Figure 3. Ground Pin Current vs Input Voltage (VSD = VIN)

Figure 3. Ground Pin Current vs Input Voltage (VSD = VIN)

Figure 5. Ground Current vs Temperature (VSD = VIN)

Figure 5. Ground Current vs Temperature (VSD = VIN)

Figure 7. Ground Pin Current vs Shutdown Pin Voltage

Figure 7. Ground Pin Current vs Shutdown Pin Voltage

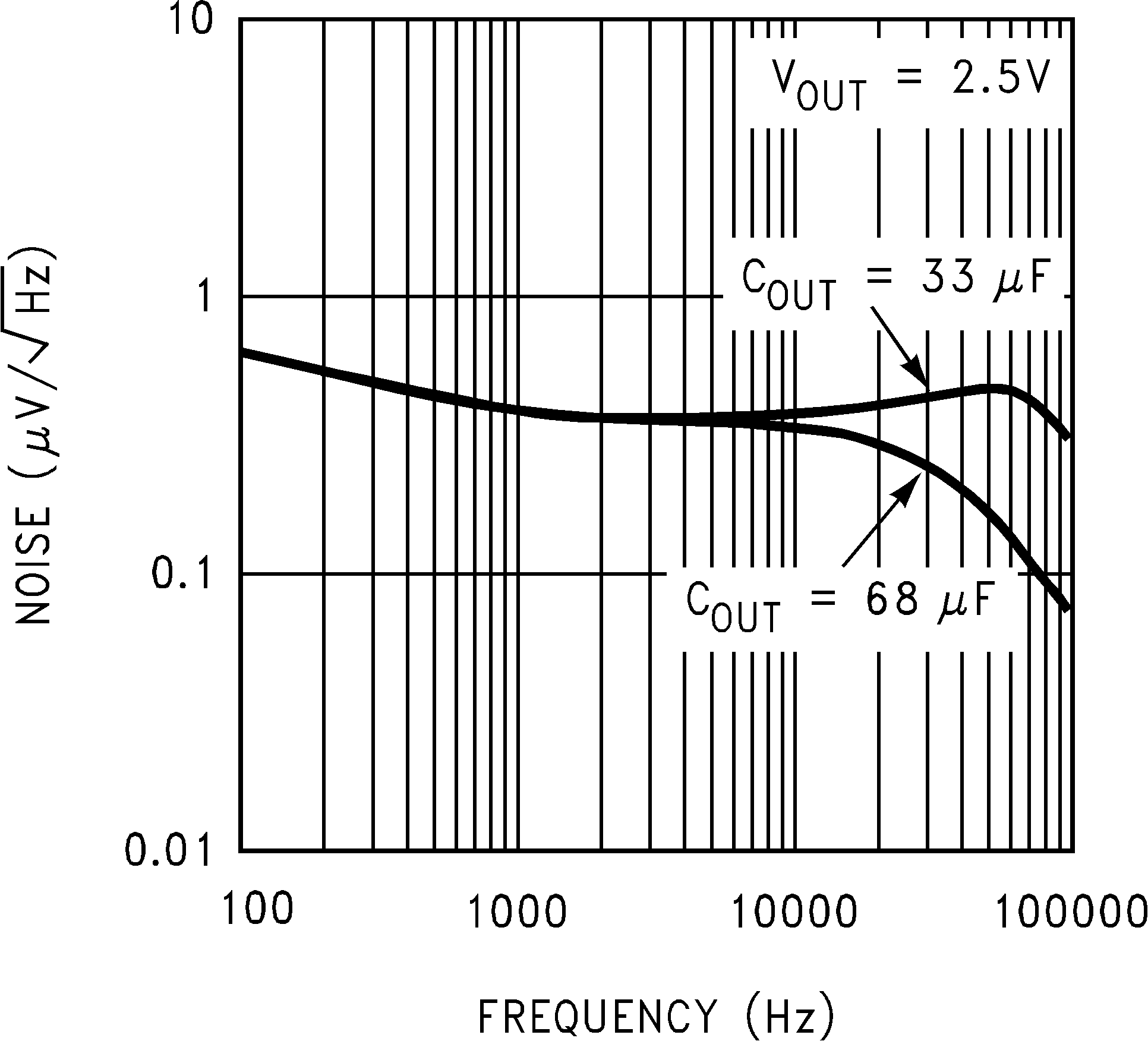

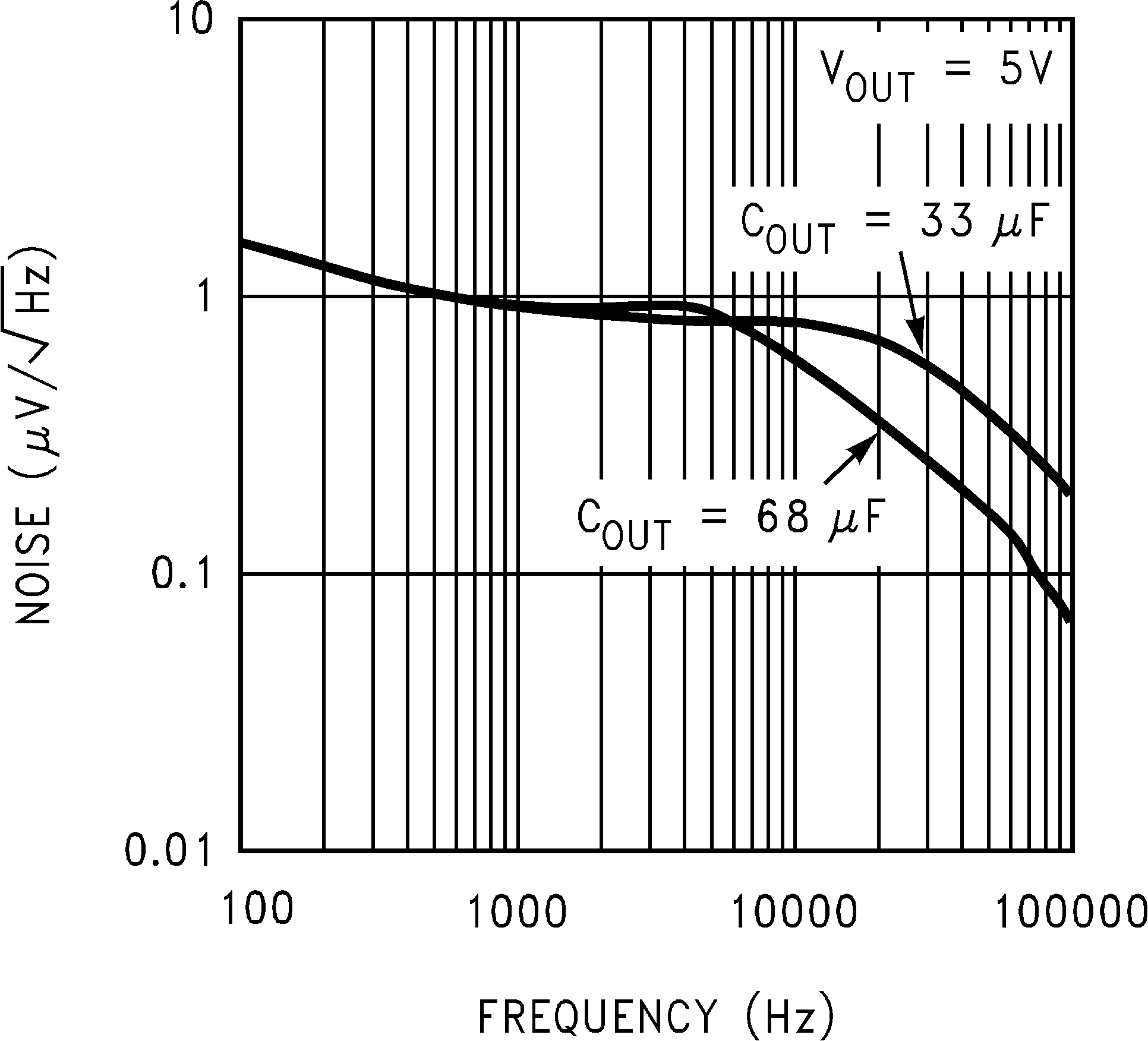

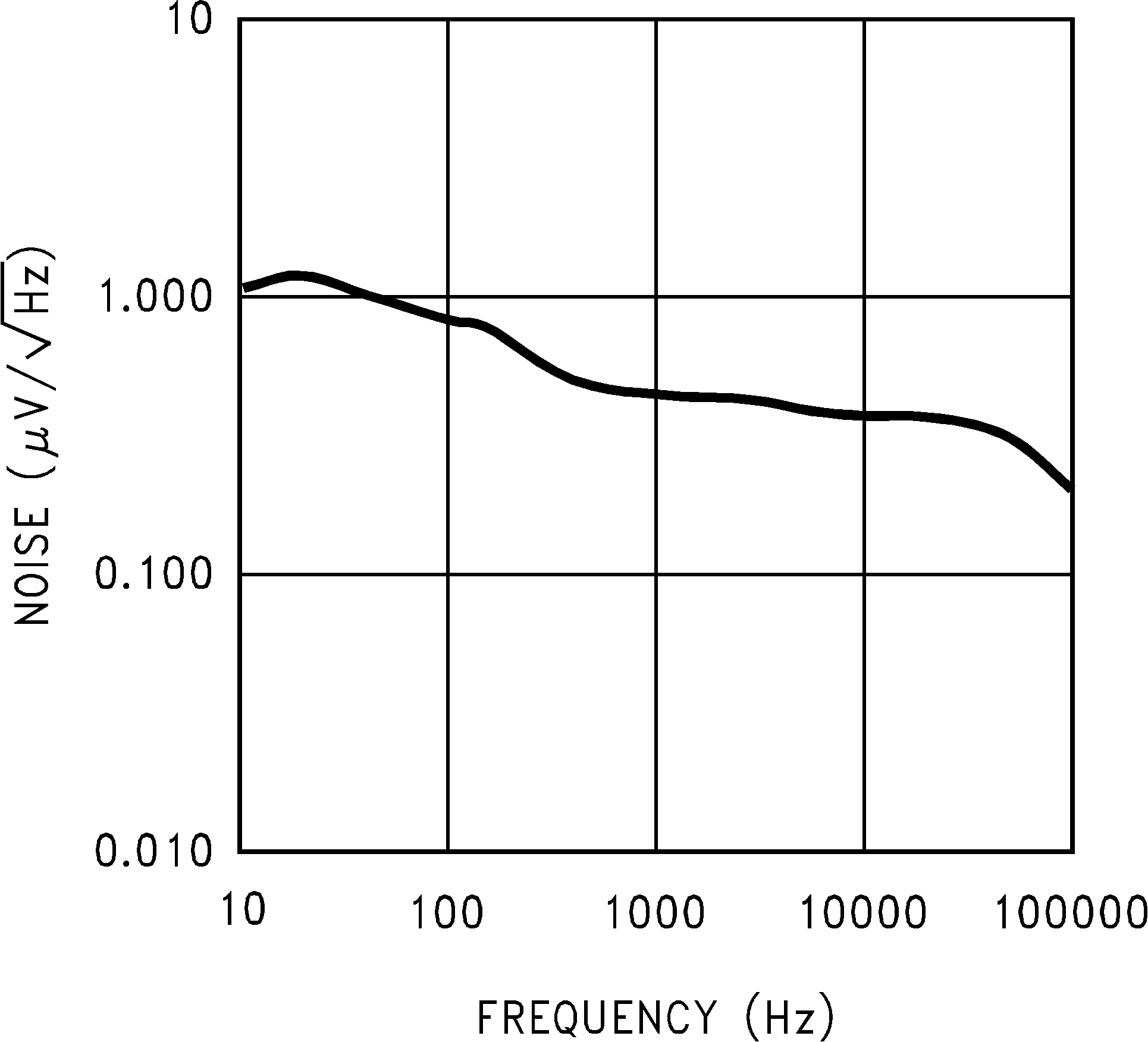

Figure 9. Output Noise Density, VOUT = 2.5 V

Figure 9. Output Noise Density, VOUT = 2.5 V

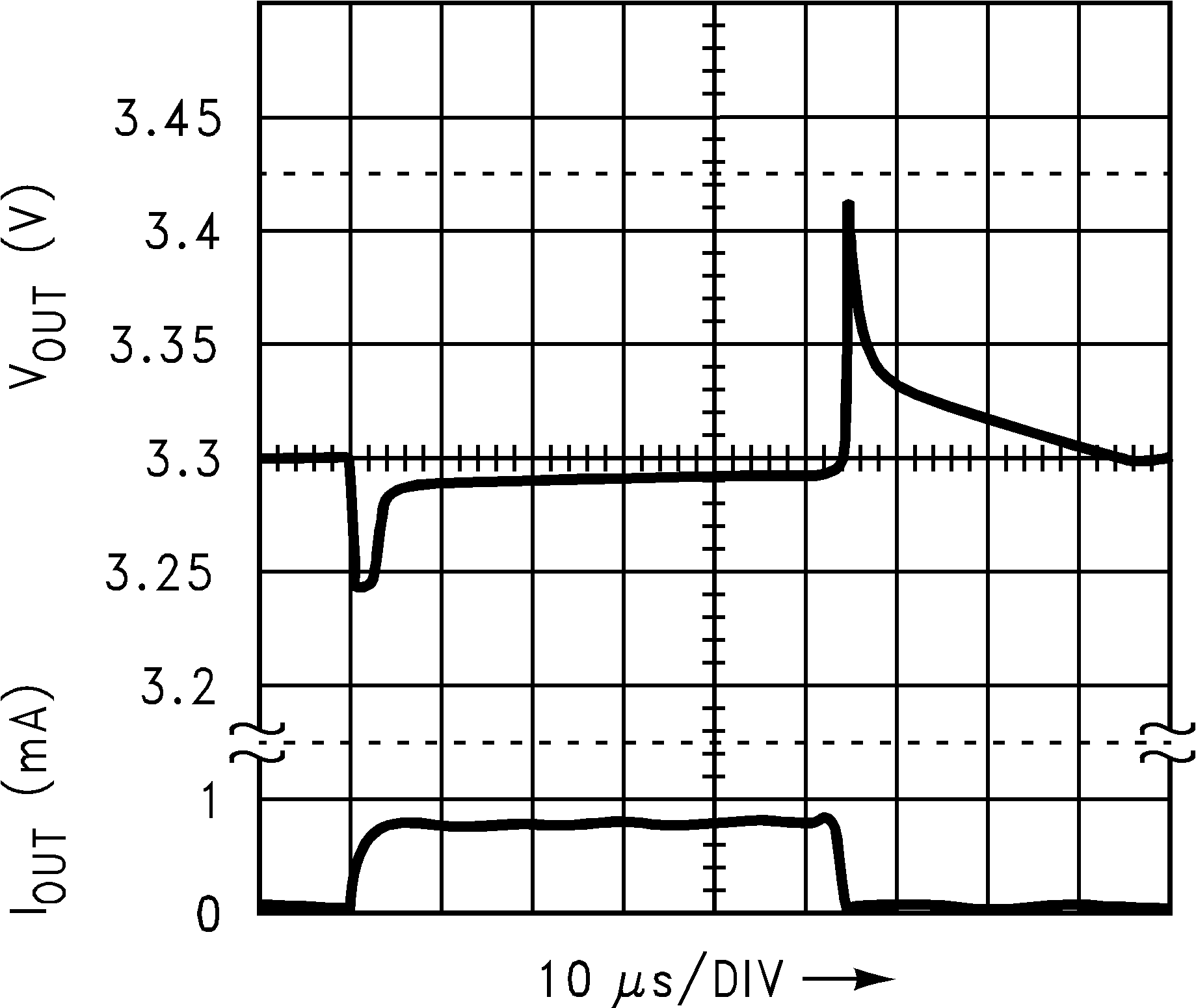

Figure 11. Load Transient Response

Figure 11. Load Transient Response

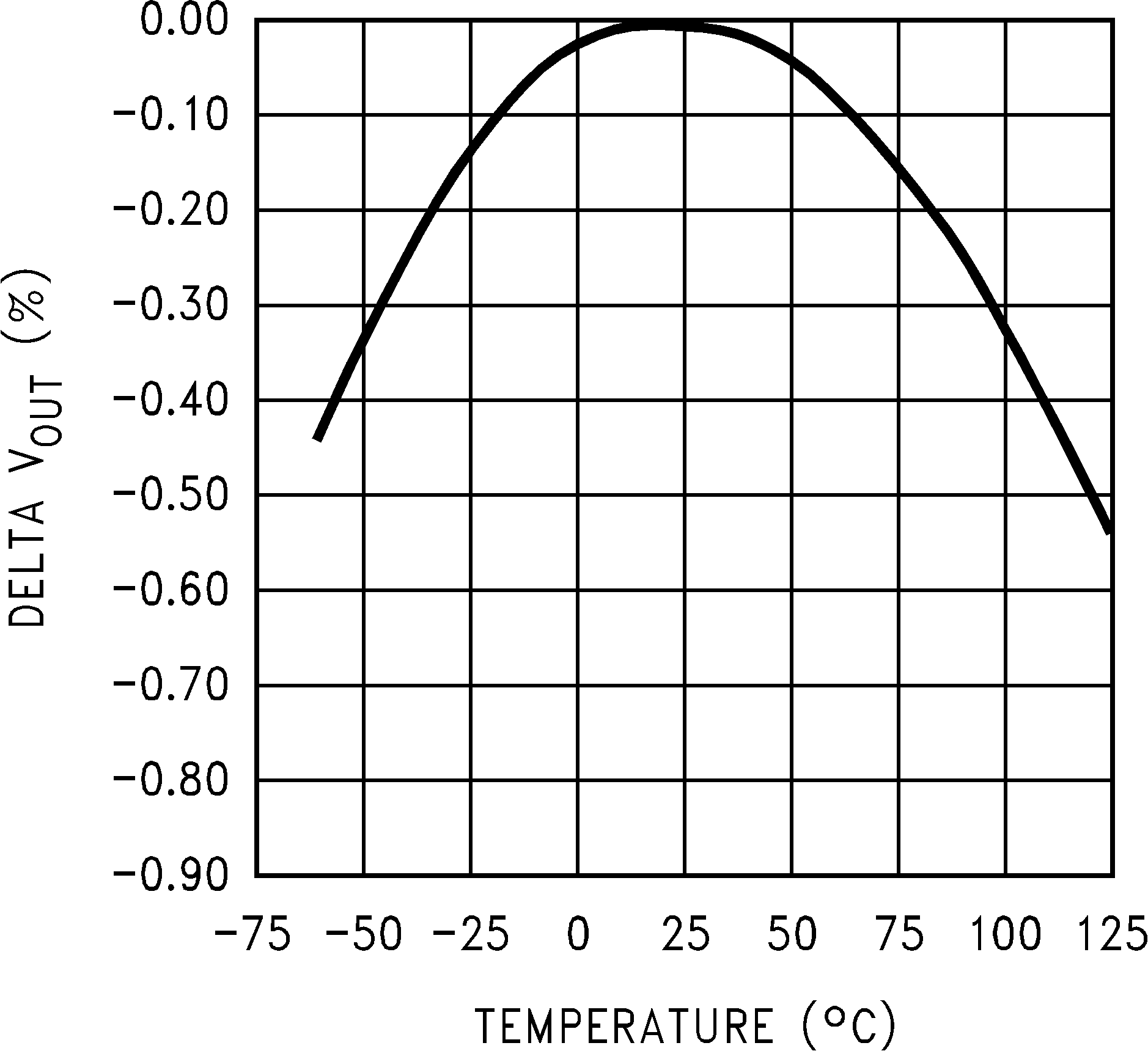

Figure 13. δVOUT vs Temperature

Figure 13. δVOUT vs Temperature

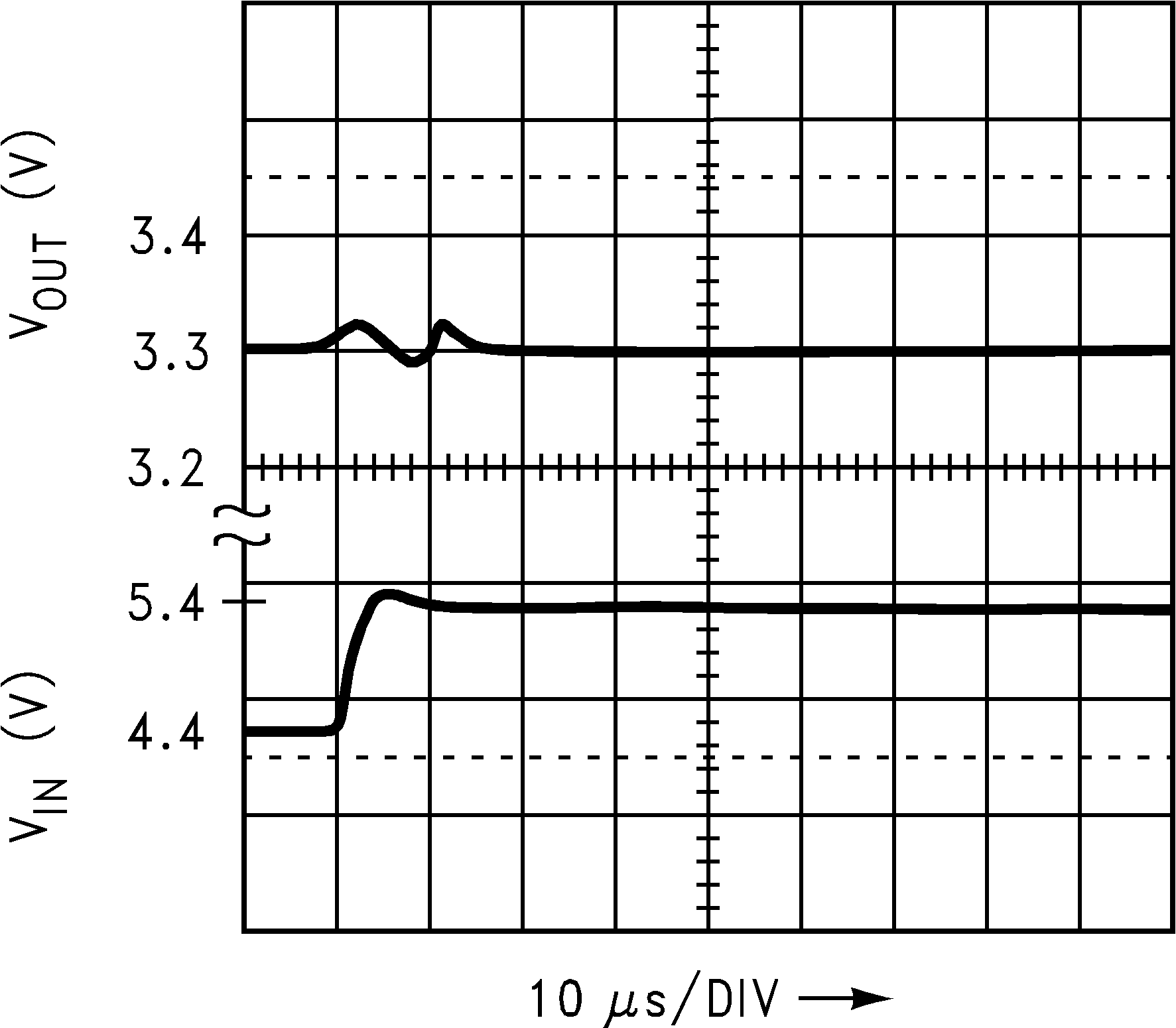

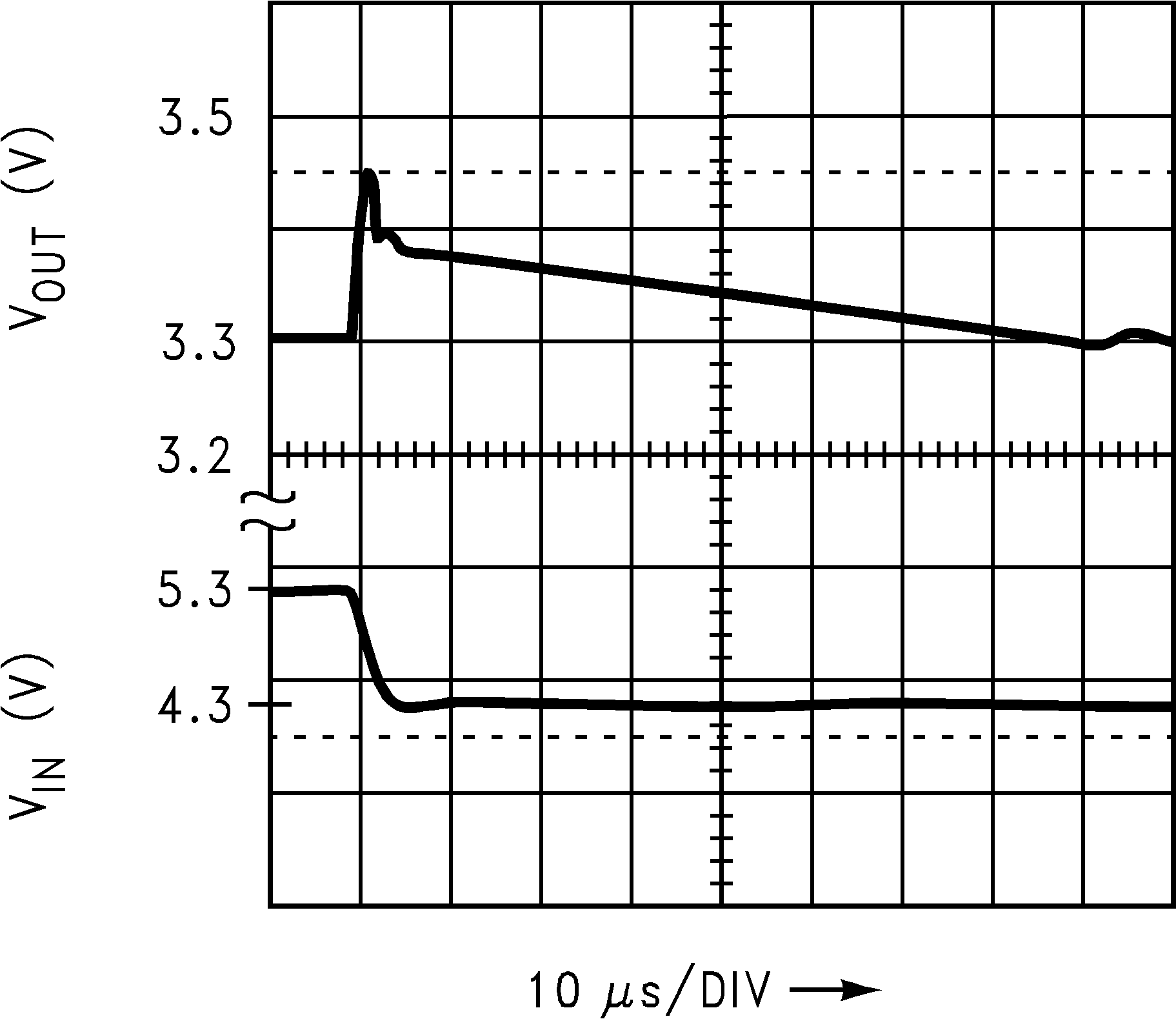

Figure 15. Line Transient Response

Figure 15. Line Transient Response

Figure 2. Drop-Out Voltage vs Temperature for Different Output Voltages (IOUT = 800 mA)

Figure 2. Drop-Out Voltage vs Temperature for Different Output Voltages (IOUT = 800 mA)

Figure 4. Ground Pin Current vs Input Voltage (VSD = 100 mV)

Figure 4. Ground Pin Current vs Input Voltage (VSD = 100 mV)

Figure 6. Ground Current vs Temperature (VSD = 0 V)

Figure 6. Ground Current vs Temperature (VSD = 0 V)

Figure 8. Input Voltage vs Output Voltage

Figure 8. Input Voltage vs Output Voltage

Figure 10. Output Noise Density, VOUT = 5 V

Figure 10. Output Noise Density, VOUT = 5 V

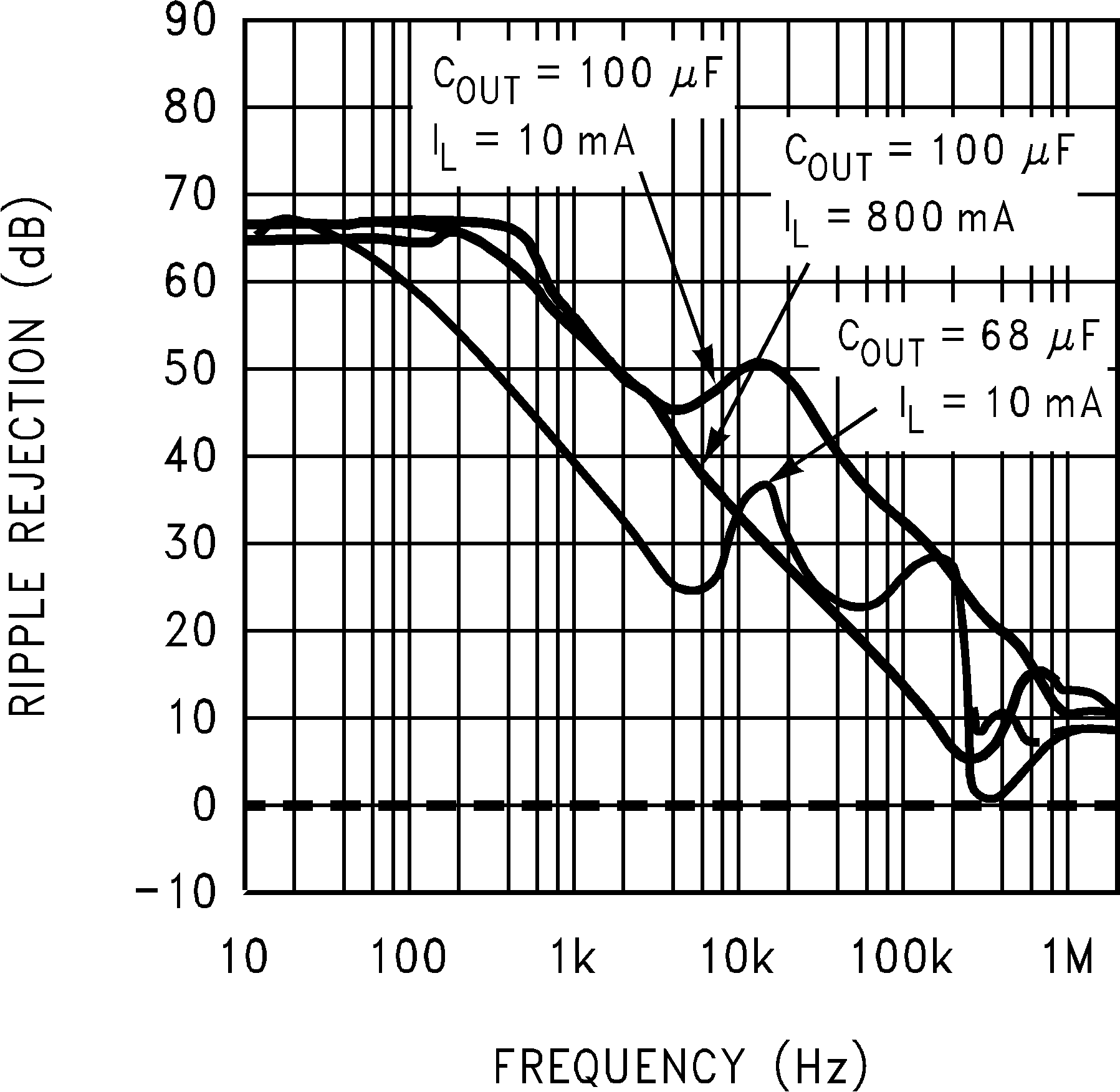

Figure 12. Ripple Rejection vs Frequency

Figure 12. Ripple Rejection vs Frequency

Figure 14. Noise Density VIN = 3.5 V, VOUT = 2.5 V, IL = 10 mA

Figure 14. Noise Density VIN = 3.5 V, VOUT = 2.5 V, IL = 10 mA

Figure 16. Line Transient Response

Figure 16. Line Transient Response