SLAS928B March 2013 – November 2016 LP3988-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device And Documentation Support

- 13Mechanical, Packaging, And Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- DBV|5

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

The LP3988-Q1 voltage regulator offers the benefit of ultra-low-dropout voltage, low noise, very low standby current, and miniaturized surface-mount packaging. The LP3988-Q1 is designed for continuous, or sporadic (power back-up), battery-operated applications where very low standby current is critical to extending system battery life.

9.2 Typical Application

Figure 16. LP3988-Q1 Typical Application

Figure 16. LP3988-Q1 Typical Application

9.2.1 Design Requirements

For typical CMOS voltage regulator applications, use the parameters listed in Table 1.

Table 1. Design Parameters

| DESIGN PARAMETER | EXAMPLE VALUE |

|---|---|

| Minimum input voltage | 3.05 V |

| Output voltage | 2.85 V |

| Output current | 150 mA |

9.2.2 Detailed Design Procedure

9.2.2.1 External Capacitors

Like any low-dropout regulator, the LP3988-Q1 requires external capacitors for regulator stability. The LP3988-Q1 is specifically designed for portable applications requiring minimum board space and smallest components. These capacitors must be correctly selected for good performance.

9.2.2.2 Input Capacitor

An input capacitance of at least 1 μF is required between the LP3988-Q1 IN pin and ground (the amount of the capacitance may be increased without limit). This capacitor must be located a distance of not more than 1cm from the input pin and returned to a clean analog ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input

NOTE

Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a low-impedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be ensured by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for the equivalent series resistance (ESR) on the input capacitor, but tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance is at least 1 μF over the entire operating temperature range.

9.2.2.3 Output Capacitors

The LP3988-Q1 is designed specifically to work with very small ceramic output capacitors. A ceramic capacitor (dielectric types Z5U, Y5V or X7R) in the 1-µF to 22-µF range with a 5-mΩ to 500-mΩ ESR range is suitable in the LP3988-Q1 application circuit.

It may also be possible to use tantalum or film capacitors at the output, but these are not as attractive for reasons of size and cost (see Capacitor Characteristics).

The output capacitor must meet the requirement for minimum amount of capacitance and also have an ESR value which is within a stable range (5 mΩ to 500 mΩ).

9.2.2.4 No-Load Stability

The LP3988-Q1 remains stable and in regulation with no external load. This is specially important in CMOS RAM keep-alive applications.

9.2.2.5 Capacitor Characteristics

The LP3988-Q1 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer: for capacitance values in the range of 1 µF to 4.7 µF, ceramic capacitors are the smallest, least expensive and have the lowest ESR values (which makes them best for eliminating high-frequency noise). The ESR of a typical 1-µF ceramic capacitor is in the range of 20 mΩ to 40 mΩ, which easily meets the ESR requirement for stability by the LP3988-Q1.

The ceramic capacitor's capacitance can vary with temperature. Most large-value ceramic capacitors (≊ 2.2 µF) are manufactured with Z5U or Y5V temperature characteristics, which results in the capacitance dropping by more than 50% as the temperature goes from 25°C to 85°C.

A better choice for temperature coefficient in a ceramic capacitor is X7R, which holds the capacitance within ±15%.

Tantalum capacitors are less desirable than ceramic for use as output capacitors because they are more expensive when comparing equivalent capacitance and voltage ratings in the 1-µF to 4.7-µF range.

Another important consideration is that tantalum capacitors have higher ESR values than equivalent-size ceramics. This means that while it may be possible to find a tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly ) than a ceramic capacitor with the same ESR value. It should also be noted that the ESR of a typical tantalum will increase about 2:1 as the temperature goes from 25°C down to −40°C, so some guard band must be allowed.

9.2.2.6 Power Dissipation

Knowing the device power dissipation and proper sizing of the thermal plane connected to the tab or pad is critical to ensuring reliable operation. Device power dissipation depends on input voltage, output voltage, and load conditions and can be calculated with Equation 1.

Power dissipation can be minimized, and greater efficiency can be achieved, by using the lowest available voltage drop option that would still be greater than the dropout voltage (VDO). However, keep in mind that higher voltage drops result in better dynamic (that is, PSRR and transient) performance.

On the SOT-23 (DBV) package, the primary conduction path for heat is through the device leads to the PCB, predominately device lead 2 (GND). TI recommends that the trace from lead 2 be extended under the package body and connected to an internal ground plane with thermal vias.

The maximum allowable junction temperature (TJ(MAX)) determines maximum power dissipation allowed (PD(MAX)) for the device package.

Power dissipation and junction temperature are most often related by the junction-to-ambient thermal resistance (RθJA) of the combined PCB and device package and the temperature of the ambient air (TA), according to Equation 2 or Equation 3:

Unfortunately, this RθJA is highly dependent on the heat-spreading capability of the particular PCB design, and therefore varies according to the total copper area, copper weight, and location of the planes. The RθJA recorded in Thermal Information is determined by the specific EIA/JEDEC JESD51-7 standard for PCB and copper-spreading area, and is to be used only as a relative measure of package thermal performance.

9.2.2.7 Estimating Junction Temperature

The EIA/JEDEC standard recommends the use of psi (Ψ) thermal characteristics to estimate the junction temperatures of surface mount devices on a typical PCB board application. These characteristics are not true thermal resistance values, but rather package specific thermal characteristics that offer practical and relative means of estimating junction temperatures. These psi metrics are determined to be significantly independent of copper-spreading area. The key thermal characteristics (ΨJT and ΨJB) are given in Thermal Information and are used in accordance with Equation 4 or Equation 5.

where

- PD(MAX) is explained in Equation 1.

- TTOP is the temperature measured at the center-top of the device package.

where

- PD(MAX) is explained in Equation 1.

- TBOARD is the PCB surface temperature measured 1-mm from the device package and centered on the package edge.

For more information about the thermal characteristics ΨJT and ΨJB, see Semiconductor and IC Package Thermal Metrics, available for download at www.ti.com.

For more information about measuring TTOP and TBOARD, see Using New Thermal Metrics, available for download at www.ti.com.

For more information about the EIA/JEDEC JESD51 PCB used for validating RθJA, see the Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs, available for download at www.ti.com.

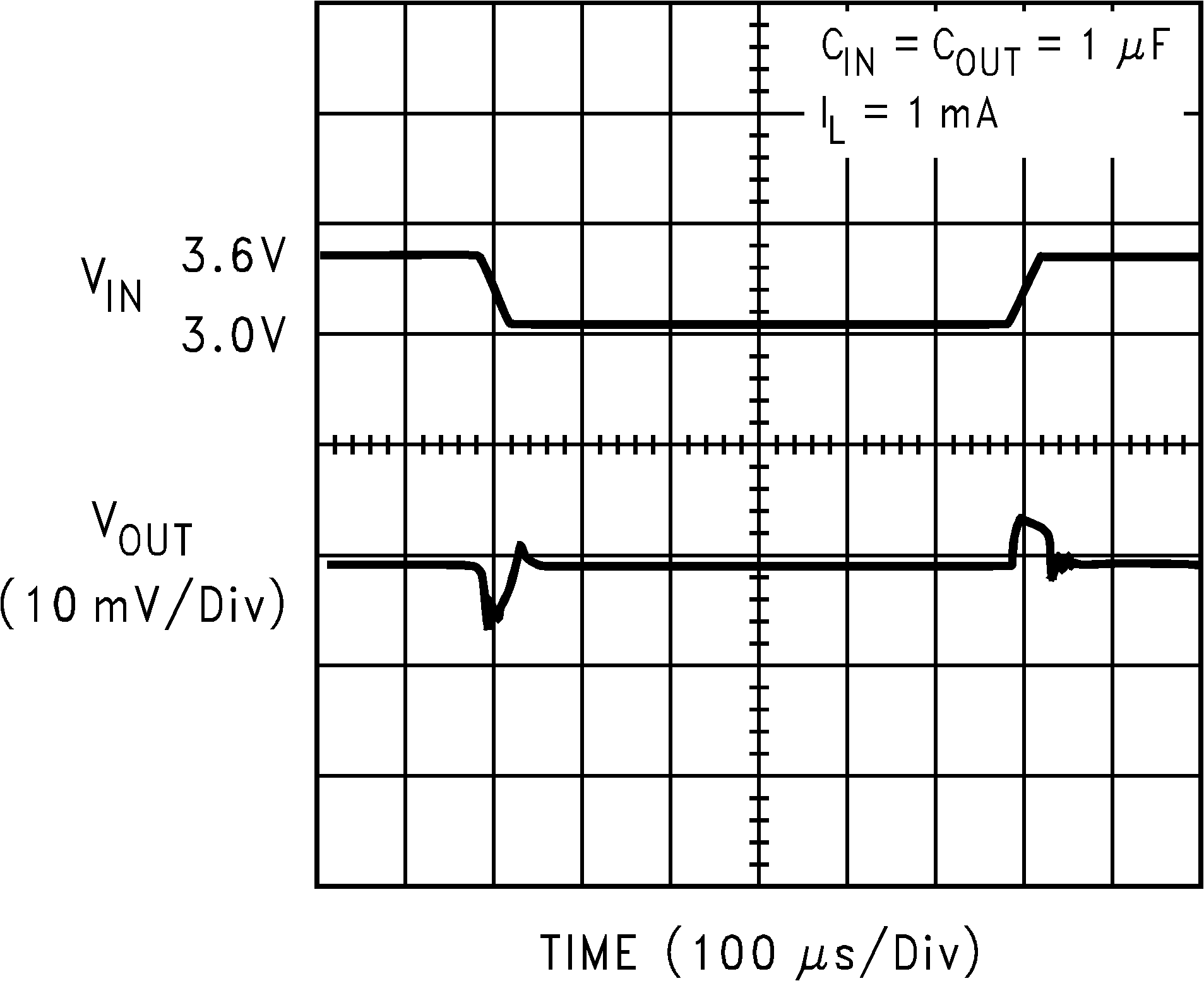

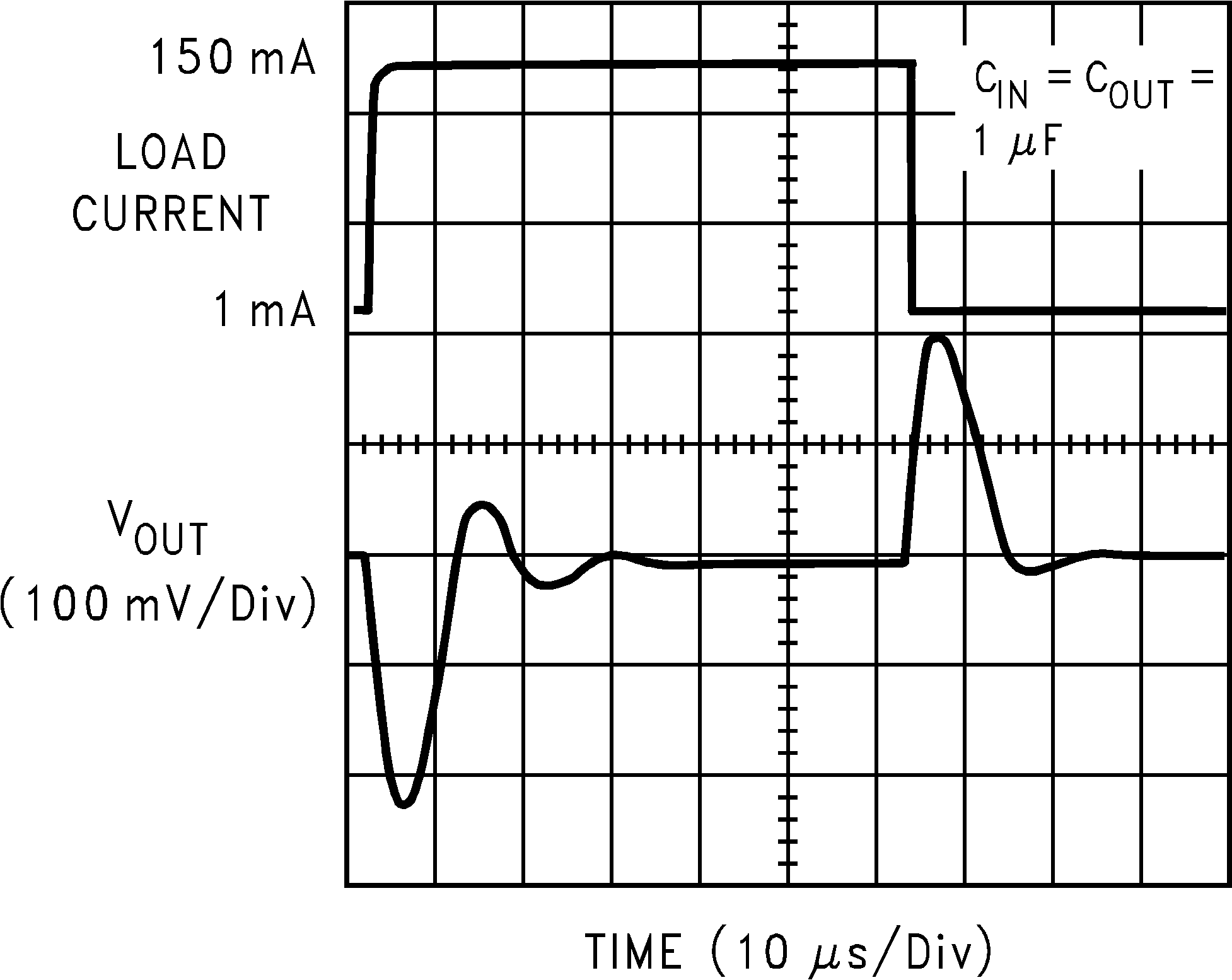

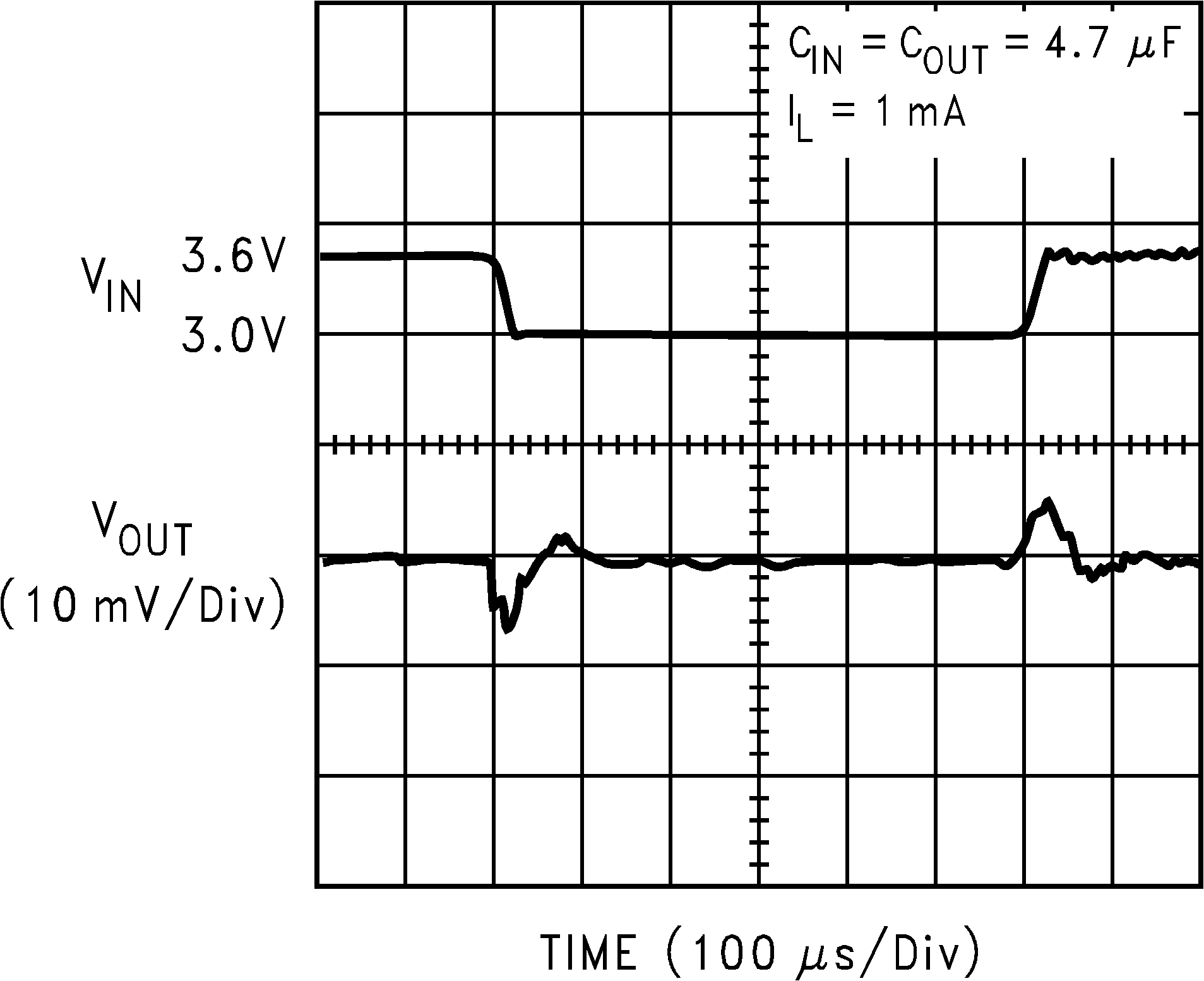

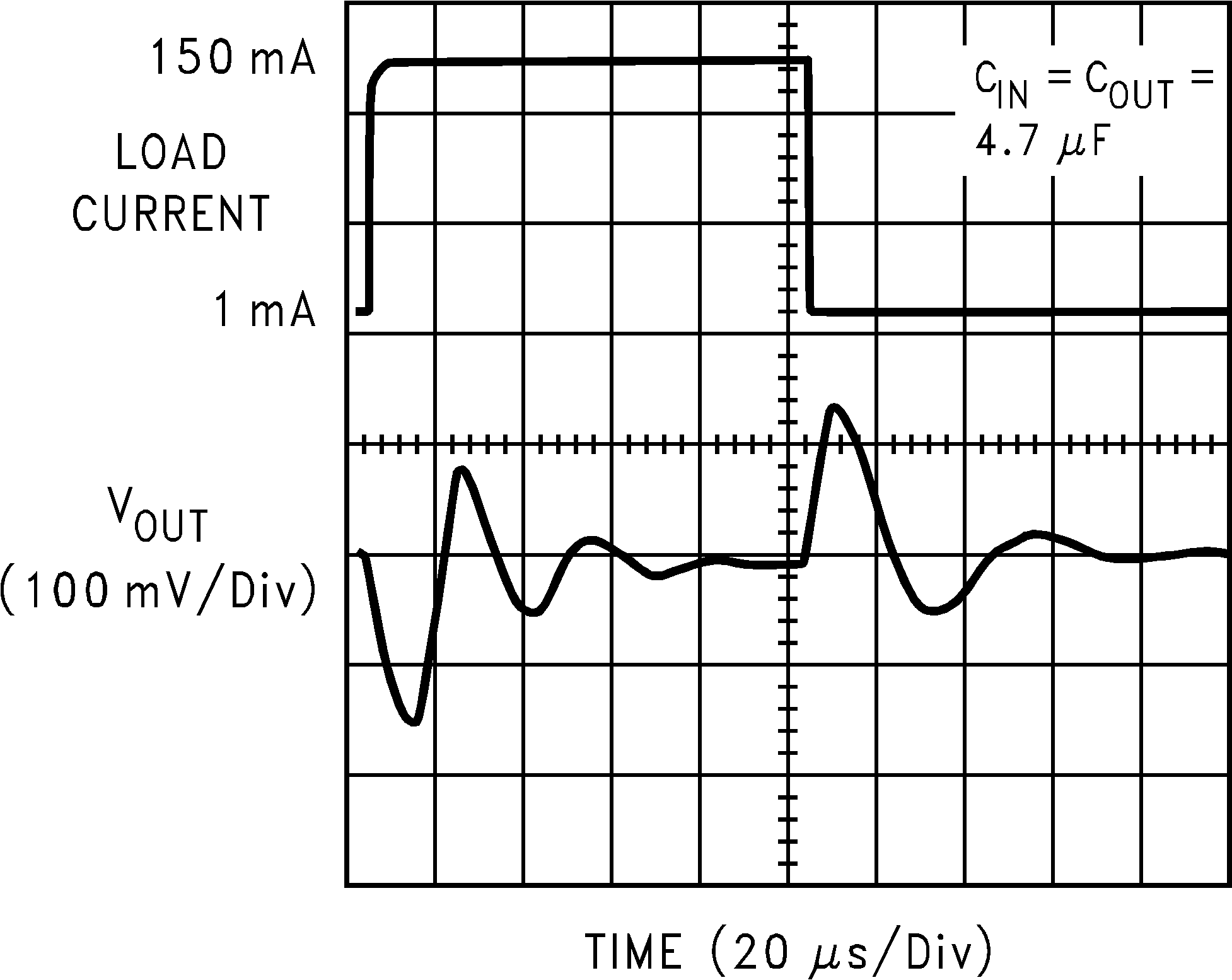

9.2.3 Application Curves