SLASEE5D January 2018 – January 2021 MSP430FR2422

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Functional Block Diagram

- 5 Revision History

- 6 Device Comparison

- 7 Terminal Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Active Mode Supply Current Into VCC Excluding External Current

- 8.5 Active Mode Supply Current Per MHz

- 8.6 Low-Power Mode (LPM0) Supply Currents Into VCC Excluding External Current

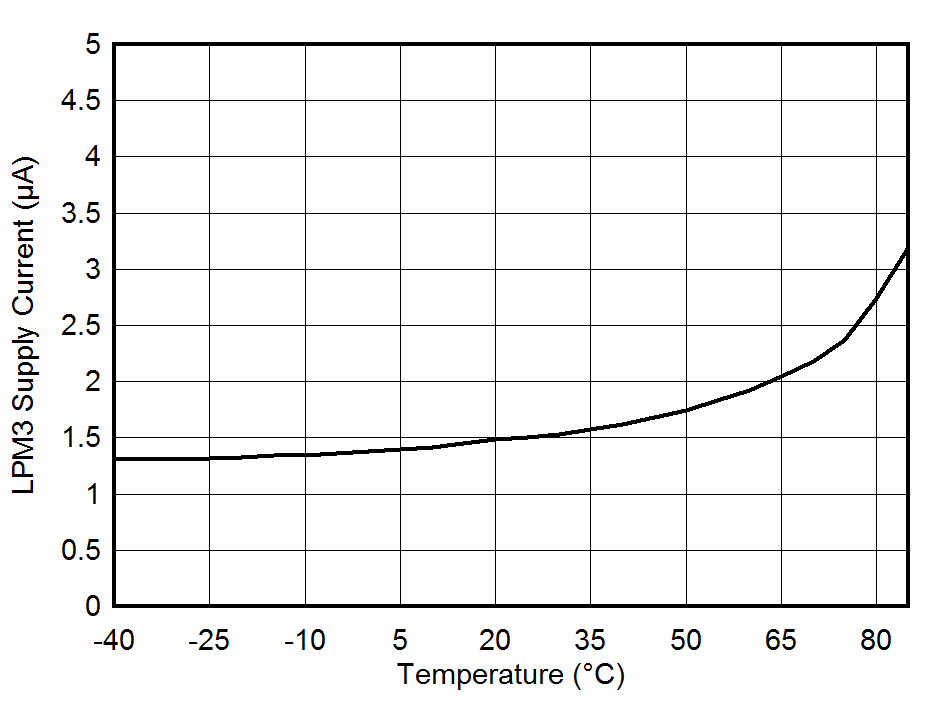

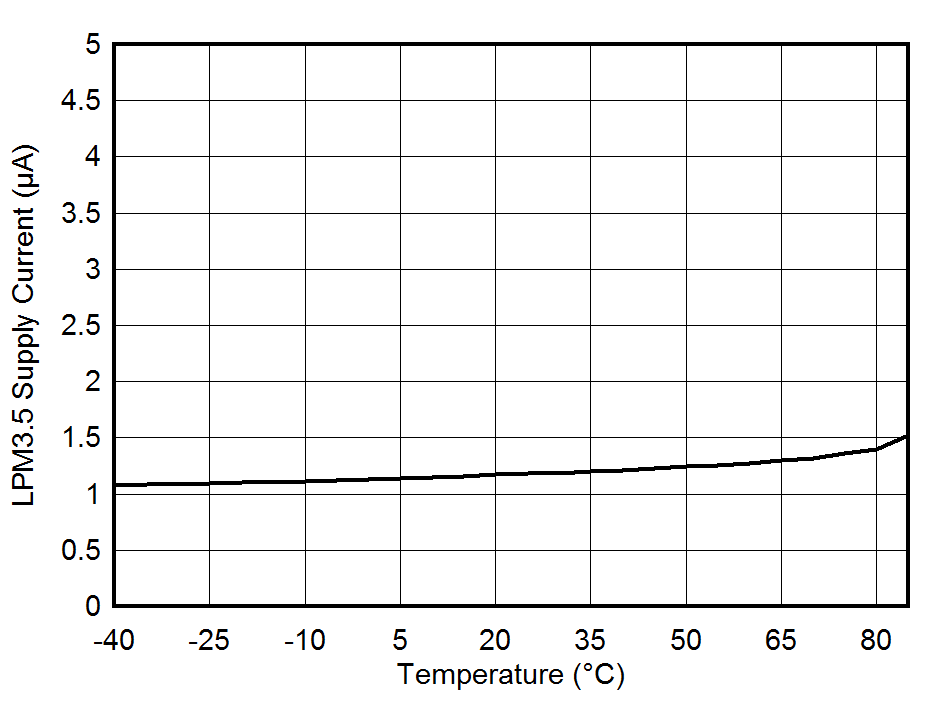

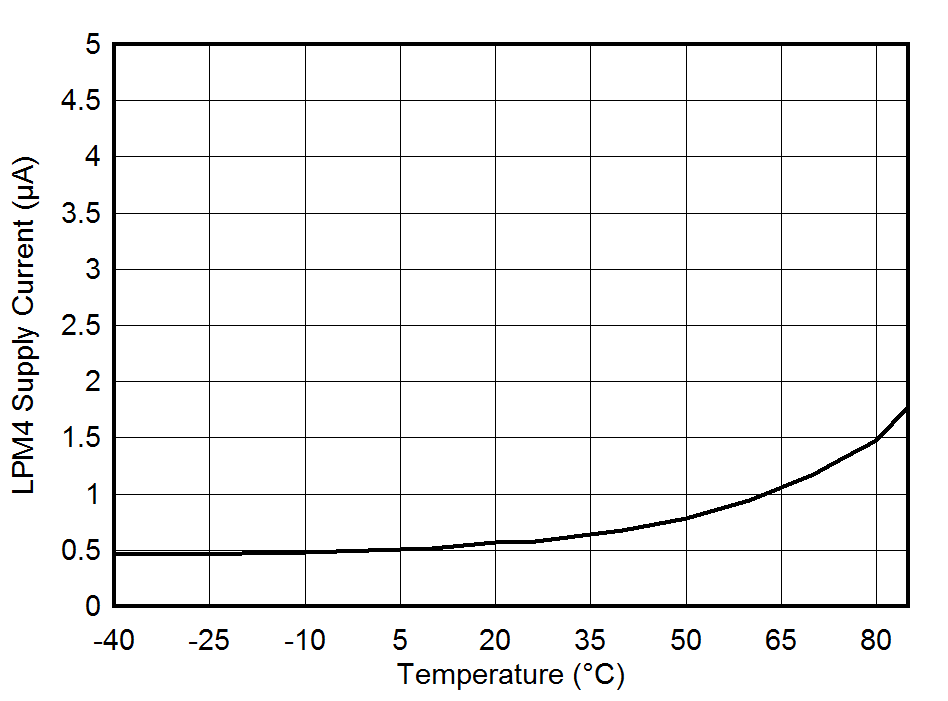

- 8.7 Low-Power Mode (LPM3, LPM4) Supply Currents (Into VCC) Excluding External Current

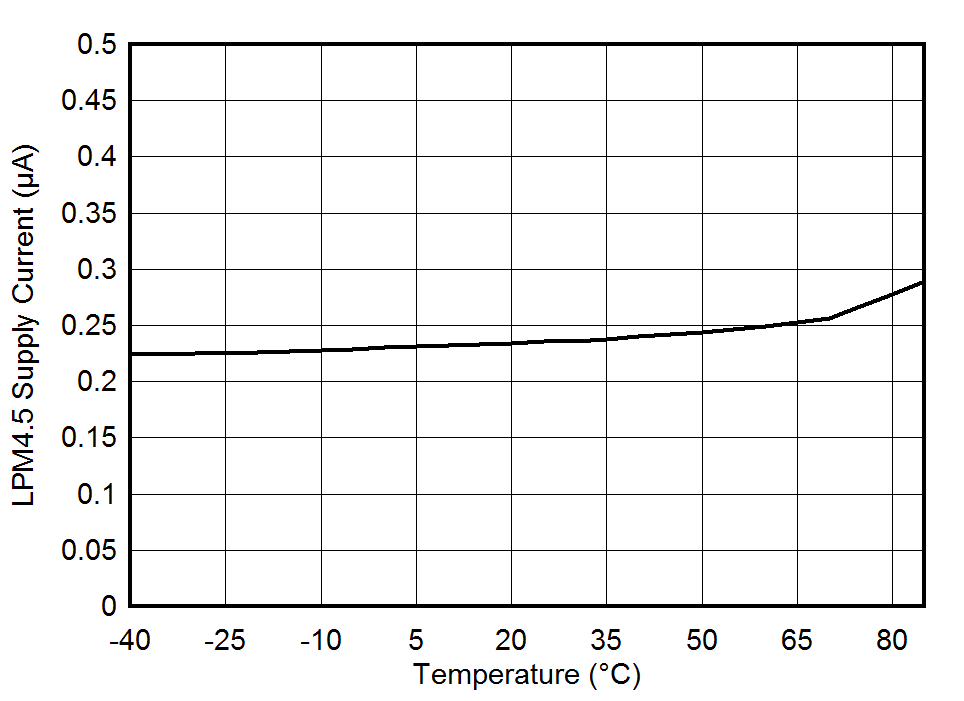

- 8.8 Low-Power Mode (LPMx.5) Supply Currents (Into VCC) Excluding External Current

- 8.9 Typical Characteristics - Low-Power Mode Supply Currents

- 8.10 Typical Characteristics – Current Consumption Per Module

- 8.11 Thermal Resistance Characteristics

- 8.12 Timing and Switching Characteristics

-

9 Detailed Description

- 9.1 Overview

- 9.2 CPU

- 9.3 Operating Modes

- 9.4 Interrupt Vector Addresses

- 9.5 Bootloader (BSL)

- 9.6 JTAG Standard Interface

- 9.7 Spy-Bi-Wire Interface (SBW)

- 9.8 FRAM

- 9.9 Memory Protection

- 9.10

Peripherals

- 9.10.1 Power-Management Module (PMM)

- 9.10.2 Clock System (CS) and Clock Distribution

- 9.10.3 General-Purpose Input/Output Port (I/O)

- 9.10.4 Watchdog Timer (WDT)

- 9.10.5 System (SYS) Module

- 9.10.6 Cyclic Redundancy Check (CRC)

- 9.10.7 Enhanced Universal Serial Communication Interface (eUSCI_A0, eUSCI_B0)

- 9.10.8 Timers (Timer0_A3, Timer1_A3)

- 9.10.9 Hardware Multiplier (MPY)

- 9.10.10 Backup Memory (BAKMEM)

- 9.10.11 Real-Time Clock (RTC)

- 9.10.12 10-Bit Analog-to-Digital Converter (ADC)

- 9.10.13 Embedded Emulation Module (EEM)

- 9.11 Input/Output Diagrams

- 9.12 Device Descriptors

- 9.13 Memory

- 9.14 Identification

- 10Applications, Implementation, and Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- PW|16

- RHL|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8.9 Typical Characteristics - Low-Power Mode Supply Currents

| VCC = 3 V | RTC enabled | SVS disabled |

| VCC = 3 V | XT1 enabled | SVS enabled |

| VCC = 3 V | RTC enabled | SVS disabled |

| VCC = 3 V | SVS enabled |