SLOS982C August 2017 – April 2018 TAS5755M

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 PWM Operation at Recommended Operating Conditions

- 7.6 DC Electrical Characteristics

- 7.7 AC Electrical Characteristics (BTL, PBTL)

- 7.8 Electrical Characteristics - PLL External Filter Components

- 7.9 Electrical Characteristic - I2C Serial Control Port Operation

- 7.10 Timing Requirements - PLL Input Parameters

- 7.11 Timing Requirements - Serial Audio Ports Slave Mode

- 7.12 Timing Requirements - I2C Serial Control Port Operation

- 7.13 Timing Requirements - Reset (RESET)

- 7.14 Typical Characteristics

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagrams

- 9.3

Feature Description

- 9.3.1 Power Supply

- 9.3.2 I2C Address Selection and Fault Output

- 9.3.3 Single-Filter PBTL Mode

- 9.3.4 Device Protection System

- 9.3.5 SSTIMER Functionality

- 9.3.6 Clock, Autodetection, and PLL

- 9.3.7 PWM Section

- 9.3.8 2.1-Mode Support

- 9.3.9 I2C Compatible Serial Control Interface

- 9.3.10 Audio Serial Interface

- 9.3.11 Dynamic Range Control (DRC)

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6

Register Maps

- 9.6.1 Register Map Summary

- 9.6.2

Register Maps

- 9.6.2.1 Clock Control Register (0x00)

- 9.6.2.2 Device ID Register (0x01)

- 9.6.2.3 Error Status Register (0x02)

- 9.6.2.4 System Control Register 1 (0x03)

- 9.6.2.5 Serial Data Interface Register (0x04)

- 9.6.2.6 System Control Register 2 (0x05)

- 9.6.2.7 Soft Mute Register (0x06)

- 9.6.2.8 Volume Registers (0x07, 0x08, 0x09, 0x0A)

- 9.6.2.9 Volume Configuration Register (0x0E)

- 9.6.2.10 Modulation Limit Register (0x10)

- 9.6.2.11 Interchannel Delay Registers (0x11, 0x12, 0x13, and 0x14)

- 9.6.2.12 PWM Shutdown Group Register (0x19)

- 9.6.2.13 Start/Stop Period Register (0x1A)

- 9.6.2.14 Oscillator Trim Register (0x1B)

- 9.6.2.15 BKND_ERR Register (0x1C)

- 9.6.2.16 Input Multiplexer Register (0x20)

- 9.6.2.17 Channel 4 Source Select Register (0x21)

- 9.6.2.18 PWM Output Mux Register (0x25)

- 9.6.2.19 DRC Control Register (0x46)

- 9.6.2.20 Bank Switch and EQ Control Register (0x50)

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Applications

- 10.2.1 Stereo Bridge Tied Load Application

- 10.2.2 Mono Parallel Bridge Tied Load Application

- 10.2.3 2.1 Application

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

Package Options

Mechanical Data (Package|Pins)

- DFD|56

Thermal pad, mechanical data (Package|Pins)

- DFD|56

Orderable Information

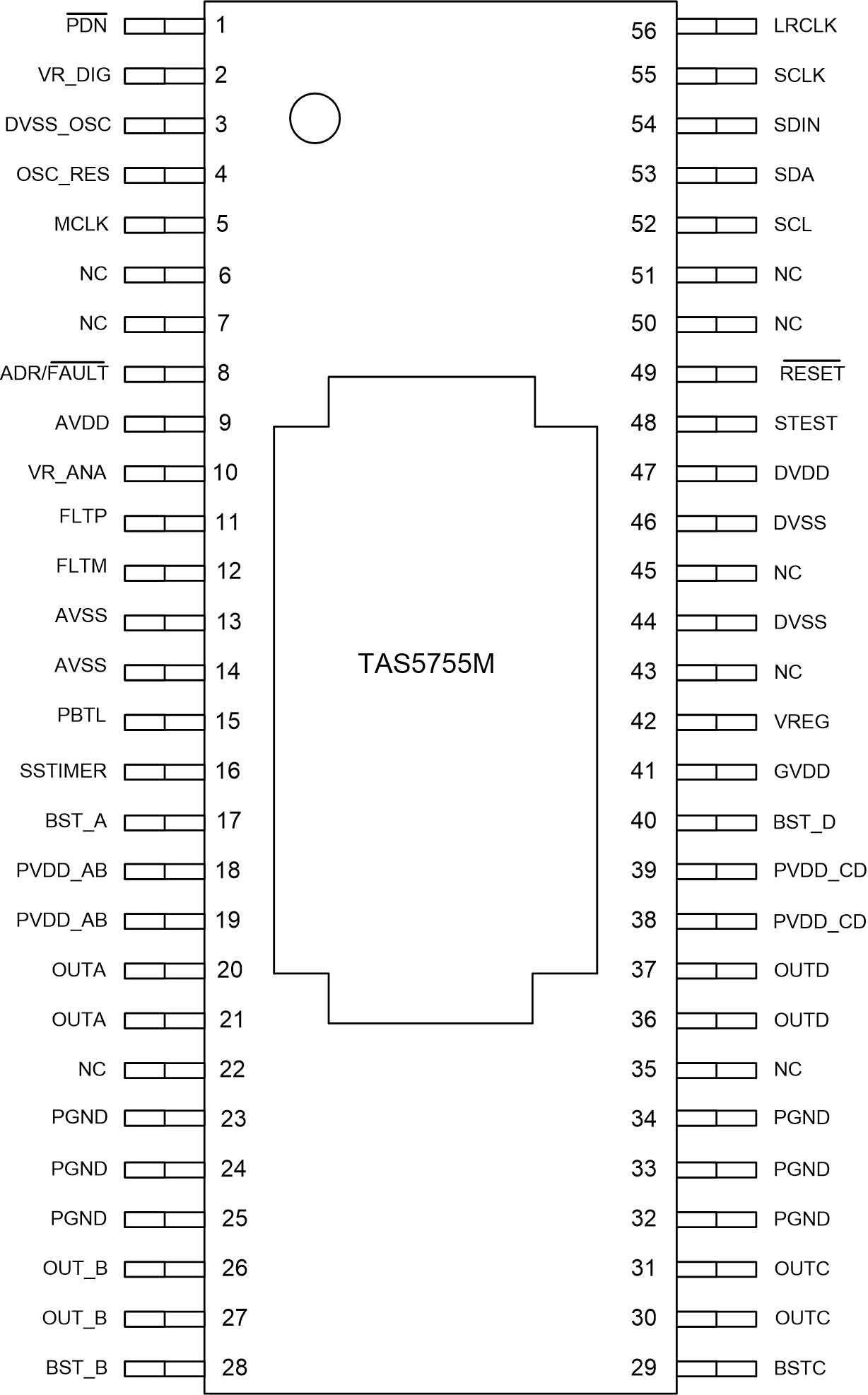

6 Pin Configuration and Functions

HTSSOP Package

56-Pin DFD

Top View

Pin Functions

| PIN | TYPE(1) | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| ADR/FAULT | 8 | DIO | Dual function terminal which sets the LSB of the 7-bit I2C address to "0" if pulled to GND and to "1" if pulled to DVDD. If configured to be a fault output by the methods described in I²C Address Selection and Fault Output, this terminal is pulled low when an internal fault occurs. A pull-up or pull-down resistor is required, as is shown in the Typical Application Circuit Diagrams. If pulled high (to DVDD), a 15-kΩ resistor must be used to minimize in-rush current at power up and to isolate the net if the pin is used as a fault output, as described above. |

| AVDD | 9 | P | 3.3-V analog power supply |

| AVSS | 13,14 | P | Analog 3.3-V supply ground |

| BST_A | 17 | P | High-side bootstrap supply for half-bridge A |

| BST_B | 28 | P | High-side bootstrap supply for half-bridge B |

| BST_C | 29 | P | High-side bootstrap supply for half-bridge C |

| BST_D | 40 | P | High-side bootstrap supply for half-bridge D |

| DVDD | 47 | P | 3.3-V digital power supply |

| DVSS | 44,46 | P | Digital ground |

| DVSS_OSC | 3 | P | Oscillator ground |

| GVDD | 41 | P | Gate drive internal regulator output |

| LRCLK | 56 | P | Input serial audio data left/right clock (sample-rate clock) |

| MCLK | 5 | DI | Master clock input |

| NC | 6,7,22,35,43,45,50,51 | – | No connect |

| OSC_RES | 4 | AO | Oscillator trim resistor. Connect an 18.2-kΩ, 1% resistor to DVSS_OSC ground. |

| OUT_A | 20,21 | O | Output, half-bridge A |

| OUT_B | 26,27 | O | Output, half-bridge B |

| OUT_C | 30,31 | O | Output, half-bridge C |

| OUT_D | 36,37 | O | Output, half-bridge D |

| PBTL | 15 | DI | Low means BTL mode; high means PBTL mode. Information goes directly to power stage. |

| PDN | 1 | DI | Power down, active-low. PDN prepares the device for loss of power supplies by shutting down the noise shaper and initiating the PWM stop sequence. |

| PGND | 23,24,25, 32,33,34 | P | Power ground for half-bridges A and B |

| FLTM | 12 | AO | PLL negative loop-filter terminal |

| FLTP | 11 | AO | PLL positive loop-filter terminal |

| PVDD_AB | 18,19 | P | Power-supply input for half-bridge output A and B |

| PVDD_CD | 38,39 | P | Power-supply input for half-bridge output C and D |

| RESET | 49 | DI | Reset, active-low. A system reset is generated by applying a logic low to this pin. RESET is an asynchronous control signal that restores the DAP to its default conditions and places the PWM in the hard-mute (high-impedance) state. |

| SCL | 52 | DI | I2C serial control clock input |

| SCLK | 55 | DI | Serial audio-data clock (shift clock). SCLK is the serial-audio-port input-data bit clock. |

| SDA | 53 | DIO | I2C serial control data interface input/output |

| SDIN | 54 | DI | Serial audio data input. SDIN supports three discrete (stereo) data formats. |

| SSTIMER | 16 | AI | Controls ramp time of OUT_x to minimize pop. Leave this pin floating for BD mode. Requires capacitor of 2.2 nF to GND in AD mode. The capacitor determines the ramp time. |

| STEST | 48 | DI | Factory test pin. Connect directly to DVSS. |

| VR_ANA | 10 | P | Internally regulated 1.8-V analog supply voltage. This pin must not be used to power external devices. |

| VR_DIG | 2 | P | Internally regulated 1.8-V digital supply voltage. This pin must not be used to power external devices. |

| VREG | 42 | P | Digital regulator output. Not to be used for powering external circuitry. |

| PowerPAD™ | P | Connect to GND for best system performance. If not connected to GND, leave floating. | |

(1) TYPE: A = analog; D = 3.3-V digital; P = power/ground/decoupling; I = input; O = output