SLVSDT4F October 2017 – December 2021 TPS2662

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Undervoltage Lockout (UVLO)

- 9.3.2 Overvoltage Protection (OVP)

- 9.3.3 Hot Plug-In and Inrush Current Control

- 9.3.4 Reverse Polarity Protection

- 9.3.5 Overload and Short-Circuit Protection

- 9.3.6 Reverse Current Protection

- 9.3.7 FAULT Response

- 9.3.8 IN, OUT, RTN, and GND Pins

- 9.3.9 Thermal Shutdown

- 9.4 Device Functional Modes

-

10Application and Implementation

- 10.1 Application Information

- 10.2 Typical Application

- 10.3 System Examples

- 10.4 Do's and Don'ts

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DRC|10

Thermal pad, mechanical data (Package|Pins)

- DRC|10

Orderable Information

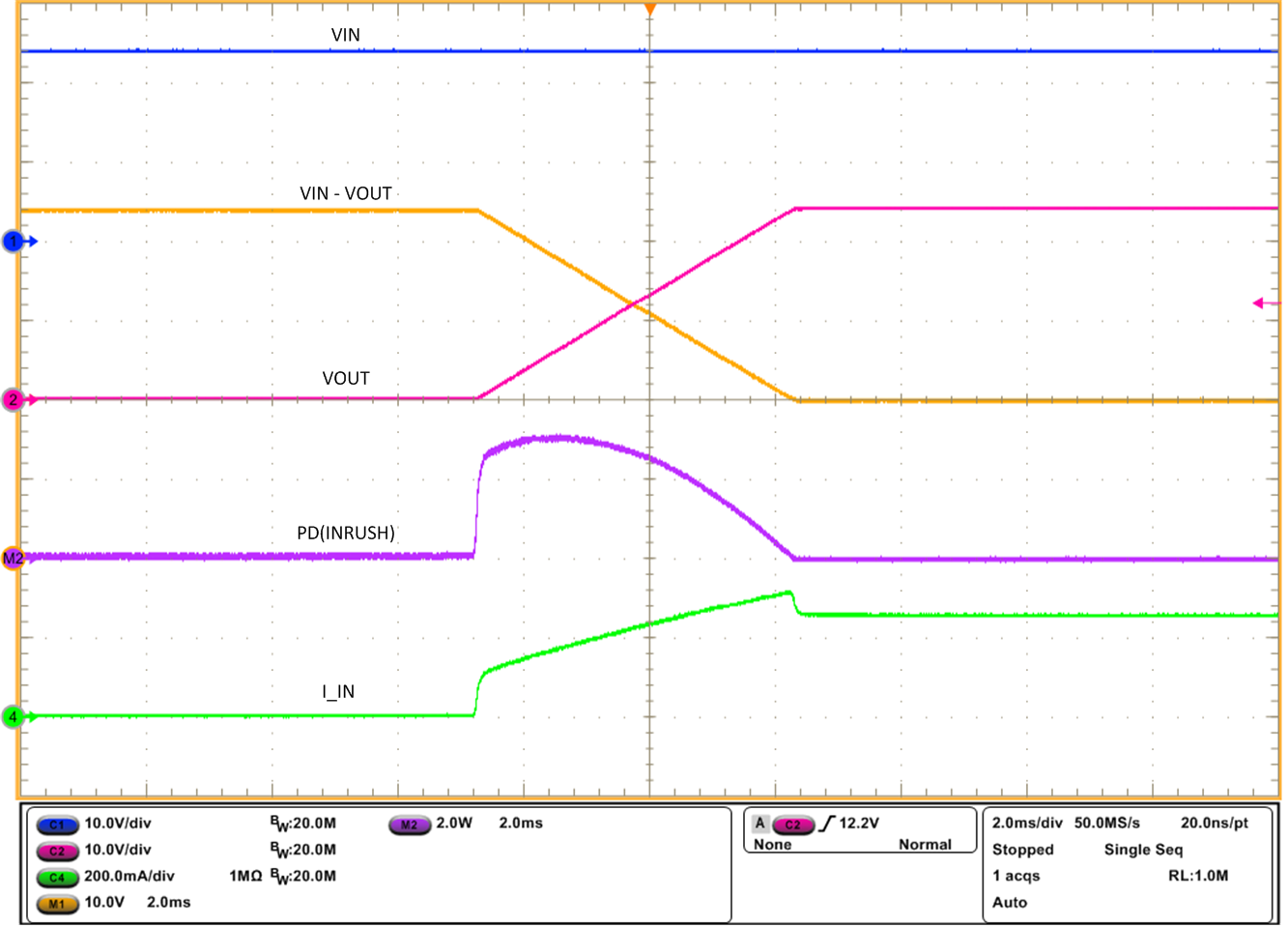

10.2.2.4.2 Case 2: Start-Up With Load —Output Capacitance C(OUT) and Load Draws Current During Start-Up

When the load draws current during the turn-on sequence, additional power is dissipated in the device. Considering a resistive load RL(SU) during start-up, typical ramp-up of output voltage, Figure 10-4 shows load current and the instantaneous power dissipation in the device. Figure 10-5 plots Instantaneous power dissipation with respect to time.

| VIN = 24 V | RL(SU) = 96 Ω | ||

| CdVdT = 10 nF | COUT = 22 µF | ||

| VIN = 24 V | RL(SU) = 96 Ω | ||

| CdVdT = 10 nF | COUT = 22 µF | ||

The additional power dissipation during start-up is calculated using Equation 10.

Total power dissipated in the device during start-up is given by Equation 11.

Total current during start-up is given by Equation 12.

For the design example under discussion,

Select the inrush current I(INRUSH) = 0.1 A and tdVdT calculated using Equation 8 is 5.28 ms.

For a given start-up time, CdVdT capacitance value calculated using Equation 2 is 10.7 nF for tdVdT = 5.28 ms and VIN = 24 V.

Choose the closest standard value: 10.0 nF and 16-V capacitor.

The inrush power dissipation due to output capacitor alone is calculated using Equation 9 and it is 1.2 W. Considering the start-up with 96-Ω load, the additional power dissipation calculated using Equation 10 is 1 W. The total device power dissipation during start-up is 2.2 W

The power dissipation with or without load, for a selected start-up time must not exceed the thermal shutdown limits as shown in Figure 10-6.

From the thermal shutdown limit graph, at TA = 125°C, thermal shutdown time for 2.2 W is close to 580 ms. It is safe to have a minimum 30% margin to allow for variation of the system parameters such as load, component tolerance, input voltage and layout. Selected 10-nF CdVdT capacitor and 5.28-ms start-up time (tdVdT) are well within the limit for successful start-up with 96-Ω load.

Higher value C(dVdT) capacitor can be selected to further reduce the power dissipation during start-up.

Figure 10-6 Thermal Shutdown Time vs Power Dissipation

Figure 10-6 Thermal Shutdown Time vs Power Dissipation