SLVSCB6E November 2013 – December 2017 TPS56520 , TPS56720 , TPS56920 , TPS56C20

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (Continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- PWP|20

Thermal pad, mechanical data (Package|Pins)

- PWP|20

Orderable Information

9 Applications and Implementation

9.1 Application Information

The devices are synchronous step down DC-DC converters rated at different output currents whose output voltage can be dynamically scaled by sending commands over an I2C interface. The section below discusses the design of the external components to complete the power supply design by using a typical application as a reference

9.2 Typical Application

9.2.1 TPS56520, TPS56720 and TPS56920, 5-A, 7-A, and 9-A Converter

Figure 31. Typical Application Schematic – TPS56520, TPS56720 and TPS56920

Figure 31. Typical Application Schematic – TPS56520, TPS56720 and TPS56920

9.2.1.1 Design Requirements

To begin the design process, the user must know a few application parameters:

- Input voltage range

- Output voltage

- Output current

- Output voltage ripple

- Input voltage ripple

Table 4. Design Example

| DESIGN PARAMETER | EXAMPLE VALUE |

|---|---|

| Input voltage range | 4.5V to 17V |

| Output voltage | 1.1V |

| Transient response, 3A-9A load step | ΔVOUT = ±5% |

| Output voltage ripple | 25mV |

| Input ripple voltage | 400mA |

| Output current rating | 12A |

| Operating Frequency | 500kHz |

9.2.1.2 Detailed Design Procedure

9.2.1.2.1 Output Voltage Resistors Selection

The output voltage is set with a resistor divider from the output node to the VFB terminal. It is recommended to use 1% tolerance or better divider resistors. Start by using Equation 3 to calculate VOUT.

To improve efficiency at light loads consider using larger value resistors, high resistance is more susceptible to noise, and the voltage errors from the VFB input current are more noticeable.

9.2.1.2.1.1 Output Filter Selection

The output filter used with the TPS56X20 is an LC circuit. This LC filter has double pole at:

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal gain of the TPS56X20. The low frequency phase is 180 degrees. At the output filter pole frequency, the gain rolls off at a –40 dB per decade rate and the phase drops rapidly. D-CAP2™ introduces a high frequency zero that reduces the gain roll off to –20 dB per decade and increases the phase to 90 degrees one decade above the zero frequency. The inductor and capacitor selected for the output filter must be selected so that the double pole of Equation 4 is located below the high frequency zero but close enough that the phase boost provided be the high frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the values recommended in Table 5.

Table 5. Recommended Component Values

| Output Voltage (V) | R5 (kΩ) | R6 (kΩ) | C8 (pF)(1) | L1 (µH) | C7 (µF) |

|---|---|---|---|---|---|

| 1 | 14.7 | 22 | DNP | 1.0-2.2 | 44-100 |

| 1.1 | 18.2 | 22 | DNP | 1.0-2.2 | 44-100 |

| 1.2 | 22 | 22 | DNP | 1.0-2.2 | 44-100 |

| 1.5 | 33 | 22 | DNP | 1.0-2.2 | 44-100 |

| 1.8 | 44.2 | 22 | DNP | 1.0-2.2 | 44-100 |

For higher output voltages additional phase boost can be achieved by adding a feed forward capacitor (C6) in parallel with R5.

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 5, Equation 6 and Equation 7. The inductor saturation current rating must be greater than the calculated peak current and the RMS or heating current rating must be greater than the calculated RMS current. Use 500 kHz for fSW.

Use 500 kHz for fSW. Make sure the chosen inductor is rated for the peak current of Equation 6 and the RMS current of Equation 7.

The capacitor value and ESR determines the amount of output voltage ripple. The TPS56X20 is intended for use with ceramic or other low ESR capacitors. Recommended values range from 44µF to 100µF. Use Equation 8 to determine the required RMS current rating for the output capacitor.

9.2.1.2.2 Input Capacitor Selection

The TPS56X20 requires an input decoupling capacitor and a bulk capacitor depending on the application. A ceramic capacitor of 20µF or above is recommended for the decoupling capacitors from PVIN to PGND. Additionally, a 4.7 µF ceramic capacitor from VIN to GND is also recommended. The capacitors voltage rating needs to be greater than the maximum input voltage.

9.2.1.2.3 Bootstrap Capacitor Selection

The 0.1 µF ceramic capacitors must be connected between the VBST to SW terminals for proper operation. It is recommended to use ceramic capacitors with a dielectric of X5R or better.

9.2.1.2.4 VREG5 Capacitor Selection

For the TPS56920/720/520, a 2.2 µF ceramic capacitor must be connected between the VREG5 to GND terminals for proper operation.

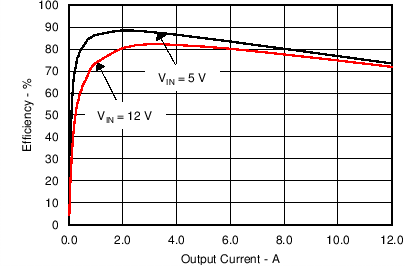

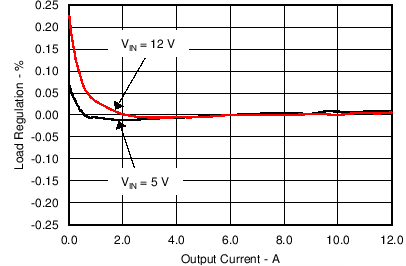

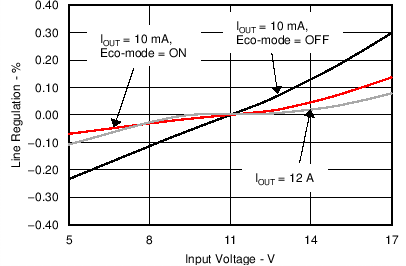

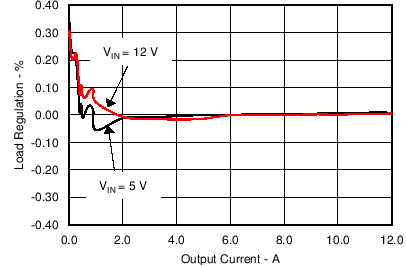

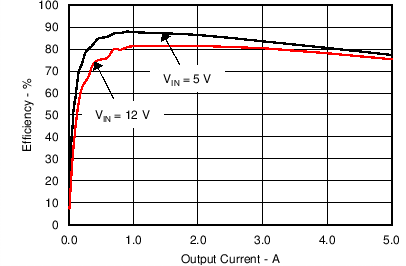

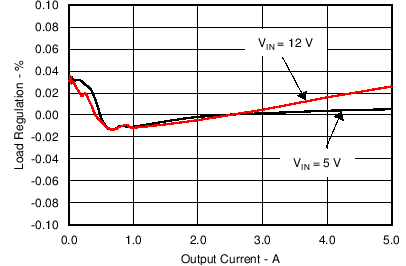

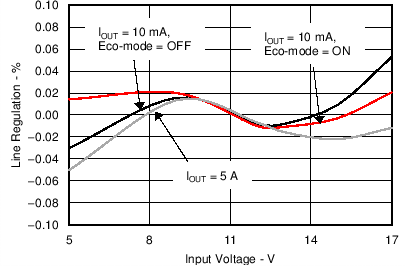

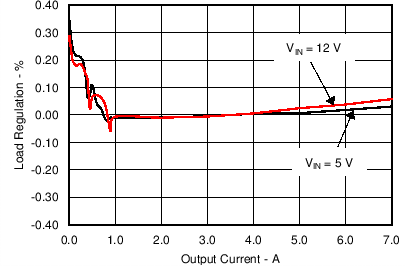

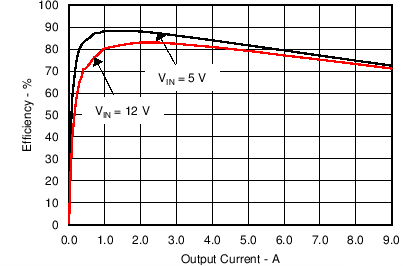

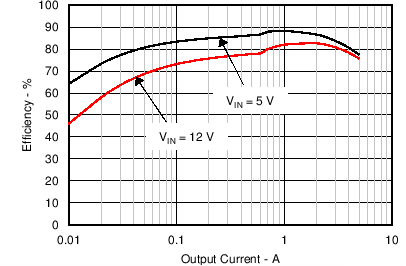

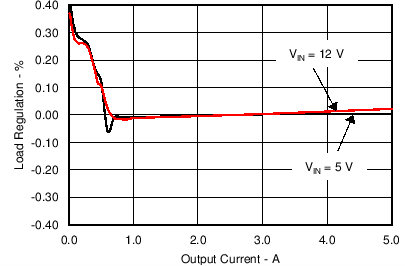

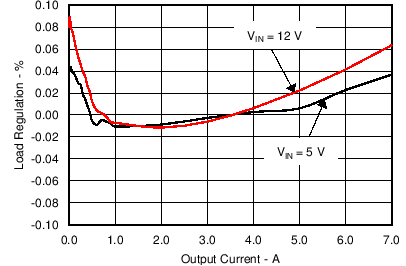

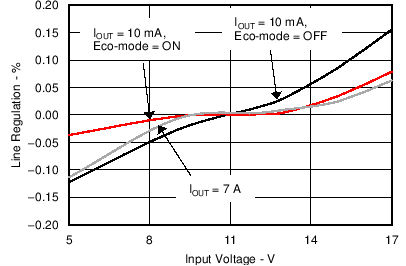

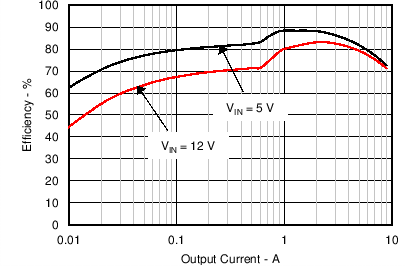

9.2.2 TPS56520, TPS56720 and TPS56920 Application Performance Curves

VIN = 12 V, VOUT = 1.0 V, Ta = 25 °C, unless otherwise specified.

9.2.3 TPS56C20 12-A Converter

Figure 51. Typical Schematic – TPS56C20

Figure 51. Typical Schematic – TPS56C20

9.2.3.1 Design Requirements

To begin the design process, the user must know a few application parameters:

- Input voltage range

- Output voltage

- Output current

- Output voltage ripple

- Input voltage ripple

9.2.3.2 Design Procedure

Follow the design procedure for the TPS56X20 converter listed above. For the TPS56C20, a 3.3 µF ceramic capacitor must be connected between the VREG5 to GND terminals for proper operation. Do not load the VREG5 terminal with any other load. It is recommended to use a ceramic capacitor with a dielectric of X5R or better.

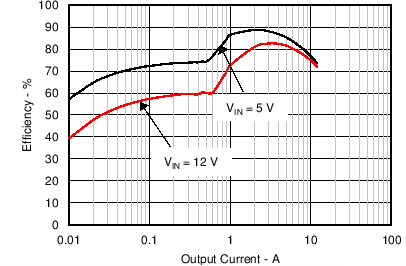

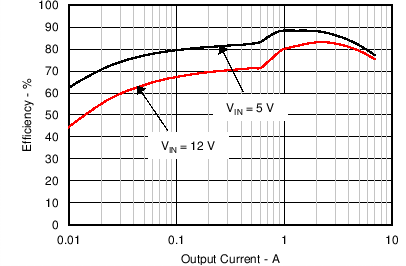

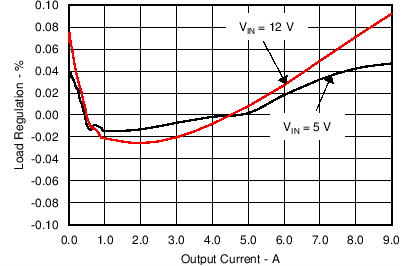

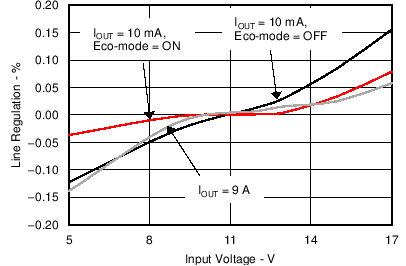

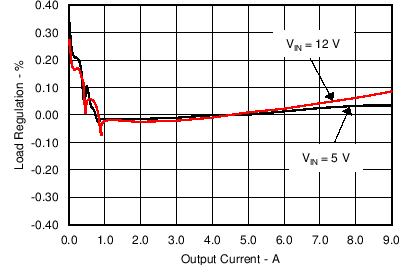

9.2.3.3 TPS56C20 Application Performance Curves

VIN = 12 V, VOUT = 1.0 V, Ta = 25 °C, unless otherwise specified.