SLVSBM1H June 2013 – November 2016 TPS65132

UNLESS OTHERWISE NOTED, this document contains PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

Low-current Applications (≤ 40 mA)

- 9.2.1.1 Design Requirements

- 9.2.1.2 Detailed Design Procedure

- 9.2.1.3 Application Curves

- 9.2.2

Mid-current Applications (≤ 80 mA)

- 9.2.2.1 Design Requirements

- 9.2.2.2 Detailed Design Procedure

- 9.2.2.3 Application Curves

- 9.2.3 High-current Applications (≤ 150 mA)

- 9.2.1

Low-current Applications (≤ 40 mA)

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

1 Features

- Input Voltage Range: 2.5 V to 5.5 V

- VPOS Boost Converter:

4 V to 6 V (0.1-V step) - VNEG Inverting Buck-Boost Converter:

–6 V to –4 V (0.1-V step) - Maximum Output Current:

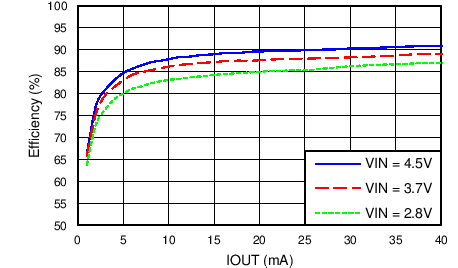

80 mA or 150 mA - Outstanding Combined Efficiency

- > 85% at IOUT > 10 mA

- > 90% at IOUT > 40 mA

- Excellent Performance

- Outstanding Transient Response

- 1% Output Voltage Accuracy over

Full Temperature Range

- I2C Interface

- Programmable Power-Up / -Down

Sequencing Options - Flexible Output Voltage Programming

- Programmable Active Output Discharge

- > 1000x Programmable Non-Volatile Memory

- Programmable Power-Up / -Down

- Under-Voltage Lock-Out and Thermal Protection

- Two Package Options

- 15-Ball CSP Package

- 20-Pins QFN Package

2 Applications

- Small-, Medium-Size Bipolar LCD Displays

- Smartphone, Tablet

- Camera, GPS

- Home Automation, Point-of-Sales

- Wearables (Smart Watch, Activity Tracker)

- General Split-Rail Power Supply

- Differential Audio, Headphone Amplifier

- Instrumentation, Operational Amplifier, Comparator

- DAC / ADC

3 Description

The TPS65132 family is designed to supply positive/negative driven applications. The device uses a single inductor scheme for both outputs to provide the user smallest solution size, a small bill-of-material as well as high efficiency. The devices offer best line and load regulation at low noise. With its input voltage range of 2.5 V to 5.5 V, it is optimized for products powered by single-cell batteries (Li-Ion, Ni-Li, Li-Polymer) and fixed 3.3-V and 5-V rails. The TPS656132 family provides 80 mA and 150 mA output current options with programmability to 40 mA. There are both CSP and QFN package options available.

Device Information (1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM.) |

|---|---|---|

| TPS65132 -B, -L, -T, -S |

DSBGA (15) | 2.11 mm × 1.51 mm |

| TPS65132W | WQFN (20) | 4.00 mm × 3.00 mm |

- For all available packages, see the orderable addendum at the end of the datasheet.

space

space

Typical Application

Efficiency vs Output Current