SNAS304H January 2006 – April 2016 ADC121S101 , ADC121S101-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBV|6

Thermal pad, mechanical data (Package|Pins)

Orderable Information

1 Features

2 Applications

- Portable Systems

- Remote Data Acquisition

- Instrumentation and Control Systems

- Automotive

3 Description

The ADC121S101 is a low-power, single-channel CMOS 12-bit analog-to-digital converter with a high-speed serial interface. Unlike the conventional practice of specifying performance at a single sample rate only, the ADC121S101 is fully specified over a sample rate range of 500 ksps to 1 Msps. The converter is based upon a successive-approximation register architecture with an internal track-and-hold circuit.

The output serial data is straight binary, and is compatible with several standards, such as SPI™, QSPI™, MICROWIRE, and many common DSP serial interfaces.

The ADC121S101 operates with a single supply with a range from 2.7 V to 5.25 V. Normal power consumption using a 3 V or 5 V supply is 2 mW and 10 mW, respectively. The power-down feature reduces the power consumption to as low as 2.6 µW using a 5-V supply.

The ADC121S101 is packaged in 6-pin WSON and SOT-23 packages. Operation over the temperature range of −40°C to 125°C is specified.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| ADC121S101 | WSON (6) | 2.50 mm × 2.20 mm |

| SOT-23 (6) | 2.90 mm × 1.60 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

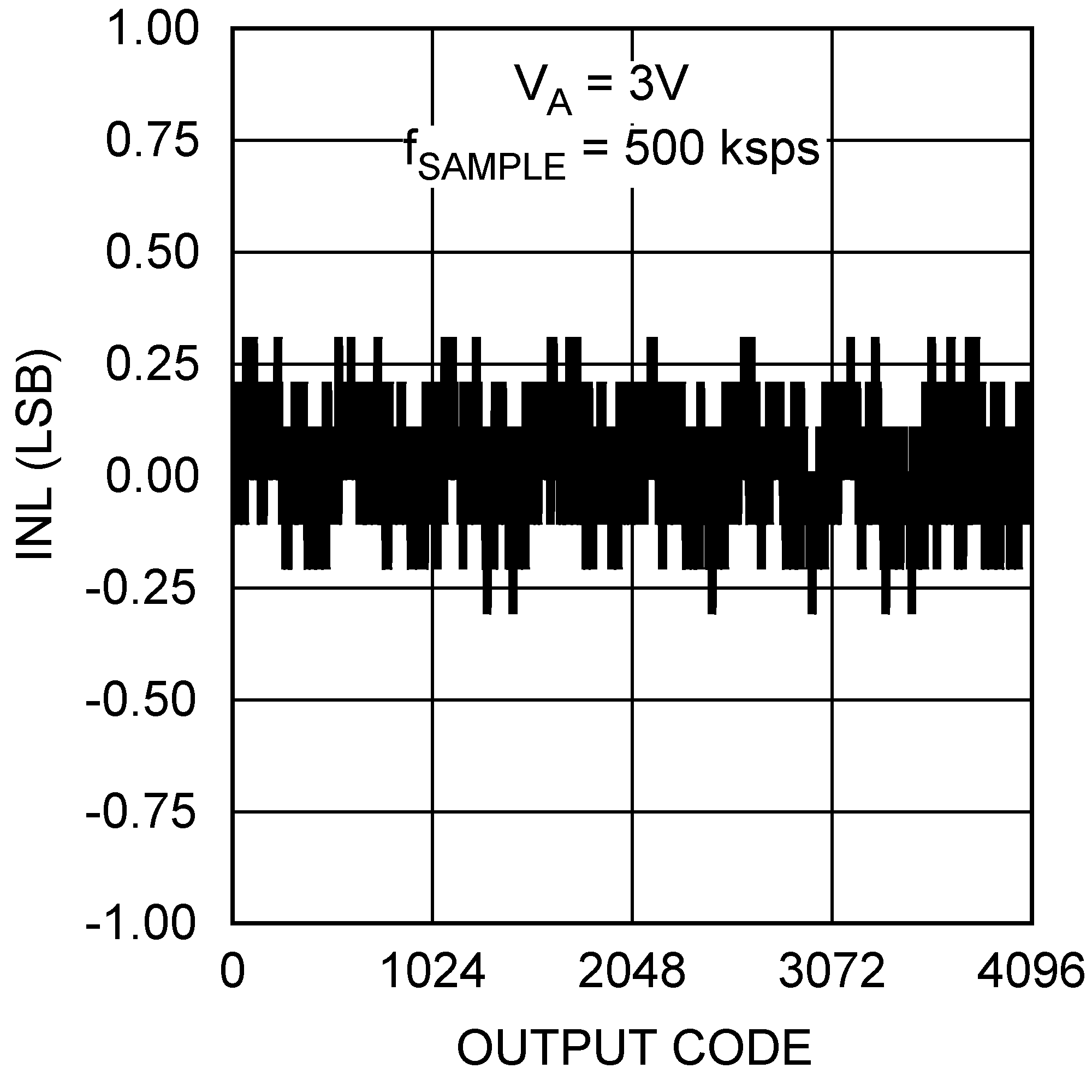

INL, fSCLK = 10 MHz