JAJSD75C August 2011 – February 2016 ADS8528 , ADS8548 , ADS8568

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: General

- 7.6 Electrical Characteristics: ADS8528

- 7.7 Electrical Characteristics: ADS8548

- 7.8 Electrical Characteristics: ADS8568

- 7.9 Serial Interface Timing Requirements

- 7.10 Parallel Interface Timing Requirements (Read Access)

- 7.11 Parallel Interface Timing Requirements (Write Access)

- 7.12 Typical Characteristics

- 8 Parameter Measurement information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- RGC|64

発注情報

1 特長

- 12、14、16ビットでピンおよびソフトウェア互換のADCファミリ

- チャネルごとの最大データ転送速度:

- ADS8528: 650kSPS (PAR)または

480kSPS (SER) - ADS8548: 600kSPS (PAR)または

450kSPS (SER) - ADS8568: 510kSPS (PAR)または

400kSPS (SER)

- ADS8528: 650kSPS (PAR)または

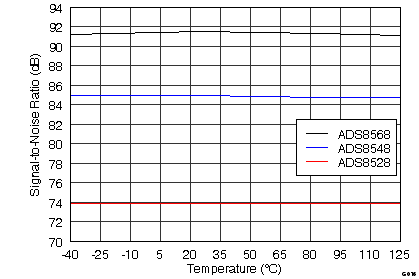

- 優れたAC特性

- 信号対雑音比:

ADS8528: 73.9dB、ADS8548: 85dB、ADS8568: 91.5dB - 全高調波歪み:

ADS8528: -89dB、ADS8548: -91dB、 ADS8568: -94dB

- 信号対雑音比:

- プログラム可能なバッファ付き内部基準電圧:

0.5V~2.5Vまたは0.5V~3.0Vで、±12Vまでの入力電圧範囲をサポート - パラレルまたはシリアルのインターフェイスを選択可能

- 自動スリープ・モードの使用によるスケーラブルな低消費電力動作: 10kSPSでわずか32mW

- 拡張工業用温度範囲にわたって完全に定格を規定

2 アプリケーション

- 保護リレー

- 電力品質測定

- 多軸モータ制御

- プログラマブル・ロジック・コントローラ

- 工業用データ収集

SNRと温度との関係

3 概要

ADS85x8は、低消費電力で12、14、16ビットの8つの逐次比較型(SAR)アナログ/デジタル・コンバータ(ADC)が搭載されており、真のバイポーラ入力を受け付けます。これらのチャネルは4つのペアにグループ化されているため、最大650kSPSの高速な信号を同時に取得できます。

これらのデバイスはパラレルまたはシリアルのインターフェイスを選択でき、デイジー・チェーン機能に対応します。基準電圧をプログラム可能なため、最大±12Vの振幅でアナログ入力信号を処理できます。

ADS85x8ファミリは自動スリープ・モードをサポートして消費電力を最小限に抑えており、64ピンのVQFNおよびLQFPパッケージで供給されます。ファミリのすべての製品は、-40℃~+125℃の温度範囲で動作が規定されています。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| ADS85x8 | VQFN (64) | 9.00mm×9.00mm |

| LQFP (64) | 10.00mm×10.00mm |

- 提供されているすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

ブロック概略図

4 改訂履歴

Changes from B Revision (November 2015) to C Revision

Changes from A Revision (October 2011) to B Revision

- 「ESD定格」表、「推奨動作条件」表、「機能説明」セクション、「デバイスの機能モード」セクション、「レジスタ・マップ」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加Go

- Changed title of Device Comparison Table, deleted footnote 1 Go

- Added Storage temperature parameter to Absolute Maximum Ratings tableGo

- Changed Clock cycles per conversion to be a single parameter instead of part of tCONV parameter in Serial Interface Timing Requirements table Go

- Changed tBUFS parameter in Serial Interface Timing Requirements tableGo

- Added footnote 3 to Serial Interface Timing Requirements tableGo

- Changed Clock cycles per conversion to be a single parameter instead of part of tCONV parameter in Parallel Interface Timing Requirements (Read Access) table Go

- Changed tBUCS parameter in Parallel Interface Timing Requirements (Read Access) table Go

- Added footnote 3 to Parallel Interface Timing Requirements (Read Access) table Go

- Changed Data Readout and BUSY/INT Signal sectionGo

- Added Sequential Operation sectionGo

- Changed description of initiating a new conversion in Reset and Power-Down Modes sectionGo

Changes from * Revision (August 2011) to A Revision