JAJSUJ6 May 2024 AWRL6432AOP

ADVANCE INFORMATION

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 機能ブロック図

- 5 デバイスの比較

- 6 端子構成および機能

-

7 仕様

- 7.1 絶対最大定格

- 7.2 ESD 定格

- 7.3 電源投入時間 (POH)

- 7.4 推奨動作条件

- 7.5 ワンタイム プログラマブル (OTP) eFuse の VPP 仕様

- 7.6 電源仕様

- 7.7 パワー セーブ モード

- 7.8 電圧レールごとのピーク電流要件

- 7.9 サポート対象 DFE 機能

- 7.10 RF 仕様

- 7.11 CPU の仕様

- 7.12 熱抵抗特性

- 7.13 アンテナ放射パターン

- 7.14 アンテナ位置

- 7.15

タイミングおよびスイッチング特性

- 7.15.1 電源シーケンスおよびリセット タイミング

- 7.15.2 同期フレーム トリガ

- 7.15.3 入力クロックおよび発振器

- 7.15.4 マルチチャネル バッファ付き / 標準シリアル ペリフェラル インターフェイス (McSPI)

- 7.15.5 RDIF インターフェイスの構成

- 7.15.6 LIN

- 7.15.7 汎用入出力 (General-Purpose Input/Output)

- 7.15.8 CAN-FD (Controller Area Network - Flexible Data-rate)

- 7.15.9 シリアル通信インターフェイス (SCI)

- 7.15.10 I2C (Inter-Integrated Circuit Interface)

- 7.15.11 クワッド シリアル ペリフェラル インターフェイス (QSPI)

- 7.15.12 JTAG インターフェイス

- 8 詳細説明

- 9 監視と診断

- 10アプリケーション、実装、およびレイアウト

- 11デバイスおよびドキュメントのサポート

- 12改訂履歴

- 13メカニカル、パッケージ、および注文情報

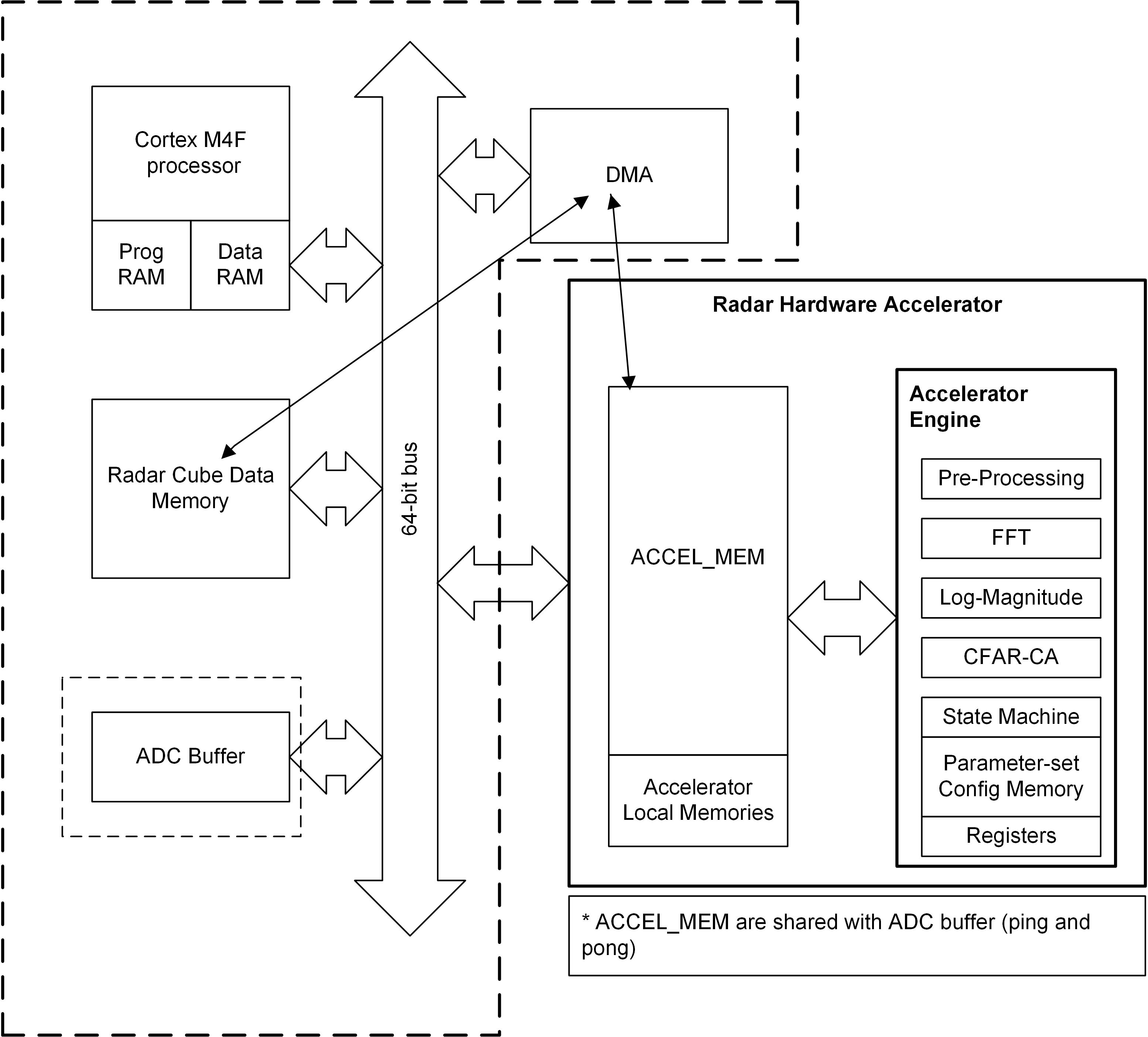

8.3.9 ハードウェア アクセラレータ (HWA1.2) の特長

- 高速 FFT の計算は、サイズがプログラマブル (2N) で、最大 1024 ポイントの複素 FFT

- 24 ビットの内部 FFT ビット幅 (I と Q のそれぞれ) により、優れた信号対量子化雑音比 (SQNR) 性能を実現

- radix-2 の段ごとに完全にプログラマブルなバタフライ スケーリングにより、ユーザーのフレキシビリティを向上

- FFT 前処理機能を内蔵 – 例:DC の推定と減算

- DC の推定 & 減算、干渉の推定 & ゼロ設定、実数ウィンドウ、複素前方乗算

- 振幅 (絶対値) と対数振幅の計算

- フレキシブルなデータ フローとデータ サンプルの調整機能により、効率的な多次元 FFT 演算と転置アクセス

- メイン プロセッサからの干渉を最小限に抑えながら一連の演算を 1 つずつ実行するチェーン化およびループ化機能

- ピーク検出 – CFAR (CFAR-CA、CFAR-OS) 検出器

- Sum と 1D Max を含む基本的な統計値

- レーダー キューブ メモリを最適化するための圧縮エンジン

図 8-5 HWA 1.2 の機能ブロック図

図 8-5 HWA 1.2 の機能ブロック図