JAJSQV7 july 2023 BQ25173-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

7.3.2 Supercapacitor Regulation Voltage

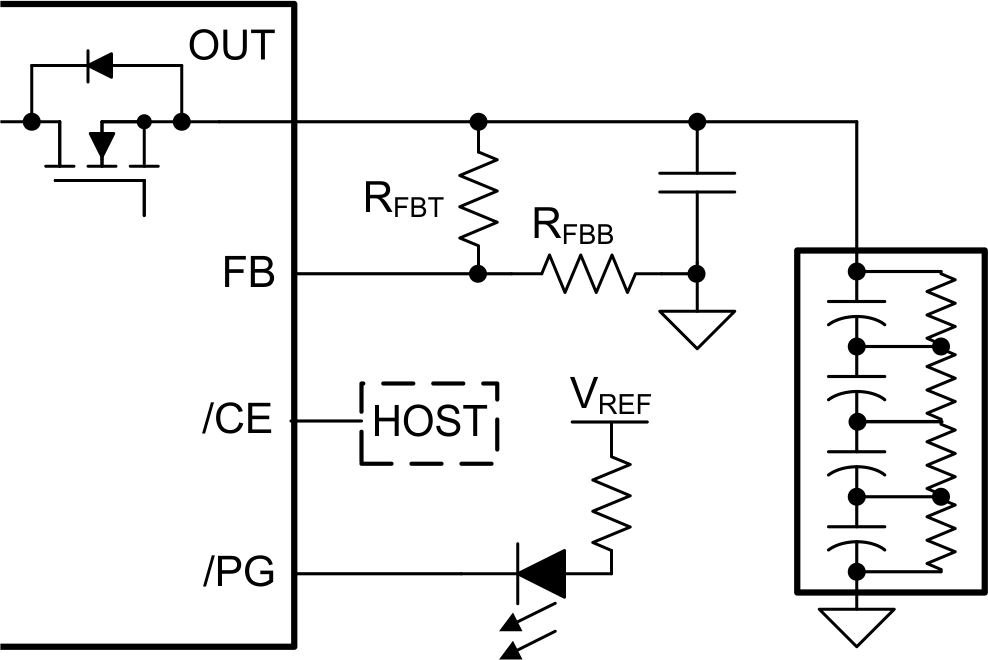

The device allows for the supercapacitor regulation voltage, VREG, to be programmed with a resistor divider between the OUT and FB pins:

Equation 2.

Where VFB_REF is listed in the electrical characteristcs table. The resistors can be seen in Figure 7-2. The total resistance (RFBT + RFBB) should not exceed 1 MΩ.

Figure 7-2 BQ25173-Q1 Feedback Divider

Figure 7-2 BQ25173-Q1 Feedback Divider