JAJSKU9B December 2022 – February 2024 BQ25628 , BQ25629

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 概要 (続き)

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Power-On-Reset (POR)

- 8.3.2 Device Power Up from Battery

- 8.3.3 Device Power Up from Input Source

- 8.3.4 Power Path Management

- 8.3.5 Battery Charging Management

- 8.3.6 USB On-The-Go (OTG)

- 8.3.7 Integrated 12-Bit ADC for Monitoring

- 8.3.8 Status Outputs ( STAT, INT)

- 8.3.9 BATFET Control

- 8.3.10 Protections

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Revision History

- 14Mechanical, Packaging, and Orderable Information

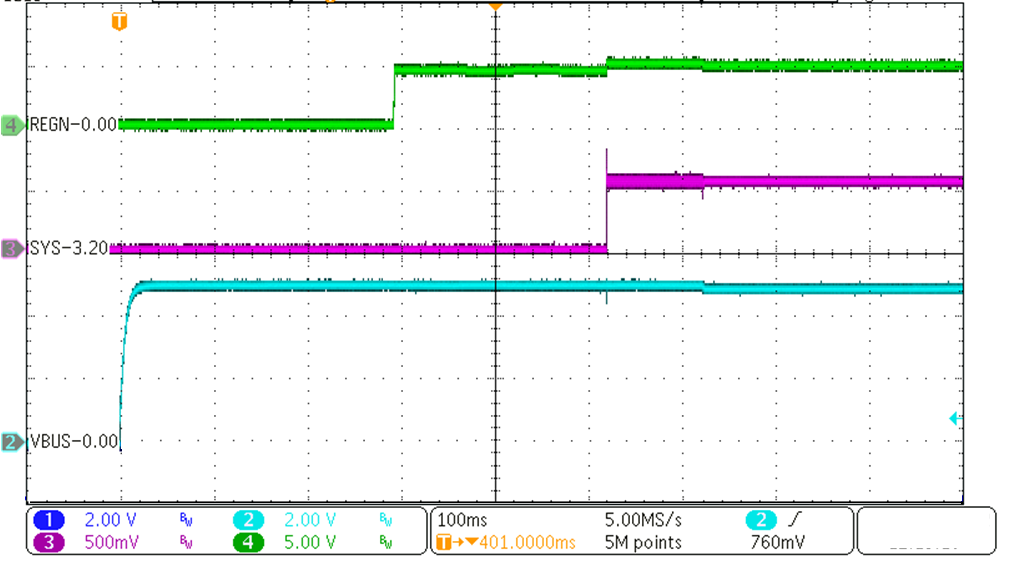

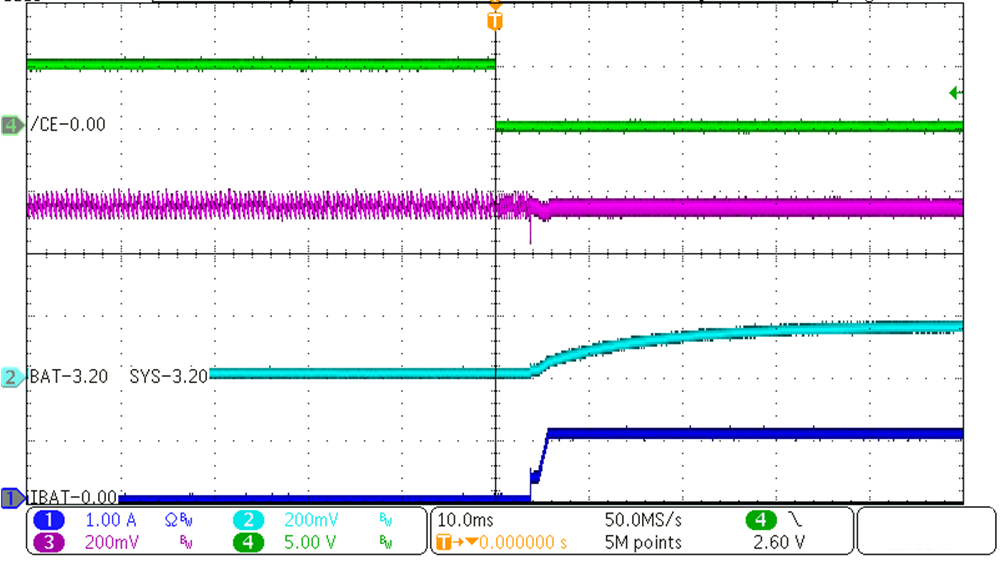

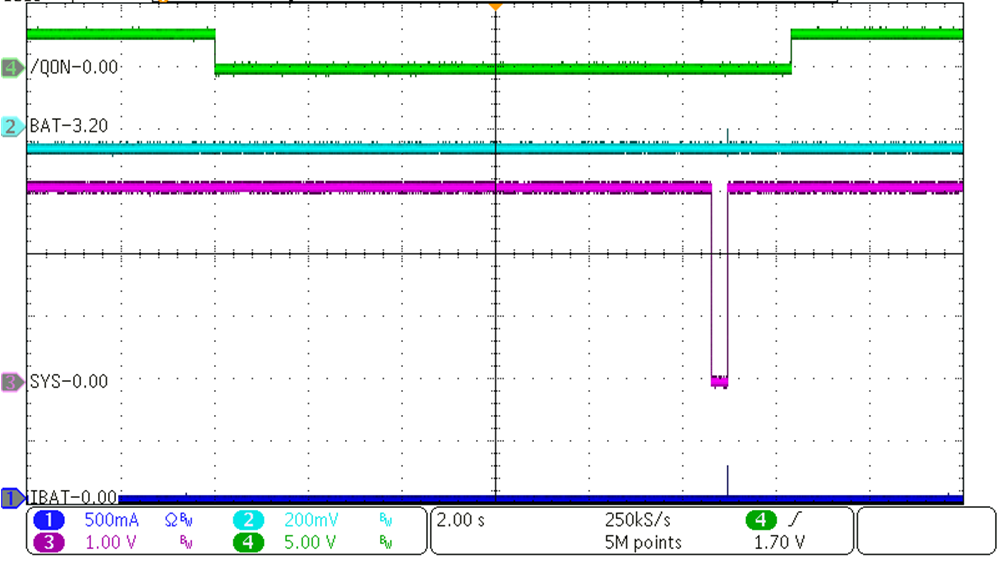

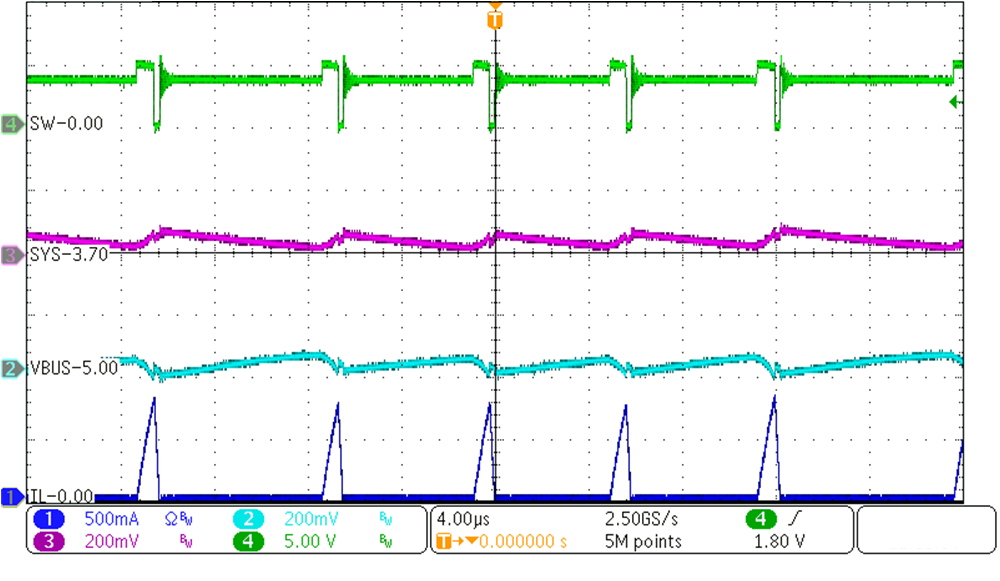

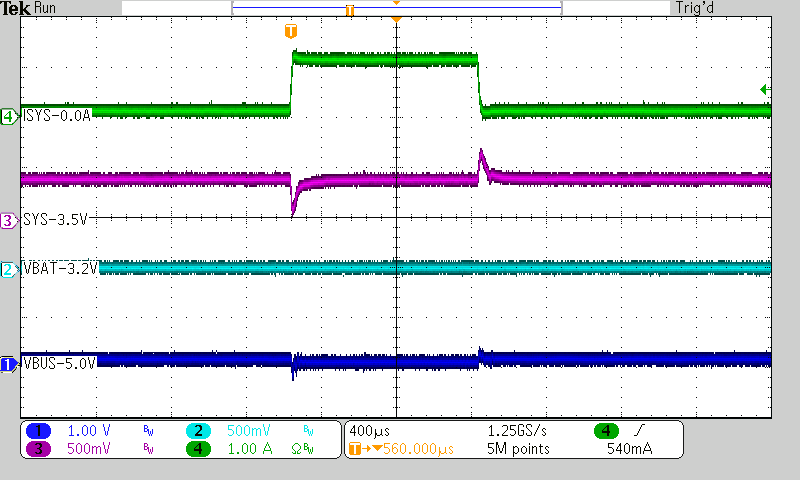

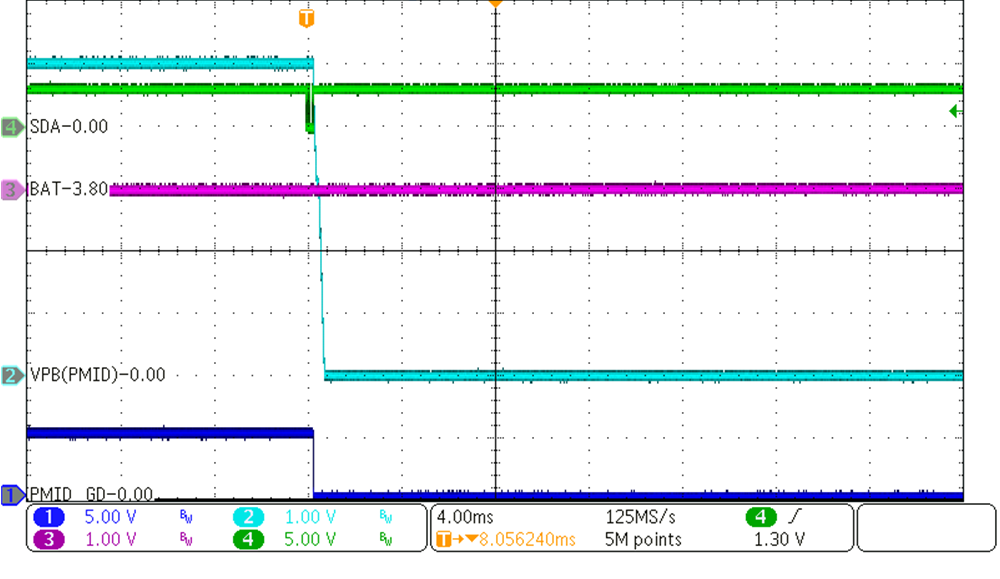

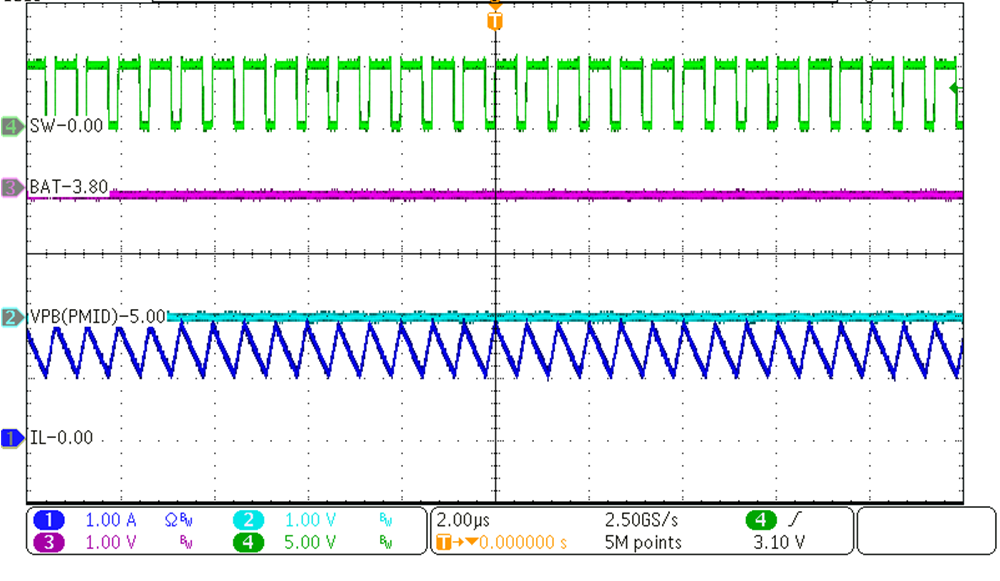

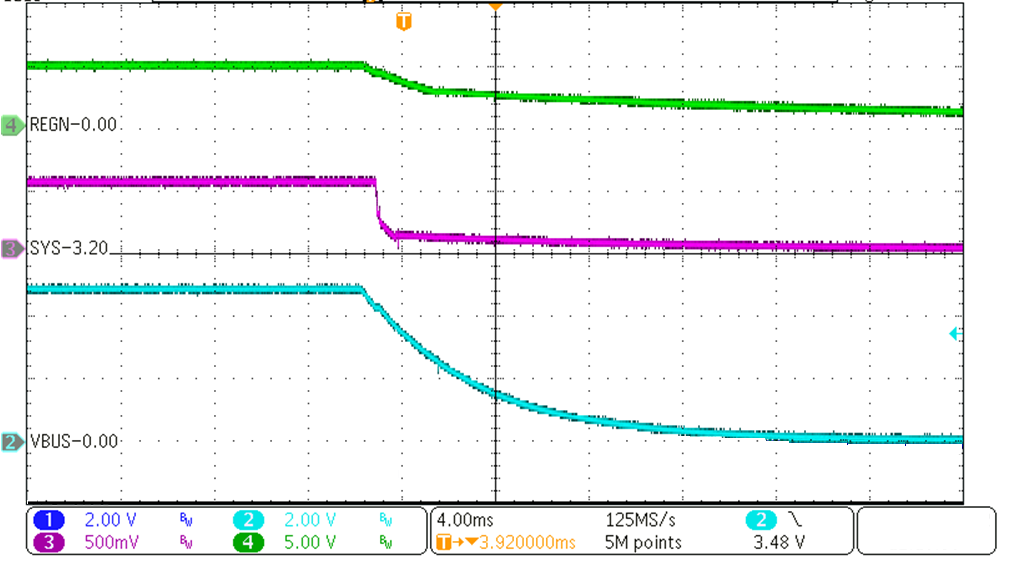

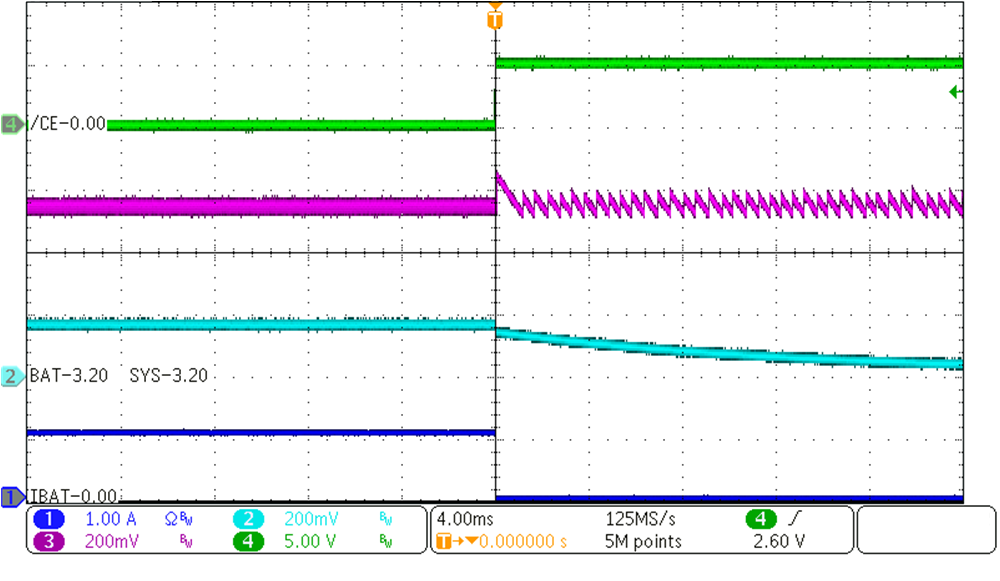

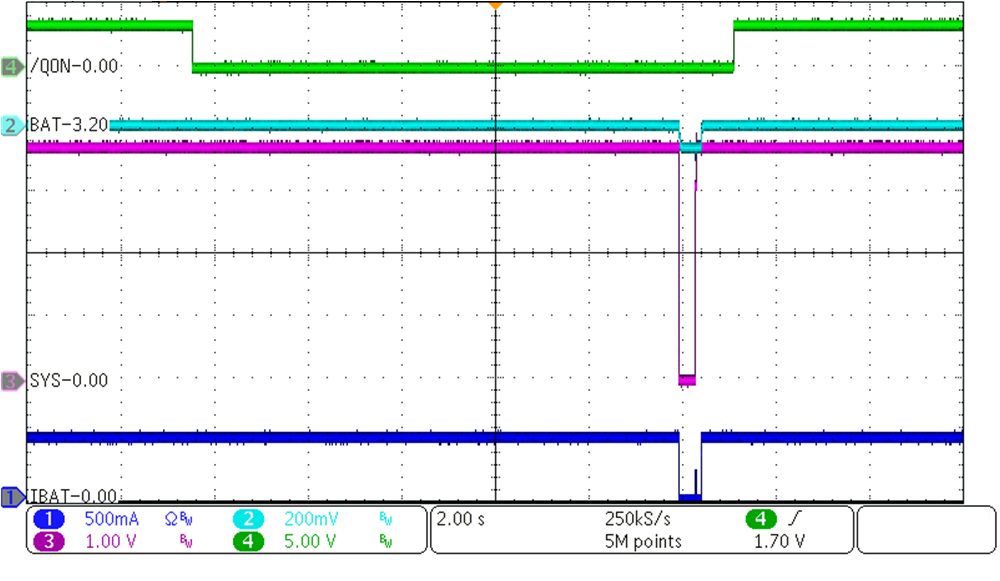

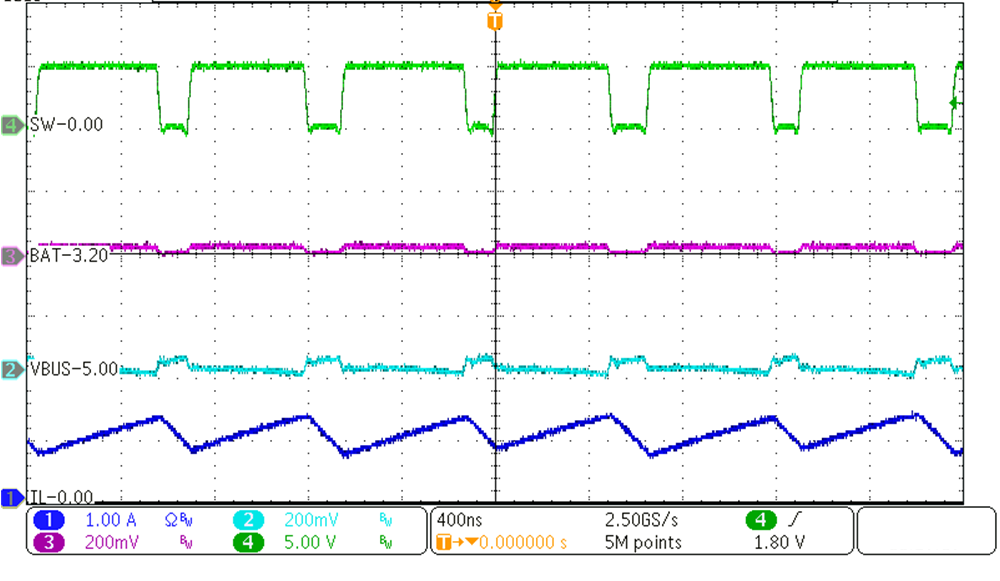

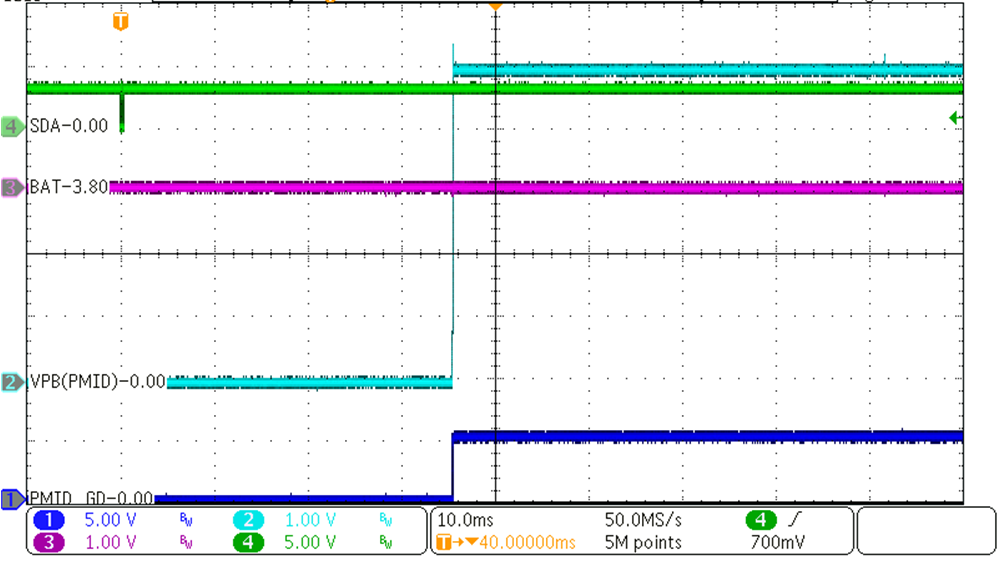

9.2.3 Application Curves

| VVBUS = 5 V | VBAT = 3.2 V |

| ICHG = 1 A |

| VVBUS = 5 V | VBAT = 3.2 V |

| ICHG = 1 A |

| VBAT = 3.2 V | |

| VVBUS = 5 V | VBAT = 3.2 V |

| ISYS = 50 mA | Charge Disabled |

| VVBUS = 5 V | VBAT = 3.2 V | |

| ISYS from 0 A to 1 A | Charge Disabled |

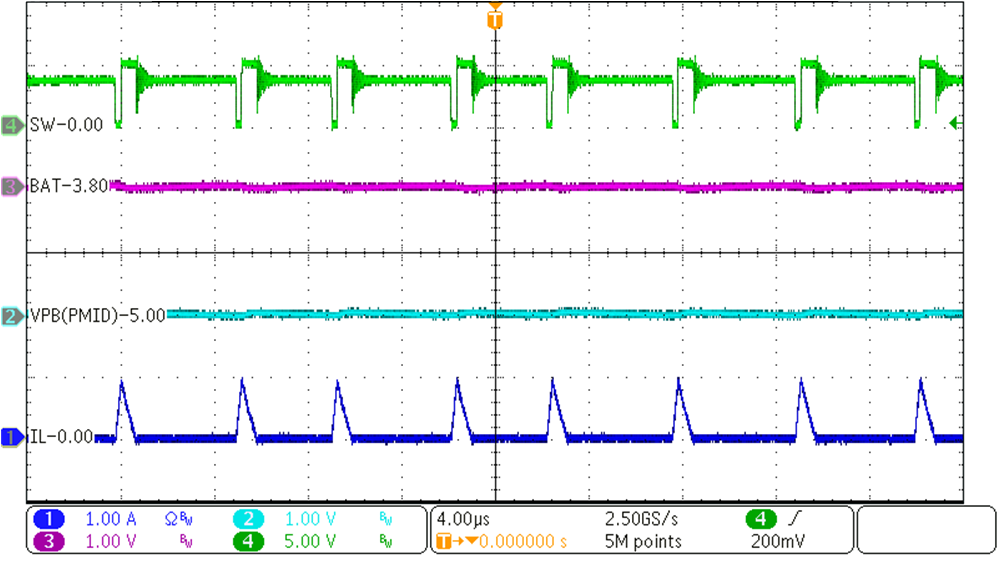

| VBAT = 3.8 V | VBOOST = 5.04V |

| IBOOST = 100 mA |

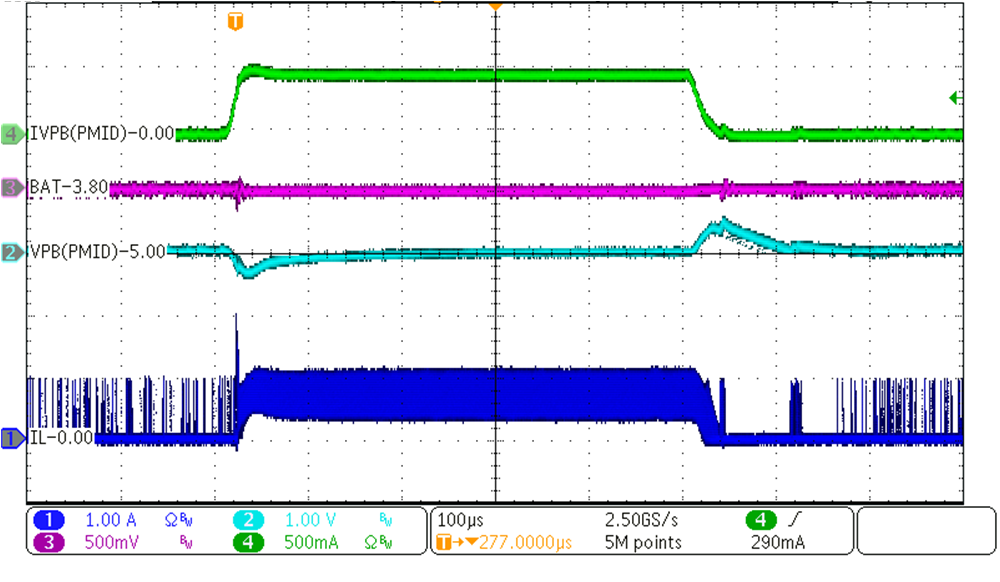

| VBAT = 3.8 V | VBOOST = 5.04V |

| IBOOST= 1 A |

| VVBUS = 5 V | VBAT = 3.2 V |

| ICHG = 1 A |

| VVBUS = 5 V | VBAT = 3.2 V |

| ICHG = 1 A |

| VVBUS = 5 V | VBAT = 3.2 V |

| ICHG = 480mA |

| VVBUS = 5 V | VVBAT = 3.2 V |

| ICHG = 1 A |

| VBAT = 3.8 V | VBOOST = 5.04 V |

| IBOOST = 100 mA |

| VBAT = 3.8 V | VBOOST = 5.04V |

| IBOOST= 50 mA |

| VBAT = 3.8 V | VBOOST = 5.04 V |

| IBOOST from 5 mA to 500 mA |