-

CD74AC540、CDx4ACT54x、CDx4AC541 オクタル バッファ / ライン ドライバ、3 ステート JAJSUM2B December 1998 – May 2024 CD54AC541 , CD54ACT540 , CD54ACT541 , CD74AC540 , CD74AC541 , CD74ACT540 , CD74ACT541

PRODUCTION DATA

-

CD74AC540、CDx4ACT54x、CDx4AC541 オクタル バッファ / ライン ドライバ、3 ステート

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- J|20

サーマルパッド・メカニカル・データ

Data Sheet

CD74AC540、CDx4ACT54x、CDx4AC541 オクタル バッファ / ライン ドライバ、3 ステート

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- SCR ラッチアップ耐性の高い CMOS プロセスと回路設計

- 消費電力を大幅に低減した、バイポーラ FAST®/AS/S の速度

- 伝搬遅延時間の平衡化

- AC タイプは 1.5V~5.5V で動作し、バランスのとれたノイズ耐性を電源の 30% で実現。

- ±24mA 出力駆動電流

- 15 個の FAST® IC にファンアウト

- 50Ω 伝送ラインを駆動

. FAST® は Fairchild Semiconductor Corp. の登録商標です。

2 概要

CD54/74AC540、-541、および CD54/74ACT540、-541 は、RCA アドバンスト CMOS テクノロジを使用したオクタル バッファ / ライン ドライバです。CD54/74AC/ACT540 は、2 つのアクティブ Low 出力イネーブルを備えた反転 3 ステート バッファです。CD54/74AC/ACT541 は、2 つのアクティブ Low 出力イネーブルを備えた非反転 3 ステート バッファです。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| CD74AC540、CDx4ACT54x、CDx4AC541 | DW (SOIC、20) | 12.8mm × 10.3mm | 12.8mm × 7.5mm |

| DB (SSOP、20) | 7.2mm × 7.8mm | 7.2mm × 5.3mm | |

| N (PDIP、20) | 24.33mm × 9.4mm | 24.33mm × 6.35mm |

(1) 供給されているすべてのパッケージについては、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

機能ブロック図

機能ブロック図3 Pin Configuration and Functions

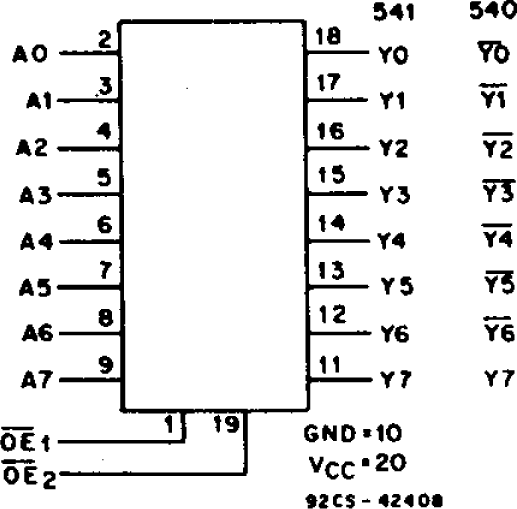

Figure 3-1 CDx4AC540,

CDx4ACT540

Figure 3-1 CDx4AC540,

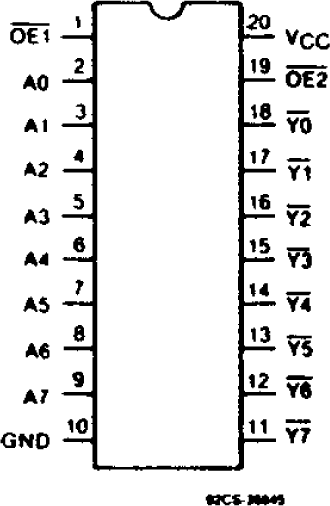

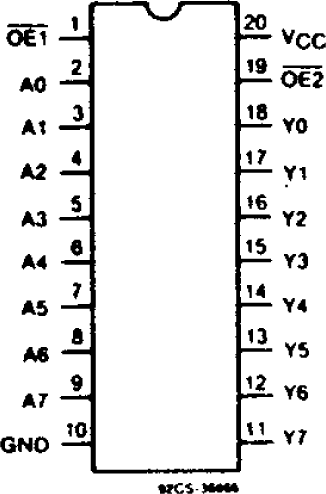

CDx4ACT540 Figure 3-2 CDx4AC541,

CDx4ACT541

Figure 3-2 CDx4AC541,

CDx4ACT541Table 3-1 Pin Functions

| PIN | |||

|---|---|---|---|

| NO. | NAME | I/O1 | DESCRIPTION |

| !MR | 1 | I | Master reset, active low |

| Q0 | 2 | O | Output Q0 |

| D0 | 3 | I | Input D0 |

| D1 | 4 | I | Input D1 |

| Q1 | 5 | O | Output Q1 |

| Q2 | 6 | O | Output Q2 |

| D2 | 7 | I | Input D2 |

| D3 | 8 | I | Input D3 |

| Q3 | 9 | O | Output Q3 |

| GND | 10 | - | Ground |

| CP | 11 | I | Clock, rising edge triggered |

| Q4 | 12 | O | Output Q4 |

| D4 | 13 | I | Input D4 |

| D5 | 14 | I | Input D5 |

| Q5 | 15 | O | Output Q5 |

| Q6 | 16 | O | Output Q6 |

| D6 | 17 | I | Input D6 |

| D7 | 18 | I | Input D7 |

| Q7 | 19 | O | Output Q7 |

| VCC | 20 | - | Supply |

- I = input, O = output, P = power, FB = feedback, GND = ground, N/A = not applicable

4 Specifications

4.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise

noted)

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| VCC | Supply voltage | −0.5 | 6 | V | |

| IIK | Input diode current | (VI < −0.5 or VI > VCC + 0.5 V) | ±20 | mA | |

| IOK | Output diode current | (VO < −0.5 or VO > VCC + 0.5 V) | ±50 | mA | |

| IO | Output source or sink current per output PIN | (VO > −0.5 or VO < VCC + 0.5 V) | ±50 | mA | |

| Vcc or ground current, ICC or IGND(1) | ±100 | mA | |||

| Tstg | Storage temperature | −65 | +150 | °C | |

(1) For up to 4 outputs per device: add ±25 mA for each additional output.

4.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-0011 | ±2000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe

manufacturing with a standard ESD control process.