JAJSU74B December 2003 – April 2024 CD74HC4051-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PW|16

- D|16

サーマルパッド・メカニカル・データ

発注情報

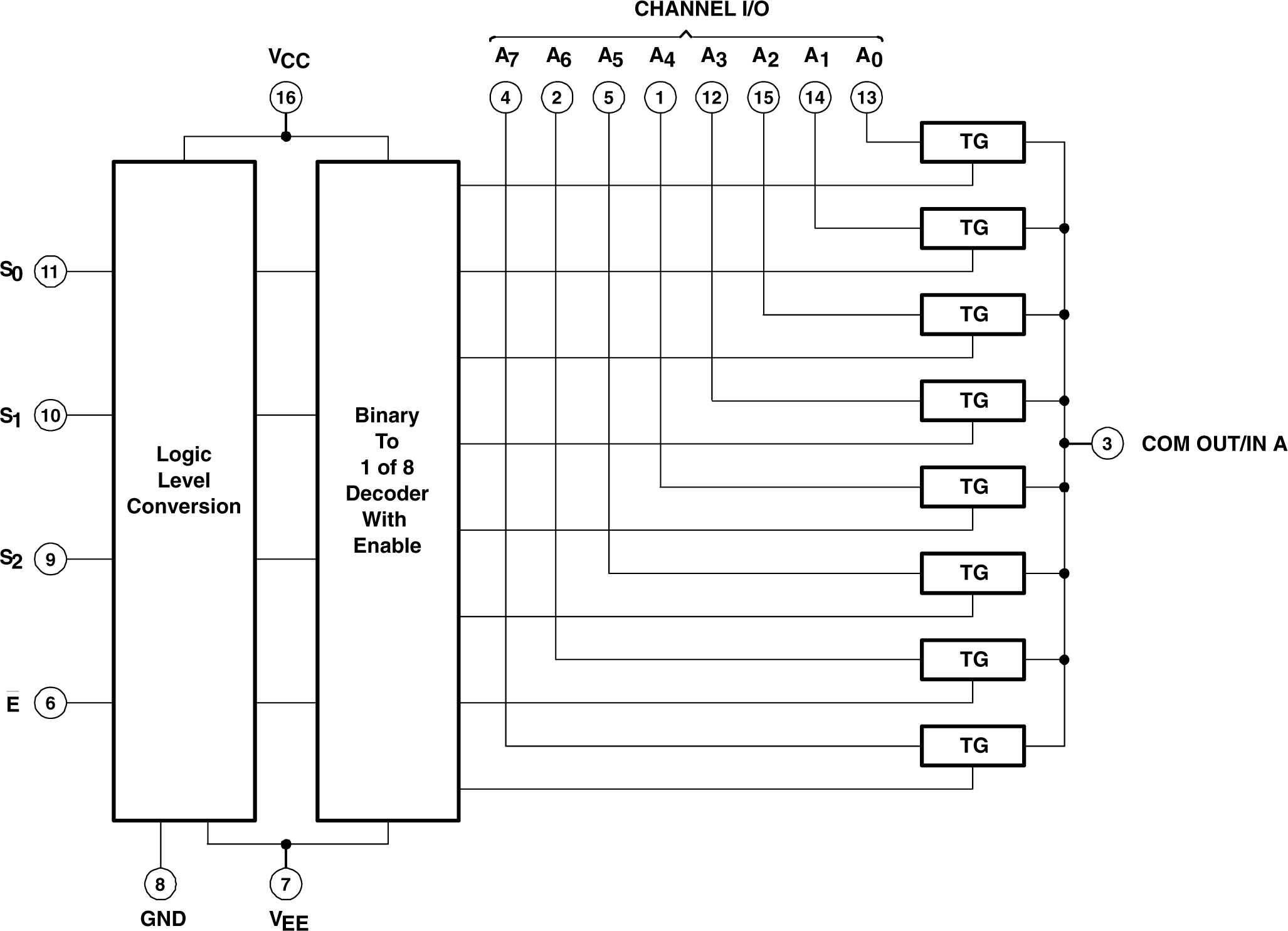

3 概要

このデバイスは、シリコン ゲート CMOS テクノロジを使って、標準 CMOS IC の低い消費電力で LSTTL と同様の動作速度を実現したデジタル制御アナログ スイッチです。

これらのアナログ マルチプレクサおよびデマルチプレクサは、電源電圧範囲にわたって変化する可能性があるアナログ電圧を制御します (例:VCC から VEE まで)。これらの双方向スイッチを使うと、任意のアナログ入力を出力として使用でき、その逆も行えます。スイッチはオン抵抗が低く、オフ時のリーク電流が小さい特長があります。また、本デバイスは、High のときにすべてのスイッチをオフ状態に無効化するイネーブル制御 (E) を備えています。

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

論理図 (正論理)

論理図 (正論理)