JAJSQN0 june 2023 CDCE6214Q1TM

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要 (続き)

- 6 デバイスの比較

- 7 ピン構成および機能

-

8 仕様

- 8.1 絶対最大定格

- 8.2 ESD 定格

- 8.3 推奨動作条件

- 8.4 熱に関する情報

- 8.5 EEPROM の特性

- 8.6 リファレンス入力、シングルエンド特性

- 8.7 リファレンス入力、差動特性

- 8.8 リファレンス入力、水晶振動子モードの特性

- 8.9 汎用入力特性

- 8.10 トリプル・レベル入力特性

- 8.11 ロジック出力特性

- 8.12 フェーズ・ロック・ループ特性

- 8.13 閉ループ出力ジッタの特性

- 8.14 入力および出力絶縁

- 8.15 バッファ・モードの特性

- 8.16 PCIe スペクトラム拡散ジェネレータ

- 8.17 LVCMOS 出力特性

- 8.18 LP-HCSL 出力特性

- 8.19 LVDS 出力特性

- 8.20 出力同期特性

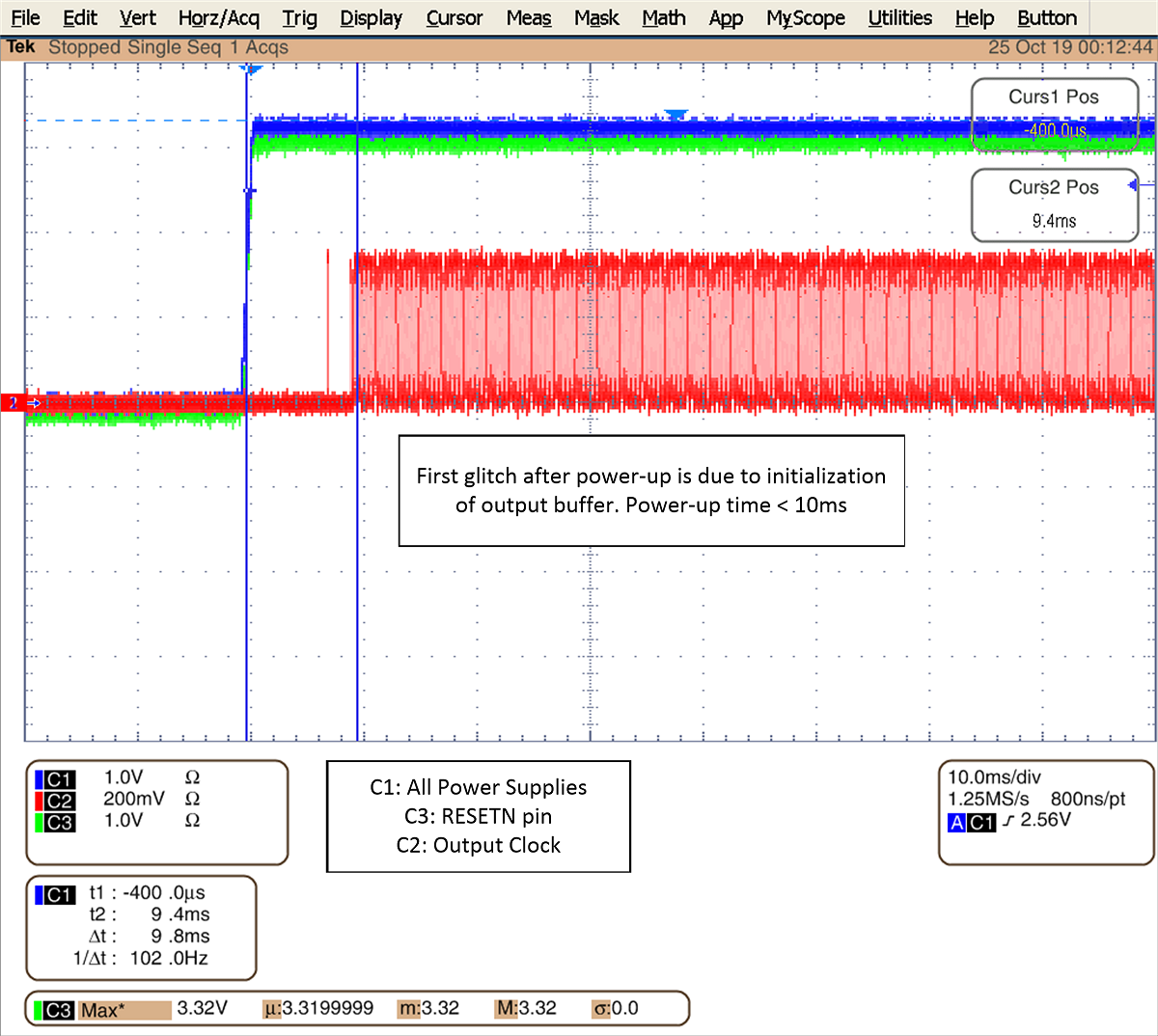

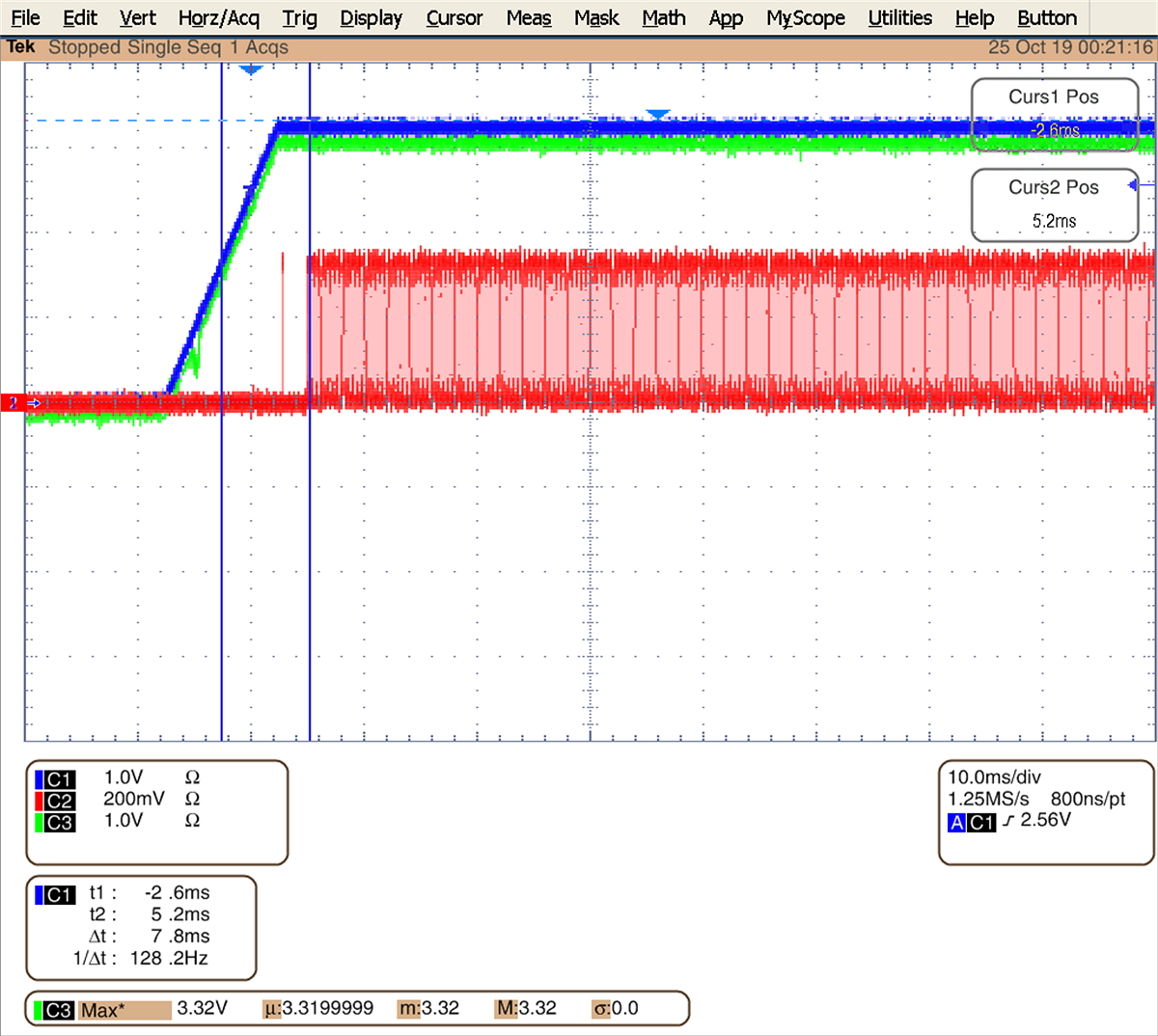

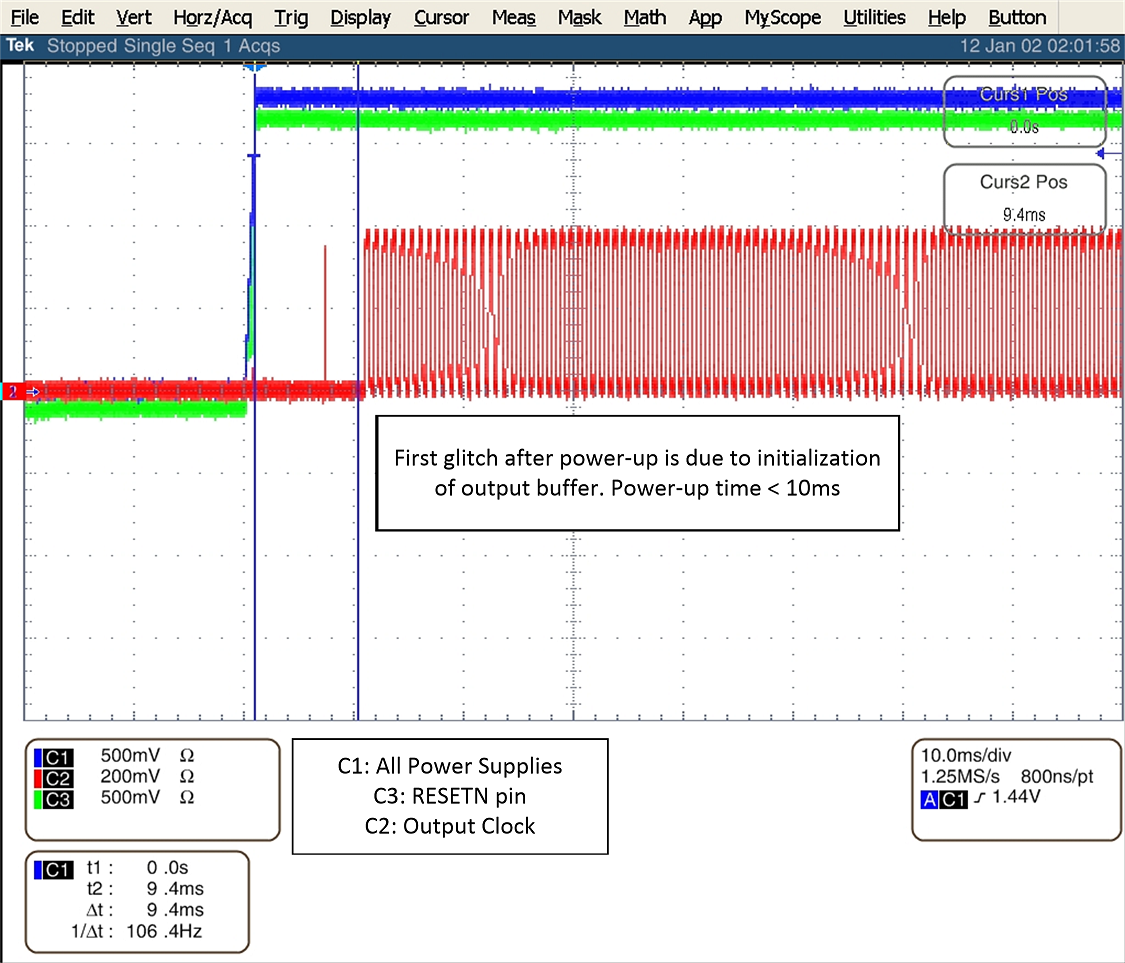

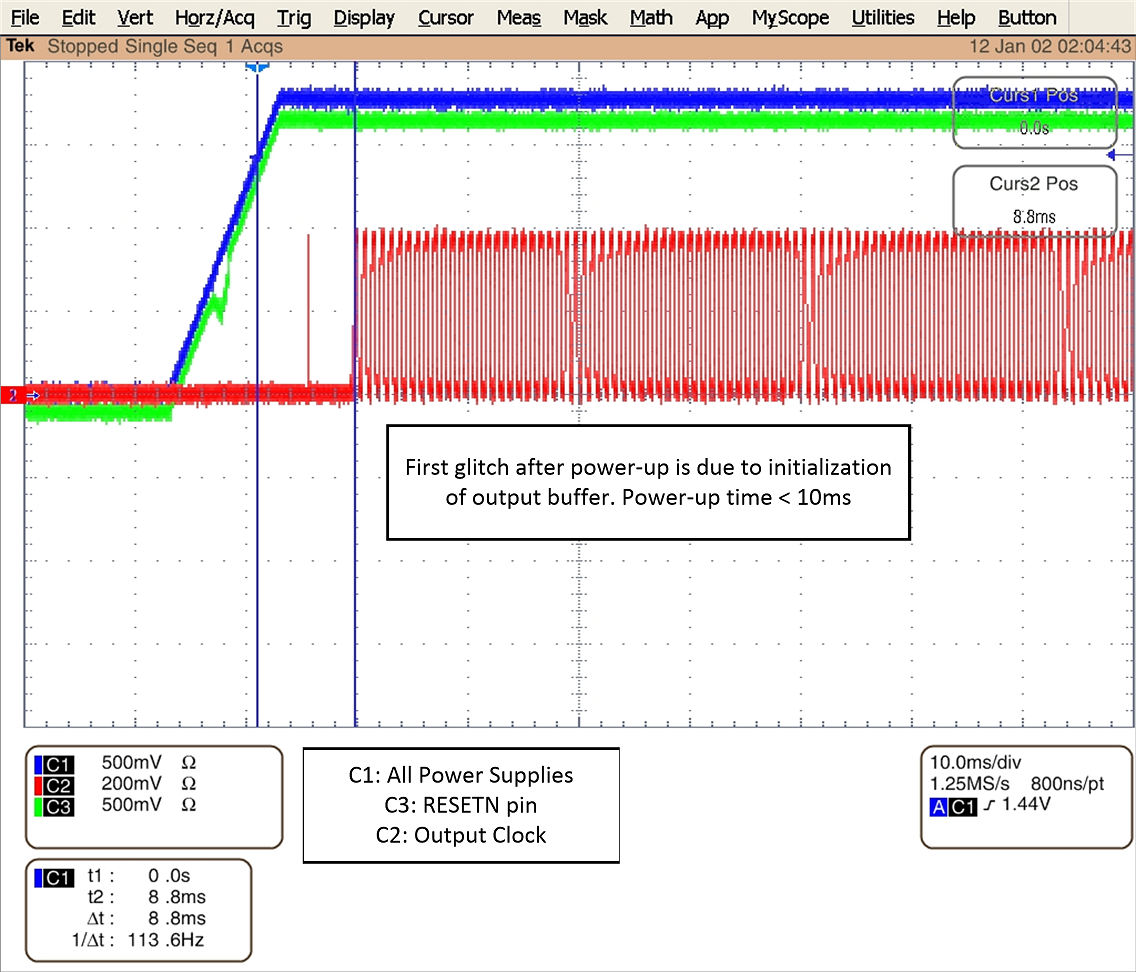

- 8.21 パワーオン・リセット特性

- 8.22 I2C 互換シリアル・インターフェイスの特性

- 8.23 タイミング要件、I2C 互換シリアル・インターフェイス

- 8.24 電源特性

- 8.25 代表的特性

- 9 パラメータ測定情報

- 10詳細説明

- 11アプリケーションと実装

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGE|24

サーマルパッド・メカニカル・データ

- RGE|24

発注情報

8.25 代表的特性

室温で測定

| リファレンス:水晶振動子入力 25MHz | 2.5GHz VCO による閉ループ位相ノイズ | 156.25MHz LVDS |

| リファレンス:水晶振動子入力 25MHz | 2.376GHz VCO による閉ループ位相ノイズ | 148.5MHz LVDS |

| リファレンス:水晶振動子入力 25MHz | 2.4GHz VCO による閉ループ位相ノイズ | 100MHz LP-HCSL |

| リファレンス:水晶振動子入力 25MHz | 2.4576GHz VCO による閉ループ位相ノイズ | 24.576MHz LVCMOS |