JAJSEY5 March 2018 CSD86336Q3D

PRODUCTION DATA.

- 1特長

- 2アプリケーション

- 3概要

- 4改訂履歴

-

5Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions

- 5.3 Thermal Information

- 5.4 Power Block Performance

- 5.5 Electrical Characteristics – Q1 Control FET

- 5.6 Electrical Characteristics – Q2 Sync FET

- 5.7 Typical Power Block Device Characteristics

- 5.8 Typical Power Block MOSFET Characteristics

- 6Application and Implementation

- 7Layout

- 8デバイスおよびドキュメントのサポート

- 9メカニカル、パッケージ、および注文情報

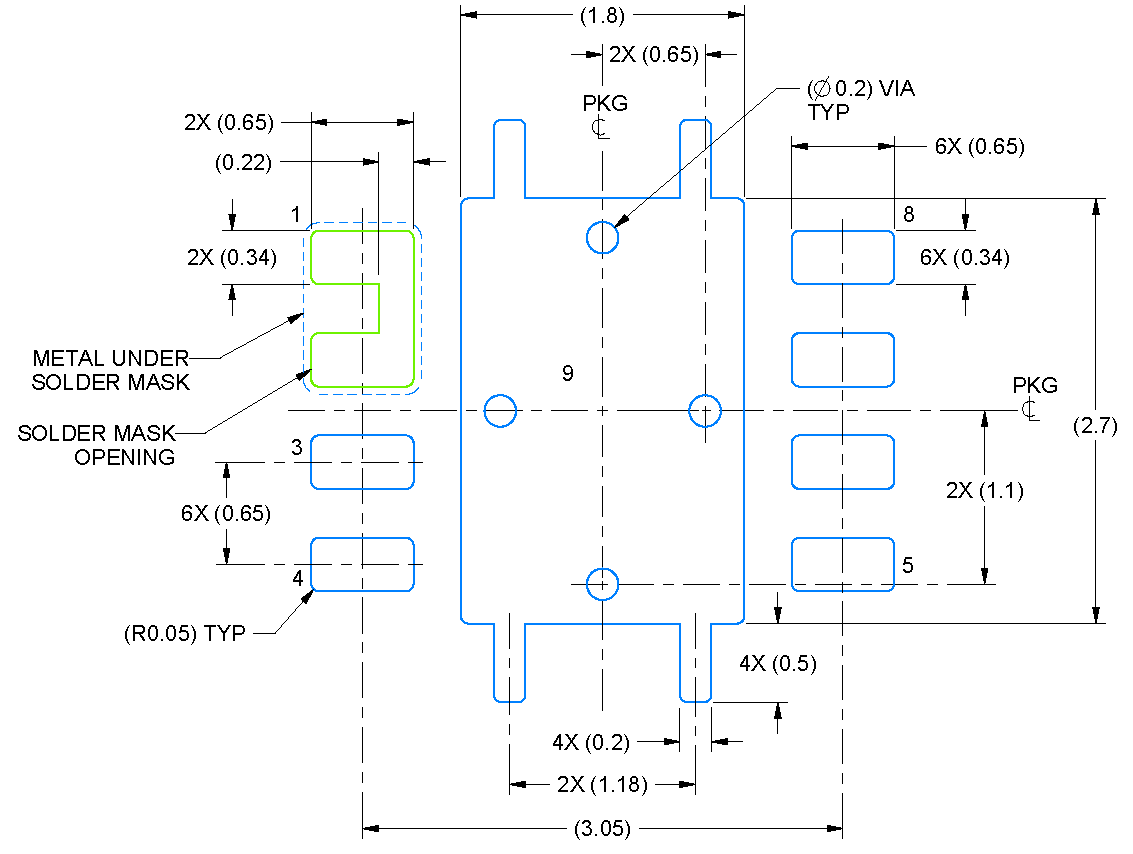

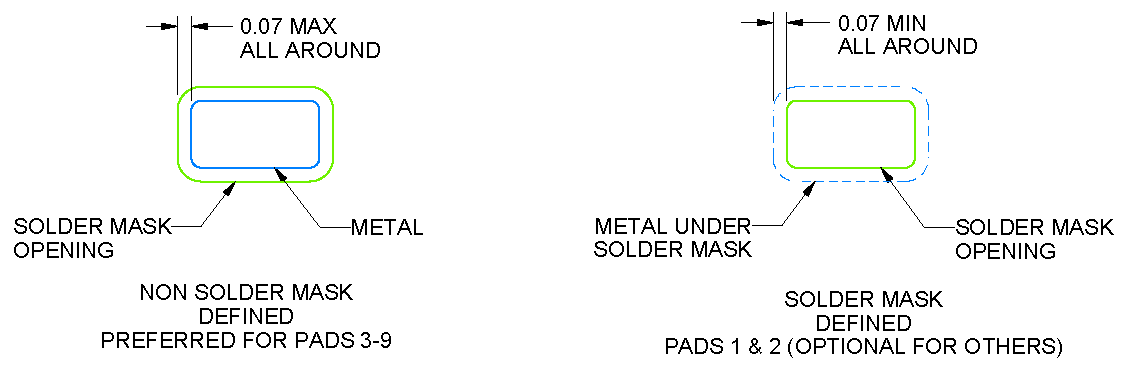

9.3 推奨ランド・パターン

- すべての直線寸法はミリメートル(mm)単位です。括弧内のすべての寸法は、参照のみを目的としたものです。寸法と許容誤差は、ASME Y14.5M準拠です。

- このパッケージは、基板上のサーマル・パッドにハンダ付けされるよう設計されています。詳細については、『QFN/SON PCBアタッチメント』(SLUA271)を参照してください。

- ビアはアプリケーションに応じてのオプションです。デバイスのデータシートを参照してください。一部またはすべてを実装する場合に推奨されるビアの場所が示されています。