JAJSEY5 March 2018 CSD86336Q3D

PRODUCTION DATA.

- 1特長

- 2アプリケーション

- 3概要

- 4改訂履歴

-

5Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions

- 5.3 Thermal Information

- 5.4 Power Block Performance

- 5.5 Electrical Characteristics – Q1 Control FET

- 5.6 Electrical Characteristics – Q2 Sync FET

- 5.7 Typical Power Block Device Characteristics

- 5.8 Typical Power Block MOSFET Characteristics

- 6Application and Implementation

- 7Layout

- 8デバイスおよびドキュメントのサポート

- 9メカニカル、パッケージ、および注文情報

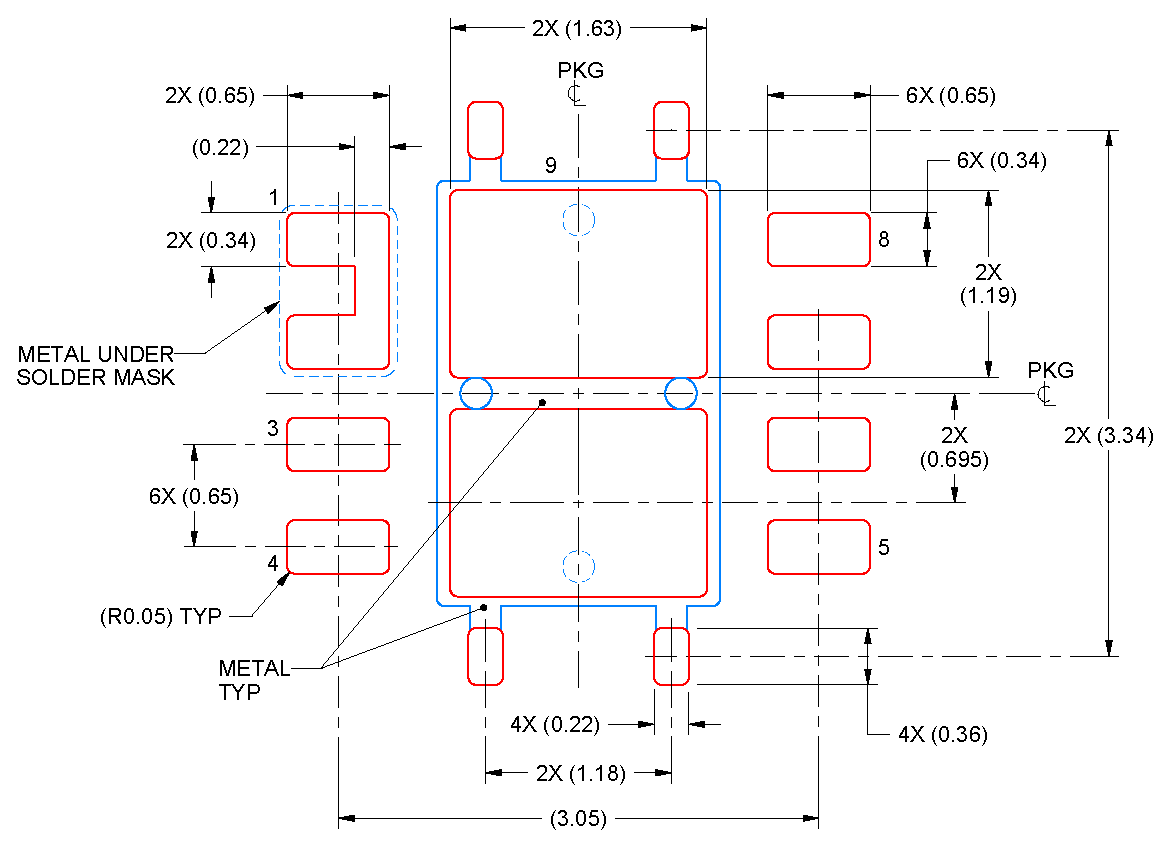

9.4 推奨ステンシル

- すべての直線寸法はミリメートル(mm)単位です。括弧内のすべての寸法は、参照のみを目的としたものです。寸法と許容誤差は、ASME Y14.5M準拠です。

- レーザ・カット・アパーチャの壁面を台形にし、角に丸みを付けることで、ペースト離れが良くなります。IPC-7525には、別の設計推奨事項が存在する可能性があります。