JAJSDT0 September 2017 CSD87503Q3E

PRODUCTION DATA.

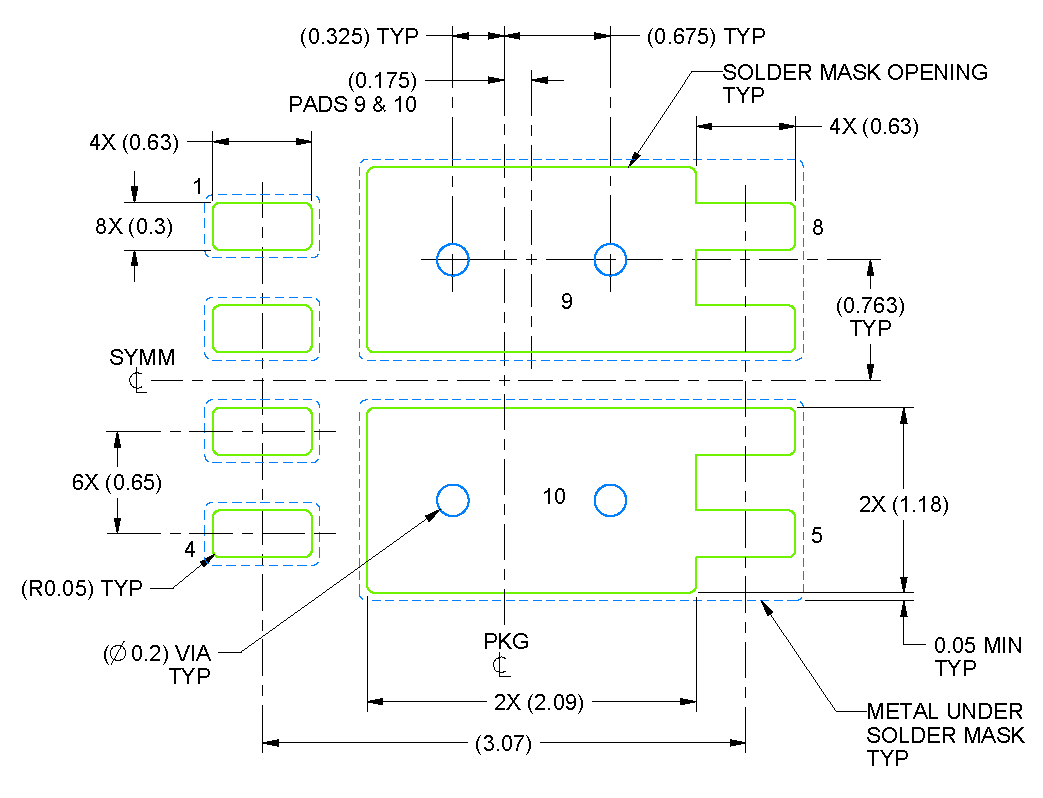

7.2 推奨されるPCBパターン

- このパッケージは、基板上のサーマル・パッドにハンダ付けされるよう設計されています。詳細については、『QFN/SON PCBアタッチメント』(SLUA271)を参照してください。

- ビアはアプリケーションに応じてのオプションです。デバイスのデータシートを参照してください。ビアを実装する場合、この図に示されているビアの位置を参考にしてください。ペーストの下のビアは埋める、プラグを付ける、またはテントで覆うことをお勧めします。

- この図面は、予告なく変更される可能性があります。