JAJSRY8A November 2023 – March 2024 DAC39RF12 , DAC39RFS12

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Device Comparison

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - DC Specifications

- 6.6 Electrical Characteristics - AC Specifications

- 6.7 Electrical Characteristics - Power Consumption

- 6.8 Timing Requirements

- 6.9 Switching Characteristics

- 6.10 SPI and FRI Timing Diagrams

- 6.11 Typical Characteristics: Bandwidth and DC Linearity

- 6.12 Typical Characteristics: Single Tone Spectra

- 6.13 Typical Characteristics: Dual Tone Spectra

- 6.14 Typical Characteristics: Noise Spectral Density

- 6.15 Typical Characteristics: Linearity Sweeps

- 6.16 Typical Characteristics: Modulated Waveforms

- 6.17 Typical Characteristics: Phase and Amplitude Noise

- 6.18 Typical Characteristics: Power Dissipation and Supply Currents

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagrams

- 7.3

Feature Description

- 7.3.1 DAC Output Modes

- 7.3.2 DAC Core

- 7.3.3 DEM and Dither

- 7.3.4 Offset Adjustment

- 7.3.5 Clocking Subsystem

- 7.3.6 Digital Signal Processing Blocks

- 7.3.7

JESD204C Interface

- 7.3.7.1 Deviation from JESD204C Standard

- 7.3.7.2 Transport Layer

- 7.3.7.3 Scrambler and Descrambler

- 7.3.7.4 Link Layer

- 7.3.7.5 Physical Layer

- 7.3.7.6 Serdes PLL Control

- 7.3.7.7 Serdes Crossbar

- 7.3.7.8 Multi-Device Synchronization and Deterministic Latency

- 7.3.7.9 Operation in Subclass 0 Systems

- 7.3.7.10 Link Reset

- 7.3.8 Alarm Generation

- 7.4 Device Functional Modes

- 7.5 Programming

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

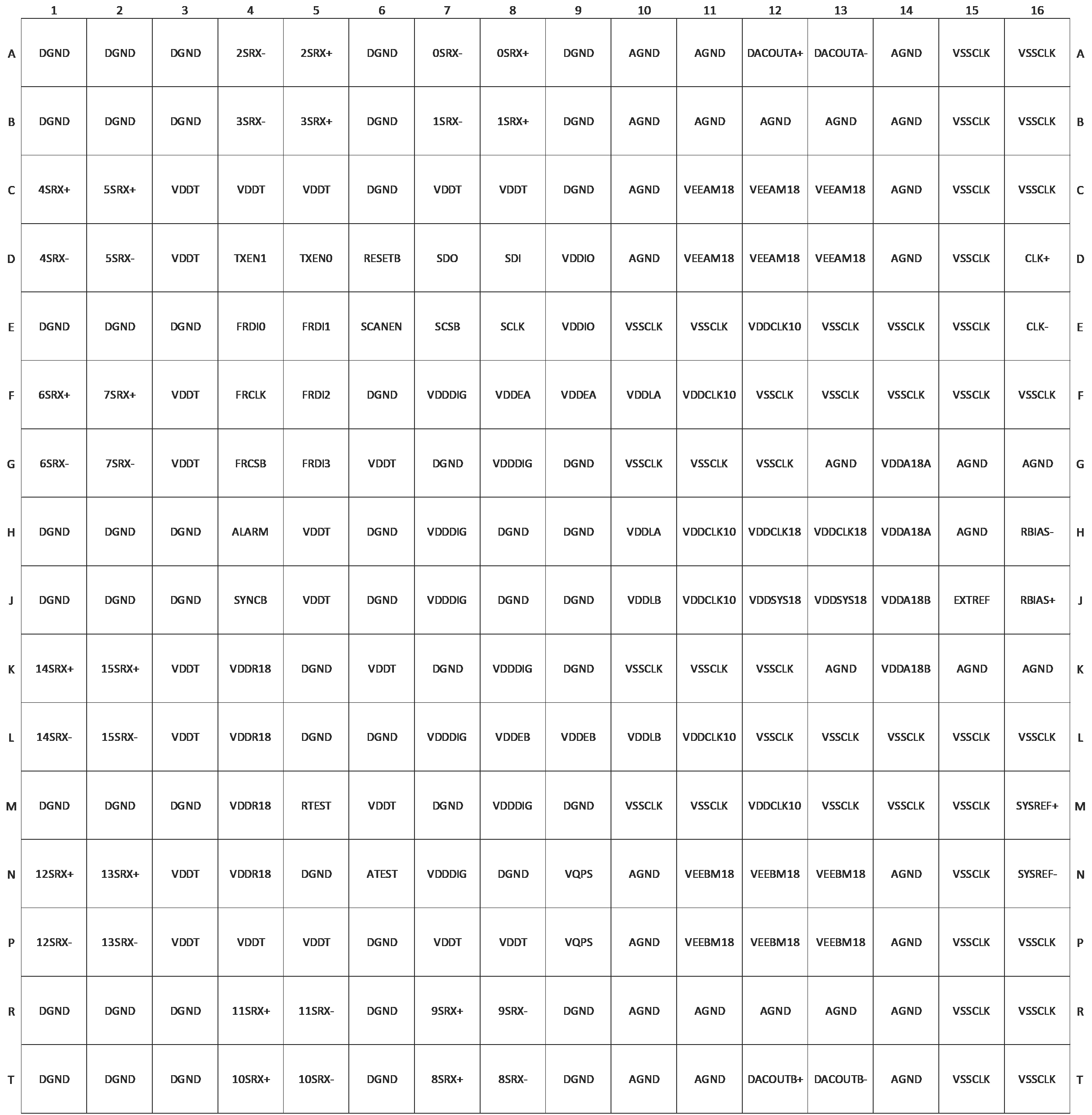

5 Pin Configuration and Functions

Figure 5-1 ACK Package, 256-Ball Flip Chip BGA

with 1mm pitch, Top View

Figure 5-1 ACK Package, 256-Ball Flip Chip BGA

with 1mm pitch, Top View| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | COORD. | ||

| DAC Outputs | |||

| DACOUTA- | A13 | O | DAC channel A analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. |

| DACOUTA+ | A12 | O | DAC channel A analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. |

| DACOUTB- | T13 | O | DAC channel B analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. Not available in single channel devices. |

| DACOUTB+ | T12 | O | DAC channel B analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. Not available in single channel devices. |

| Differential Clock and SYSREF Inputs | |||

| CLK- | E16 | I | Device clock input negative terminal. There is an internal 100-Ω differential termination between CLK+ and CLK–. This input is self-biased and should be AC coupled to the clock source. |

| CLK+ | D16 | I | Device clock input positive terminal. There is an internal 100-Ω differential termination between CLK+ and CLK–. This input is self-biased and should be AC coupled to the clock source. |

| SYSREF- | N16 | I | Differential JESD204C SYSREF input negative terminal.There is an internal 100-Ω differential termination between SYSREF+ and SYSREF–. |

| SYSREF+ | M16 | I | Differential JESD204C SYSREF input negative terminal.There is an internal 100-Ω differential termination between SYSREF+ and SYSREF–. |

| SerDes Interface | |||

| 0SRX- | A7 | I | Serdes Lane 0 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 0SRX+. |

| 0SRX+ | A8 | I | Serdes Lane 0 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 0SRX-. |

| 1SRX- | B7 | I | Serdes Lane 1 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 1SRX+. |

| 1SRX+ | B8 | I | Serdes Lane 1 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 1SRX-. |

| 2SRX- | A4 | I | Serdes Lane 2 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 2SRX+. |

| 2SRX+ | A5 | I | Serdes Lane 2 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 2SRX-. |

| 3SRX- | B4 | I | Serdes Lane 3 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 3SRX+. |

| 3SRX+ | B5 | I | Serdes Lane 3 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 3SRX-. |

| 4SRX- | D1 | I | Serdes Lane 4 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 4SRX+. |

| 4SRX+ | C1 | I | Serdes Lane 4 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 4SRX-. |

| 5SRX- | D2 | I | Serdes Lane 5 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 5SRX+. |

| 5SRX+ | C2 | I | Serdes Lane 5 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 5SRX-. |

| 6SRX- | G1 | I | Serdes Lane 6 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 6SRX+. |

| 6SRX+ | F1 | I | Serdes Lane 6 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 6SRX-. |

| 7SRX- | G2 | I | Serdes Lane 7 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 7SRX+. |

| 7SRX+ | F2 | I | Serdes Lane 7 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 7SRX-. |

| 8SRX- | T8 | I | Serdes Lane 8 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 8SRX+. |

| 8SRX+ | T7 | I | Serdes Lane 8 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 8SRX-. |

| 9SRX- | R8 | I | Serdes Lane 9 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 9SRX+. |

| 9SRX+ | R7 | I | Serdes Lane 9 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 9SRX-. |

| 10SRX- | T5 | I | Serdes Lane 10 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 10SRX+. |

| 10SRX+ | T4 | I | Serdes Lane 10 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 10SRX-. |

| 11SRX- | R5 | I | Serdes Lane 11 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 11SRX+. |

| 11SRX+ | R4 | I | Serdes Lane 11 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 11SRX-. |

| 12SRX- | P1 | I | Serdes Lane 12 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 12SRX+. |

| 12SRX+ | N1 | I | Serdes Lane 12 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 12SRX-. |

| 13SRX- | P2 | I | Serdes Lane 13 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 13SRX+. |

| 13SRX+ | N2 | I | Serdes Lane 13 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 13SRX-. |

| 14SRX- | L1 | I | Serdes Lane 14 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 14SRX+. |

| 14SRX+ | K1 | I | Serdes Lane 14 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 14SRX-. |

| 15SRX- | L2 | I | Serdes Lane 15 negative input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 15SRX+. |

| 15SRX+ | K2 | I | Serdes Lane 15 positive input. Includes in package AC-coupling series capacitor and 100Ω internal termination to 15SRX-. |

| GPIO Functions | |||

| ALARM | H4 | O | ALARM pin is asserted when an internal unmasked alarm is detected. Alarm mask is set by ALM_MASK register. |

| FRCLK | F4 | I | Fast reconfiguation interface clock. |

| FRCS | G4 | I | Fast reconfiguation interface chip select. Internal pullup. |

| FRDI0 | E4 | I | Fast reconfiguation interface data bit 0. |

| FRDI1 | E5 | I | Fast reconfiguation interface data bit 1. |

| FRDI2 | F5 | I | Fast reconfiguation interface data bit 2. |

| FRDI3 | G5 | I | Fast reconfiguation interface data bit 3. |

| RESET | D6 | I | Device reset input, active low. Must be toggled after power up. Internal pullup. |

| SCANEN | E6 | I |

TI use only, can be left unconnected. Internal pulldown. |

| SCLK | E8 | I | Serial programming interface (SPI) clock input. |

| SCS | E7 | I | Serial programming interface (SPI) device select input, active low. Internal pullup. |

| SDI | D8 | I |

Serial programming interface (SPI) data input. |

| SDO | D7 | O | Serial programming interface (SPI) data output. High impedance when not reading out SPI data. |

| SYNC | J4 | O | JESD204C SYNC output, active low. |

| TXEN0 | D5 | I |

Transmit enable for channel A active high input. This pin must be enabled using register USE_TX_EN0. The DAC output is forced to midcode (0x0000 in 2's complement) when transmission is disabled. Internal pullup. |

| TXEN1 | D4 | I |

Transmit enable for channel B active high input. This pin must be enabled using register USE_TX_EN1. The DAC output is forced to midcode (0x0000 in 2's complement) when transmission is disabled. Internal pullup. |

| Analog functions | |||

| ATEST | N6 | O | Analog test pin. Can be left disconnected if not used. |

| EXTREF | J15 | I/O | Reference voltage output or input, determined by the EXTREF_EN register field. If the internal reference is used, the ball should be tied through 0.1uF to AGND. |

| RBIAS- | H16 | O | Full-scale output current bias is set by the resistor tied from this terminal to RBIAS+. |

| RBIAS+ | J16 | O | Full-scale output current bias is set by the resistor tied from this terminal to RBIAS-. |

| RTEST | M5 | O | TI use only. Tie to AGND. |

| Power Supplies | |||

| VDDA18A | G14 H14 | I |

1.8-V supply voltage for DAC channel A. Can be combined with VDDA18B, but may degrade channel-to-channel crosstalk (XTALK). |

| VDDA18B | J14 K14 | I | 1.8-V supply voltage for DAC channel B. Can be combined with VDDA18A, but may degrade channel-to-channel crosstalk (XTALK). |

| VDDCLK10 | F11 H11 J11 L11 E12 M12 | I | 1.0-V supply voltage for internal sampling clock distribution path. Noise or spurs on this supply may degrade phase noise performance. Recommended to separate from VDDDIG and VDDA for best performance. |

| VDDCLK18 | H12 H13 | I | 1.8-V supply voltage for clock (CLK+/–) input buffer. Noise or spurs on this supply may degrade phase noise performance. |

| VDDDIG | F7 H7 J7 L7 N7 G8 K8 M8 | I | 1.0-V supply voltage for digital block. Recommended to separate from VDDA and VDDCLK for best performance. |

| VDDEA | F8 F9 | I | 1.0-V supply voltage for channel A DAC encoder. Recommended to separate from VDDDIG for best performance. Can be combined with VDDEB. |

| VDDEB | L8 L9 | I | 1.0-V supply voltage for channel B DAC encoder. Recommended to separate from VDDDIG for best performance. Can be combined with VDDEA. |

| VDDIO | D9 E9 | I | 1.8-V supply for CMOS input and output terminals. |

| VDDLA | F10 H10 | I | 1.0-V supply for DAC analog latch for channel A. Separate from VDDLB for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance. |

| VDDLB | J10 L10 | I | 1.0-V supply for DAC analog latch for channel B. Separate from VDDLA for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance. |

| VDDR18 | K4 L4 M4 N4 | I | 1.8V Supply voltage for SerDes receivers. |

| VDDSYS18 | J12 J13 | I | 1.8-V supply voltage for SYSREF (SYSREF+/–) input buffer. Can be combined with VDDCLK18 when SYSREF is disabled during normal operation. This supply should be separate from VDDCLK18 when SYSREF is run continuously during operation to avoid noise and spur coupling and reduced phase noise performance. |

| VDDT | C3 D3 F3 G3 K3 L3 N3 P3 C4 P4 C5 H5 J5 P5 G6 K6 M6 C7 P7 C8 P8 | I | 1.0V Supply voltage for SerDes termination. |

| VEEAM18 | C11 D11 C12 D12 C13 D13 | I | –1.8-V supply voltage for DAC current source bias for channel A. Can be combined with VEEBM18, but may degrade channel-to-channel crosstalk (XTALK). |

| VEEBM18 | N11 P11 N12 P12 N13 P13 | I | –1.8-V supply voltage for DAC current source bias for channel B. Can be combined with VEEAM18, but may degrade channel-to-channel crosstalk (XTALK). |

| VQPS | N9 P9 | I | TI use only. Can be tied to DGND during normal operation. |

| Grounds | |||

| AGND | A10 B10 C10 D10 N10 P10 R10 T10 A11 B11 R11 T11 B12 R12 B13 G13 K13 R13 A14 B14 C14 D14 N14 P14 R14 T14 G15 H15 K15 G16 K16 | - | Analog ground. |

| DGND | A1 B1 E1 H1 J1 M1 R1 T1 A2 B2 E2 H2 J2 M2 R2 T2 A3 B3 E3 H3 J3 M3 R3 T3 K5 L5 N5 A6 B6 C6 F6 H6 J6 L6 P6 R6 T6 G7 K7 M7 H8 J8 N8 A9 B9 C9 G9 H9 J9 K9 M9 R9 T9 | - | Digital ground. |

| VSSCLK | E10 G10 K10 M10 E11 G11 K11 M11 F12 G12 K12 L12 E13 F13 L13 M13 E14 F14 L14 M14 A15 B15 C15 D15 E15 F15 L15 M15 N15 P15 R15 T15 A16 B16 C16 F16 L16 P16 R16 T16 | - | Clock ground. |